JP3713876B2 - 論理回路接続装置 - Google Patents

論理回路接続装置 Download PDFInfo

- Publication number

- JP3713876B2 JP3713876B2 JP07307297A JP7307297A JP3713876B2 JP 3713876 B2 JP3713876 B2 JP 3713876B2 JP 07307297 A JP07307297 A JP 07307297A JP 7307297 A JP7307297 A JP 7307297A JP 3713876 B2 JP3713876 B2 JP 3713876B2

- Authority

- JP

- Japan

- Prior art keywords

- instruction

- transfer

- logic circuit

- data

- instructions

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Multi Processors (AREA)

- Bus Control (AREA)

Description

【発明の属する技術分野】

本発明は、論理回路間の命令の転送性能を向上する論理回路接続方法及びそれを用いた論理回路接続装置に係り、特に複数のプロセッサを結合した並列計算機のプロセッサ間の接続に用いるのに好適な論理回路接続方法及び論理回路接続装置に関する。

【0002】

【従来の技術】

計算機等の大規模なシステムは、全体を適当な論理単位(モジュール単位)に分割され、モジュール単位で個別に設計される。従来、モジュールはシステムを構成する集積回路単位としていた。近年では、特に、集積回路の大規模化が進んでおり、集積回路内を更に複数のモジュールに分割して、分割された個々のモジュール単位で設計することが一般的となっている。

【0003】

システム及び集積回路内の各モジュール間のデータ信号や制御信号の授受の方法は、送信側及び受信側のモジュール間のインターフェイスとして規定される。そして、信号の送信側及び受信側の双方のモジュールは、このインターフェイスに従って動作する様に設計される。

【0004】

上記のモジュール間のインターフェイスは、使用する信号線数が少ないことが要求される。これは、集積回路間のインターフェイスでは、集積回路の入出力ピン数に制限があること、集積回路内のインターフェイスでは、モジュール間の信号線はモジュール内の信号線と比較して長くなりやすく、集積回路の配線領域を多くとること、の理由による。

【0005】

通常、モジュール間でやり取りする命令は複数存在する。これらの命令毎にモジュール間の信号線を設け、個別に転送する構造を採用した場合、信号線数が多くなり、上記要求を満たせない。このため、通常は、命令の種類を伝える制御信号と付随するデータを伝えるデータ信号線を設け、複数の命令で信号線を共用するインターフェースを採用する。この方式では、送信側モジュールに、モジュールの論理回路内の種々の命令の転送要求を受付けて受信側に転送する送信回路を設け、受信側モジュールには送信回路から命令の信号線を介して転送された命令を受けて受信モジュール内の論理回路に発行する受信回路を設ける。なお、送信回路、命令の信号線、受信回路からなる部分を論理回路接続装置と呼ぶ。

【0006】

この従来の論理回路接続装置では、同時に転送可能な命令数は固定であった。例えば、「MIPS R10000 Microprocessor User's Manual Version 2.0(MIPS Technologies Inc.発行)」の第6章によると(従来技術1)、R10000はスプリットトランザクション方式のバスを採用し、アドレス及びデータの転送を64ビットのバス(multiplex address/data bus)で転送する。バスをアドレス転送及びデータ転送のいずれに使用するかは、命令毎に指定される。例えば、プロセッサがメモリ読出しを発行する"Processor Block Read Request"、外部からプロセッサのキャッシュを無効化する"External Invalidate Request"はアドレス転送であり40ビットを用いていた。また、外部からプロセッサにメモリデータを返送する"External Block Data Response"はデータ転送であり、64ビットを用いていた。このように一度に転送される命令が使用するバス幅は固定されていた。

【0007】

また、特開平8−16510号公報(従来技術2)には、システムバスを介して複数の入出力装置とプロセッサ間でデータ転送を行う場合に、データバスを複数の入出力装置が使用するフィールドに分割して転送を行うことが記載されている。この例では、複数の入出力装置はプロセッサから同一のアドレスに配置され、入出力装置とプロセッサ間のデータ幅は固定となっていた。

【0008】

また、特開昭62−134745号公報(従来技術3)には、中央処理装置及び主記憶装置と複数の入出力装置間でデータ転送を行う場合に、共通バスを2分割し、上位を入出力装置1、下位を入出力装置2で使用することが記載されている。この従来技術では、処理モジュール(中央処理装置、入出力装置等)の種類に応じて共通バスの上位/下位を独立に使用するか、または同時に使用するかが決められていた。

【0009】

【発明が解決しようとする課題】

上記従来技術1で述べた論理回路接続装置では、命令の種類により転送するデータ長が異なる場合、データ長の短い命令は信号線の一部のみを使用して転送される。このため、データ長の短い命令の伝達時に信号線に空きができる。アドレスは40ビットであるため、バスをアドレス転送に使用する場合には、その他制御信号を付加しても17ビットの未使用部分が生じる。今後、バス幅が128ビット等に拡大されると、アドレス転送時の未使用部分が増加する。

【0010】

また、従来技術2で述べた論理回路接続装置では、対象とする転送区間がプロセッサと入出力装置間に限定されており、また、入出力装置とプロセッサ間のデータ幅は固定であり、定められたデータ幅より小さいデータ幅を持つ命令のデータ転送の場合にはシステムバスに未使用部分が生じ無駄を生じていた。

【0011】

また、従来技術3で述べたものに関しては、処理モジュールの種類に応じて共通バスの上位/下位を独立に使用するか、または同時に使用するかが決められていたが、処理モジュール間で転送される個々の命令の転送単位では、バスの使用ビット数を設定することができず、即ち、バス上位や下位等で定められたデータ幅より小さいデータ幅を持つ命令のデータ転送の場合にはシステムバスに未使用部分が生じ無駄を生じていた。

【0012】

本発明の目的は、命令単位で、転送するデータ長が短い命令の転送時に、命令データ信号線の空きビットを利用して複数の命令を伝達し、転送性能を向上することにある。

【0013】

【課題を解決するための手段】

上記課題を解決するために、送信側論理回路が転送を要求する複数の命令の中から、同時に受信側論理回路に転送可能な命令の組を選択する調停回路と、選択した命令の組を転送命令に変換し、受信側論理回路に向けて送出するエンコーダと、エンコーダからの転送命令を受けて送信側論理回路が発行した命令の組を復元するデコーダを備え、送信側論理回路側は、調停回路、エンコーダ、デコーダからなる論理回路接続装置を介して、各命令の種類により異なる個数の命令を同一サイクルで受信側論理回路に送出可能とする。

【0014】

【発明の実施の形態】

(実施例1)

以下に、本発明の第1の実施例を図1〜3を用いて説明する。

【0015】

図1は、本発明に係る論理回路接続装置を示す。図1の論理回路接続装置は、調停回路100、エンコーダ102、デコーダ104、および信号線から構成される。送信側論理回路から送出される命令(命令コード部と命令データ部から構成される)は、ポートA〜ポートDから論理回路接続装置に与えられ、論理回路接続装置を通って受信側論理回路のポートE及びポートFに転送される。

【0016】

送信側論理回路から受信側論理回路へ出力される命令は、命令の種類によって、命令データ部の転送に必要とする信号線のビット幅が異なる。そこで、命令データ部の転送に必要な信号線のビット数が送信側論理回路から受信側論理回路へ向けて設けられている信号線のビット数より小さい場合は、複数の命令を纏めて転送することにより、つまり、1つの命令のデータ部の転送では使用していなかった信号線の部分に、他の命令のデータ部を合わせて転送することにより、信号線の未使用部分をなくすことができ、結果として信号線を有効に利用することができる。

【0017】

本願発明では、送信側論理回路と受信側論理回路との間に論理回路接続装置を設け、送信側論理回路側にある論理回路接続装置(調停回路100及びデコーダ102)によって、送信側論理回路が送信した命令を少なくとも1つ以上纏めて一つの新たな命令(転送命令)として合成し、合成した転送命令を受信側論理回路側にある論理回路接続装置(デコーダ104)へ、エンコーダとデコーダ間の信号線(転送ライン)を用いて転送し、転送命令を受信したデコーダは、送信側論理回路が出力した元の複数の命令に戻して受信側論理回路へ出力する。これにより、エンコーダとデコーダ間の信号線を有効利用でき、複数の命令を同時に送信側論理回路から受信側論理回路へ転送することが可能となる。

【0018】

従って、一つの転送命令で2つ以上の命令を転送できるようになる。例えば、従来1サイクルで命令を転送できていたとすれば、この転送命令を用いることで、1サイクルで2つの命令を転送できるようになり、効率よく命令を転送できるようになる。言い換えれば、本実施例は、送信側論理回路から受信側論理回路に対して同一サイクルに伝送する命令数を、命令データの長さに応じて変えることができる点に特長がある。

【0019】

また、送信側論理回路側のエンコーダと受信側論理回路側のデコーダ間の転送ラインは、送信側論理回路からエンコーダまでの距離やデコーダから受信側論理回路までの距離と比べて一般に長く、この部分の領域は、複数の論理回路およびモジュール間転送路から構成されるシステムの全体を考える場合、送信側論理回路からエンコーダまでの距離やデコーダから受信側論理回路までの転送路の領域より大きいといえる。従って、この転送ラインを、命令に応じて使い分けることは重要である。

【0020】

以下、図1を詳しく説明する。

【0021】

送信側論理回路のポート数は、送信側論理回路が同時に発行しうる命令の数により決定される。受信側論理回路のポート数は、1つの転送命令で転送可能な命令の最大数により決定される。本実施例では、送信側論理回路のポート数を4、受信側論理回路のポート数を2としているが、これらの値は送信側論理回路の構成及び1つの転送命令で転送可能な命令数によって変わりうる。

【0022】

調停回路100は、出力側論理回路がポートA〜ポートDを通して出力する最大4つの命令の中から受信側論理回路へ出力する命令を最大2つ選択し、選択命令ライン1(130a、140a)及び選択命令ライン2(130b、140b)を通してエンコーダ102に出力する。エンコーダ102は、調停回路100で選択された命令を転送命令に変換し、転送ライン(150、160)を通してデコーダ104に出力する。デコーダ104は、エンコーダ102から受けた転送命令を調停回路100が選択した命令に戻し、ポートE及びポートFを通して受信側論理回路に出力する。

【0023】

送信側論理回路のポートA〜ポートDから調停回路へ信号線を介して命令が転送される。それぞれのポートから接続される信号線は、命令コード部を転送する信号線110a〜110d、命令データ部を転送する信号線120a〜120d、および、調停回路が送信側論理回路へ命令を受理したことを知らせるためのアクノリッジ信号線から構成される。命令コード部を転送する信号線は、命令の種類を転送するのに用いる。図1では、それぞれのポートに対して、命令コード部を転送する信号線として2ビット、命令データ部を転送する信号線として64ビット、アクノリッジ信号線として1ビットが割り付けられている。

【0024】

次に、送信側論理回路から調停回路へ転送される命令について説明する。命令は、命令の種類を示す2ビットの命令コード部と、命令により伝送する命令データ部分からなる。ここで、命令の種類というのは、命令が、命令データ部を転送する信号線の内、実際に使用する信号線の部分を示すものである。例えば、命令データを転送する信号線が64ビットとした場合、64ビットの内の64ビットを全て使用するとか、上位32ビットを使用するとか、上位16ビットを使用するとかの違いによる種類である。従って、図1においては、命令コード部が上位32ビットの使用すると示す場合、命令コード部を転送する64ビットの信号線の内の上位32ビットの信号線を用いて命令データ部が伝送されることになる。

【0025】

調停回路100は、出力側論理回路がポートA〜ポートDを通して出力した命令の中から受信側論理回路へ出力する命令を複数選んで送出する。基本的な選び方は次のようになる。選択は、選択した一つ以上の命令の命令データ部のビット数の合計が、エンコーダからデコーダへの転送ラインの信号線のビット数より大きくならない様に、一つ以上の命令が選択される。選択された一つ以上の命令は、調停回路100からエンコーダ102へ選択命令ライン1および選択命令ライン2を介して送られる。選択命令ライン1及び2の構造は、ポートA〜Dの信号線の構造からアクノリッジ信号線を削除した構造と同じである。図1においては、出力側論理回路がポートA〜ポートDを通して出力する最大4つの命令の中から受信側論理回路へ出力する命令を最大2つ選択し、選択命令ライン1(130a、140a)及び選択命令ライン2(130b、140b)を通してエンコーダ102に出力する。なお、調停回路100については後で更に詳細に説明する。

【0026】

エンコーダ102(後で詳細に述べる)は、調停回路100で選択された1つ以上の命令を選択命令ライン1及び2から受信すると、これら1つ以上の命令を一つの転送命令(後述する)に変換し、転送ライン(転送コード部用信号線150、転送データ部用信号線160)を通してデコーダ104に出力する。転送命令は、転送命令の種類を示す2ビットの転送コード部と、転送命令により伝送するデータ部分である64ビットの転送データ部からなる。転送コード部は、調停回路からきた命令がどのような種類であり、また、これをどのように組み合わせたかを示す情報をであり、転送ラインの転送コード部用信号線を介して転送される。転送データ部は、調停回路より受信した命令のデータを送る部分であり、例えば、全ビットが1つの命令のデータであったり、転送データ部の上位と下位とで互いに異なる命令のそれぞれのデータ部であったりし、これらは、転送データ部用信号線を介して転送される。

【0027】

デコーダ104は、エンコーダ102から転送ラインを介して受けた転送命令の転送コード部により、受信した転送データ部がどのような種類の命令の組み合わせであるかを判定し、判定結果に従って、転送データ部をそのまま、または必要に応じて分割して命令データ部を得て、判定結果である命令コード部と命令データ部を組み合わせて一つの命令とし、これを命令として、デコーダから受信側論理回路へ出力する。即ち、転送ラインから受信した転送命令を調停回路100が選択した1つ以上の命令に戻し、ポートE及びポートFを通して受信側論理回路に出力する。デコーダ104からポートEおよびポートFへの命令信号線のそれぞれの構造は、ポートA信号線の構造からアクノリッジ信号線を削除した構造と同様の構造であり、170a、170bが命令コード部であり、180a、180bが命令データ部を伝送する信号線である。なお、デコーダ104については後で更に説明する。

【0028】

なお、本実施例では、命令コード部と転送コード部を2ビット、命令データ部と転送データ部を64ビットとしているが、本発明は任意の命令および転送命令の構成について有効である。

【0029】

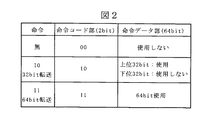

図2は、図1の論理回路接続装置で使用する命令を示す。命令は、命令コード部と命令データ部から構成される。命令コード部が"00"の場合、命令を発行しないことを示す。命令I0は、32ビットのデータを伝送する命令であり、命令コード部は"10"、命令データ部は、命令データ部を転送する信号線64ビットの内上位32ビットを用いて転送される。命令I1は、64ビットのデータを伝送する命令であり、命令コード部は"11"であり、命令データ部は、命令データ部を転送する信号線64ビットの全部を用いて転送される。この命令は、送信側論理回路から調停回路への命令、調停回路からエンコーダへの命令、および、デコーダから受信側論理回路への命令として使用される。

【0030】

図3は、図1の論理回路接続装置で使用する転送命令を示す。転送命令は、転送コード部と転送データ部から構成される。転送コード部が"00"の場合、転送命令を発行しないことを示す。転送命令T0は、図2で説明した命令I0を1つ伝送する転送命令である。転送コード部は"01"であり、転送データ部は、64ビットの内上位32ビットを用いて命令I0の命令データが転送される。転送ラインの内、転送する部分である信号線160の上位32ビットが当該転送命令の転送データを転送するのに使用される。転送命令T1は、命令I0を同時に2つ伝送する転送命令である。転送コード部は"10"であり、転送データ部は信号線160の64ビットの内上位32ビットが1つ目の命令I0の命令データ部、下位32ビットが2つ目の命令I0の命令データ部を転送するのに使用される。転送命令T2は、命令データ部が64ビットである命令I1を1つ伝送する転送命令であり、転送コード部は"11"、転送データ部は命令I1の命令データ部とする。

【0031】

本実施例は、送信側論理回路から受信側論理回路に対して同一サイクルに伝送する命令数を、命令データの長さに応じて変えることができる点に特長がある。

【0032】

本実施例の論理回路接続装置の動作を具体的に以下に示す。

【0033】

送信側論理回路は、ポートA〜ポートDを用いて0から4個の命令の転送を要求する。

【0034】

<調停回路の動作>

調停回路100は、同時に転送可能な命令の組をポートA〜ポートDから選択し、エンコーダ102に出力する。以下、調停回路100の構成及び同時に転送可能な命令の組の選択方法を説明する。

【0035】

図27は、調停回路100の構成を示す図である。信号線110a〜110d、120a〜120d、115a〜115d、130a〜130b、140a〜140bは図1の対応する信号線である。調停回路100は、命令順序決定回路100a、命令順序キュー100b、命令選択回路100c、第1命令セレクタ100d、第2命令セレクタ100eにより構成される。

【0036】

命令順序決定回路100aは、ポートA〜ポートDの全ての命令コード部を受けて順序を決定し、ポート番号及び命令コードの列を命令順序キュー100bに送出する。ここでは、命令順序キュー100bの命令順序決定をラウンドロビンで行なうこととする。ラウンドロビン制御は、前回送出したポート番号列の最後のポート番号+1のポートの命令を最優先として送出する。ただし、前回送出したポート番号及び命令コードの列の最後のポート番号がポートDを示す場合、最優先のポートはAとする。例えば、サイクルNでポートB、ポートC、ポートDが命令の送信を要求しており、ポートCが最優先である場合、ポートC、ポートD、ポートBのポート番号及び命令コードの列を命令順序キュー100bに送出し、サイクルN+1ではポートCが最優先となる。従って、サイクルN+1でポートA、ポートDが命令の送信を要求すると、ポートD、ポートAのポート番号及び命令コードの列が命令順序キュー100bに送出される。

【0037】

命令順序キュー100bは、命令順序決定回路100aから送出されるポート番号及び命令コードの列を順に格納し、命令選択回路100cにポート番号及び命令コードを最大2つ送出する。命令選択回路100cの指示により命令がエンコーダに送出されると、命令順序キュー100bから当該エントリを削除する。この制御により、命令順序キュー100b内には送信側論理回路の各ポートから出力中の命令の内、エンコーダ側に出力されなかった命令が発行される順序で格納される。また、ポート番号及び命令コードの格納時に、命令順序キュー100b内に存在するポート番号に対応するものを除外して格納することで、すでにエンコーダへの送出を待っている命令の2重格納を防ぐ。命令順序キュー100bから命令選択回路100cに送出するポート番号及び命令コードが不足する場合、命令順序決定回路100aの送出するポート番号及び命令コードを直接命令選択回路100cに送出する。これにより、命令順序キュー100bが空の場合に送信側論理回路の送出する命令を遅滞なくエンコーダに送出できる。

【0038】

命令選択回路100cは、命令順序キュー100bから送出されるポート番号及び命令コードを最大2つ受け、これらの命令が同時に送出可能かどうかを判断し、判断結果に基づいて第1命令セレクタ100d、第2命令セレクタ100eを制御する。本実施例においては、命令順序キュー100bが命令I0を2つ送出した場合のみ、これらの命令を同時に送出可能である。従って、以下のアルゴリズムにより、第1命令セレクタ100d及び第2命令セレクタ100eを制御し、命令をエンコーダに発行する。

【0039】

(1)命令順序キュー100bから命令I0を2つ受け取った場合、

第1の命令のポート番号を第1命令セレクタ100dに送出してセレクタを制御し、信号線130a、140aを介して対応する命令をエンコーダに送出する。同時に、第2の命令のポート番号を第2命令セレクタ100eに送出してセレクタを制御し、信号線130b、140bを介して対応する命令をエンコーダに送出する。この時、第1及び第2命令に対応するエントリを命令順序キュー100bから削除すると共に、アクノリッジ信号線115a〜115dの当該ポートに対応する信号線を”1”として、命令の発行を完了する。

【0040】

(2)(1)の場合以外で、命令順序キュー100bから第1の命令I0を受け取った場合、

第1の命令のポート番号を第1命令セレクタ100dに送出してセレクタを制御し、信号線130a、140aを介して対応する命令をエンコーダに送出する。同時に、第2の命令を発行しないことを第2命令セレクタ100eに送出してセレクタを制御し、信号線130bを"00"として、信号線130b、140bからは命令を送出しない。この時、第1命令に対応するエントリを命令順序キュー100bから削除すると共に、アクノリッジ信号線115a〜115dの当該ポートに対応する信号線を”1”として、命令の発行を完了する。

【0041】

(3)命令順序キュー100bから第1の命令I1を受け取った場合、

第1の命令のポート番号を第1命令セレクタ100dに送出してセレクタを制御し、信号線130a、140aを介して対応する命令をエンコーダに送出する。同時に、第2の命令を発行しないことを第2命令セレクタ100eに送出してセレクタを制御し、信号線130bを"00"として、信号線130b、140bからは命令を送出しない。この時、第1命令に対応するエントリを命令順序キュー100bから削除すると共に、アクノリッジ信号線115a〜115dの当該ポートに対応する信号線を”1”として、命令の発行を完了する。

【0042】

(4)第1及び第2の命令を発行しないことを第1命令セレクタ100d及び第2命令セレクタ100eに送出してセレクタを制御し、信号線130a及び130bを"00"として、信号線130b、140bから命令を送出しない。この時、命令順序キュー100bからのエントリの削除を行なわず、アクノリッジ信号線115a〜115dは全て”0”とする。

【0043】

調停回路100を以上の様に構成することで、ポートA〜ポートDから送出される命令を、異なるタイミングで到達するものに対しては前後の順序を維持し、同一のタイミングで到達するものに対してはラウンドロビンで順序を決定して命令を受信側論理回路側に送出することができる。受信側論理回路が、送信側論理回路の発行する命令の順序に関係なく命令を受け付ける場合の構成としては、例えば命令選択回路100cが命令順序キュー100bから任意の1〜2命令を抽出し、発行する方式が考えられる。

【0044】

<エンコーダの動作>

エンコーダ102は、調停回路100から選択命令ライン1及び選択命令ライン2を通して命令の組を受けると、受け取った命令の種類と数に応じて転送命令(図3に示す)を生成し、デコーダ104に対して発行する。

【0045】

図29にエンコーダ102の構成を示す。エンコーダ102は、選択命令ライン1及び選択命令ライン2の命令コードを受けて転送コードを生成する転送命令生成回路102a、転送命令の種類によって転送データ部下位32ビットに選択命令ライン1の命令データ部下位32ビット叉は選択命令ライン2の命令データ部のいずれかを送出するセレクタ102bからなる。以下に、エンコーダ102の動作を示す。

【0046】

(1)調停回路100から命令I0を2つ受けた場合

転送命令生成回路102aは、転送コード信号線150に"10"を出力する。また、転送命令生成回路102aは、命令データ選択線を用いてセレクタ102bを"1"側に選択し、転送データ信号線160の下位32ビットを命令データ信号線140bの値とする。転送データ信号線160の上位32ビットは命令データ信号線140aの値とする。これにより、命令I0を2つ転送する転送命令T1を生成し、デコーダに対して発行できる。

【0047】

(2)(1)以外の場合で、調停回路100から命令コード130aを通して命令I0を受けた場合

転送命令生成回路102aは、転送コード信号線150に"01"を出力する。また、転送命令生成回路102aは、命令データ選択線を用いてセレクタ102bを"0"側に選択し、転送データ信号線160の下位32ビットを命令データ信号線140a下位32ビットの値とする。転送データ信号線160の上位32ビットは命令データ信号線140aの値とする。これにより、命令I0を1つ転送する転送命令T0を生成し、デコーダに対して発行できる。

【0048】

(3)調停回路100から命令コード130aを通して命令I1を受けた場合

転送命令生成回路102aは、転送コード信号線150に"11"を出力する。また、転送命令生成回路102aは、命令データ選択線を用いてセレクタ102bを"0"側に選択し、転送データ信号線160の下位32ビットを命令データ信号線140a下位32ビットの値とする。転送データ信号線160の上位32ビットは命令データ信号線140aの値とする。これにより、命令I0を1つ転送する転送命令T2を生成し、デコーダに対して発行できる。

【0049】

(4)上記(1)〜(3)の場合

転送コード信号線150に"00"を出力し、転送命令を発行しない。

【0050】

<デコーダの動作>

デコーダ104は、エンコーダ102から転送ラインを通して転送命令を受信すると、転送命令の転送コード部を解析し、解析結果に従って命令コードを復元するとともに、転送データ部から命令コード部を引き出す。そして、復元した命令コードと引き出した命令データ部を合わせて命令を復元し、エンコーダ部から受信側論理回路へ復元した命令を送出する。

【0051】

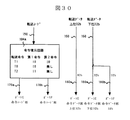

図30にデコーダ104の構成を示す。命令復元回路104aは、転送命令の転送コード部150を受け、送出された命令1〜2個に復元し、第1の命令の命令コード部を信号線170a、第2の命令の命令コード部を170bに送出する。第1の命令の命令データ部は、32ビットを転送する命令I0の場合、転送データ部上位32ビットを用いて転送される。64ビットを転送する命令I1の場合、転送データ部64ビットの全てを用いて転送される。よって、転送データ信号線160は、ポートEの命令データ信号線180aに直結する。第2の命令の命令データ部は、転送命令T1の場合にのみ転送データ部下位32ビットを用いて転送される。よって、転送データ信号線160の下位32ビットはポートFの命令データ部32ビット(180b)として使用される。

【0052】

転送命令の転送コード部と復元する命令の関係は次のようになる。

(1)エンコーダ102から転送命令T2を受けた場合

命令コード信号線170aを"11"、命令データ信号線180aを転送データ信号線160の値とし、入力側論理回路に対して命令I1を発行する。命令コード信号線170bは"00"とし、ポートFからは命令を発行しない。

【0053】

(2)エンコーダ102から転送命令T1を受けた場合

命令コード信号線170a及び命令コード信号線170bを"10"、命令データ信号線180aを転送データ信号線160の上位32ビット、命令データ信号線180bを転送データ信号線160の下位32ビットとし、入力側論理回路に対して命令I0を2つ発行する。入力側論理回路はポートE上の命令を1つ目の命令、ポートF上の命令を2つ目の命令として処理する。

【0054】

(3)エンコーダ102から転送命令T0を受けた場合

命令コード信号線170aを"10"、命令データ信号線180aを転送データ信号線160の上位32ビットの値とし、入力側論理回路に対して命令I0を発行する。命令コード信号線170bは"00"とし、ポートFからは命令を発行しない。

【0055】

図31に本実施例の論理回路接続装置の動作を示す。図31では、サイクルt0でポートAが最優先であり、サイクルt0でポートAが命令I0(I0−01)、ポートCが命令I1(I1−02)、サイクルt1でポートD、ポートBが命令I0(それぞれI0−03、I0−04)、サイクルt2でポートAが命令I1(I1−05)、サイクルt3でポートC及びポートDが命令I0(I0−6、I0−7)を発行している。

【0056】

各サイクルの論理回路接続装置の動作は以下の通りである。

【0057】

(1)サイクルt0

命令I0−01がポートAから、命令I1−02がポートCから入力される。調停回路100内で、命令順序決定回路100aが命令I0−01、命令I1−02の順に命令を順序付け、命令順序キュー100bに送出する。命令選択回路100cは命令順序キュー100bが空のため、命令順序決定回路100aの命令I0−01、I1−02を受け、命令I0−01の発行を決定する。この結果、命令I0−01は受信側論理回路に送出され、ポートAはアクノリッジ信号線115aにより命令の受理を通知される。この時、命令順序キュー100bは命令I0−01が削除されるため、命令I1−02のみを格納する。命令列の最後のポートはCのため、次サイクルの最優先ポートはDとなる。

【0058】

(2)サイクルt1

命令I0−03及び命令I0−04がポートDから入力される。調停回路内で命令順序決定回路100aが命令I0−03、命令I0−04の順に命令を順序付け、命令順序キュー100bに送出する。命令選択回路100cは、命令順序キュー100bに命令I1−02が格納されているため、命令I1−02の発行を決定する。この結果、命令I1−02は受信側論理回路に送出され、ポートCはアクノリッジ信号線115cにより命令の受理を通知される。この時、命令順序キュー100bは命令I1−02が削除され、命令I0−03、命令I0−04を格納する。命令列の最後のポートはBのため、次サイクルの最優先ポートはCとなる。

【0059】

(3)サイクルt2

命令I1−05がポートAから入力される。命令順序決定回路100aは命令I1−05を、命令順序キュー100bに送出する。命令選択回路100cは、命令順序キュー100bに命令I0−03、命令I0−04が格納されており、これらは同時に転送可能であるため、命令I0−03と命令I0−04の発行を決定する。この結果、命令I0−03及び命令I0−04は受信側論理回路に送出され、ポートB及びポートDはアクノリッジ信号線115b、115dにより命令の受理を通知される。この時、命令順序キュー100bは命令I0−03、命令I0−04が削除され、命令I1−05を格納する。命令列の最後のポートはAのため、次サイクルの最優先ポートはBとなる。

【0060】

(4)サイクルt3

命令I0−06がポートCから入力される。命令順序決定回路100aは命令I0−06を、命令順序キュー100bに送出する。命令選択回路100cは、命令順序キュー100bに命令I1−05が格納されているため、命令I1−05の発行を決定する。この結果、命令I1−05は受信側論理回路に送出され、ポートAはアクノリッジ信号線115aにより命令の受理を通知される。この時、命令順序キュー100bは命令I1−05が削除され、命令I0−06を格納する。

【0061】

(5)サイクルt4

命令I0−07がポートDから入力される。命令順序決定回路100aは命令I0−07を、命令順序キュー100bに送出する。命令選択回路100cは、命令順序キュー100bに命令I0−06が格納されており、命令I0−07と同時に転送化のであるため、命令I0−06及び命令I0−07の発行を決定する。この結果、命令I0−06及び命令I0−07は受信側論理回路に送出され、ポートAはアクノリッジ信号線115c及び115dにより命令の受理を通知される。この時、命令順序キュー100bは命令I0−06及び命令I0−07が削除される。

【0062】

以上に示すように、送信側論理回路のポートA〜ポートDの複数のポートからデータ量が小さい命令I0が同時に出力された場合、1サイクルに2つの命令I0を受信側論理回路に送出できる。また、複数のポートから異なるサイクルに命令I0が出力された場合であっても、転送ラインを他の命令の転送に使用した結果として第1の命令I0が命令順序キュー100bで待たされ、次のサイクルでさらに命令I0が到着した場合においても、これら2つの命令I0を1サイクルで受信側論理回路に送出できる。よって、従来、命令I0は1サイクルに1命令のみしか転送できなかったが、本発明を適用することにより命令I0を1サイクルに最大2命令転送可能となる。これにより、図31の例では従来転送に7サイクル必要であった命令列を、5サイクルで転送することができる。

【0063】

以上が本発明の実施例1である。

【0064】

本実施例では、送信側論理回路から受信側論理回路に送出する命令の種類によって生じる転送データ部の空きを利用して複数の命令を1転送命令にまとめて転送し、転送データを伝送する信号線を効率良く利用することができる。

【0065】

(実施例1a)

以下に本発明の実施例1aを図28を用いて説明する。本実施例は実施例1の変形であるため、相違点についてのみ説明する。本実施例は、実施例1の調停回路100内において命令コード及び命令データをバッファリングする点のみが実施例1と異なる。

【0066】

図28に調停回路内に命令をバッファリングする調停回路の構成を示す。

【0067】

本実施例では、実施例1の送信側論理回路のポートA〜ポートDから送出される命令は、それぞれ一旦命令バッファ100f〜100iに格納される。命令の格納時に各命令バッファは対応するアクノリッジ信号線を”1”とし、命令を受理したことを送信側論理回路に伝える。ただし、命令バッファの空きが無い場合、命令を格納することができないため、命令を受理しない。

【0068】

図28の命令順序決定回路100a、命令順序キュー100b、命令選択回路100c、第1命令セレクタ100d、第2命令セレクタ100eの構成は実施例1と同じである。命令選択回路100cの出力するアクノリッジ信号線115a’〜115d’は実施例1と異なり、それぞれ命令バッファ100f〜100i内に保持された命令の発行完了を示し、命令バッファ内のエントリの削除に使用される。

【0069】

調停回路内に命令をバッファリングする構成としたことで、命令をバッファリングしない構成と比較し受信側論理回路に命令が到達するまでにかかるサイクル数が増加する。しかし、命令をバッファリングしない構成では、出力側論理回路が命令を発行してから命令の受理を行なうまでの処理を1サイクルに納めなければならないが、本構成では調停回路内の命令バッファから命令を発行し、アクノリッジ信号線115a’〜115d’を用いて命令バッファ内のエントリを削除するまでを1サイクルに納めればよい。このため、実施例1と比較してサイクル時間を短縮することができる。

【0070】

(実施例2)

以下に、本発明の第2の実施例を図4〜図5を用いて説明する。本実施例は実施例1の変形であるため、相違点についてのみ説明する。本実施例は、調停回路100及びエンコーダ102の代わりに命令コードの調停回路・エンコーダ200、命令データ上位32ビットの調停回路202、命令データ下位32ビットの調停回路203を設けた点、及び、デコーダ104の代わりに転送コードのデコーダ204を設け、転送データは調停回路202及び調停回路203の出力をそのまま命令データとして使用する点が異なる。

【0071】

図4は本発明に係る論理回路接続装置を示す。本実施例の論理回路接続装置では、送信側論理回路のポートA〜ポートDから送信される命令の命令コード部を調停回路・エンコーダ200、調停回路202及び調停回路203に、命令データ部の上位32ビットを調停回路202、命令データ部の下位32ビットを調停回路203に入力する。

【0072】

図5に送信側論理回路のポートA〜ポートDから出力される命令を示す。本実施例では、32ビットのデータ転送を行なう命令I0において、送信側論理回路が転送データを命令データ部の上位32ビット及び下位32ビットの双方に出力する点が実施例1と異なる。これにより、調停回路202は全ての命令I0の命令データ部32ビット及び全ての命令I1の命令データ部上位32ビットを受け取る。また、調停回路202は全ての命令I0の命令データ部32ビット及び全ての命令I1の命令データ部下位32ビットを受け取る。

【0073】

調停回路・エンコーダ200は、ポートA〜ポートDの命令の命令コード部を受けて、入力側論理回路に送出する命令の組を選択し、図3に示す命令の組に対応する転送コードを生成してデコーダ204に送出する。この時、選択した命令に対応するポートの命令アクノリッジ信号線215a〜215dを"1"とし、出力側論理回路に命令を出力したことを伝える。

【0074】

調停回路202は、ポートA〜ポートDの命令の命令コード部及び命令データ部の上位32ビットを受けて、命令コード部から入力側論理回路に送出する命令の組を選択し、図3に示す命令データ部を選択して、転送データ線上位260に送出する。命令I0を2つ送出する場合、調停回路202は1つ目の命令I0の命令データ部を送出し、2つ目の命令I0の命令データ部は破棄する。

【0075】

調停回路203は、ポートA〜ポートDの命令の命令コード部及び命令データ部の下位32ビットを受けて、命令コード部から入力側論理回路に送出する命令の組を選択し、図3に示す命令データ部を選択して、転送データ線下位261に送出する。命令I0を2つ送出する場合、調停回路202は2つ目の命令I0の命令データ部を送出し、1つ目の命令I0の命令データ部は破棄する。

【0076】

本実施例は、これらの調停回路・エンコーダ200、調停回路202及び調停回路203が、ポートA〜ポートDの命令の命令コード部の中から同一の方法で入力側論理回路に送出する命令の組を選択することで、それぞれが独立に動作して正しく命令を転送できる。なお、動作タイミングは同一のクロック等の入力により一致させる。

【0077】

デコーダ204は、調停回路・エンコーダ200から転送コード線を通して転送命令を受け、以下に示すように命令の組を復元し、入力側論理回路に対して発行する。

【0078】

(1)調停回路・エンコーダ200から転送命令T2を受けた場合

命令コード信号線270aを"11"とし、入力側論理回路に対して命令I1を発行する。ポートFからは命令を発行しない。

【0079】

(2)調停回路・エンコーダ200から転送命令T1を受けた場合

命令コード信号線270a及び命令コード信号線270bを"10"とし、入力側論理回路に対して命令I0を2つ発行する。

【0080】

(3)調停回路・エンコーダ200から転送命令T0を受けた場合

命令コード信号線270aを"10"とし、入力側論理回路に対して命令I0を1つ発行する。ポートFからは命令を発行しない。

【0081】

入力側論理回路は、命令コードE及び命令コードFが命令I0を示す場合はそれぞれ転送データ上位32ビット及び転送データ下位32ビットを命令データ部として使用する。命令コードEが命令I1を示す場合は、転送データ上位32ビットを命令データ上位32ビット、転送データ下位32ビットを命令データ下位32ビットとして使用する。

【0082】

以上が本発明の実施例2である。本実施例により、例えば出力側論理回路を命令コード部及び複数の命令データ部を処理する複数のLSIに分割した場合において、転送するデータ量が小さい命令は、同時に複数転送することができ、論理回路接続装置の転送性能を従来と比較し高めることができる。

【0083】

(実施例3)

以下に本発明の第3の実施例を図6を用いて説明する。本実施例は実施例1の変形であるため、相違点についてのみ説明する。本実施例は、論理回路接続装置で接続する論理回路が、命令の入力及び出力の双方を行なう点、及び、論理回路間の接続にバスを使用する点が実施例1と異なる。

【0084】

図6は本実施例に係る論理回路接続装置をユニット間の接続に適用したものを示す。

【0085】

本実施例では、転送命令の送信及び受信を行なうユニット300aと300bが、転送コードバス350と転送データバス360からなるバスに結合される。ユニット300a及び300bは、論理回路310a及び310b、調停回路・エンコーダ320a及び320b、バス調停回路340a及び340b、デコーダ330a及び330bからなる。論理回路接続装置は、調停回路・エンコーダ320a及び320b、バス調停回路340a及び340b、デコーダ330a及び330b、転送コードバス350、転送データバス360からなる。

【0086】

論理回路310a及び310bは、論理回路接続装置を介して相互に命令の入出力を行なう。論理回路310aから論理回路310bに命令を転送する場合、論理回路310aの発行する命令は、調停回路・エンコーダ320a、バス調停回路340a、転送コードバス350及び転送データバス360、バス調停回路340b、デコーダ330bを経由して論理回路310bに到達する。

【0087】

調停回路・エンコーダ320a及び320bは、論理回路310a及び310bが出力ポートA〜ポートBに出力する命令からバスに出力する命令の組を選択し、転送命令に変換する。生成した転送命令は自ユニット内のバス調停回路340a叉は340bに伝送される。論理回路310a及び310bで使用する命令の形式は、実施例1の図2の通りである。また、論理回路接続装置内で使用する転送命令の形式は、実施例1の図3の通りである。命令の組から転送命令を生成する方法は、実施例1の通りである。

【0088】

バス調停回路340a及び340bは、送信する転送命令を受けるとバス権の獲得を要求する。この時、他ユニットのバス調停回路340a叉は340bとの間でバス権を調停し、バス権を獲得したバス調停回路が受信側のバス調停回路に対して転送命令を送信する。バス権の調停には従来からラウンドロビン等の方法が提案されているが、本発明は、バス権の調停方法に係わらず有効である。

【0089】

デコーダ330a及び330bは、バス調停回路340a叉は340bが受信した転送命令を命令に復元し、論理回路310a叉は310bに出力する。転送命令から命令を復元する方法は、実施例1の通りである。

【0090】

本実施例においては、調停回路・エンコーダ320a及び320b内のバッファの有無、バス調停回路340a及び340bのバッファの有無の種々の実現方法が考えられる。経路上にバッファを設けてステージ数を増やすと命令伝達のレイテンシが増加する。一方、ステージ数を減らすとバッファ間の論理ディレイが長くなり、動作サイクルが長くなる。実施例1aに示した方法と同様の方法を用いて調停回路320a及び320b内にポートA及びポートBに対応する命令バッファを設けた場合、転送命令は命令バッファ内の命令を組み合わせて生成可能である。このため、転送命令はポートA及びポートBから異なるサイクルで出力された任意の命令の中から組み合わせることができる。バス調停回路340a及び340b内に転送命令バッファを設ければ、バス権を獲得できない場合においても転送命令バッファに空きがある限り、調停回路・エンコーダ320a叉は320bの転送命令生成を継続することができる。調停回路・エンコーダ320a及び320b、バス調停回路340a及び340b内のバッファの有無により論理回路接続装置の複数命令を転送できる可能性及びステージ数は異なるが、本実施例は各部のバッファの有無に係わらず有効である。

【0091】

以上が本発明の実施例3である。本実施例により、バスにより結合されたユニット間で、転送するデータ量が小さい命令I0は1サイクルに2つ転送することができ、論理回路接続装置の転送性能を従来と比較し高めることができる。

【0092】

(実施例4)

以下に、本発明の第4の実施例を図7〜13を用いて説明する。図7は本発明に係る論理回路接続装置を用いた並列計算機を示す。図7の並列計算機は、プロセッサノード1000a及び1000b、メモリノード1080が転送コードバス1050及び転送データバス1060からなる転送バスに接続された構成をとる。本実施例の変形として、プロセッサノード内にメモリを分散配置することも可能であるが、本発明は、いずれの構成においても有効である。

【0093】

プロセッサノード1000a及び1000b内では、それぞれプロセッサ1010a及び1010bがプロセッサバスを介して論理回路接続装置の調停回路・エンコーダ1020a及び1020b、デコーダ1030a及び1030bと接続される。調停回路・エンコーダ1020a及び1020b、デコーダ1030a及び1030bはバス調停回路1040a及び1040bと接続される。また、プロセッサ1010a及び1010bは、キャッシュメモリ1015a及び1015bとキャッシュ専用バスで接続される。

【0094】

メモリノード1080内では、メモリ1070が調停回路・エンコーダ1020c及びデコーダ1030cと接続される。調停回路・エンコーダ1020c及びデコーダ1030cは、バス調停回路1040cと接続される。

【0095】

図8に、本実施例の並列計算機における各プロセッサノード1000a及び1000b上のキャッシュ1015a及び1015bのキャッシュエントリの状態の種類を示す。

【0096】

INVALID状態(I状態)は、当該キャッシュエントリに有効なデータを保持していないことを示す。

【0097】

CLEAN状態(C状態)は、当該キャッシュエントリにメモリ1070と同じデータを保持していることを示す。複数のプロセッサノードが同一のラインをC状態でキャッシングできる。

【0098】

MODIFIED状態(M状態)は、当該キャッシュエントリに最新のデータを保持していることを示す。この時、メモリ1070上の当該ラインは古いデータを保持している。同一のラインは、並列計算機内の1つのプロセッサノードのみがM状態で保持することができ、他のプロセッサノードは当該ラインをキャッシュ上に保持できない。

【0099】

あるプロセッサ(1010aとする)がメモリを読み出すと、当該メモリラインがキャッシュエントリにキャッシングされ、このキャッシュエントリはC状態となる。この時、異なるプロセッサ(1010bとする)が同一メモリラインを読み出すと、当該メモリラインはプロセッサ1010bの対応するキャッシュエントリにキャッシングされ、キャッシュエントリはC状態となる。これにより、複数のプロセッサが読み出したデータをキャッシングすることができる。

【0100】

ここで、あるプロセッサAが当該メモリラインに書込みを行なうと、バスを介して他のプロセッサの対応するキャッシュラインを無効化し、I状態とする。そして、メモリラインを読み出しキャッシュエントリにキャッシングして、データを書き込む。この時、当該キャッシュエントリをM状態とする。他のプロセッサがM状態のキャッシュエントリに対応するメモリラインをアクセスすると、当該キャッシュエントリがメモリに書き戻されると共にメモリデータとして使用される。この動作により、全てのプロセッサのキャッシュの一貫性を保つことができる。

【0101】

図9に、本実施例の並列計算機のプロセッサ1010a及び1010b、または、メモリ1070が発行する命令の種類を示す。LD要求は、プロセッサがメモリ読み出しを行なうときに、転送バスにメモリ読み出し要求を発行する命令である。RDI要求は、プロセッサがメモリ書込みを行なうために、他のプロセッサノードの当該キャッシュラインを無効化すると共に当該キャッシュラインのデータを読み出す命令である。ライン読み出しデータは、LD要求及びRDI要求を受けて、メモリが要求を発行したプロセッサにメモリの内容を転送する命令である。WB要求は、プロセッサノードが外部からのLD要求又はRDI要求に対応するキャッシュラインをM状態で保持している時、または、自プロセッサのLD要求又はRDI要求発行時にキャッシュエントリに空きがなく、M状態のキャッシュラインを置き換える時に、プロセッサノードが当該キャッシュラインの内容をメモリに書き戻す命令である。

【0102】

本実施例では、ライン読み出しデータ及びLD要求叉はRDI要求に伴うWB要求の順序は、LD要求及びRDI要求の順序と一致する。バス調停回路1040a〜1040cは、バス上に出力された全てのLD要求及びRDI要求の発行順を記録しておき、他のバス調停回路からライン読み出しデータや対応するWB要求が発行された時に記録を消去する。当該バス調停回路がライン読み出しデータや対応するWB要求によってデータを返送する順番が来ると、バス権を獲得し、データを返送する。バス権の調停には種々の方法が存在するが、本発明は、バス権の調停方法に係わらず有効である。LD要求叉はRDI要求の順序を保証しない場合、命令の順序保証の制約によって生じる待ち時間を削減できる代わりに、各命令の対応を示すための識別子を命令に付加する必要が生じる。本発明は、命令に識別子を付加するかどうかに係わらず有効である。

【0103】

図10に、本実施例の並列計算機のプロセッサ1010aがメモリ読み出し命令(LD命令)を実行する場合の動作を示す。

【0104】

プロセッサ1010aは、LD命令実行時にキャッシュ1015aに読み出し対象データが保持されているか検査する(L1)。キャッシュ1015a内に対象データが保持されている場合、プロセッサ1010aはキャッシュ1015aから対象データを読み出し使用する(L2)。キャッシュ1015a内に対象データが保持されていない場合かつ、キャッシュ1015a内に空エントリがない場合、置き換えるキャッシュラインを決定する。置き換えるキャッシュラインがM状態の場合、WB要求を発行し、置き換えるキャッシュラインの内容をメモリに書き込む(以上L0)。キャッシュ1015a内に対象データが保持されていない場合かつキャッシュ1015a内に空エントリがある場合、または、L0の動作を行なった場合、プロセッサ1010aは転送バスに対してLD要求を発行する(L3)。

【0105】

転送バスに接続された全てのプロセッサノード1000a〜1000bとメモリ1080は、プロセッサ1010aのLD要求を受ける。全プロセッサノード上のプロセッサは、自プロセッサのキャッシュ内に対象データを含むキャッシュラインをM状態で保持しているか検査する(L4)。

【0106】

対象データがM状態で保持されている場合、M状態のキャッシュラインを保持するプロセッサはWB要求を転送バスに発行すると共に、当該キャッシュラインの状態をCLEANとする(L5)。メモリノード1080は転送バス上のWB要求を受け、WB要求対象のラインをメモリ1070に書き込む(L6)。プロセッサノード1000aは、転送バス上のWB要求を受け、WB要求対象のラインをキャッシュ1015aに書込み当該キャッシュラインの状態をCLEANにすると共に、ライン内の対象データをLD要求に対する読み出しデータとして使用する(L6)。

【0107】

L4において、全てのプロセッサノード上のキャッシュに対象データを含むM状態のキャッシュラインが存在しない場合、メモリノード1080はLD要求を受けて対象ラインを読み出し、転送バスを介してプロセッサノード1000aにライン読み出しデータを転送する(L7)。プロセッサ1010aは、ライン読み出しデータをキャッシュ1015aに書込み当該キャッシュラインの状態をCLEANにすると共に、ライン内の対象データをLD要求に対する読み出しデータとして使用する(L8)。

【0108】

図11に、本実施例の並列計算機のプロセッサ1010aがメモリ書き込み命令(ST命令)を実行する場合の動作を示す。

【0109】

プロセッサ1010aは、ST命令実行時にキャッシュ1015aに書込み対象データが保持されているか検査する(S1)。キャッシュ1015a内に対象データが保持されており、当該ラインがM状態の場合、プロセッサ1010aはキャッシュ1015aの当該ラインに対象データを書き込む(S2)。キャッシュ1015a内に対象データが保持されていない場合かつ、キャッシュ1015a内に空エントリがない場合、置き換えるキャッシュラインを決定する。置き換えるキャッシュラインがM状態の場合、WB要求を発行し、置き換えるキャッシュラインの内容をメモリに書き込む(以上S0)。キャッシュ1015a内に対象データが保持されていない場合かつキャッシュ1015a内に空エントリがある場合、または、S0の動作を行なった場合、プロセッサ1010aは転送バスに対してRDI要求を発行し、対象データを含むキャッシュラインを読み出すと共に他プロセッサノード上の当該キャッシュラインを無効化する(S3)。

【0110】

転送バスに接続された1000aを除く全てのプロセッサノードとメモリ1080は、プロセッサ1010aのRDI要求を受ける。全プロセッサノード上のプロセッサは、自プロセッサのキャッシュ内に対象データを含むキャッシュラインをM状態で保持しているか検査する(S4)。

【0111】

対象データをM状態で保持しているプロセッサはWB要求を転送バスに発行すると共に、当該キャッシュラインの状態をI状態とする(S5)。プロセッサ1010aは、転送バス上のWB要求を受けてST命令の書込みデータ部を更新し、キャッシュ1015aに書き込む。この時、キャッシュ1015aの当該キャッシュラインをM状態とする(S6)。

【0112】

S4の動作時に対象データを含むキャッシュラインをM状態で保持しているプロセッサが存在しない場合、当該キャッシュラインを保持する全プロセッサはキャッシュラインの状態をI状態に変更する(S7)。また、メモリ1070は、S3の動作時に発行されたRDI要求を受け、対象ラインを読み出す(S8)。ST命令を発行したプロセッサは、ライン読み出しデータを受けてST命令の書込みデータ部を更新し、キャッシュ1015aに書き込む。この時、キャッシュ1015aの当該キャッシュラインをM状態とする(S9)。

【0113】

図12に本実施例の並列計算機で使用する転送命令の一覧を示す。本実施例の並列計算機では、図9に示した命令のうち命令データとしてアドレス32bitのみを転送するLD要求とRDI要求を同時に転送可能とする。このため、LD要求とRDI要求の全ての組み合わせに対応する転送命令T1〜T6を用意する。WB要求は、1サイクル目にアドレス32bitを転送し、2サイクル目から5サイクル目にデータ256bitを転送する。1サイクル目の転送データ部に32bitの空きができるが、本実施例の並列計算機ではWB要求は他の命令と同時に転送しないこととし、WB要求とLD要求、RDI要求等を同時に転送する転送命令は用意しない。

【0114】

プロセッサノード2つで構成した本実施例の並列計算機において、プロセッサノード0がアドレスA0及びA1、プロセッサノード1がアドレスA2及びA3にLD要求を発行した場合の動作を図13に示す。

【0115】

時刻t0で、プロセッサノード0がアドレスA0及びA1へのLD要求を発行する。2つのLD要求は、プロセッサノード内の調停回路・エンコーダ320aで転送命令T2に変換され、1サイクルでプロセッサノード0及びメモリノードに伝送される。

【0116】

時刻t1で、プロセッサノード1がアドレスA2及びA3へのLD要求を発行する。2つのLD要求は、プロセッサノード内の調停回路・エンコーダ320bで転送命令T2に変換され、1サイクルでプロセッサノード1及びメモリノードに伝送される。

【0117】

ここでは、プロセッサノード1のキャッシュ内にアドレスA0及びA1のデータが保持されていなく、また、プロセッサノード0のキャッシュ内にアドレスA2及びA3のデータが保持されていない場合を示す。従って、プロセッサノード0及び1はキャッシュラインの書き戻しを行なわず、全LD要求に対する返答はメモリノードが行なう。

【0118】

時刻t2〜t5では、プロセッサノード0が転送バスを通してアドレスA0のLD要求に対するライン読み出しデータを受ける。

【0119】

時刻t6〜t9では、プロセッサノード0が転送バスを通してアドレスA1のLD要求に対するライン読み出しデータを受ける。

【0120】

時刻t10〜t13では、プロセッサノード1が転送バスを通してアドレスA2のLD要求に対するライン読み出しデータを受ける。

【0121】

時刻t14〜t17では、プロセッサノード0が転送バスを通してアドレスA3のLD要求に対するライン読み出しデータを受ける。

【0122】

以上が、第4の実施例である。本実施例により、バスにより結合された並列計算機において、各プロセッサノードは転送するデータ量が小さいLD要求命令およびRDI要求命令を同時に複数転送することができ、転送バスの転送性能を従来と比較し高めることができる。

【0123】

(実施例5)

以下に、本発明の第5の実施例を図14〜16を用いて説明する。本実施例は実施例4の変形であるため、相違点についてのみ説明する。本実施例は、並列計算機の各ノードを転送バスで結合する代わりにネットワークで結合することとした点、及び、命令及び転送命令に識別子を付加し、命令及び転送命令を順不同に処理できる点が実施例4と異なる。

【0124】

図14は、本発明に係る並列計算機を示す。

【0125】

プロセッサノード400a及び400b内では、それぞれプロセッサ410a及び410bがプロセッサバスを介して論理回路接続装置の調停回路・エンコーダ420a及び420b、デコーダ430a及び430bと接続される。調停回路・エンコーダ420a及び420b、デコーダ430a及び430bはネットワーク450と接続される。また、プロセッサ410a及び410bは、キャッシュメモリ415a及び415bとキャッシュ専用バスで接続される。

【0126】

メモリノード480c及び480d内では、それぞれメモリ470c及び470dが調停回路・エンコーダ420c及び420d、デコーダ430c及び430dと接続される。調停回路・エンコーダ420c及び420d、デコーダ430c及び430dは、ネットワーク450と接続される。

【0127】

本実施例では、プロセッサノード及びメモリノードの数をそれぞれ4とするが、本発明はプロセッサノード及びメモリノードの数に依存せず有効である。また、本実施例の変形として、プロセッサノード内にメモリを分散配置することも可能であるが、本発明は、いずれの構成においても有効である。

【0128】

並列計算機で使用する命令、転送命令、キャッシュの状態及び命令発行時の動作は、命令及び転送命令に識別子(ID)が付加される点を除いて実施例4と同じである。本実施例では命令の識別子として、LD要求叉はRDI要求叉は置き換えに伴うWB要求を発行したプロセッサノードの番号2ビットと、プロセッサノード内で一意に定めた発行中の要求の番号2ビットの計4ビットからなる識別子を使用する。また、転送命令の識別子は8ビットとし、上位4ビットが1つめの命令の識別子、下位4ビットが2つめの命令の識別子とする。本発明は、識別子の値の設定方法に係わらず有効である。

【0129】

図15に、ネットワーク450の内部の構造を示す。セレクタ500a〜500bは、全てのプロセッサノード及びメモリノードから転送命令を受け、これらを調停して1つの転送命令を生成し、担当するノードへ転送命令を出力する。これらのセレクタをノード毎に対応して用意することで、任意のノード間で転送命令を授受できる。

【0130】

プロセッサ410a〜410b、メモリ470c及び470dは、図9に示した命令を調停回路・エンコーダ420a〜420dに発行する。調停回路・エンコーダ420a〜420dは、プロセッサ及びメモリの発行する命令を図12に示した転送命令に変換し、ネットワーク450に発行する。ネットワーク内のセレクタ500a〜500bは、全てのノードからの転送命令を受けて、それぞれ対応するノードに出力する転送命令を生成する。

【0131】

ここでは、セレクタ500aの構造を例として説明する。各ノードから受信した転送命令は、セレクタ500a内のデコーダ520a〜520cによって命令に変換される。変換後以下に示す方法でノードに出力する命令を選択し、対応する命令バッファ525a〜525cに書き込む。

【0132】

<命令がLD要求叉はRDI要求の場合>

図9に示したように、命令の対象ノードは全てのプロセッサノード及びアクセス対象のメモリである。よって、全てのプロセッサノードに対応するセレクタ内のデコーダ、及び、命令の対象アドレスを保持するメモリノードに対応するセレクタ内のデコーダは、各々に対応する命令バッファに当該命令を書き込む。上記以外のデコーダは、当該命令を破棄する。

【0133】

<命令がライン読み出しデータ叉はRDI要求に対応するWB要求の場合>

図9に示したように、命令の対象ノードはアクセスを発行したプロセッサノード及びメモリである。よって、全デコーダは、命令の識別子から要求の送信元を得て、アクセスを発行したプロセッサノードに対応するセレクタを特定する。当該セレクタ内のデコーダは、対応する命令バッファに当該命令を書き込む。また、命令の対象アドレスを保持するメモリノードに対応するセレクタ内のデコーダは、各々に対応する命令バッファに当該命令を書き込む。上記以外のデコーダは、当該命令を破棄する。

【0134】

<命令が置き換えによるWB要求の場合>

図9に示したように、命令の対象ノードはメモリである。よって、命令の対象アドレスを保持するメモリノードに対応するセレクタ内のデコーダは、各々に対応する命令バッファに当該命令を書き込む。上記以外のデコーダは、当該命令を破棄する。

【0135】

WB要求が置き換えによる場合、WB要求の識別子中のプロセッサノード番号がWB要求の発行元となる。この基準により、WB要求が置き換えによるものであることを判断する。

【0136】

上記に示した手順により、プロセッサノード0に送出される命令が命令バッファ525a〜525cに格納される。調停回路・エンコーダ530aは、セレクタ500a内の全命令バッファ525a〜525cからプロセッサノード0に送出する命令の組を選択し、転送命令に変換してプロセッサノード0に送出する。

【0137】

ネットワーク内で各ノードが出力した転送命令を一旦命令に復元し、命令バッファに格納することで、調停回路・エンコーダ530aは複数の命令の選択時に、異なる命令バッファから選択可能となる。これにより、異なるノードを対象とする、命令が同一転送命令として到着した場合においても、各命令を対象ノードに送出できる。

【0138】

対応するノードに送出する命令を調停回路・エンコーダ530aで選択する構成も考えられる。この構成ではデコーダ520a〜520c毎に命令の送出判定を行なう回路を設けなくてもよいが、対応するノード送出しない命令についても命令バッファ525a〜525cに格納するため命令バッファ利用の効率が低下する。

【0139】

本実施例では各セレクタはデコーダを保持する構造としているが、デコーダを全てのセレクタで共通とし、ネットワーク単位で保持して、セレクタ内にはデコーダを設けない方法も可能である。

【0140】

プロセッサノード及びメモリノードをそれぞれ4つで構成した本実施例の並列計算機において、プロセッサノード0がアドレスA0及びA1、プロセッサノード1がアドレスA2及びA3、プロセッサノード2がアドレスA4及びA5、プロセッサノード3がアドレスA6及びA7にLD要求を発行した場合の動作を図16に示す。

【0141】

時刻t0で、プロセッサノード0がアドレスA0及びA1、プロセッサノード1がアドレスA2及びA3、プロセッサノード2がアドレスA4及びA5、プロセッサノード3がアドレスA6及びA7へのLD要求をそれぞれ発行する。各プロセッサノードの発行するそれぞれ2つのLD要求は、プロセッサノード内の調停回路・エンコーダ420a〜420bで転送命令T2に変換され、ネットワーク450に伝送される。ネットワーク450内の各セレクタ500a〜500b内では、各プロセッサノードから受けた転送命令T2をデコーダ520a〜520bでそれぞれ2つのLD要求に戻し、命令バッファ525a〜525bに格納する。

【0142】

時刻t1〜t4で、各セレクタ内の調停回路・エンコーダ530aは、セレクタ内の命令バッファから命令の組を選択し、各プロセッサノード及びメモリノードへ出力する。図16では、各セレクタは時刻t1でアドレスA0及びA2へのLD命令、時刻t2でアドレスA4及びA6へのLD命令、時刻t3でアドレスA1及びA3へのLD命令、時刻t4でアドレスA5及びA7へのLD命令を選択し、各プロセッサノード及びメモリノードへ送出している。

【0143】

ここでは、プロセッサノード1のキャッシュ内にアドレスA0、A1のデータが保持されていなく、また、プロセッサノード0のキャッシュ内にアドレスA2、A3のデータが保持されていない場合を示す。従って、プロセッサノード0及び1はキャッシュラインの書き戻しを行なわず、全LD要求に対する返答はメモリノードが行なう。

【0144】

また、アドレスA0及びA2及びA4及びA6、アドレスA1及びA3及びA5及びA7の各組は異なるメモリノード上のアドレスであり、各メモリノードが同時にネットワークに対して対応するライン読みだしデータ発行できる場合を示す。

【0145】

時刻t5〜t8では、プロセッサノード0がアドレスA0のLD要求に対するライン読み出しデータを受け、プロセッサノード1がアドレスA2のLD要求に対するライン読み出しデータを受け、プロセッサノード2がアドレスA4のLD要求に対するライン読み出しデータを受け、プロセッサノード3がアドレスA6のLD要求に対するライン読み出しデータを受ける。

【0146】

時刻t9〜t12では、プロセッサノード0がアドレスA1のLD要求に対するライン読み出しデータを受け、プロセッサノード1がアドレスA3のLD要求に対するライン読み出しデータを受け、プロセッサノード2がアドレスA5のLD要求に対するライン読み出しデータを受け、プロセッサノード3がアドレスA7のLD要求に対するライン読み出しデータを受ける。

【0147】

以上が本発明の第5の実施例である。図16の動作例では、2つのLD要求を1サイクルで転送することにより、時刻t0〜t4の間の動作で動作サイクル数が5サイクル削減できる。本実施例により、ネットワークにより結合された並列計算機において、各ノード及びネットワークは転送するデータ量が小さいLD要求命令およびRDI要求命令を1サイクルに最大2つ転送することができる。これにより、ネットワークの処理性能を従来と比較し高めることができる。

【0148】

<実施例6>

以下に、本発明の第6の実施例を図17〜19を用いて説明する。本実施例は実施例5の変形であるため、相違点についてのみ説明する。本実施例は、並列計算機の各ノードからネットワークに送出する信号線を命令コード及び命令データに変更した点、及び、ネットワークを命令コード部及び命令データ部上位32ビットを処理するネットワーク上位部分、及び、命令データ部下位32ビットを処理するネットワーク下位部分に分割した点が実施例5と異なる。

【0149】

図17は、本発明に係る並列計算機を示す。図17は実施例5における図14の変形であり、変更点のみを説明する。実施例5では、プロセッサ及びメモリの発行する命令は、調停回路・エンコーダ420a〜420dで転送コード及び転送データに変更され、ネットワーク450に送出される。これに対し、本実施例では、プロセッサ及びメモリの発行する命令は、ネットワークインターフェイス720a〜720dを介して命令コード及び命令データとしてネットワーク750に送出される。

【0150】

図18は、本発明に係る並列計算機のネットワークの構造を示す。ネットワーク750は、ネットワーク上位部分602aとネットワーク下位部分602bからなる。ネットワーク上位部分602aは、各ノードの出力する命令コード、命令データ上位32ビット及び命令IDを受け、転送コード、転送データ上位32ビット及び転送ID上位4ビットを各ノードに送出する。ネットワーク下位部分602bは、各ノードの出力する命令データ下位32ビット及び命令IDを受け、転送データ下位32ビット及び転送ID下位4ビットを各ノードに送出する。

【0151】

セレクタ600a〜600dは、全てのプロセッサノード及びメモリノードから命令を受け、これらを調停して1つの転送命令を生成し、転送コード及び転送データ上位32ビット、または、転送データ下位32ビットのいずれか担当部分を対応するノードへ出力する。

【0152】

各ノードからネットワークに送出する命令の種類は図9の通りである。ただし、LD要求及びRDI要求の発行時には、ネットワークインターフェイス720a〜720dは命令データの上位32ビットと下位32ビットに同一アドレスを出力する点が異なる。

【0153】

並列計算機で使用する転送命令、キャッシュの状態及び命令発行時の動作は実施例5と同じである。

【0154】

ネットワーク上位部分602aのセレクタ600a〜600bの構造を、セレクタ600aを用いて説明する。各ノードからセレクタ600aに発行された命令コード及び命令データ上位32ビットは、命令バッファ625a〜625bに格納される。調停回路・エンコーダ630aは、セレクタ600a内の全命令バッファ625a〜625bからプロセッサノード0に送出する命令の組を選択し、転送命令に変換して転送コード及び転送データ上位32ビットをプロセッサノード0に送出する。複数の命令を選択する場合、異なる命令バッファから選択することができる。調停回路・エンコーダ630aにおける送出命令の選択方法は、実施例5のデコーダの動作と同様である。

【0155】

ネットワーク下位部分602bのセレクタ600c〜600dの構造を、セレクタ600cを用いて説明する。各ノードからセレクタ600cに発行された命令コード及び命令データ下位32ビットは、命令バッファ625c〜625dに格納される。調停回路630bは、セレクタ600b内の全命令バッファ625c〜625dからプロセッサノード0に送出する命令の組を選択し、転送命令に変換して転送データ下位32ビットをプロセッサノード0に送出する。複数の命令を選択する場合、異なる命令バッファから選択することができる。調停回路・エンコーダ630bにおける送出命令の選択方法は、実施例5のデコーダの動作と同様である。

【0156】

調停回路・エンコーダ600a〜600bにおける命令の組の選択は、ネットワーク上位側及びネットワーク下位側で同一のアルゴリズムで行なう。命令の組の選択アルゴリズムは任意の方法が使用可能であり、本実施例では説明しない。

【0157】

図19は、プロセッサノードAから受けたアドレスA0のLD要求と、プロセッサノードBから受けたアドレスB0のLD要求の2命令を選択し、転送命令に変換してプロセッサノード0に送出する動作を示す。

【0158】

プロセッサノードAは、命令コードにLD要求を示す"100"、命令データ上位32ビット及び命令データ下位32ビットの双方にアドレスA0、命令IDを出力する。プロセッサノードBは、命令コードにLD要求を示す"100"、命令データ上位32ビット及び命令データ下位32ビットの双方にアドレスB0、命令IDを出力する。図19は、プロセッサノードA及びBのLD要求が命令バッファ625a−1〜625d−1に格納された状態を示す。ネットワーク上位のセレクタ600a−1内の調停回路・エンコーダ630a−1は、プロセッサノード0に送出する命令の組をアドレスA0及びアドレスB0へのLD要求と決定し、転送コードにT2、転送データ上位32ビットに1番目の命令の命令データであるアドレスA0、転送ID上位4ビットに1番目の命令の命令IDを出力する。出力後、命令バッファ625a−1及び命令バッファ625b−1からアドレスA0及びB0へのLD要求を取り除く。一方、ネットワーク下位のセレクタ600c−1内の調停回路630b−1は、プロセッサノード0に送出する命令の組を、調停回路・エンコーダ630a−1と同一の方法を用いてアドレスA0及びアドレスB0へのLD要求と決定し、転送データ下位32ビットに2番目の命令の命令データであるアドレスB0、転送ID下位4ビットに2番目の命令の命令IDを出力する。出力後、命令バッファ625c−1及び命令バッファ625d−1からアドレスA0及びB0へのLD要求を取り除く。

【0159】

本実施例の動作は、実施例5と比較し、各ノードからネットワークには同一サイクルで複数の命令を転送できない点が異なる。プロセッサノード及びメモリノードをそれぞれ4つで構成した本実施例の並列計算機において、プロセッサノード0がアドレスA0及びA1、プロセッサノード1がアドレスA2及びA3、プロセッサノード2がアドレスA4及びA5、プロセッサノード3がアドレスA6及びA7にLD要求を発行した場合、図16の時刻t0における2つのLD要求の同時転送が実行できない。従って、実施例5と比較し動作サイクルが1サイクル長くなる。

【0160】

以上が本発明の第6の実施例である。本実施例により、ネットワークにより結合された並列計算機において、ネットワークは転送するデータ量が小さいLD要求命令およびRDI要求命令を1サイクルに最大2つ転送することができる。これにより、ネットワークの処理性能を従来と比較し高めることができる。また、データ幅を分割した複数のユニットでネットワークを構成することで、ネットワークを構成するLSIのピン数を削減できる。

【0161】

(実施例7)

以下に、本発明の第7の実施例を図20〜図22を用いて説明する。本実施例は実施例1の変形であるため、相違点についてのみ説明する。本実施例は、調停回路及びデコーダにそれぞれ直前上位データレジスタを設け、命令データ部上位が直前に転送した命令データ部上位と等しい命令を複数同時に入力側論理回路に転送できる点が実施例1と異なる。

【0162】

図20は、本実施例に係る論理回路接続装置を示す。図20は実施例1における図1の変形であり、変更点のみを説明する。

【0163】

本実施例では、調停回路800及びデコーダ804のそれぞれに直前上位データレジスタ806及び808を付加する。本実施例では全ての命令が64ビットであり、命令データ部の上位32ビットが直前に転送した命令の命令データ部上位32ビットと等しい場合に命令データ部の上位32ビットを省略し、命令データ部の下位32ビットのみを転送する。直前上位データレジスタ806は、調停回路800側で直前に転送した命令の命令データ部上位32ビットを保持する。調停回路800は、転送する命令の選択時に各命令データ部の上位32ビットと直前上位データレジスタ806の一致確認を行なう。直前上位データレジスタ808は、デコーダ804側で直前に受信した命令の命令データ部上位32ビットを保持する。デコーダ804は、命令データ部上位32ビットを省略した命令を受信した時に、直前上位データレジスタ808の値を命令データ部上位32ビットとして用いる。直前上位データレジスタの初期値は双方とも同じ値とし、誤動作を防ぐ。

【0164】

図21に図20の論理回路接続装置で使用する命令を示す。

【0165】

命令コード部が"00"の場合、命令を発行しないことを示す。命令I0は、64ビットのデータを伝送する命令であり、命令コード部は"10"である。この命令は、命令データ部の上位32ビットが以前の命令と同一である可能性が高い命令である。例えば、計算機におけるアドレスを指定する信号線は、参照の局所性があるためアドレス上位が同一である可能性が高い。命令I1は、64ビットのデータを伝送する命令であり、命令コード部は"11"である。

【0166】

図22に図20の論理回路接続装置で使用する転送命令を示す。

【0167】

転送コード部が"00"の場合、転送命令を発行しないことを示す。転送命令T0は、命令I0を1つ伝送する転送命令であり、転送コード部は"01"、転送データ部は命令I0の命令データ部とする。転送命令T1は、命令I0を2つ伝送する転送命令であり、転送コード部は"10"、転送データ部は64ビットの内上位32ビットが1つ目の命令I0の命令データ部下位32ビット、転送データ部下位32ビットは2つ目の命令I0の命令データ部下位32ビットとする。この転送命令は、転送する2つの命令I0の命令データ部上位32ビットが直前アドレスレジスタ806と等しい場合にのみ使用される。転送命令T2は、命令I1を1つ伝送する転送命令であり、転送コード部は"11"、転送データ部は命令I1の命令データ部とする。

【0168】

本実施例は、出力側論理回路から入力側論理回路に対して同一サイクルに伝送する命令数を、命令データ部の一部が直前に転送した命令と等しい場合に増やすことができる点に特長がある。

【0169】

本実施例の論理回路接続装置の動作の、実施例1に対する変更点を以下に示す。

【0170】

<調停回路の動作>

調停回路800は、以下のいずれかに該当する命令の組をポートA〜ポートDから選択し、エンコーダ802に出力する。

【0171】

(1)命令I1を1つ選択

選択した命令を、選択命令ライン1を用いてエンコーダ802に出力する。

【0172】

選択命令ライン2の命令コード信号線830bは"00"として、選択命令ライン2には命令を出力しない。

【0173】

(2)命令I0を2つ選択

2つの命令I0の命令データ部上位32ビットが、直前上位データレジスタ806とそれぞれ等しい場合にのみ選択可能である。選択した命令を、選択命令ライン1及び選択命令ライン2を用いてエンコーダ802に出力する。

【0174】

(3)命令I0を1つ選択

選択した命令を、選択命令ライン1を用いてエンコーダ802に出力する。

【0175】

選択命令ライン2の命令コード信号線830bは"00"として、選択命令ライン2には命令を出力しない。

【0176】

(4)命令を選択しない

命令コード信号線830a、830bとも"00"として、選択命令ライン1及び選択命令ライン2には命令を出力しない。

【0177】

(1)から(3)の場合、選択した命令に対応するポートの命令アクノリッジ信号線を"1"とし、出力側論理回路に当該ポートの命令を出力したことを伝える。また、命令I0を選択した場合、直前上位アドレスレジスタ806に命令I0の命令データ部上位32ビットの値を書き込む。

【0178】

<エンコーダの動作>

エンコーダ802は、調停回路800から選択命令ライン1及び選択命令ライン2を通して命令の組を受け、以下に示すように転送命令を生成し、デコーダ804に対して発行する。

【0179】

(1)調停回路800から命令I1を1つ受けた場合

転送コード信号線850を"11"、転送データ信号線160を命令データ信号線840aの値とし、転送命令T2をデコーダに対して発行する。

【0180】

(2)調停回路800から命令I0を2つ受けた場合

転送コード信号線850を"10"、転送データ信号線860の上位32ビットを信号線840a上の命令データ下位32ビットの値、転送データ信号線860の下位32ビットを信号線840b上の命令データ下位32ビットの値とし、転送命令T1をデコーダに対して発行する。

【0181】

(3)調停回路800から命令I0を1つ受けた場合

転送コード信号線850を"01"、転送データ信号線860を命令データ信号線840aの値とし、転送命令T0をデコーダに対して発行する。

【0182】

(4)調停回路800から命令を受けなかった場合

転送コード信号線850を"00"とし、転送命令を発行しない。

【0183】

<デコーダの動作>

デコーダ804は、エンコーダ802から転送ラインを通して転送命令を受け、以下に示すように命令の組を復元し、入力側論理回路に対して発行する。

【0184】

(1)エンコーダ802から転送命令T2を受けた場合

命令コード信号線870aを"11"、命令データ信号線880aを転送データ信号線860の値とし、入力側論理回路に対して命令I1を発行する。命令コード信号線870bは"00"とし、ポートFからは命令を発行しない。

【0185】

(2)エンコーダ802から転送命令T1を受けた場合

命令コード信号線870a及び命令コード信号線870bを"10"、直前上位データレジスタ808の値を命令データ信号線880a及び880bの上位32ビット、命令データ信号線880aの下位32ビットを信号線860の上位32ビット、命令データ信号線880bの下位32ビットを信号線860の下位32ビットとし、入力側論理回路に対して命令I0を2つ発行する。

【0186】

(3)エンコーダ802から転送命令T0を受けた場合

命令コード信号線870aを"10"、命令データ信号線880aを転送データ信号線860の値とし、入力側論理回路に対して命令I0を発行する。命令コード信号線870bは"00"とし、ポートFからは命令を発行しない。この時、命令データ部上位32ビットの値を直前上位データレジスタ808に書き込む。

【0187】

以上が本発明の実施例7である。

【0188】

本実施例により、データ部上位32ビットが直前の命令I0と同一である可能性の高い命令を同時に複数転送することが可能となり、論理回路接続装置の転送性能を従来と比較し高めることができる。

【0189】

(実施例8)

以下に本発明の第8の実施例を図23〜26を用いて説明する。図23は本発明にかかる論理回路接続装置を用いた計算機を示す。図23の計算機は、バスアービタ970によりバス権の調停を受けるノード900a〜900dが、転送コードバス950及び転送データバス960a〜960dに接続された構成をとる。本実施例の変形として、プロセッサとメモリを異なるノードに配置する構成も可能であるが、本発明はいずれの構成においても有効である。

【0190】

ノード900a〜900dの構成を、ノード900aを例に説明する。ノード900a内では、プロセッサ910a及びメモリ918aがプロセッサバスを介して論理回路接続装置の調停回路・エンコーダ920a、デコーダ930aと接続される。調停回路・エンコーダ920a及びデコーダ930aは、バスインターフェイス940aを介して2ビットの転送コードバス950及び128ビットの転送データバス960a〜960dと接続される。プロセッサ910aは、キャッシュメモリ915aとキャッシュ専用バスで接続される。ここでは、ノード内のプロセッサ数及びメモリ数は1としたが、本発明はノード内のプロセッサ数及びメモリ数に係わりなく有効である。

【0191】

図24は、本実施例の計算機で使用する命令を示す。図24の命令の種類は、実施例4における図9と同一である。本実施例では、計算機で使用するアドレスを30ビットとする。アドレスとデータ双方の転送を伴うライン読出データ及びWB要求では、いずれか1ノードが転送バスを占有し、転送を行なう。アドレスのみの転送であるLD要求及びRDI要求では、ノード0(900a)は転送データバス0、ノード1(900b)は転送データバス1、ノード2(900c)は転送データバス2、ノード3(900d)は転送データバス3をそれぞれ使用し、全てのノードが同時にアドレスの転送を行なう。この時、転送データ部の上位2ビットで各ノードが発行する命令の種類を伝送する。

【0192】

バスアービタ970の機能を図25及び図26を用いて説明する。各ノード900a〜900dは、命令発行を行なう前にバスアービタ970にバス要求を発行し、バス使用の許可を得る。図25は、各ノードがバスアービタ970に発行するバス要求の種類を示す。バス要求は、ライン読出データ叉はWB要求を発行する為のバス要求"10"と、LD要求叉はRDI要求を発行する為のバス要求"11"の2種類が存在する。バスアービタ970は、各ノードからのバス要求を受けてバス権の調停を行い、図26に示す3ビットのバス許可信号を全ノード900a〜900dに発行する。バス許可信号の最上位ビットが"0"の場合、いずれか1ノードのライン読出データ叉はWB要求の発行が許可される。この時、バス許可信号の下位2ビットはバス使用が許可されたノードの番号を示す。バス許可信号の最上位ビットが"1"の場合、全ノードに対してLD要求叉はRDI要求の発行が許可される。この時、全てのノード900a〜900dは、自ノードに対応する転送データバスのフィールドを使用してLD要求叉はRDI要求を発行してよい。バス許可信号の下位2ビットは、各ノード900a〜900dの発行する命令を処理する順序を示す。例えば、バス許可信号が"100"の場合、全ノード900a〜900dは、ノード0の命令-ノード1の命令-ノード2の命令-ノード3の命令の順序で命令を処理する。バスアービタは、ライン読出データ及びWB要求に対して"000"〜"011"のバス許可信号を、LD要求及びRDI要求に対して"100"〜"111"を均等に使用し、バス権の偏りを防ぐ。

【0193】

バス許可"000"〜"011"を受けてライン読出データ叉はWB要求を発行するノードは、転送コードバス950と転送データバス960a〜960dの全てに命令コード及び命令データを送出する。この時、他のノードは転送コードバス及び転送データバスに信号を送出しない。バス許可"100"〜"111"を受けた時、全てのノードは転送データバスの対応するフィールドに命令データを送出する。この時、バスアービタが転送コードバスに命令を送出し、全てのノードは転送コードバスに信号を送出しない。

【0194】

計算機の命令の転送以外の部分に関する動作は実施例4と同様である。

【0195】

以上が、本発明の第8の実施例である。本実施例により、バスにより結合された計算機において、転送するデータ量が小さいLD要求及びRDI命令を全ノードが同時に転送バスに発行することができ、転送バスの転送性能を従来と比較し高めることができる。

【0196】

【発明の効果】

本発明によれば、出力側論理回路から入力側論理回路にトランザクション(命令)を伝送する論理回路接続装置において、トランザクションの種類により生じる命令データ転送時の空きビットを利用して複数のトランザクションを伝達し、論理回路接続装置の転送性能を向上することができる。

【図面の簡単な説明】

【図1】本発明の実施例1に係る論理回路接続装置の図である。

【図2】本発明の実施例1に係る論理回路接続装置で伝送する命令を示す図である。

【図3】本発明の実施例1に係る論理回路接続装置で使用する転送命令を示す図である。

【図4】本発明の実施例2に係る論理回路接続装置の図である。

【図5】本発明の実施例2に係る論理回路接続装置で伝送する命令を示す図である。

【図6】本発明の実施例3に係る論理回路接続装置の図である。

【図7】本発明の実施例4に係る計算機の図である。

【図8】本発明の実施例4に係る計算機で使用するキャッシュ状態を示す図である。

【図9】本発明の実施例4に係る計算機で使用する命令を示す図である。

【図10】本発明の実施例4に係る計算機において、プロセッサがメモリ読み出しを行なう動作の流れを示す図である。

【図11】本発明の実施例4に係る計算機において、プロセッサがメモリ書込みを行なう動作の流れを示す図である。

【図12】本発明の実施例4に係る計算機で使用する転送命令を示す図である。

【図13】本発明の実施例4に係る計算機の動作タイミングを示す図である。

【図14】本発明の実施例5に係る計算機の図である。

【図15】本発明の実施例5に係るネットワークの構造を示す図である。

【図16】本発明の実施例5に係る計算機の動作タイミングを示す図である。

【図17】本発明の実施例6に係る計算機の図である。

【図18】本発明の実施例6に係るネットワークの構造を示す図である。

【図19】本発明の実施例6に係るネットワークの動作を示す図である。

【図20】本発明の実施例7に係る論理回路接続装置の図である。

【図21】本発明の実施例7に係る論理回路接続装置で使用する命令を示す図である。

【図22】本発明の実施例7に係る論理回路接続装置で使用する転送命令を示す図である。

【図23】本発明の実施例8に係る計算機の図である。

【図24】本発明の実施例8に係る計算機で使用する命令を示す図である。

【図25】本発明の実施例8に係る計算機で使用するバス要求信号の種類を示す図である。

【図26】本発明の実施例8に係る計算機で使用するバス使用許可信号の種類を示す図である。

【図27】図1の調停回路の構成を示す図である。

【図28】図1の調停回路の他の構成を示す図である。

【図29】図1のエンコーダの構成を示す図である。

【図30】図1のデコーダの構成を示す図である。

【図31】図1の論理接続回路の動作を示す図である。

【符号の説明】

100、202、203、310a〜310b、630b、800…調停回路、200、320a〜320b、1020a〜1020c、1030a〜1030c、1040a〜1040c、420a〜420d、530a、630a、630a−1〜630b−1、920a…調停回路・エンコーダ、 102、802…エンコーダ、 104、204、330a〜330b、430a〜430d、520a〜520c、730a〜730d、930a…デコーダ、 300a〜300b、900a〜900d…ノード、 340a〜340b、1040a〜1040c…バス調停回路、 350、1050、950…転送コードバス、360、1060…転送データバス、 960a…転送データバス0、 960b…転送データバス1、 960c…転送データバス2、 960d…転送データバス3、 970…バスアービタ、 1000a〜1000b、400a〜400b、700a〜700b…プロセッサノード、 1080、480c〜480d、780c〜780d…メモリノード、 1010a〜1010b、410a〜410b、710a〜710b、910a…プロセッサ、 1015a〜1015b、415a〜415b、715a〜715b、915a…キャッシュ、 1070、470c〜470d、770c〜770d、918a…メモリ、450、750…ネットワーク、 500a〜500b、600a〜600d、600a−1、600c−1…セレクタ、 525a〜525c、625a〜625d、625a−1〜625d−1…命令バッファ、 720a〜720d…ネットワークインターフェイス、 602a…ネットワーク上位部、 602b…ネットワーク下位部、 806、808…直前上位データレジスタ、 940a…バスインターフェイス、 110a〜110d、130a〜130b、170a〜170b、210a〜210d、270a〜270b、810a〜810d、830a〜830b、870a〜870b…命令コード信号線、 120a〜120d、140a〜140b、180a〜180b、820a〜820d、840a〜840b、880a〜880b…命令データ信号線、 220a〜220d…命令データ上位信号線、 221a〜221d…命令データ下位信号線、 115a〜115d、215a〜215d、815a〜815d…命令アクノリッジ信号線、 150、250、850…転送コード信号線、 160、860…転送データ信号線、 260…転送データ上位信号線、 261…転送データ下位信号線。

Claims (6)

- 1以上の出力側論理回路が発行する異なるデータ長を持つ2種類以上の命令を、1以上の入力側論理回路に送出する論理回路接続装置において、

命令は、命令の種類を示す命令コード部と、命令に伴うデータを示す命令デタ部からなり、

出力側論理回路から入力側論理回路に送出する時に使用する転送命令は、転送命令の種類を示す転送コード部と、転送命令に伴うデータを示す転送データ部からなり、

前記論理回路接続装置は、各出力側論理回路が発行する1以上の命令の命令コード部を受けて、転送命令に変換して入力側論理回路に一度に送出できる1以上の命令の組を選択し、該命令の組に対応した転送コード部を生成する調停回路・エンコーダと、

前記各出力側論理回路が発行する1以上の命令の命令コード部及び命令データ部の一部分をそれぞれ受けて、前記転送命令の転送データを構成する複数のデータ部分の各々を、前記各出力側論理回路が発行する命令の命令データ部の一部分からの選択によりそれぞれ決定する複数の調停回路と、

前記調停回路・エンコーダ及び複数の調停回路から転送される転送命令を受けて出力側論理回路が発行した命令の組を復元するデコーダを備えることを特徴とする論理接続装置。 - 出力側論理回路は、n個を同時に転送可能な命令の発行時に、出力側論理回路から論理回路接続装置への命令発行ポートに、命令データ部をn個に分割した複数のフィールドに発行する命令のデータを出力して調停回路・エンコーダまたは調停回路に伝送し、

調停回路・エンコーダは、各命令発行ポートからの命令の中から入力側論理回路に出力する1以上の命令の組を選択し、これに対応する転送コードを入力側論理回路に向けて出力し、

調停回路は、各命令発行ポートからの命令の中から入力側論理回路に出力する1以上の命令の組を選択し、これらに対応する転送データ部から自調停回路の担当する部分を入力側論理回路へと出力し、

デコーダは、調停回路・エンコーダから受けた転送コードを受けて出力側論理回路が発行した命令の組を復元してこれらの命令コードを入力側論理回路へと出力することで、

前記出力回路側は、前記論理回路接続装置を介して、命令の種類により異なる個数の命令を同一サイクルで前記入力側論理回路に送出可能であることを特徴とする請求項1に記載の論理回路接続装置。 - 前記調停回路及びデコーダに直前に転送した命令の一部のフィールドを記憶するレジスタを設け、

前記調停回路は後続命令の選択時に前記レジスタと命令の当該フィールドを比較して、同一のフィールドを持つ命令の転送時に当該フィールドを省略した転送命令を利用することで転送ビット数を削減して同時に転送可能な命令数を増やし、

前記デコーダは、命令のフィールドを省略した転送命令の受信時に、デコーダ側の前記レジスタの値をフィールド値として使用することで転送された命令の組を復元することを特徴とする請求項1に記載の論理回路接続装置。 - 前記転送命令をバスを介して伝送する請求項1に記載の論理回路接続装置。

- 前記出力側論理回路は、前記論理回路接続装置に出力する命令を格納するバッファを備えることを特徴とする請求項1に記載の論理回路接続装置。

- 前記命令の種類は、命令のデータ長の違いであることを特徴とする請求項1に記載の論理回路接続装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP07307297A JP3713876B2 (ja) | 1997-03-26 | 1997-03-26 | 論理回路接続装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP07307297A JP3713876B2 (ja) | 1997-03-26 | 1997-03-26 | 論理回路接続装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH10269190A JPH10269190A (ja) | 1998-10-09 |

| JP3713876B2 true JP3713876B2 (ja) | 2005-11-09 |

Family

ID=13507770

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP07307297A Expired - Fee Related JP3713876B2 (ja) | 1997-03-26 | 1997-03-26 | 論理回路接続装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3713876B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4679601B2 (ja) * | 2008-04-16 | 2011-04-27 | エヌイーシーコンピュータテクノ株式会社 | パケット制御回路、パケット処理装置、および、パケット処理方法 |

-

1997

- 1997-03-26 JP JP07307297A patent/JP3713876B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JPH10269190A (ja) | 1998-10-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CA2051222C (en) | Consistent packet switched memory bus for shared memory multiprocessors | |

| US7120755B2 (en) | Transfer of cache lines on-chip between processing cores in a multi-core system | |

| CA2051029C (en) | Arbitration of packet switched busses, including busses for shared memory multiprocessors | |

| US5265235A (en) | Consistency protocols for shared memory multiprocessors | |

| KR100360064B1 (ko) | 고도로파이프라인된버스구조 | |

| JP3832833B2 (ja) | 情報処理方法および装置 | |

| US5919254A (en) | Method and apparatus for switching between source-synchronous and common clock data transfer modes in a multiple processing system | |

| TW417047B (en) | Method for increasing efficiency in a multi-processor system and multi-processor system with increased efficiency | |

| CA2068580A1 (en) | Scientific visualization system | |

| KR980010805A (ko) | 범용 컴퓨터 구조용 프로세서 서브시스템 | |

| CN105095254B (zh) | 一种实现数据一致性的方法及装置 | |

| CA2051209C (en) | Consistency protocols for shared memory multiprocessors | |

| CN112955876B (zh) | 用于在数据处理网络中传输数据的方法和装置 | |

| KR980010806A (ko) | 각종 프로세서와 버스 프로토콜에 적응 가능한 범용 구조를 제공하는 컴퓨터 시스템 | |

| WO1998032063A2 (en) | Method and apparatus for zero latency bus transactions | |

| US6892283B2 (en) | High speed memory cloner with extended cache coherency protocols and responses | |

| US20040111576A1 (en) | High speed memory cloning facility via a source/destination switching mechanism | |

| US20040111575A1 (en) | Dynamic data routing mechanism for a high speed memory cloner | |

| EP1367499A1 (en) | Compute node to mesh interface for highly scalable parallel processing system | |

| US8359419B2 (en) | System LSI having plural buses | |

| KR980010804A (ko) | 프로세서와 고성능 시스템 버스간의 신호처리 프로토콜 변환 장치 | |

| US7043612B2 (en) | Compute node to mesh interface for highly scalable parallel processing system and method of exchanging data | |

| US5586274A (en) | Atomic operation control scheme | |

| JP3713876B2 (ja) | 論理回路接続装置 | |

| US7502917B2 (en) | High speed memory cloning facility via a lockless multiprocessor mechanism |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040322 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040322 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20040322 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050106 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050308 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050509 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050802 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050815 |

|

| LAPS | Cancellation because of no payment of annual fees |