JP3681523B2 - Optical evaluation apparatus, optical evaluation method, semiconductor device manufacturing apparatus, and semiconductor device manufacturing apparatus management method - Google Patents

Optical evaluation apparatus, optical evaluation method, semiconductor device manufacturing apparatus, and semiconductor device manufacturing apparatus management method Download PDFInfo

- Publication number

- JP3681523B2 JP3681523B2 JP30380897A JP30380897A JP3681523B2 JP 3681523 B2 JP3681523 B2 JP 3681523B2 JP 30380897 A JP30380897 A JP 30380897A JP 30380897 A JP30380897 A JP 30380897A JP 3681523 B2 JP3681523 B2 JP 3681523B2

- Authority

- JP

- Japan

- Prior art keywords

- light

- reflectance

- semiconductor region

- measurement light

- excitation light

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Testing Or Measuring Of Semiconductors Or The Like (AREA)

- Drying Of Semiconductors (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、半導体装置の製造工程におけるインラインでの特性の評価に適した光学的評価装置,光学的評価方法,半導体装置の製造装置,半導体装置の製造装置の管理方法に関する。

【0002】

【従来の技術】

近年、半導体集積回路の高集積化が大きく進展してきており、MOS型半導体装置においても、トランジスタ素子の微細化・高性能化が図られているが、特にトランジスタ素子の微細化に伴って、信頼性の高いMOSデバイスの実現が必要となってきた。MOSデバイスの信頼性の向上のためには、MOSデバイスを構成する各部が高い信頼性を有することが必要である。

【0003】

かかるMOSデバイスの信頼性を左右する重要な部分として、例えばコンタクト窓の形成方法によって影響を受けるコンタクト部の信頼性が挙げられる。コンタクト窓の形成に使用されるドライエッチングによって生じる半導体基板のダメージ層は、ドライエッチング後のウエットエッチングによって除去されるが、その除去量を適正に判断するために、従来は、製品にはならないモニターウエハ等を用いてその電気的特性を測定することにより、当該ドライエッチング条件下で生じるダメージ層の深さ等を把握したり、この電気的特性の測定結果からダメージ層を除去するためのウエットエッチングの時間や温度等の条件を設定している。このようにして、従来の半導体装置の製造方法では、モニターウエハを用いて得られた電気的特性に基づいて、半導体装置の製造工程中の加工条件が適正になるように制御している。

【0004】

また、半導体デバイスの各要素を形成するためのプロセスの中でも、例えば不純物導入技術は半導体デバイスの動作特性を決定する重要な工程である。不純物導入は、イオン注入法つまりイオンを電界により加速して半導体基板や電極等の中に不純物イオンを入り込ませる方法が主流である。その際、通常、数10keVのエネルギーで不純物イオンを加速して半導体基板等の中にイオンを注入する。しかし、この不純物イオンの注入の結果、半導体基板等の表面層には結晶性の崩れたダメージ層が生じており、また、不純物がキャリアとして活性化されておらず、かつ不純物の濃度分布も所望の分布状態にはなっていない。そこで、不純物の活性化,ダメージの回復,プロファイルの最適化のために、イオン注入後に熱処理(アニール)を行っている。従来、このアニールプロセス時間、温度などは、設計(デバイスシミュレーション)や条件の最適化により決定されており、基本的には、経験に基づいたアニール条件設定がなされていた。特に、半導体基板の表面欠陥層の回復のためのアニール処理は、経験に基づいていた。

【0005】

次に、MOSデバイスに用いられるゲート絶縁膜に関しては、その薄膜化が急速に進み、21世紀には4nm以下の非常に薄い絶縁膜が用いられることが予想されている。このような極薄の絶縁膜を有するMOSデバイスにおいては、絶縁膜の特性がMOSデバイス全体の特性さらには半導体集積回路全体の電気特性を決定するといわれるほどであり、絶縁膜の特性がとりわけ重要視されている。

【0006】

かかるゲート絶縁膜の特性は、従来、MOSキャパシタあるいはMOSトランジスタを形成し、電気的特性の評価により管理されていた。かかる電気的特性の評価は、MOSデバイスの製造途中あるいはMOSデバイスの製造後に、MOSデバイスを搭載したウエハをチャンバから取り出して行われる。

【0007】

【発明が解決しようとする課題】

ところで、上述のようなMOSデバイスの微細化等に伴い、以上のエッチング工程,不純物導入工程、ゲート絶縁膜形成工程において、上記従来のような評価方法では、以下のような問題があった。

【0008】

まず、エッチング工程においては、以下の問題がある。コンタクト窓の平面サイズ(横方向のサイズ)が縮小する一方、コンタクト窓の深さは浅くはならず、結果として、アスペクト比(=深さ/横方向のサイズ)は増大している。そして、このような高いアスペクト比を有するコンタクト窓を形成するために、例えばドライエッチング工程では、高真空・高密度プラズマが利用されている。高真空・高密度プラズマプロセスでは、高いエネルギーを有し方向性の揃ったイオンを利用して、深いコンタクト窓の形成を実現している。しかるに、高いエネルギーを有するイオンの衝撃により、従来のような比較的低真空・低密度プラズマによるドライエッチングによって生じる欠陥のレベルとは異なり、コンタクトの底において半導体結晶に生じるダメージ層の深さやダメージの度合いが大きくなってきている。また、マイクロ波領域の光(赤外線等)を使いダメージ層を評価する場合には、光自身がSi基板から1μm以上の深さまで進入するため、実際のプラズマによる数10nmレベルのSi基板へのダメージを正確に評価することはできなかった。すなわち、今後のLSIの微細化に伴い薄く表層付近に形成されるダメージ層や極微小化された領域の評価に対して、正確な結果を与えることができなくなってきている。

【0009】

したがって、従来の評価方法を用いるだけでは、ダメージ層を確実に除去したり、ダメージ層を制御よく除去することが困難となっている。

【0010】

次に、不純物導入工程やアニール工程においては、以下の問題がある。半導体デバイス中の各要素が微細化され、微少領域での不純物導入とプロファイル制御の重要性が増す中で、上記従来のような経験に基づいたアニール条件設定では、しばしば、最適なプロファイルが得られない結果や、半導体基板内に欠陥が残留した状態で処理を終えるトラブルが発生していた。また、所望の半導体デバイス開発期間の短縮が切望される中で、従来のような処理→解析→処理→解析の手順によるアニール条件の最適化を行っているのでは、開発効率が著しく低下してしまう。そこで、最近になって、アニール処理プロセスのその場観察技術によるプロセス制御技術が切望されてきた。また、枚葉式の熱処理装置を用いて熱処理を行う際には、従来のバッチ式とは異なり、熱処理装置の特性のバラツキや経時変化により、ウエハ間における熱処理量の微妙なバラツキが発生してきた。さらに、不純物導入時の実際のドーズ量と、熱処理後に基板内に導入されている実効的な不純物濃度を正確に把握することが困難であった。

【0011】

ゲート絶縁膜の形成工程においては、以下の問題がある。上記従来のような電気的特性の評価によってゲート絶縁膜の特性を管理する場合、MOSデバイスの製造中に、かりに絶縁膜形成プロセスでなんらかの不具合が発生した場合であっても、プロセスが終了してからウエハをチャンバから取りだし、電気的特性の評価を行って初めて不具合が発見されるだけである。したがって、それまでの間、不具合のあるゲート絶縁膜が形成され続けることになり、生産性(効率)の低下を招いていた。

【0012】

本発明の第1の目的は、以上のような製造工程中における半導体装置の特性に影響与える要因をインラインで確実に把握し、良好かつ均一な特性を実現しうる光学的評価装置及びその方法を提供することにある。

【0013】

本発明の第2の目的は、半導体領域の光学的特性と半導体領域の状態との間に相関関係があることに着目して、光学的特性の評価を利用して半導体装置に対する各種処理をインラインで制御する半導体装置の製造装置を提供することにある。

【0014】

本発明の第3の目的は、光学的特性の評価精度の変化を利用して半導体装置の製造装置のチャンバーのメンテナンスを行う半導体装置の製造装置の管理方法を提供することにある。

【0015】

【課題を解決するための手段】

上記第1の目的を達成するために、本発明では、請求項1から3に記載されている第1の光学的評価装置に関する手段と、請求項4から5に記載されている第2の光学的評価装置に関する手段と、請求項6から16に記載されている第3の光学的評価装置に関する手段と、請求項22から27に記載されている光学的評価方法に関する手段とを講じている。

【0016】

上記第2の目的を達成するために、本発明では、請求項18から21に記載されている半導体装置の製造装置に関する手段を講じている。

【0017】

上記第3の目的を達成するために、本発明では、請求項28から40に記載されている半導体装置の製造装置の管理方法に関する手段を講じている。

【0018】

本発明の第1の光学的評価装置は、請求項1に記載されているように、チャンバー内で半導体領域を有する基板に処理を施す際に使用される光学的評価装置であって、励起光を生成する第1の光源と、測定光を生成する第2の光源と、上記第1の光源で生成された励起光を、上記チャンバー内の半導体基板の半導体領域に間欠的に照射させるための第1の光案内部材と、上記第2の光源で生成された測定光を上記半導体領域に照射させるための第2の光案内部材と、上記半導体領域に照射された測定光の反射率を検出するための反射率検出手段と、上記半導体領域から反射された測定光を上記反射率検出手段に入射させるための第3の光案内部材と、上記反射率検出手段の出力を受け、上記半導体領域に励起光が照射されているときと励起光が照射されていないときとの測定光の反射率の差を上記励起光が照射されていないときの測定光の反射率で除した値を測定光の反射率の変化割合として演算する変化演算手段と、を備え、上記第1の光源と第2の光源とは、上記励起光の波長と測定光との波長を含む波長の広スペクトル光を生成する単一の共通光源により構成されており、上記共通光源で生成された広スペクトル光を励起光と測定光とに分離するビームスプリッターと、上記半導体領域から反射される測定光を受けて、上記測定光を分光した後上記反射率検出手段に送る分光手段をさらに備え、上記第1及び第2の光案内部材は、上記ビームスプリッターからの光を受ける位置に配置されている。

【0019】

この光学的評価装置を用いることにより、以下の作用が得られる。第1の光案内部材により導かれる励起光が半導体領域に照射されると半導体領域のキャリアが励起され、キャリアによって電界が生じる。この電界のために、第2の光案内部材によって半導体領域に導かれる測定光の反射率は、励起光の照射があるときとないときとでは変化し、この変化割合は電界強度の大小及び測定光の波長に依存して変化する。一方、半導体領域にキャリアの再結合中心となる欠陥などがあると、励起されたキャリアの寿命が短くなるので、キャリアが形成する電界強度が小さくなる。つまり、励起光の照射があるときとないときにおける反射率の変化割合が半導体領域内の欠陥などの数に依存して変化するので、変化演算手段により、反射率検出手段の検出値から半導体領域における測定光の反射率の変化割合が演算されると、この反射率の変化割合は、半導体領域の結晶状態などを反映したものとなる。したがって、チャンバー内で行われる加工処理の条件をインラインでの半導体領域の評価に基づいて制御することが可能になる。

【0020】

また、光源が単一化されるので、光学的評価装置の構造が極めて簡素化される。

【0021】

請求項2に記載されているように、請求項1において、上記第2の光案内部材は、上記測定光を上記基板の表面に垂直な方向から入射させるように構成されていることが好ましい。

【0022】

これにより、測定光を半導体基板の表面に垂直な方向から照射するように構成されているので、微少な半導体領域に対して迅速かつ正確に反射率の変化を評価できる。すなわち、微細化される半導体装置の製造工程における光学的評価を行うことが可能な光学的評価装置が得られる。

【0023】

請求項3に記載されているように、請求項2において、上記第1の光案内部材は、上記励起光を上記基板の表面に垂直な方向から入射させるように構成されていることが好ましい。

【0024】

これにより、測定光及び励起光が半導体領域の表面に垂直な方向から照射されるので、半導体領域が極めて狭い場合でも、測定光の反射率の変化割合を利用した光学的評価を行うことが可能になる。したがって、半導体領域における加工処理の状態をリアルタイムで検出するのに特に適した光学的評価装置が得られることになる。

【0025】

本発明の第2の光学的評価装置は、請求項4に記載されているように、チャンバー内で半導体領域を有する基板に処理を施す際に使用される光学的評価装置であって、励起光を生成する第1の光源と、測定光を生成する第2の光源と、上記第1の光源で生成された励 起光を、上記チャンバー内の半導体基板の半導体領域に間欠的に照射させるための第1の光案内部材と、上記第2の光源で生成された測定光を上記半導体領域に照射させるための第2の光案内部材と、上記半導体領域に照射された測定光の反射率を検出するための反射率検出手段と、上記半導体領域から反射された測定光を上記反射率検出手段に入射させるための第3の光案内部材と、上記反射率検出手段の出力を受け、上記半導体領域に励起光が照射されているときと励起光が照射されていないときとの測定光の反射率の差を上記励起光が照射されていないときの測定光の反射率で除した値を測定光の反射率の変化割合として演算する変化演算手段と、を備え、上記変化演算手段は、上記測定光の反射率の変化割合のスペクトルにおいて極値を与える測定光の特定エネルギー値における測定光の反射率の変化割合のみ演算する。

【0026】

この光学的評価装置を用いることにより、以下の作用が得られる。第1の光案内部材により導かれる励起光が半導体領域に照射されると半導体領域のキャリアが励起され、キャリアによって電界が生じる。この電界のために、第2の光案内部材によって半導体領域に導かれる測定光の反射率は、励起光の照射があるときとないときとでは変化し、この変化割合は電界強度の大小及び測定光の波長に依存して変化する。一方、半導体領域にキャリアの再結合中心となる欠陥などがあると、励起されたキャリアの寿命が短くなるので、キャリアが形成する電界強度が小さくなる。つまり、励起光の照射があるときとないときにおける反射率の変化割合が半導体領域内の欠陥などの数に依存して変化するので、変化演算手段により、反射率検出手段の検出値から半導体領域における測定光の反射率の変化割合が演算されると、この反射率の変化割合は、半導体領域の結晶状態などを反映したものとなる。したがって、チャンバー内で行われる加工処理の条件をインラインでの半導体領域の評価に基づいて制御することが可能になる。

【0027】

また、もっとも望ましいある特定の波長を有する測定光の反射率の変化のみを検知することができる。したがって、雑音のないかつ感度の高い光学的評価が可能になる。

【0028】

請求項5に記載されているように、請求項4において、上記測定光の特定のエネルギー値を、3.2〜3.6eVの範囲に含まれるいずれかの値とすることが好ましい。

【0029】

本発明の第3の光学的評価装置は、請求項6に記載されているように、基板の半導体領域上に形成された絶縁膜の電気的特性を評価するための光学的評価装置であって、励起光を生成する第1の光源と、測定光を生成する第2の光源と、上記第1の光源で生成された励起光を、上記絶縁膜を通過させてその直下の半導体領域に間欠的に照射させるための第1の光案内部材と、上記第2の光源で生成された測定光を、上記絶縁膜を通過させて上記励起光が間欠的に照射されている半導体領域に照射させるための第2の光案内部材と、上記半導体領域に照射された測定光の反射率を検出する反射率検出手段と、上記半導体領域から反射された測定光を上記反射率検出手段に入射させるための第3の光案内部材と、上記反射率検出手段の出力を受け、上記半導体領域に励起光が照射されているときと励起光が照射されていないときとの測定光の反射率の差を上記励起光が照射されていないときの測定光の反射率で除することにより、測定光の反射率の変化割合を演算する変化演算手段と、上記測定光の反射率の変化割合の大小に基づき上記絶縁膜の電気的特性を評価する評価手段とを備えている。

【0030】

これにより、絶縁膜、特にゲート絶縁膜中の電気的な欠陥についての情報が得られる。すなわち、半導体領域に励起光が照射されるとキャリアが励起され、このキャリア数の変化に伴い電界強度が変化するので、半導体領域からのある波長領域における測定光の反射率が変化する。そのとき、半導体領域の上に絶縁膜が形成されていると、半導体領域の表面層にキャリアのトラップとなる欠陥サイトが存在するので、測定光の反射率の変化割合が小さくなる。ところが、絶縁膜中の欠陥(トラップ電子)の数が多いと、隣接する半導体領域の電界強度の増大量が大きくなるので、測定光の反射率の変化割合が大きくなる。したがって、評価手段により、測定光の反射率が所定範囲外にあるのについては不良と判定することで、迅速かつ確実に絶縁膜の電気的特性を管理できることになる。

【0031】

請求項7に記載されているように、請求項6において、上記評価手段を、上記測定光の反射率の変化割合のスペクトルにおいて極値を与える測定光の特定エネルギー値における測定光の反射率の変化割合が、絶縁膜の適正な容量値に対応する値のときのみ良品と判定するものとできる。

【0032】

請求項8に記載されているように、請求項6において、上記測定光の特定のエネルギー値を、3.2〜3.6eVの範囲に含まれるいずれかの値とすることができる。

【0033】

請求項7または8により、特徴的な形状を示す反射率の変化割合のスペクトル中において、絶縁膜の電気的特性の相違を検知するための感度がもっともよい箇所で、光学的評価が行われることになる。

【0034】

請求項9に記載されているように、請求項6から8のうちいずれか1つにおいて、上記半導体領域から反射される測定光を受けて、上記測定光を分光した後上記反射率検出手段に送る分光手段をさらに備えることができる。

【0035】

これにより、測定光の反射率の変化割合のスペクトルが検出されるので、スペクトル形状全体の情報に基づいて高精度の光学的評価を行うことが可能になる。

【0036】

請求項10に記載されているように、請求項6から8のうちいずれか1つにおいて、上記半導体領域から反射される測定光を受けて、上記測定光の特定のエネルギー値に相当する波長範囲の測定光のみを透過させて上記反射率検出手段に送るためのフィルターをさらに備えることができる。

【0037】

これにより、分光手段を設けなくても、望ましい波長範囲の反射率の変化を検知できるので、光学的評価装置の構造が簡素化され、かつ迅速な光学的評価が可能になる。

【0038】

請求項11に記載されているように、請求項6において、上記反射率検出手段は、600nm以下の波長範囲の測定光の反射率を検出することが好ましい。

【0039】

請求項12に記載されているように、請求項11において、上記反射率検出手段は、300〜600nmの波長範囲の測定光の反射率を検出することがさらに好ましい。

【0040】

請求項11または12により、特に可視光領域及びそれ以下の波長領域の測定光は半導体領域の数100nm以上の深さには達しないことを利用して、半導体領域内で絶縁膜内のトラップ電子の影響を受ける領域のみからの反射率の変化割合に基づいて光学的評価を行うことができる。

【0041】

請求項13に記載されているように、請求項6から12のうちいずれか1つにおいて、光学的評価装置をエリプソメトリ分光器を利用して構成することができる。

【0042】

これにより、ゲート酸化膜等の膜厚の測定に用いられているエリプソメトリ分光器を利用して、安価に光学的評価装置を構成することが可能になる。

【0043】

請求項14に記載されているように、請求項6から13のうちいずれか1つにおいて、光学的評価装置を半導体装置の酸化膜の形成に使用されるチャンバに取り付けることが好ましい。

【0044】

これにより、半導体基板を製造装置から取り出すことなく絶縁膜の品質を評価できるので、インラインでの特性評価に適した評価装置となる。

【0045】

請求項15に記載されているように、請求項6において、上記第2の光源をXeランプとすることができる。

【0046】

請求項16に記載されているように、請求項6において、上記第1の光源をArイオンレーザあるいはHe−Neレーザとすることができる。

【0047】

請求項17に記載されているように、請求項6から16のうちいずれか1つにおいて、上記第1の光案内部材は、上記励起光を1kHz以下の周波数で間欠的に照射するように構成されていることが好ましい。

【0048】

本発明の第1の半導体装置の製造装置は、請求項18に記載されているように、半導体領域を有する基板を収納するためのチャンバーと、上記チャンバー内で上記基板に加工処理を施すための加工処理手段と、上記チャンバー内に設置された上記基板の半導体領域に間欠的に励起光を照射するための第1の光供給手段と、上記半導体領域に測定光を照射するための第2の光供給手段と、上記半導体領域に照射された測定光の反射率を検出する反射率検出手段と、上記反射率検出手段の出力を受け、上記半導体領域に励起光が照射されているときと励起光が照射されていないときとの測定光の反射率の差を上記励起光が照射されていないときの測定光の反射率で除した値を測定光の反射率の変化割合として演算する変化演算手段と、上記加工処理手段による加工処理の進行中に、上記変化演算手段の出力を受け、上記反射率の変化割合に基づき上記加工処理条件を制御する加工処理制御手段とを備え、上記加工処理手段は、上記チャンバー内にプラズマを発生させて上記半導体領域のエッチングを行う。

【0049】

この半導体装置の製造装置を用いることにより、以下の作用が得られる。第1の光供給手段により半導体領域に励起光が照射されるとキャリアが励起され、キャリアによって電界が生じる。この電界のために、第2の光供給手段によって供給される測定光の反射率は、励起光の照射があるときとないときとでは変化し、この変化割合は電界強度の大小及び測定光の波長に依存して変化する。一方、半導体領域にキャリアの再結合中心となる欠陥などがあると、励起されたキャリアの寿命が短くなるので、キャリアが形成する電界強度が小さくなる。つまり、励起光の照射があるときとないときにおける反射率の変化割合が半導体領域内の欠陥などの数に依存して変化するので、変化演算手段により、反射率検出手段の検出値から半導体領域における測定光の反射率の変化割合が演算されると、この反射率の変化割合は、半導体領域の結晶状態などを反映したものとなる。そして、加工処理制御手段により、チャンバー内で行われる加工処理の条件がインラインでの半導体領域の評価に基づいて制御されるので、所望の特性を有する半導体装置が再現性よく形成されることになる。

【0050】

また、エッチングによって生じるダメージ層の深さやダメージの程度を制御することが可能となるので、後のダメージ層の除去を円滑に行うことが可能になる。

【0051】

本発明の第2の半導体装置の製造装置は、請求項19に記載されているように、半導体領域を有する基板を収納するためのチャンバーと、上記チャンバー内で上記基板に加工処理を施すための加工処理手段と、上記チャンバー内に設置された上記基板の半導体領域に間欠的に励起光を照射するための第1の光供給手段と、上記半導体領域に測定光を照射するための第2の光供給手段と、上記半導体領域に照射された測定光の反射率を検出する反 射率検出手段と、上記反射率検出手段の出力を受け、上記半導体領域に励起光が照射されているときと励起光が照射されていないときとの測定光の反射率の差を上記励起光が照射されていないときの測定光の反射率で除した値を測定光の反射率の変化割合として演算する変化演算手段と、上記加工処理手段による加工処理の進行中に、上記変化演算手段の出力を受け、上記反射率の変化割合に基づき上記加工処理条件を制御する加工処理制御手段とを備え、上記加工処理手段は、上記チャンバー内にプラズマを発生させて上記半導体領域のエッチングにより生じたダメージ層を除去するためのライトドライエッチングを行う。

【0052】

この半導体装置の製造装置を用いることにより、以下の作用が得られる。第1の光供給手段により半導体領域に励起光が照射されるとキャリアが励起され、キャリアによって電界が生じる。この電界のために、第2の光供給手段によって供給される測定光の反射率は、励起光の照射があるときとないときとでは変化し、この変化割合は電界強度の大小及び測定光の波長に依存して変化する。一方、半導体領域にキャリアの再結合中心となる欠陥などがあると、励起されたキャリアの寿命が短くなるので、キャリアが形成する電界強度が小さくなる。つまり、励起光の照射があるときとないときにおける反射率の変化割合が半導体領域内の欠陥などの数に依存して変化するので、変化演算手段により、反射率検出手段の検出値から半導体領域における測定光の反射率の変化割合が演算されると、この反射率の変化割合は、半導体領域の結晶状態などを反映したものとなる。そして、加工処理制御手段により、チャンバー内で行われる加工処理の条件がインラインでの半導体領域の評価に基づいて制御されるので、所望の特性を有する半導体装置が再現性よく形成されることになる。

【0053】

また、エッチングによって生じたダメージ層の深さやダメージの程度を把握した上で、ダメージ層除去のためのライトドライエッチングを行うことが可能になる。

【0054】

本発明の第3の半導体装置の製造装置は、請求項20に記載されているように、半導体領域を有する基板を収納するためのチャンバーと、上記チャンバー内で上記基板に加工処理を施すための加工処理手段と、上記チャンバー内に設置された上記基板の半導体領域に間欠的に励起光を照射するための第1の光供給手段と、上記半導体領域に測定光を照射するための第2の光供給手段と、上記半導体領域に照射された測定光の反射率を検出する反射率検出手段と、上記反射率検出手段の出力を受け、上記半導体領域に励起光が照射されているときと励起光が照射されていないときとの測定光の反射率の差を上記励起光が照射されていないときの測定光の反射率で除した値を測定光の反射率の変化割合として演算する変化演算手段と、上記加工処理手段による加工処理の進行中に、上記変化演算手段の出力を受け、上記反射率の変化割合に基づき上記加工処理条件を制御する加工処理制御手段とを備え、上記加工処理手段は、上記半導体領域の上に薄い絶縁膜を形成する。

【0055】

この半導体装置の製造装置を用いることにより、以下の作用が得られる。第1の光供給手段により半導体領域に励起光が照射されるとキャリアが励起され、キャリアによって電界が生じる。この電界のために、第2の光供給手段によって供給される測定光の反射率は、励起光の照射があるときとないときとでは変化し、この変化割合は電界強度の大小及び測定光の波長に依存して変化する。一方、半導体領域にキャリアの再結合中心となる欠陥などがあると、励起されたキャリアの寿命が短くなるので、キャリアが形成する電界強度が小さくなる。つまり、励起光の照射があるときとないときにおける反射率の変化割合が半導体領域内の欠陥などの数に依存して変化するので、変化演算手段により、反射率検出手段の検出値から半導体領域における測定光の反射率の変化割合が演算されると、この反射率の変化割合は、半導体領域の結晶状態などを反映したものとなる。そして、加工処理制御手段により、チャンバー内で行われる加工処理の条件がインラインでの半導体領域の評価に基づいて制御されるので、所望の特性を有する半導体装置が再現性よく形成される ことになる。

【0056】

また、所望の特性を有する絶縁膜例えばゲート酸化膜を形成することが可能となる。

【0057】

本発明の第4の半導体装置の製造装置は、請求項21に記載されているように、半導体領域を有する基板を収納するためのチャンバーと、上記チャンバー内で上記基板に加工処理を施すための加工処理手段と、上記チャンバー内に設置された上記基板の半導体領域に間欠的に励起光を照射するための第1の光供給手段と、上記半導体領域に測定光を照射するための第2の光供給手段と、上記半導体領域に照射された測定光の反射率を検出する反射率検出手段と、上記反射率検出手段の出力を受け、上記半導体領域に励起光が照射されているときと励起光が照射されていないときとの測定光の反射率の差を上記励起光が照射されていないときの測定光の反射率で除した値を測定光の反射率の変化割合として演算する変化演算手段と、上記加工処理手段による加工処理の進行中に、上記変化演算手段の出力を受け、上記反射率の変化割合に基づき上記加工処理条件を制御する加工処理制御手段とを備え、上記半導体領域の上には薄い絶縁膜が形成されており、上記加工処理手段は、上記半導体領域上の上記絶縁膜を除去するためのドライエッチングを行う。

【0058】

この半導体装置の製造装置を用いることにより、以下の作用が得られる。第1の光供給手段により半導体領域に励起光が照射されるとキャリアが励起され、キャリアによって電界が生じる。この電界のために、第2の光供給手段によって供給される測定光の反射率は、励起光の照射があるときとないときとでは変化し、この変化割合は電界強度の大小及び測定光の波長に依存して変化する。一方、半導体領域にキャリアの再結合中心となる欠陥などがあると、励起されたキャリアの寿命が短くなるので、キャリアが形成する電界強度が小さくなる。つまり、励起光の照射があるときとないときにおける反射率の変化割合が半導体領域内の欠陥などの数に依存して変化するので、変化演算手段により、反射率検出手段の検出値から半導体領域における測定光の反射率の変化割合が演算されると、この反射率の変化割合は、半導体領域の結晶状態などを反映したものとなる。そして、加工処理制御手段により、チャンバー内で行われる加工処理の条件がインラインでの半導体領域の評価に基づいて制御されるので、所望の特性を有する半導体装置が再現性よく形成されることになる。

【0059】

また、半導体領域からの測定光の反射率の変化割合が絶縁膜の厚みによる影響を受けることを利用して、インラインでの光学的評価によって絶縁膜の除去の進行を制御することが可能となる。

【0060】

本発明の第1の半導体装置の光学的評価方法は、請求項22に記載されているように、チャンバー内で半導体領域を有する基板に加工処理を施す際に加工処理の状態を評価するための光学的評価方法であって、上記チャンバー内の上記基板の半導体領域に測定光を照射するステップと、上記半導体領域に励起光を間欠的に照射するステップと、上記半導体領域に励起光が照射されているときと励起光が照射されていないときとの測定光の反射率の差を上記励起光が照射されていないときの測定光の反射率で除した値を反射率の変化割合として演算するステップとを備え、上記加工処理は、上記半導体領域のプラズマエッチング加工である。

【0061】

この方法により、励起光が半導体領域に照射されると半導体領域のキャリアが励起され、キャリアによって電界が生じる。この電界のために、半導体領域に導かれる測定光の反射率は、励起光の照射があるときとないときとでは変化し、この変化割合は電界強度の大小及び測定光の波長に依存して変化する。一方、半導体領域にキャリアの再結合中心となる欠陥などがあると、励起されたキャリアの寿命が短くなるので、キャリアが形成する電界強度が小さくなる。つまり、励起光の照射があるときとないときにおける反射率の変化割合が半導体領域内の欠陥などの数に依存して変化するので、半導体領域における測定光の反射率の変化割合が演算されると、この反射率の変化割合は、半導体領域の結晶状態などを反映したものとなる。したがって、チャンバー内で行われる加工処理の条件をインラインでの光変調反射率測定に基づいて制御することが可能になる。

【0062】

また、エッチングによって生じるダメージ層の深さやダメージの程度を制御することが可能となるので、後のダメージ層の除去を円滑に行うことが可能になる。

【0063】

本発明の第2の半導体装置の光学的評価方法は、請求項23に記載されているように、チャンバー内で半導体領域を有する基板に加工処理を施す際に加工処理の状態を評価するための光学的評価方法であって、上記チャンバー内の上記基板の半導体領域に測定光を照射するステップと、上記半導体領域に励起光を間欠的に照射するステップと、上記半導体領域に励起光が照射されているときと励起光が照射されていないときとの測定光の反射率の差を上記励起光が照射されていないときの測定光の反射率で除した値を反射率の変化割合として演算するステップとを備え、上記加工処理は、上記半導体領域のプラズマエッチングにより生じたダメージ層を除去するためのライトドライエッチングである。

【0064】

この方法により、励起光が半導体領域に照射されると半導体領域のキャリアが励起され、キャリアによって電界が生じる。この電界のために、半導体領域に導かれる測定光の反射率は、励起光の照射があるときとないときとでは変化し、この変化割合は電界強度の大小及び測定光の波長に依存して変化する。一方、半導体領域にキャリアの再結合中心となる欠陥などがあると、励起されたキャリアの寿命が短くなるので、キャリアが形成する電界強度が小さくなる。つまり、励起光の照射があるときとないときにおける反射率の変化割合が半導体領域内の欠陥などの数に依存して変化するので、半導体領域における測定光の反射率の変化割合が演算されると、この反射率の変化割合は、半導体領域の結晶状態などを反映したものとなる。したがって、チャンバー内で行われる加工処理の条件をインラインでの光変調反射率測定に基づいて制御することが可能になる。

【0065】

また、エッチングによって生じたダメージ層の深さやダメージの程度を把握した上で、ダメージ層除去のためのライトドライエッチングを行うことが可能になる。

【0066】

本発明の第3の半導体装置の光学的評価方法は、請求項24に記載されているように、チャンバー内で半導体領域を有する基板に加工処理を施す際に加工処理の状態を評価するための光学的評価方法であって、上記チャンバー内の上記基板の半導体領域に測定光を照射するステップと、上記半導体領域に励起光を間欠的に照射するステップと、上記半導体領域に励起光が照射されているときと励起光が照射されていないときとの測定光の反射率の差を上記励起光が照射されていないときの測定光の反射率で除した値を反射率の変化割合として演算するステップとを備え、上記加工処理は、上記半導体領域の上における絶縁膜の形成である。

【0067】

この方法により、励起光が半導体領域に照射されると半導体領域のキャリアが励起され、キャリアによって電界が生じる。この電界のために、半導体領域に導かれる測定光の反射率は、励起光の照射があるときとないときとでは変化し、この変化割合は電界強度の大小及び測定光の波長に依存して変化する。一方、半導体領域にキャリアの再結合中心となる欠陥などがあると、励起されたキャリアの寿命が短くなるので、キャリアが形成する電界強度が小さくなる。つまり、励起光の照射があるときとないときにおける反射率の変化割合が半導体領域内の欠陥などの数に依存して変化するので、半導体領域における測定光の反射率の変化割合が演算されると、この反射率の変化割合は、半導体領域の結晶状態などを反映したものとなる。したがって、チャンバー内で行われる加工処理の条件をインラインでの光変調反射率測定に基づいて制御することが可能になる。

【0068】

また、所望の特性を有する絶縁膜例えばゲート酸化膜を形成することが可能となる。

【0069】

本発明の第4の半導体装置の光学的評価方法は、請求項25に記載されているように、チャンバー内で半導体領域を有する基板に加工処理を施す際に加工処理の状態を評価するための光学的評価方法であって、上記チャンバー内の上記基板の半導体領域に測定光を照射するステップと、上記半導体領域に励起光を間欠的に照射するステップと、上記半導体領域に励起光が照射されているときと励起光が照射されていないときとの測定光の反射率の差を上記励起光が照射されていないときの測定光の反射率で除した値を反射率の変化割合として演算するステップとを備え、上記加工処理は、上記半導体領域上の絶縁膜の除去するためのドライエッチングである。

【0070】

この方法により、励起光が半導体領域に照射されると半導体領域のキャリアが励起され、キャリアによって電界が生じる。この電界のために、半導体領域に導かれる測定光の反射率は、励起光の照射があるときとないときとでは変化し、この変化割合は電界強度の大小及び測定光の波長に依存して変化する。一方、半導体領域にキャリアの再結合中心となる欠陥などがあると、励起されたキャリアの寿命が短くなるので、キャリアが形成する電界強度が小さくなる。つまり、励起光の照射があるときとないときにおける反射率の変化割合が半導体領域内の欠陥などの数に依存して変化するので、半導体領域における測定光の反射率の変化割合が演算されると、この反射率の変化割合は、半導体領域の結晶状態などを反映したものとなる。したがって、チャンバー内で行われる加工処理の条件をインラインでの光変調反射率測定に基づいて制御することが可能になる。

【0071】

また、半導体領域からの測定光の反射率の変化割合が絶縁膜の厚みによる影響を受けることを利用して、インラインでの光変調反射率測定によって絶縁膜の除去の進行を制御することが可能となる。

【0072】

請求項26に記載されているように、請求項22から25のうちいずれか一つにおいて、上記測定光を照射するステップでは、上記測定光を上記基板の表面に垂直な方向から照射することが好ましい。

【0073】

この方法により、面積の狭い半導体領域に対しても光変調反射率測定を行うことが可能になる。

【0074】

請求項27に記載されているように、請求項26において、上記励起光を照射するステップでは、上記励起光を上記基板の表面に垂直な方向から照射することが好ましい。

【0075】

本発明の半導体装置の製造装置の管理方法は、請求項28に記載されているように、半導体領域を有する基板を収納するためのチャンバーと、上記チャンバー内で上記基板に加工処理を施すための加工処理手段と、上記チャンバー内に設置された上記基板の半導体領域に間欠的に励起光を照射するための第1の光供給手段と、上記半導体領域に測定光を照射するための第2の光供給手段と、上記半導体領域に照射された測定光の反射率を検出する反射率検出手段とを備えた半導体装置の製造装置の管理方法であって、上記半導体領域に測定光を照射する第1のステップと、上記半導体領域に励起光を間欠的に照射する第2のステップと、上記半導体領域に励起光が照射されているときと励起光が照射されていないときとの測定光の反射率の差を上記励起光が照射されていないときの測定光の反射率で除した値を測定光の反射率の変化割合として演算する第3のステップと、上記第3のステップで演算された反射率の変化割合が所定値に達するまでの所定時間の間上記加工処理手段を作動させるように制御する第4のステップと、上記第4のステップにおける上記所定時間を監視して、上記所定時間が限界値を超えると上記半導体装置の製造装置のメンテナンスを行うための信号を出力する第5のステップとを備えている。

【0076】

この方法により、半導体装置の製造装置を使用していくにつれて、チャンバー内の構成部材の劣化によって反射率の変化割合が所定値に達するまでの加工処理時間が増大するのを監視することができる。したがって、チャンバー内の構成部材の劣化が生じたときには、適正なタイミングでかつ無駄のないメンテナンスを行うことができる。そして、メンテナンスの実施によって、適正な加工処理時間を確保することができ、加工処理時間の過大に起因する半導体領域の不良の発生を回避することができる。

【0077】

請求項29に記載されているように、請求項28において、上記加工処理手段は、上記チャンバー内にプラズマを発生させて上記半導体領域のエッチングを行うことができる。

【0078】

この方法により、チャンバー内でプラズマエッチングを行いながら、例えばプラズマ加工の際に生じるチャンバーの壁面等へのデポ物によって測定光の反射率の変化割合の検知感度の劣化が生じたときなどには、チャンバー等のメンテナンスを行って、適正な制御を維持することができる。

【0079】

請求項30に記載されているように、請求項28において、上記加工処理手段を、上記チャンバー内にプラズマを発生させて上記半導体領域のエッチングにより生じたダメージ層を除去するためのドライエッチングを行うものとすることができる。

【0080】

この方法により、エッチングによって生じたダメージ層を除去するドライエッチングを行いながら、例えばプラズマ加工の際に生じるチャンバーの壁面等へのデポ物によって測定光の反射率の変化割合の検知感度の劣化が生じたときなどには、チャンバー等のメンテナンスを行って、適正な制御を維持することができる。

【0081】

請求項31に記載されているように、請求項28において、上記加工処理手段を、上記半導体領域に不純物を導入するものとすることができる。

【0082】

この方法により、不純物導入処理を行いながら、例えば不純物導入の際に生じるチャンバーの壁面等へのデポ物によって測定光の反射率の変化割合の検知感度の劣化が生じたときなどには、チャンバー等のメンテナンスを行って、適正な制御を維持することができる。

【0083】

請求項32に記載されているように、請求項28において、上記加工処理手段は、上記半導体領域にイオン注入を行った後のアニールを行うものとすることができる。

【0084】

この方法により、イオン注入によって生じた構造の乱れを回復させるためのアニールを行いながら、高温状態で行われるアニール処理のためにチャンバーの部材が劣化したときなどには、チャンバー等のメンテナンスを行って、適正な制御を維持することができる。

【0085】

請求項33に記載されているように、請求項28において、上記加工処理手段は、上記半導体領域の上に薄い絶縁膜を形成するものとすることができる。

【0086】

この方法により、熱酸化,CVDなどによる絶縁膜の形成を行いながら、例えば熱酸化の際に生じるチャンバー内の部材の劣化によって測定光の反射率の変化割合の検知感度の劣化が生じたときなどには、チャンバー等のメンテナンスを行って、適正な制御を維持することができる。

【0087】

請求項34に記載されているように、請求項28において、上記半導体領域上に薄い絶縁膜が形成されている場合には、上記加工処理手段を、上記半導体領域上の薄い絶縁膜を除去するためのドライエッチングを行うものとすることができる。

【0088】

この方法により、エッチングによって生じたダメージ層を除去するドライエッチングを行いながら、例えばプラズマ加工の際に生じるチャンバーの壁面等へのデポ物によって測定光の反射率の変化割合の検知感度の劣化が生じたときなどには、チャンバー等のメンテナンスを行って、適正な制御を維持することができる。

【0089】

請求項35に記載されているように、請求項28から34のうちいずれか1つにおいて、上記反射率検出手段は、600nm以下の波長範囲の測定光の反射率を検出することが好ましい。

【0090】

請求項36に記載されているように、請求項35において、上記反射率検出手段は、300〜600nmの波長範囲の測定光の反射率を検出することがさらに好ましい。

【0091】

請求項37に記載されているように、請求項28から36のうちいずれか1つにおいて、上記反射率の変化割合を演算するステップでは、測定光の反射率の変化割合のスペクトルの極値を与える測定光の特定エネルギー値における測定光の反射率の変化割合を演算することができる。

【0092】

請求項38に記載されているように、請求項28から37のうちいずれか1つにおいて、上記反射率検出手段を、光フィルターを用いて特定の波長の反射光の反射率を検出するように構成することが好ましい。

【0093】

請求項39に記載されているように、請求項28から38のうちいずれか1つにおいて、上記半導体領域は、n型シリコンにより構成されていることが好ましい。

【0094】

請求項40に記載されているように、請求項28から39のうちいずれか1つにおいて、上記励起光を照射するステップでは、上記励起光を1kHz以下の周波数で間欠的に照射することが好ましい。

【0095】

【発明の実施の形態】

(第1の実施形態)

以下、本発明の第1の実施形態について説明する。

【0096】

図4は、第1の実施形態に係る反射強度Rの観測手段を備えたエッチング装置の構成を概略的に示す断面図である。同図に示すように、反応処理室200内には、下部電極であるアノード電極213と、上部電極であるカソード電極214とが配設されていて、アノード電極213の上に被加工物であるp型シリコンからなるウエハ103が設置されている。そして、高周波電源211からカップリングコンデンサ212を介して高周波電力が各電極213,214間に供給されると、反応処理室200内にプラズマ401が生成されるように構成されている。また、反応処理室200の壁面には、終点検出用窓215と、プローブ光入射用窓218と、反射光観測用窓219とが設けられている。

【0097】

一方、反応処理室200の外部には、終点検出システム216が設けられているとともに、反射強度Rの観測のための部材が配設されている。まず、n型半導体領域101に照射するプローブ光を発生するXeランプ302が設けられており、Xeランプ302で生成されたプローブ光403はミラー217により反射された後、プローブ光入射用窓218を介して反応処理室200内に設置されたウエハ103のn型半導体領域101に送られる。そして、n型半導体領域101で反射された反射プローブ光404は、反射光観測用窓219から反応処理室200の外に取り出され、反射強度観測システム220によりその強度(特に、波長376nm,エネルギー3.3eVの付近)が検出される。そして、反射強度観測システム220で計測された反射強度に関するデータは、信号経路221を経てエッチング制御システム222に送られる。また、n型半導体領域101に照射する励起光を発生するArイオンレーザー301が設けられており、このArイオンレーザー301で発生された励起光402はチョッパ223によって周波数200Hzでチョッピングされて、間欠的に送られる。この励起光402は、終点検出用窓215を介して反応処理室200内に送られ、n型半導体領域101に間欠的に照射される。そして、上述のように、励起光402が照射されているときと照射されていないときのプローブ光403の反射強度(つまり反射プローブ光404の強度)の差ΔRを励起光402の照射がないときの反射強度Rで割った値(ΔR/R)が反射強度の変化割合として反射強度観測システム220で検知される。以上の構成により、反射強度の変化割合の変動がモニターされる。 なお、一般的には、本実施形態及び後述の各実施形態における光学システムにおいて、プローブ光の入射側には偏光子を反射側には検光子が配置されることが多い。

【0098】

ここで、このような反射強度の変化割合(ΔR/R)は、以下の作用によって生じると考えられる。一般的に、半導体に光を照射すると、光によって励起されてキャリア数が増大し、その後、キャリアが元のエネルギー準位に戻る際には光を放出して消滅する。このキャリア数の変化に伴い電界強度が変化する。したがって、励起光が照射されているときと、励起光が照射されていないときとでは、反射強度が異なる。ところが、半導体内に欠陥が多く存在すると、その欠陥によってエネルギー準位の低い界面準位が存在することになる。そして、このような界面準位を有する欠陥がキャリアの捕獲層として機能するために、光が照射されてもキャリアが欠陥に捕獲されて十分に高いエネルギー準位まで励起されなかったり、高いエネルギー準位まで励起されたキャリアが欠陥に捕獲されたりすると、励起されてキャリアが低いエネルギー準位に戻る際に発生する光の強度が低下し、電界強度も変化することになる。したがって、ダメージ層の深さやダメージの程度が大きいほど反射強度の変化割合(ΔR/R)が小さくなる。したがって、この反射強度の変化割合をモニターすることにより、ダメージ層に関する情報が得られる。

【0099】

なお、上記チョッピングの周波数は、キャリアが再結合して電界強度が変化する時間と関係があるものと思われ、実験から1kHz以下が好ましく、より好ましくは500Hz以下が好ましいことがわかっている。また、励起光のフォトンのエネルギーが半導体領域のバンドギャップよりも大きいことが好ましい。シリコン基板を使用する場合には、フォトンのエネルギーが1.1eV以上の波長の励起光を使用することが好ましい。以上のことは、後述の各実施形態においても同様である。

【0100】

本実施形態では、測定光の照射強度(各波長域における)を一定と仮定しているので、反射強度を検出することで反射率の検出に置き換えている。すなわち、反射強度の変化割合の測定は、n型半導体領域101にArイオンレーザー光である励起光402を間欠的に照射しながら、別の方向からXeランプ光であるプローブ光403を連続的に照射して、このプローブ光403の反射強度の変化の検出により行われる。つまり、n型半導体領域101に励起光402が照射されているときの反射強度と励起光402が照射されていないときの反射強度との差ΔRを、n型半導体領域101に励起光402が照射されていないときの反射強度Rで割った値(ΔR/R)を反射強度の差つまり反射率としている。

【0101】

ここで、励起光の照射・非照射を繰り返しながらプローブ光の波長を変化させて、その波長(光のエネルギー値)ごとに反射率の変化割合を測定して、そのスペクトル形状を調べることは光変調反射率分光と呼ばれている。例えば図22は、半導体領域である単結晶シリコン層に入射したプローブ光の波長λの逆数に比例するエネルギーの値と反射率の変化割合(ΔR/R)との関係を示すスペクトル線図である。ただし、同図の反射率の変化割合(ΔR/R)の値は、初期の状態を0とする相対値である。本実施形態では、反射率の変化割合(ΔR/R)が変動する感度のもっとも高いエネルギー値3.30eV(ほぼ極値を示すエネルギー値)に相当するプローブ光の波長376nmを使用するようにしている。

【0102】

図3は、本実施形態に係るウエハの構造を概略的に示す上面図である。図3に示すように、p型シリコンからなるウエハ103の上に、最終的にウエハから切り出されて半導体チップとなるチップ領域Rtpと、光学的評価のためのモニター領域Rmnとが設けられている。

【0103】

次に、本実施形態におけるエッチング処理の進行と反射強度の変化割合(ΔR/R)の測定との関係を、ウエハの断面構造を参照しながら説明する。図2(a)〜(c)は、本実施形態に係る半導体装置の製造工程を示すウエハの断面図である。

【0104】

図2(a)に示す工程の前に、ウエハ103上のモニター領域Rmnにおいて、広さが例えば13×13μm2 のn型半導体領域(比抵抗値が約0.02Ωcm)101が形成されている。一方、チップ領域Rtpには各種の半導体素子が形成されており、図2(a)には、その例として、ポリシリコンからなるゲート電極106と、厚みが例えば6nmのゲート酸化膜107と、n型ソース領域108及びn型ドレイン領域109とを有するMOSトランジスタが示されている。そして、ウエハの全面上に層間絶縁膜104が堆積されている。なお、本実施形態では、n型半導体領域101は、n型ソース領域108及びn型ドレイン領域109と同じ導電型かつ同じ濃度の不純物がドープされているが、後述のように、モニター用領域Rmn内の半導体領域には、モニターされる半導体素子内のソース・ドレイン領域とは異なる導電型,異なる濃度を有する不純物をドープしておいてもよい。特に、モニター領域Rmn内における不純物濃度を高くすることで、エッチングダメージの除去状態の検出感度をより高めることができる。

【0105】

次に、図2(b)に示す工程において、層間絶縁膜104上にコンタクトホール形成用フォトレジストマスク105が形成され、このフォトレジストマスク105を用いて、層間絶縁膜104を選択的に除去するためのドライエッチングが行われる。このドライエッチングは、後述するようにプラズマを利用した加工であり、エッチング条件は、例えば以下の通りである。Arガス、CHF3 ガス及びCF4 ガスの混合ガスを用い、ガス流量は、Arガスが80sccm、CHF3 ガスが45sccm、CF4 ガスが20sccmで、全体のガス圧力を80mTorrとして、パワー400Wで高周波放電させる。このドライエッチング工程により、MOSトランジスタのn型ソース領域108,n型ドレイン領域109にそれぞれ到達するコンタクトホールである開口110a,110bが形成されると同時に、n型半導体領域101に到達するモニター用の開口110cが形成される。そして、プラズマ発光法による各開口110a〜110cの形成の完了が検知された時点では、ウエハ上のn型ソース領域108,n型ドレイン領域109,n型半導体領域101には、ダメージ層Rdm1,Rdm2,Rdm3がそれぞれ形成されている。

【0106】

次に、図2(c)に示す工程で、ドライエッチングにより生じたダメージ層Rdm1〜Rdm3を取り除くためのライトエッチング(ドライエッチング)を行う。このとき、本実施形態では、ガス流量・圧力は変化させず、パワーを200Wに下げた条件を適用している。

【0107】

図1は、プラズマ処理の際の光学的モニターの一般的な手順を示すフローチャートである。

【0108】

まず、ステップST100でメインエッチングを行い、メインエッチングが終了すると、ステップST101で、n型半導体領域101の初期の反射強度の変化割合(ΔR/R)を測定する。本実施形態では、メインエッチング終了後におけるn型半導体領域101についての測定値を初期の反射強度の変化割合(ΔR/R)とする。

【0109】

次に、ステップST102でプラズマ処理を行い、ステップST103で、プラズマ処理中における反射強度の変化割合(ΔR/R)をモニターする。本実施形態では、プラズマ処理としてライトエッチングを行い、ライトエッチング中における反射強度の変化割合(ΔR/R)をモニターする。

【0110】

さらに、ステップST104で、プラズマ処理(本実施形態ではライトエッチング)中における反射強度の変化割合(ΔR/R)を初期の反射強度の変化割合(ΔR/R)と比較し、予め実験により得られたプラズマ処理が完了したことを判定する基準値に達したと判定されるまでは、ステップST102〜ST104の処理を行い、プラズマ処理が終了したと判定すると、ステップST105でプラズマ処理を終了する。本実施形態では、ダメージ層の除去が完了したと判定すると、ステップST105でライトエッチングを終了することになる。

【0111】

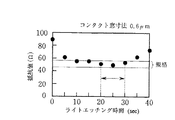

ここで、本実施形態における反射強度の変化割合とダメージ層の状態との関係について説明する。図5は、波長376nm(エネルギー3.3eV)における反射強度の変化割合(ΔR/R)の初期値に対する比の時間的変化を示す図である。図5に示すように、ライトエッチングの開始直後(0〜20sec間での間)は、メインステップのドライエッチングが終了したときよりも反射強度の変化割合(ΔR/R)が大きくなって初期値に近づいており、ダメージ層が除去されていることがわかる。しかし、ライトエッチング時間の増大とともに(20sec経過後)、反射強度の変化割合(ΔR/R)の初期値に対する比がライトエッチング開始時の値(図5に示す例では約0.6)よりも小さくなり、過度のライトエッチングによってSi結晶(基板)への損傷が大きくなることが分かる。

【0112】

一方、図6に示すように、ライトエッチング時間とコンタクト部の抵抗値(コンタクト抵抗)との相関は、あらかじめ実験を行うことにより得ておくことができる。図6に示すように、ライトエッチング初期の段階では、コンタクト抵抗が大きいが、これは、メインエッチング発生した有機系のポリマーがコンタクトホールの底面付近に堆積しているためであり、その後のライトエッチングによりしだいに除去されているのがわかる。そして、図6と図5とを比べるとわかるように、コンタクト抵抗と反射強度の変化割合(ΔR/R)との間には相関がある。そして、この相関関係から、コンタクト抵抗の規格値(コンタクト窓の断面寸法が0.6μmのときに50±5Ω)にするためには、反射強度の変化割合(ΔR/R)が初期値より60%の値以上でなければならないことがわかる。したがって、反射強度の変化割合(ΔR/R)が60%になった時点でライトエッチングステップを終了することで、メインエッチングで生じたダメージ層をほぼ除去しながらその後ライトエッチングにより生じる新たなダメージの発生を抑制することができ、良好な接合を有する半導体デバイスを実現することができる。

【0113】

図7は、ダメージ層に関する情報を得るための光学的監視を伴って行われる本実施形態のライトエッチングによって形成されたMOSトランジスタのコンタクト抵抗と、そのような光学的監視を伴わない従来のライトエッチングによって形成されたMOSトランジスタのコンタクト抵抗とを比較するデータである。同図に示されるように、本実施形態の半導体製造装置の製造方法を用いることで、従来方法にくらべ、コンタクト抵抗バラツキを抑えることができ、品質・信頼性の高い半導体装置を製造することができる。

【0114】

次に、本実施形態のごとく光変調反射率分光によりダメージ層をモニターすることにより得られる利点について説明する。一般に、プラズマ処理を行った際のイオンの進入深さは数10nm程度である。ここで、赤外線等のマイクロ波の半導体基板内への進入深さは1μm以上であるので、反射率から得られる情報にはダメージ層からの情報だけでなくダメージ層以外の領域からの情報が多量に混在していて、ダメージ層のみに関する情報を正確に取り出すことは困難である。したがって、これらの方法はエッチングダメージのような微少な領域に対する検知方法としては適当でない。それに対し、可視光以下の領域の光を利用した光学的モニターを行う場合、半導体基板内への進入深さはたかだか数100nm程度であるので、深さが数10nmのダメージ層に関する検知感度が極めて高くなる。しかも、エッチングされている半導体ウエハの表面に光を照射することにより、直接ダメージ層に関する情報を得ることができるので、このような可視光以下の領域の光を利用した光学的モニターを行うことにより、インラインでの評価及びプロセス制御に極めて有用な情報を提供することができる。かかる観点から、本実施形態及び後述の各実施形態における光変調反射率測定法においては、測定光の光源の選定により、あるいはフィルターの取り付けにより、600nm以下の波長範囲の測定光を検出することが好ましく、300〜600nmの波長範囲の測定光を検出することがより好ましい。

【0115】

なお、本実施形態では、ウエハ103内に、チップ領域Rtpとは別にモニター用領域Rmnを設けたが、本発明は、斯かる実施形態に限定されるものではなく、チップ領域Rtp内に光学的評価パターンを設けても本実施形態と同様の効果が得られる。

【0116】

さらに、一定時間内のライトエッチング処理による反射強度の変化割合(ΔR/R)の変動量を管理することで、装置の異常を迅速に把握し、装置トラブルが防止できる。

【0117】

上記実施形態では、エッチング加工をプラズマを用いたドライエッチングとしたが、本発明は斯かる実施形態に限定されるものではなく、例えばスパッタリング等によるプラズマを利用しないドライエッチングや、ウエットエッチング等に対しても適用することができる。

【0118】

また、当初に大きなダメージ層がある半導体領域に対してそのダメージ層を除去するためのエッチングだけでなく、ダメージ層がほとんどない半導体領域をエッチングしていく際のエッチングに対しても適用できる。

【0119】

さらに、上記実施形態では、チップ領域Rtp内の第1の半導体領域であるソース・ドレイン領域108,109と第2の半導体領域であるモニター用領域Rmn内のn型半導体領域101との不純物濃度や深さを同じとしているが、本発明は斯かる実施形態に限定されるものではなく、第1の半導体領域と第2の半導体領域の不純物濃度や不純物の導電型が異なっていてもよいものとする。あらかじめ実験を行っておけば、第1の半導体領域における適正なコンタクト抵抗を得るための第2の半導体領域における光学的特性(上記実施形態ではコンタクト抵抗)がわかるからである。たとえば、モニター領域Rmnにおける不純物濃度を特別に濃くしておいて、反射強度の変化割合の検知感度を高くしておくことも可能である。

【0120】

また、本実施形態では、図4に示すように、基板表面に対するプローブ光403の角度が励起光402の角度よりも小さくなっているが、反射強度の測定が必要なプローブ光403の角度を大きくすることが、モニターされる第2の半導体領域の面積を低減するためには好ましい。

【0121】

(第2の実施形態)

図8は、本実施形態における光学的モニターシステムを示したものである。同図に示すように、n型半導体領域101に照射する測定光であるプローブ光を発生するXeランプ502が設けられており、Xeランプ502で生成されたプローブ光507はミラー506により反射された後、ウエハステージ504上に設置されたウエハ103上のn型半導体領域101に送られる。そして、n型半導体領域101で反射された反射プローブ光508は、ミラー506を通過して顕微鏡システム505に送られ、観測システム兼解析システム509によりその強度(特に、波長376nmの付近)が検出される。本実施形態では、プローブ光507の観測領域への照射及びその反射プローブ光508の取り出しは、顕微鏡システム505とミラー506との併用により、試料の表面に対して垂直な方向から行うことができる。この点が上記第1の実施形態と異なる主要な点である。また、プローブ光507の径は、レンズ510により10μmφまで絞ることができる。なお、この観測システム兼解析システム509で計測された反射強度に関するデータは、信号線を介してエッチング制御システム(図示せず)に送られる。

【0122】

また、n型半導体領域101に照射する励起光を発生する強度5WのArイオンレーザー503が設けられており、このArイオンレーザー503で生成された励起光511はチョッパ510によって周波数100Hzでチョッピングされて、n型半導体領域101に間欠的に照射される。そして、上述のように、励起光511が照射されているときと照射されていないときのプローブ光507の反射強度(つまり反射プローブ光508の強度)の差ΔRを励起光511の照射がないときの反射強度Rで割った値(ΔR/R)が反射強度の変化割合として観測システム兼解析システム509で検知される。以上の構成により、プローブ光の反射強度の変化割合の変動がモニターされる。なお、半導体領域101からの反射励起光512の強度を検出する反射励起光観測システム513も設けられており、この反射励起光512の強度に関する情報は、信号線を介して観測システム兼解析システム509に送られる。なお、チョッパ510と、反射光の強度を検出する検出器とは同期して動作するように構成されている。

【0123】

そして、本実施形態においても、上記第1の実施形態と同様に、図3に示すように、p型シリコンからなるウエハ103の上に、最終的にウエハから切り出されて半導体チップとなるチップ領域Rtpと、光学的評価のためのモニター領域Rmnとが設けられている。

【0124】

次に、本実施形態におけるプラズマエッチング方法について、図9(a)〜(c)を参照しながら説明する。

【0125】

図9(a)に示す工程の前に、ウエハ103上のモニター領域Rmnにおいて、広さが例えば13×13μm2 のn型半導体領域(比抵抗値が約0.02Ωcm)101が形成されている。一方、チップ領域Rtpには各種の半導体素子が形成されており、図9(a)には、その例として、ポリシリコンからなるゲート電極106と、厚みが例えば6nmのゲート酸化膜107と、n型ソース領域108及びn型ドレイン領域109とを有するMOSトランジスタが示されている。そして、ウエハのほぼ全面上に層間絶縁膜104が堆積されている。なお、本実施形態では、n型半導体領域101は、n型ソース領域108及びn型ドレイン領域109と同じ導電型かつ同じ濃度の不純物がドープされているが、後述のように、モニター用領域Rmn内の半導体領域には、モニターされる半導体素子内のソース・ドレイン領域とは異なる導電型,異なる濃度を有する不純物をドープしておいてもよい。

【0126】

次に、図9(b)に示す工程において、層間絶縁膜104上にコンタクトホール形成用フォトレジストマスク105が形成され、このフォトレジストマスク105を用いて、層間絶縁膜104を選択的に除去するためのドライエッチングが行われる。このドライエッチングは、プラズマを利用したエッチングであり、エッチング条件は、例えば、チャンバ(図示せず)内に、Arガス、CHF3 ガス及びCF4 ガスの混合ガスを、Arガスの流量が80sccm、CHF3 ガスの流量が45sccm、CF4 ガスの流量が20sccmで、全体のガス圧力を80mTorrとして、パワー400Wで高周波放電させる。このドライエッチング工程により、MOSトランジスタのn型ソース領域108,n型ドレイン領域109にそれぞれ到達するコンタクトホールである開口110a,110bが形成されると同時に、n型半導体領域101に到達するモニター用の開口110cが形成される。そして、プラズマ発光法による各開口110a〜110cの形成の完了が検知された時点では、ウエハ103上のn型ソース領域108,n型ドレイン領域109,n型半導体領域101には、ダメージ層Rdm1,Rdm2,Rdm3がそれぞれ形成されている。

【0127】

次に、図9(c)に示す工程で、ドライエッチングにより生じたダメージ層Rdm1〜Rdm3を取り除くためのライトエッチング(ドライエッチング)を行う。このとき、本実施形態では、ガス流量・圧力は変化させず、パワーを200Wに下げた条件を適用している。

【0128】

図10は、プラズマ処理を行ったサンプルとプラズマ処理を行っていないサンプルとについて、照射励起光の強度を変えたときのプローブ光の反射強度の変化割合を測定したデータである。同図に示されるデータからわかるように、プラズマ処理を行ったサンプルのプローブ光の反射強度の変化(ΔR/R)の値は、プラズマ処理を行わないサンプルに比較して小さくなっている。

【0129】

したがって、本実施形態においても、上記第1の実施形態と同様に、光変調反射率分光を利用して、所望の量だけライトエッチングを行い、低抵抗の半導体領域からなるソース・ドレイン領域の形成などを行うことができる。

【0130】

特に、本実施形態のごとく、プローブ光507をウエハの表面に対して垂直方向から入射させてその反射強度を検出するようにした場合、プローブ光を基板の表面に対して傾いた方向から入射させるのに比べて、微小領域でのSiダメージ層の評価が容易に行うことができるので、モニター領域Rmnという無駄なスペースを低減できる利点がある。

【0131】

また、プローブ光507を垂直方向から入射させた場合には、反射強度も大きくなるつまり検知感度が高くなる。つまり、現実に高精度の測定を行うためには、S/N比を上げるために1カ所の測定点について何回もチョッピングを行って得たデータを積算する必要がある。ところが、プローブ光507を垂直方向から入射させた場合には、1回のチョッピングあたりの測定で高いS/N比が得られるので、チョッピング回数が低減され評価時間が短縮される。具体的には、例えばウエハの表面に対して垂直方向から入射させた場合には、45°傾いた方向から入射させた場合に比べ、評価時間が1枚あたり、15分から3分で済み評価時間を大幅に低減することができる。インラインでエッチングのダメージ層を評価する際には、この評価時間の短縮によるメリットは極めて大きいといえる。

【0132】

なお、本実施形態では、ウエハ103内に、チップ領域Rtpとは別にモニター用領域Rmnを設けたが、本発明は、斯かる実施形態に限定されるものではなく、チップ領域Rtp内に光学的評価パターンを設けても本実施形態と同様の効果が得られる。さらに、基板の表面に対して垂直方向からプローブ光を照射する場合、光学的評価パターンを別途設けなくても、コンタクト窓を直接観察することも可能である。

【0133】

また、一定時間内のライトエッチング処理による反射強度の変化割合(ΔR/R)の変動量を管理することで、装置の異常を迅速に把握し、装置トラブルが防止できる。

【0134】

上記第1,第2の実施形態では、エッチング加工をプラズマを用いたドライエッチングとしたが、本発明は斯かる実施形態に限定されるものではなく、例えばスパッタリング等によるプラズマを利用しないドライエッチングや、ウエットエッチング等に対しても適用することができる。

【0135】

また、第1,第2の実施形態は、当初に大きなダメージ層がある半導体領域に対してそのダメージ層を除去するためのエッチングだけでなく、ダメージ層がほとんどない半導体領域をエッチングしていく際のエッチングに対しても適用できる。さらに、シリコン酸化膜の形成あるは除去時における膜厚の検出や、半導体基板のアニール処理の際の結晶性の回復程度の検出など、広く半導体領域の構造に関する情報を得るために本発明の光学的評価方法を利用することもできる。

【0136】

さらに、第1,第2の実施形態では、チップ領域Rtp内の第1の半導体領域であるソース・ドレイン領域108,109と第2の半導体領域であるモニター用領域Rmn内のn型半導体領域101との不純物濃度や深さを同じとしているが、本発明は斯かる実施形態に限定されるものではなく、第1の半導体領域と第2の半導体領域の不純物濃度や不純物の導電型が異なっていてもよいものとする。あらかじめ実験を行っておけば、第1の半導体領域における適正なコンタクト抵抗を得るための第2の半導体領域における光学的特性(上記実施形態ではコンタクト抵抗)がわかるからである。たとえば、モニター領域Rmnにおける不純物濃度を特別に濃くしておいて、反射強度の変化割合の検知感度を高くしておくことも可能である。

【0137】

(第3の実施形態)

本実施形態では、光学的モニターシステムの実施形態について説明する。なお、半導体装置の加工方法は、上記第1,第2の実施形態や注記した変形可能な形態と同様に行うことができる。

【0138】

図11は、本実施形態における光学的評価装置を示す斜視図である。同図において、図8に示す構成部品と同じ構成部品には同じ符号を付している。すなわち、上記第2の実施形態と同様に、ウエハステージ504と、Xeランプ502と、ミラー506と、Arイオンレーザー503と、チョッパ510と、観測システム兼解析システム509とが設けられている。そして、本実施形態の特徴は、励起光511とプローブ光507とを同軸上に誘導するためのミラー523と、ウエハ103のn型半導体領域から反射される励起光及びプローブ光が混在した反射光518を分光するための分光器521と、該分光器521で分光された各波長における光の強度を検出するための検出器522とを備えている点である。上記Xeランプ502、ミラー506及び523、Arイオンレーザー503、チョッパ510、及び分光器521により光学システム530が構成されている。

【0139】

本実施形態の光学的評価装置においては、Xeランプ502で生成されたプローブ光507と、Arイオンレーザー503で生成された励起光511とは、ミラー523により同軸上に誘導され、ミラー506によって共に反射された後、ウエハステージ504上に設置されたウエハ103上のn型半導体領域101に送られる。そして、n型半導体領域で反射された反射プローブ光と反射励起光とが混在した反射光518は、ミラー506を通過して分光器521に送られ、検出器522によりその強度が検出された後、観測システム兼解析システム509によりその強度の変化が解析される。

【0140】

したがって、本実施形態の光学的評価装置を利用して、第2の実施形態で示した方法と同様の方法により、プラズマ処理を施したサンプルを評価することができる。加えて、本実施形態では、プローブ光と励起光とを共通の光軸に誘導してから、観測点であるウエハ103上のn型半導体領域に入射させるように構成されているので、観測点へのアライメントが非常に簡便に行うことができ、また、装置の構成が簡素になる。

【0141】

さらに、本実施形態の構成により、第2の実施形態で示している方法に比べて、より微小な半導体領域でのSiダメージ層の評価が容易に行うことができる。また、励起光も鉛直方向から入射するため、ビーム径を約30μmまで絞ることができ、45°傾いた方向から励起光を入射させる場合に比べ、さらに微少な観測点でのサンプル評価を行うことができる。また、評価時間も、第2の実施形態の約20%まで短縮することができる。

【0142】

したがって、ウエハ内にモニター領域を別途設けなくても、ウエハのLSI内に広めの半導体領域があればそれを利用してプラズマ加工のダメージ等を測定することが可能になる。

【0143】

(第4の実施形態)

図12は、第4の実施形態における光学的評価装置を示す斜視図である。同図において、図11に示す構成部品と同じ構成部品には同じ符号を付している。すなわち、上記第3の実施形態と同様に、ウエハステージ504と、Xeランプ502と、ミラー506及び523と、Arイオンレーザー503と、チョッパ510と、観測システム兼解析システム509とが設けられている。そして、本実施形態の特徴は、ウエハ103のn型半導体領域から反射されるプローブ光と励起光とが混在した反射光518のうち特定の波長範囲の光を通過させるためのフィルター525(ピーク波長が350nm)と、このフィルター525を通過した光の強度を検出するための検出器524とを備えている点である。上記Xeランプ502、ミラー506及び523、Arイオンレーザー503、チョッパ510、及びフィルター525により光学システム530が構成されている。

【0144】

本実施形態の光学的評価装置では、上記各実施形態の方法とは異なり、プローブ光の特定の波長範囲における反射強度の変化割合を分光せずに観測することができる。この方法により、評価に要する時間を数秒のオーダにまで短縮することができる。

【0145】

図13は、本実施形態の光学的評価装置を用いて、ライトエッチングを20秒間行った後におけるプローブ光の反射強度の変化割合(ΔR/R)を、RFバイアスパワーを変化させて、測定した結果を示す図である。この場合、反射プローブ光を分光してスペクトル解析するのではなく、検出器524によりフィルター525を透過した光を観測しているので、同図に示す結果は、フィルター特性から波長範囲350nmから390nmの光の強度を積分して検出していることと考えられる。図13をみると、プラズマ強度を大きくするほどプローブ光の反射強度の変化割合(ΔR/R)が低下しているので、加工領域におけるダメージが大きくなっていることがわかる。すなわち、本実施形態の方法においても、プラズマ処理の加工程度の相違による測定光の反射率の変化割合の相違を明確に検出することができた。本実施形態では、前述したように、スペクトル解析が必要でないため、評価時間は、数秒のオーダまで短縮することができた。

【0146】

(第5の実施形態)

図14は、第5の実施形態における光学的評価装置を示す斜視図である。同図において、図11と同じ構成部品には同じ符号を記している。すなわち、上記第3の実施形態と同様に、ウエハステージ504と、Xeランプ502と、チョッパ510と、分光器521と、検出器522とが設けられている。そして、本実施形態の特徴は、光学システム530内に、Xeランプ502で生成された光をプローブ507と励起光511とに分離するビームスプリッター526と、励起光511を反射させるためのミラー527と、プローブ光507を反射させ、ウエハ103からの反射光518を透過させるミラー528と、プローブ光507を透過させかつ励起光511を反射させて両者を共にウエハに導くとともに、反射光を透過させる組合せミラー529とを備えている点である。上記Xeランプ502、チョッパ521、ビームスプリッター526、ミラー527及び528、組合せミラー529、及び分光器521により光学システム530が構成されている。

【0147】

すなわち、本実施形態では、上記各実施形態とは異なり、1つの光源であるXeランプ502からの光をプローブ光507と励起光511とに分離させてから、上記各実施形態におけると同様の光変調反射率分光測定を行う。したがって、本実施形態によれば、光源が1つで済むことから光学システム530が図14に示すようにコンパクト化することができ、またレーザを用いる必要がないために低コスト、メンテナンス効率の向上を図ることができる。

【0148】

図15は、本実施形態の光学的評価装置を用いて、ライトエッチングを20秒間行った後におけるプローブ光の反射強度の変化割合(ΔR/R)を、RFバイアスパワーを変化させて、測定した結果を示す図である。図15をみると、プラズマ強度を大きくするほどプローブ光の反射強度の変化割合(ΔR/R)が低下しているので、加工領域におけるダメージが大きくなっていることがわかる。すなわち、本実施形態の方法においても、プラズマ処理の加工程度の相違による測定光の反射率の変化の相違を明確に検出することができる。

【0149】

図16は、本実施形態の光学的評価装置を用いて、波長376nm(エネルギー3.3eV)におけるプローブ光の反射強度の変化割合(ΔR/R)の初期値に対する比の時間的変化を測定した結果を示す図である。同図に示すように、ライトエッチングの進行に伴うプローブ光の反射強度の変化割合(ΔR/R)の変化は、基本的に図5に示す変化とほとんど同じである。ただし、本実施形態では、反射強度の変化割合(ΔR/R)の値そのものが図5に示す値よりも大きい。これは、励起光も上方から入力させたことで、感度が高くなったことを意味している。

【0150】

(第2〜第5の実施形態に共通のプラズマ処理装置)

図17は、上記第2〜第5の実施形態において共通に使用されるプラズマ処理装置の構造を概略的に示す断面図である。同図に示すように、プラズマ処理装置は、チャンバ200と、プラズマ発生用の高周波電力を供給するためのRF電源211と、カップリングコンデンサ212と、チャンバ200内の底部に設置された下部電極213と、チャンバ200内の天井部に設置された上部電極214と、チャンバ200の側壁に設けられた覗き窓218,219と、チャンバ200の天井部中央付近に設けられた観測用窓220とを備えている。ただし、同図においてウエハステージは図示を省略されている。そして、RF電源211から供給される高周波電力により上部電極214と下部電極213との間にプラズマ領域401を生ぜしめて、下部電極213の上に設置されたウエハ103内のn型半導体領域101を加工するように構成されている。

【0151】

そして、上記第3〜第5の実施形態においては、図17に示すように、光学システム530をチャンバ200の観測用窓220の上方にまとめて配置することができる。ただし、第2の実施形態では、プローブ光用の光学システムのみを観測用窓220の上方に配置し、励起光用の光学的システムは覗き窓218,219の側方に配置することになる。

【0152】

このようなプラズマ処理装置の構造により、ウエハ面に垂直な方向から少なくともプローブ光を入射することが可能になり、プローブ光の反射率の変化を観測することで、リアルタイムにプロセス観測を実現することができるのである。また、光学的システムからの信号531を利用して、加工条件へのフィードバック等を行うことができる。

【0153】

(第6の実施形態)

図18は、第6の実施形態における半導体装置の熱処理装置(アニール処理装置)の構成を概略的に示す断面図である。図18示すように、反応容器607内には、石英チューブ603が取り付けられており、石英チューブ603の内側面上にはウエハサセプタ602を介してウエハ103が設置されている。石英チューブ603の外側面の上には赤外線を用いたヒーター604が取り付けられており、このヒーター604によって石英チューブ603内のウエハ103を加熱するようにしている。また、反応容器607には反応ガスの導入口609と、反応ガスの排出口610とが設けられており、反応ガスの流量は流量制御計608によって適宜調整できるようになされている。また、反応容器607の側部には、2つの観測用石英窓605,606が互いに相対向して設けられている。ウエハ103の一部にはn型半導体領域101(比抵抗値約0.02Ωcm)が設けられており、一方の観測用石英窓605からウエハ103上のn型半導体領域101に入射させた光を他方の観測用石英窓606から取り出せるように構成されている。このウエハ103のn型半導体領域101には図示しないが、光学的評価のためのパターン(大きさは13×13μm2 )が設けられている。

【0154】

また、反応容器607の外には、反応容器607内に入射する測定光であるプローブ光618を発生するXeランプ611と、反応容器607内に励起光620を発生するArイオンレーザー612(出力1W)と、この励起光620を周波数200Hzでチョッピングするチョッパー614と、ウエハ103上のn型半導体領域101から反射される反射プローブ光619を受けてその強度を検出する検出器613とが配設されている。すなわち、Xeランプ611で発生したプローブ光618を評価パターンであるウエハ103上のn型半導体領域101に照射する一方、Arイオンレーザー612で発生した励起光620も周波数200Hzでチョッパー614によりチョッピングしながらウエハ103上のn型半導体領域101に照射し、励起光620の照射・非照射によるn型半導体領域101からの反射プローブ光619の強度の変化から、反射率の変動をモニターするように構成されている。そして、制御系コンピュータ615により、ヒーター604,チョッパー614及び流量制御計608の動作を制御する一方、検出器613の検出信号を取り込んでn型半導体領域101の光学的特性を監視するように構成されている。なお、チョッパ614と、反射光の強度を検出する検出器613とは同期して動作するように構成されている。

【0155】

次に、反射率の変化を利用した光学的評価方法の原理について説明する。

【0156】

測定光の反射率の変化割合とは、評価対象である半導体領域に励起光が照射されているときの測定光の反射率と励起光が照射されていないときの反射率との差ΔRを、半導体領域に励起光が照射されていないときの反射率Rで割った値(ΔR/R)である。このような測定光の反射率の変化は、以下の作用によって生じると考えられる。一般的に、半導体に光を照射すると、光によって励起されてキャリア数が増大し、その後、キャリアが元のエネルギー準位に戻る際には光を放出して消滅する。このキャリア数の変化に伴い電界強度が強くなったり弱くなったり変化する。したがって、励起光が照射されているときと、励起光が照射されていないときとでは、測定光の反射強度が異なる。そして、半導体領域の構造が完全な結晶状態である場合には、反射率の変化割合は、測定光の波長に依存して変化する。つまり、測定光の反射率の変化割合を測定光の各波長についてプロットしたスペクトルは、半導体領域を構成する半導体の伝導帯の底と価電子帯の頂上との差であるエネルギーギャップに応じた特徴的な変化特性を示す。

【0157】

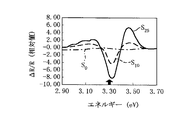

図22は、その一例を示す。つまり、エネルギーが約3.3eVに相当する波長の領域では反射率の変化割合(ΔR/R)が極小値(極値)を示し、エネルギーが3.5eVに相当する波長の領域では反射率の変化割合(ΔR/R)が極大値(極値)を示す。反射率の変化割合(ΔR/R)の極値のうち極小値の方が極大値よりも絶対値が大きい。

【0158】

ところが、半導体内に結晶学的な欠陥や電子構造の正常状態からのずれなどの構造的な乱れが多く存在すると、その領域にはエネルギー準位の低い捕獲準位が存在することになる。そして、このような構造の乱れによって生じたエネルギー準位の低い領域がキャリアの捕獲層として機能するために、キャリア数の増加量が減少し、電界強度の差が少なくなる。したがって、不純物イオンの注入によって生じた半導体領域内の構造が乱れた領域の深さや乱れの程度が大きいほど測定光の反射率の変化割合(ΔR/R)が小さくなり、構造の乱れが大きい場合には励起光の照射による測定光の反射率の変化がほとんどなくなる。つまり、このような場合には、測定光の反射率の変化割合を測定光の各波長についてプロットしたスペクトルは、ほぼ一定の小さな値を示すだけとなる。

【0159】

以上のことから、この測定光の反射率の変化割合をモニターすることにより、不純物イオンの注入後のアニールプロセスにおける半導体領域の回復の程度に関する情報を得ることができるのである。

【0160】

次に、図19及び図20を参照しながら、イオン注入後のアニールプロセスにおけるプローブ光の反射率の変化割合のスペクトルの経時変化について説明する。

【0161】

図19は、プローブ光の波長λの逆数に比例するエネルギーの値と反射率の変化割合(ΔR/R)との関係を示すスペクトル線図である。ただし、図19の横軸は実質的には測定光の波長を連続的に変化させたものにほかならないので、結局、図19は波長の変化に対する反射率の変化割合(ΔR/R)のスペクトルを示している。また、本実施形態では、照射するプローブ光618の強度は一定であるので、励起光620の照射・非照射時における反射プローブ光619の強度差ΔRを励起光620の非照射時における強度Rで割ることで、反射率の変化割合(ΔR/R)を算出している。なお、図19の反射率の変化割合(ΔR/R)の値は、初期の状態を0とする相対値である。

【0162】

熱処理工程を開始する前の状態では、反応容器607内に収納されているウエハ103上のn型半導体領域101には、すでに不純物イオン注入プロセスにおいて、ドーズ量が約1×1015cm-2、注入エネルギーが約35keVの条件で、ヒ素(As)が導入されている。図19中のスペクトル線S0 は、不純物イオンの注入直後における反射率の変化割合(ΔR/R)のスペクトルである。

【0163】

また、図19中のスペクトル線S10は、このウエハ103を図18で示す装置によりN2 ガス雰囲気中で900℃、10秒間アニール処理したときの反射率の変化割合(ΔR/R)のスペクトルであり、図19中のスペクトル線S25は同じ条件で25秒間アニールしたときの反射率の変化割合(ΔR/R)のスペクトルである。同図に示すように、アニール処理が進行するにつれて、反射率の変化割合(ΔR/R)のスペクトルの形状が大きく変化していることがわかる。つまり、このスペクトル形状は、アニール処理によるSi結晶性の回復を示すものであり、回復が進むにつれて反射率の変化割合(ΔR/R)のスペクトル線の極大側のピーク値が上方に、極小側のピーク値が下方に移動していることがわかる。

【0164】

そこで、本実施形態では、スペクトル線中でより変化幅の大きい極小ピーク値に着目し、不純物イオンの注入後のアニールプロセスにおける回復程度をスペクトル線の極小ピーク値によって監視するようにしている。ただし、図19に示すように、スペクトル線にはエネルギーが約3.3eV(波長376nm)の点で極小ピーク値があるので、反射プローブ光619のエネルギー3.3eVに相当する波長における反射率の変化割合をスペクトル線の極小ピーク値と仮定する。

【0165】

図20は、図18で示す装置を用い、反射プローブ光619のエネルギー3.3eVに相当する波長における反射率の変化割合をスペクトル線の極小ピーク値と仮定して、ウエハ103のアニールプロセスにおけるスペクトル線の極小ピーク値の経時変化を示す図である。同図に示すように、アニールプロセスの時間の経過とともに半導体領域の結晶性の回復が進行するので、極小ピーク値は時間とともに増大する。極小ピーク値が−12.0になった時点(35秒)でアニール処理を終了しても、半導体領域(本実施形態ではSi結晶)の結晶性が十分回復していることがラマン分光により確認できた。

【0166】

したがって、本実施形態では、ある程度の余裕をもって定められたアニール処理の時間ではなく、あらかじめモニターウエハーについて行った実験等より、現実のアニールプロセスにおけるスペクトル線中の極小ピーク値の変化によりアニール処理プロセスを制御することで、安定した結晶性とともに安定した不純物プロファイルを有したデバイス製造が実現できる。すなわち、アニール処理中において、特定波長(エネルギー領域)での反射率の変化割合(ΔR/R)をモニターすることにより、安定したアニール処理プロセス及び良好な特性を有するデバイス製造を実現できる。

【0167】

さらに、本実施形態では、極小ピーク値が−12.0になるまでに要する時間を管理し、その時間が、40秒を超えた時点で、本熱処理装置の定期メンテナンスを行った。図23は、ウエハの処理枚数に対するスペクトル線の極小ピーク値が−12.0になるまでのアニール時間の変化を示す。このように、ウエハの処理枚数に応じて極小ピーク値が−12.0に達するまでの時間が長くなるのは、装置構成部品の劣化によるものと考えられる。従来の管理方法では、40秒を越えるアニールを行った場合には、半導体領域におけるコンタクト抵抗不良などのトラブルが発生していたが、本発明の管理手法によれば、そのようなトラブルの発生を抑制することができる。すなわち、本実施形態の光学的な管理手法とプロセス時間管理手法の融合により、従来の方法では困難であった熱処理工程のプロセス管理をも実現することができ、よって、安定した稼動を達成することができる。

【0168】

なお、第6の実施形態において、図18に示す光学的モニターシステムに代えて、第2の実施形態における図8に示す光学的モニターシステムや、第3の実施形態における図9に示す光学的モニターシステム、第4の実施形態における図12に示す光学的モニターシステム、第5の実施形態における図14に示す光学的モニターシステムなどを使用することができる。

【0169】

(第7の実施形態)

次に、不純物濃度の計測方法に関する第2の実施形態について説明する。

【0170】

本実施形態では、上記第2の実施形態で使用した図8に示す光学的モニターシステムを用いる。

【0171】

ただし、本実施形態では、励起光511はチョッパ510によって周波数100Hzでチョッピングされて、ウエハ103のn型半導体領域103aに間欠的に照射される。そして、この観測システム兼解析システム509で計測された反射強度に関するデータは、信号線を介して熱処理制御システム(図示せず)に送られる。また、チョッパ510と、反射プローブ光の強度を検出する検出器とは同期して動作するように構成されている。

【0172】

図21は、実際に観測して得られた反射率の変化割合のスペクトル線における極小ピーク値と不純物導入の際の不純物のドーズ量との関係を示す。不純物はヒ素(As)であり、実験を行ったドーズ量は1.0×1015cm-2、5.0×1015cm-2、5.0×1014cm-2、1.0×1014cm-2であり、いずれの場合にもイオンの加速エネルギーは150keVである。また、熱処理は、N2 ガス雰囲気中で、850C、1時間行っている。図22には、ドーズ量が1.0×1015cm-2の場合の反射率の変化割合(ΔR/R)のスペクトルを示す。

【0173】

図21からわかるように、不純物が導入されたサンプルの反射率の変化割合(ΔR/R)の極小ピーク値は、ドーズ量の増加とともに負の側に大きくなっていくことがわかる。すなわち、反射率の変化割合(ΔR/R)が不純物濃度を反映したものであり、反射率の変化割合(ΔR/R)をモニターすることにより、熱処理後の最終的な基板内の不純物濃度を知ることができることを意味している。したがって、この極小ピーク値がある値になるまで不純物のイオン注入と拡散用の熱処理とを行うことにより、n型半導体領域101における所望の不純物濃度に正確に制御することが可能になる。

【0174】

なお、上記第6,第7の実施形態では、不純物イオンの注入により生じた欠陥等に起因する構造の乱れを回復させるための熱処理工程について説明したが、本発明の熱処理はかかる実施形態に限定されるものではなく、エッチングによって生じた欠陥などに起因する構造の乱れを回復させるための熱処理工程についても適用されるものである。

【0175】

なお、第7の実施形態において、図8に示す光学的モニターシステムに代えて、第3の実施形態における図9に示す光学的モニターシステムや、第4の実施形態における図12に示す光学的モニターシステム、第5の実施形態における図14に示す光学的モニターシステムなどを使用することができる。

【0176】

(第8の実施形態)

以下、図24〜図29を参照しながら、第8の実施形態に係る半導体装置(絶縁膜)の光学的評価装置及び評価方法について説明する。

【0177】

図24は、本実施形態に係る絶縁膜の光学的モニターシステムの構成を概略的に示す斜視図である。図24において、701はシリコン酸化膜が形成されたウエハ状態の半導体基板、702はウエハステージ、703は出力150Wの第2の光源であるXeランプ、704は偏光子、705は検光子を備えた検出器、706はXeランプ光であるプローブ光(測定光)、707は反射プローブ光、708は検出器705からの信号を伝達するための信号線、709は出力が5Wの第1の光源であるArイオンレーザ、710は励起光を変調するためのチョッパー、711はチョッパー710により変調された励起光である励起光、712は励起光の変調との同期信号を伝達するための信号線、713は制御システムをそれぞれ示す。そして、検出器705は、反射プローブ光707の強度を各波長について連続的なスペクトルを測定するように構成されている。また、励起光711は、チョッパー710によって周波数500Hzでチョッピングされて、半導体基板701の表面に対して垂直な方向から半導体基板701の被測定領域に間欠的に照射されるように構成されている。さらに、チョッパ710と、反射光の強度を検出する検出器705とは同期して動作するように構成されている。

【0178】

一方、図25に示すように、被測定領域である半導体基板701のn型半導体領域701b上には、たとえば温度850℃下の熱酸化法によりシリコン酸化膜701cが形成されている。プローブ光706はこのシリコン酸化膜701cを通過してその直下のn型半導体領域701bに入射され、n形半導体領域701bの表面で反射される。そして、この反射プローブ光707は、シリコン酸化膜701cを通過して外方に出射される。

【0179】

ただし、図24において図示されていないが、例えば図18に示すような構造と類似した熱酸化を行うためのチャンバーが配置されており、ウエハステージ702はこのチャンバー内に設置され、チャンバーにはプローブ光706、反射プローブ光707及び励起光711を通過させるための窓が設けられている。

【0180】

ここで、光変調反射率分光法の基本的な原理と、本実施形態に係る反射プローブ光707の反射強度の変化割合(ΔR/R)の測定方法とについて説明する。

【0181】

一般的に、半導体に光を照射すると、光によって励起されてキャリア数が増大し、その後、キャリアが元のエネルギー準位に戻る際には光を放出して消滅する。このキャリア数の変化に伴い半導体領域の表面電界強度が変化する。したがって、励起光が照射されているときと励起光が照射されていないときとでは、測定光が半導体領域の表面で反射される割合つまり測定光の反射率が異なる。すなわち、励起光の照射によって生じるべき電界強度の変化の大きさが被測定領域の何らかの特性に依存して変わるのであれば、測定光の反射率の変化割合を測定することにより、被測定領域の特性を評価できるはずである。本発明は、このような光変調反射率分光の技術を前提としている。

【0182】

そこで、本実施形態では、まず、被測定領域である半導体基板701のシリコン酸化膜701cを通過させてその直下のn型半導体領域701bに励起光711を間欠的に照射しながら、別の方向からプローブ光706を連続的にシリコン酸化膜701cを通過させてその直下のn型半導体領域701bに照射して、反射プローブ光707の反射強度の変化を検出する。そして、励起光711が照射されているときと照射されていないときの反射プローブ光707の反射強度の差ΔRを、励起光711が照射されていないときの反射強度Rで割った値(ΔR/R)が反射強度の変化割合として解析システム713で検知される。ここで、反射強度の変化割合(ΔR/R)は、照射されるプローブ光706の強度が一定であることを前提として、反射率の代わりに使用されているものであり、技術的に意味があるのは反射率の変化割合である。以上の構成により、プローブ光の反射強度の変化割合の変動がモニターされる。そして、図24に示す解析システム713のディスプレイ上には、図示するような測定光の反射強度の変化割合(ΔR/R)のスペクトルが表示される。

【0183】

図26は、上記検出器705によって測定された反射強度の変化割合(ΔR/R)のスペクトルを示す。同図において、曲線Spaは正常なシリコン酸化膜を有する半導体基板からの反射強度の変化割合(ΔR/R)のスペクトルを示し、曲線Spb,Spcは不良のシリコン酸化膜を有する半導体基板からの反射強度の変化割合(ΔR/R)のスペクトルを示す。これらの反射強度の変化割合(ΔR/R)のスペクトルの形状の相違から、良品の半導体基板の反射強度の変化割合(ΔR/R)はある一定の範囲(同図の斜線で示す領域)に収まるのに対し、不良のシリコン酸化膜を有する半導体基板からの反射強度の変化割合(ΔR/R)はこの範囲からはみ出るほど大きいということがわかった。このような相違が生じる原因については、以下の作用によるものと考えられる。

【0184】

図27(a)に示すように、シリコン酸化膜を通過させてその直下のn型半導体領域に励起光711を照射するとn型半導体領域にキャリアが発生し、このキャリア数の変化に伴い表面電界強度がΔΦだけ増大する。この表面電界強度の変化ΔΦが生じることで、励起光が照射されているときと照射されていないときとで反射強度が異なることは、既に説明したとおりである。ここで、n型半導体領域の上にシリコン酸化膜が形成されていると、n型半導体領域の表面層にキャリアのトラップとなる欠陥サイトが発生するので、測定光の反射率の変化分は小さくなるはずである。

【0185】

ところが、図27(b)に示すように、シリコン酸化膜中にトラップ電子が存在していると、この電子によってn型半導体領域にはより大きな表面電界強度の変化ΔΦ’が生じることになる。このために、トラップ電子が多く存在するシリコン酸化膜の直下のn型半導体領域から反射強度の変化割合(ΔR/R)は、トラップ電子が少ないシリコン酸化膜の直下のn型半導体領域からの反射強度の変化割合(ΔR/R)よりも大きくなると考えられる。つまり、図26に示すような反射強度の変化割合(ΔR/R)の大きいスペクトルSpb,Spcを与える半導体基板のシリコン酸化膜には多くのトラップ電子が存在していることになる。このようなトラップ電子は、シリコン酸化膜の欠陥が多いほど多く存在することは知られている。なお、トラップ電子が多く存在していると、絶縁破壊によるキャリアパスが発生しやすくなり、絶縁膜の寿命が短いこともわかっている。

【0186】

そこで、発明者は、上記推論を裏付けるために、厚みが2〜4nm程度のシリコン酸化膜に電気的ストレスをその大きさを種々に変えて印加する実験を行って、図28に示すデータを得た。図28は、反射強度の変化割合(ΔR/R)のスペクトル中のピーク強度と、水銀プローバによる容量の測定より得られたおのおのの酸化膜中のトラップ電子密度との関係を示す図である。同図において、縦軸はトラップ電子密度(×1011cm2 )を示し、横軸は反射強度の変化割合(ΔR/R)のスペクトル中の3.35eV付近の極小ピーク値(波長375nm付近に対応する)を与えるピーク信号強度の相対値をとっている。図28に示すように、ピーク信号強度の絶対値が増大するほどトラップ電子密度も増大しているので、反射強度の変化割合(ΔR/R)の絶対値がある範囲よりも大きいときにはシリコン酸化膜の品質がよくない(つまりトラップ電子が多く存在している)と評価することができる。

【0187】

すなわち、反射強度の変化割合(ΔR/R)(絶対値)が所定値以上であればゲート酸化膜を不良と判定することは、上述のような推論が理論的に正しいかどうかは別にして、経験的に得られる因果関係に合致している。したがって、反射強度の変化割合(ΔR/R)をモニターすることにより、絶縁膜中の電子トラップ量を特定できるため、絶縁膜の電気的特性の管理を光学的に行うことができる。

【0188】

次に、このような光学的評価により半導体デバイスの製造における工程管理を行った実施例について説明する。

【0189】

図29に示すように、反射強度の変化割合(ΔR/R)のスペクトル中のピーク値が−0.25〜0.25×10-3の範囲に収まるのであれば良品とし、逆にこの範囲に収まらないのであれば不良と設定して、半導体基板(ウエハ)の上に熱酸化によりシリコン酸化膜を試作する際の工程管理を行った。図29において、横軸は処理枚数を示し、縦軸は3.35eV付近における反射強度の変化割合(ΔR/R)(ピーク値)である。125枚ごとに1回の割合でモニターした結果、750枚目のところで突如信号が大きく変化した。これは、突発的なトラブルであり、このときのゲート酸化膜の特性は、ゲートへの印加電圧Vgが−6.6Vのときに、信頼性を示す破壊までの時間tbd(寿命値)が100sec程度であった。通常の寿命値tbdは104 sec以上であるから、この寿命値は異常に低い値であることがわかる。この場合、迅速なトラブルへの対応によってトラブルの原因を取り除くことができ、その後の不良の発生を防止することができた。このように、本発明では、光学的な特性評価による製造工程の管理を行うことにより、従来の電気的特性の評価による管理よりも迅速な対応ができ、サンプルの試作工程や、MOSデバイスの製造工程における歩留まりの悪化を確実に防止することができる。

【0190】

なお、予め実験を行って、適正な電子トラップ密度に対応する容量(電気的特性)の適正範囲と、この適正範囲に相当する反射強度の変化割合(ΔR/R)の適正範囲との関係を求めておけば、反射強度の変化割合(ΔR/R)が適正範囲に入るように製造条件を制御することができる。

【0191】

なお、本実施形態において、図24に示す光学的モニターシステムに代えて、第2の実施形態における図8に示す光学的モニターシステムや、第3の実施形態における図9に示す光学的モニターシステム、第4の実施形態における図12に示す光学的モニターシステム、第5の実施形態における図14に示す光学的モニターシステムなどを使用することができる。

【0192】

また、本実施形態における光学的モニターシステムにおいて、測定光の光源の選定により、あるいはフィルターの取り付けにより、600nm以下、より好ましくは300〜600nmの波長範囲の測定光を半導体領域に照射するようにすることが好ましい。かかる波長範囲の光は、半導体領域への侵入深さが数10nm以上にならないので、シリコン酸化膜等の絶縁膜内のトラップ電子の影響を受けやすい表面領域からの反射光の強度の差に基づき感度の高い光学的評価を行うことができる。

【0193】

(第9の実施形態)

次に、第9の実施形態について説明する。図30(a)〜(c)は、ゲート電極及びゲート酸化膜のパターニング工程を示すウエハの断面図である。ただし、本実施形態では、第1の実施形態における図4に示すエッチング装置を使用して、ゲート電極及びゲート酸化膜のパターニングを行うものとする。

【0194】

まず、図30(a)に示す工程の前に、ウエハ803上のチップ領域Rtpの基板領域には、しきい値制御用の低濃度の不純物が導入された第1半導体領域800が設けられており、この第1半導体領域800に半導体素子であるMOSトランジスタが形成される。一方、ウエハ803上のモニター領域Rmnには、広さが例えば13×13μm2 のn型不純物が導入された第2半導体領域801(比抵抗値が約0.02Ωcm)が形成されている。そして、基板の全面上には、厚みが例えば6nmのゲート酸化膜807と、ポリシリコンからなるゲート電極膜806とが堆積されている。さらに、ゲート電極膜806の上には、ゲート電極形成用のパターン形状を有するフォトレジストマスク809が形成されている。ただし、このフォトレジストマスク809は、第2半導体領域801の上方にも開口領域を有している。

【0195】

次に、図30(b)に示す工程において、フォトレジストマスク809を用いたドライエッチング(プラズマエッチング)により、ゲート電極膜806が除去され、ゲート電極806aが形成される。このとき、第2半導体領域801のゲート電極膜が除去されて、ゲート酸化膜807が露出した状態となっている。

【0196】

そして、この状態で、励起光402及びプローブ光403がゲート酸化膜807を通って第2半導体領域801に照射される。ただし、励起光402は間欠的に照射される。そして、上述のように、励起光402が照射されているときと照射されていないときのプローブ光403の反射強度の差ΔRを励起光402の照射がないときの反射強度Rで割った値(ΔR/R)が反射強度の変化割合として図4に示す反射強度観測システム220で検知される。以上の構成により、反射強度の変化割合の変動がモニターされる。

【0197】

次に、図30(c)に示す工程で、ゲート酸化膜807のパターニングが完了して、ゲート電極806aの直下にゲート酸化膜807aが残される状態になる。ここで、本実施形態では、このようにエッチングが完了した時点では、第2の半導体領域801におけるプローブ光の反射率の変化割合(ΔR/R)が図30(b)に示すときの値よりも大きく変化している点に着目する。

【0198】

図31は、ゲート酸化膜が除去されていくときのプローブ光の反射率の変化割合(ΔR/R)を示すスペクトル線図である。図30(b)のようにゲート酸化膜が存在しているときには、ゲート酸化膜中のトラップ電子の存在によってピーク値の絶対値が大きいスペクトル線となるが、ゲート酸化膜が除去されるにつれてピーク値の絶対値が小さいスペクトル線(例えば図31に示すスペクトル線Slow )を示すように変化する。さらにゲート酸化膜の除去が進むと、トラップ電子数が極めてわずかになり、しかもシリコン基板にはダメージ層もほとんどないことから、ピーク値の絶対値が増大するように転ずる。そして、図30(c)に示すゲート酸化膜の除去が完了した時点では、ピーク値が大きいスペクトル線Shighを示す。したがって、プローブ光の反射率の変化割合(ΔR/R)をモニターし続けることにより、基板内にほとんどダメージが入らずしかもゲート酸化膜の除去が完了した時点を検知することができる。すなわち、ゲート酸化膜の除去が完了して時点でエッチングを停止するようにドライエッチング工程を制御することができ、シリコン基板へのダメージをできるだけ小さくすることができる。

【0199】

ただし、本実施形態のエッチング工程の制御方法は、ゲート酸化膜の除去だけでなく、測定感度が有効に得られない程度に厚い絶縁膜でさえなければ、他の絶縁膜の除去のためのエッチングにも適用することができる。

【0200】

(第10の実施形態)

次に、第10の実施形態について説明する。本実施形態では、ウエハの図示は省略するが、例えば上記第9の実施形態の図30(c)に示す状態で、第1の半導体領域800にソース・ドレイン領域を形成するための不純物導入を行う工程に適用できるものである。

【0201】

図32は、BF2 とHeの混合ガスを用い圧力10mTorrで、プラズマドーピングを行って半導体領域内に不純物を導入していく過程において、プローブ光の反射率の変化割合(ΔR/R)をモニターした結果を示す図である。同図において、横軸は処理時間を、縦軸は極小ピーク値の信号強度(相対値)の絶対値を示す。同図に示されるように、不純物の導入につれて信号強度が低下してきており、不純物の導入によって半導体領域内に欠陥が生じていることがわかる。したがって、プローブ光の反射率の変化割合(ΔR/R)が初期値から所定値または所定割合だけ小さくなったときに不純物の導入を停止させたり、予め実験を行って所望の不純物濃度に対応する信号強度を求めこの信号強度に達したときに不純物の導入を停止するなどの制御を行うことにより、所望の濃度の不純物を導入することができる。

【0202】

さらに、上記プラズマドーピングやイオン注入などによる不純物の導入後に熱処理を行い、熱処理後に光変調反射率測定を行って測定光の反射率の変化割合(ΔR/R)を評価すれば、熱処理後の不純物の濃度がわかる。したがって、予め予備実験を行って適正な不純物濃度を実現するための不純物導入条件(例えばイオン注入量,イオン注入エネルギーやプラズマドーピング時の高周波電力など)を決定しておくことができる。特に、不純物導入前における半導体領域についてインラインでの光変調反射率測定を行って、その工程での半導体領域の不純物の濃度を把握しておけば、より精度のよい不純物導入を行うことができる。

【0203】

ただし、本実施形態においても、半導体素子が形成される領域とは別の領域に光学的評価用のモニター領域を設けておくことができる。

【0204】

(その他の実施形態)

なお、上記各実施形態における光学的モニターシステムのうちXeランプ,偏光子,検出器等は、現在酸化膜の膜厚の測定のために使用されているエリプソメトリ分光器の部材をそのまま利用することができる。その場合、Arイオンレーザ,チョッパー及び制御システムを新たに設けるだけで、本発明の光学的評価を行うことができる。

【0205】

また、上記各実施形態では、MOSトランジスタを形成する場合を例にとって説明したが、バイポーラトランジスタや、化合物半導体基板に形成されるMESFETなどのデバイスを形成する場合にも適用することができる。

【0206】

【発明の効果】

請求項1から3または4から5によれば、チャンバー内で半導体領域を有する基板に処理を施す際に使用される光学的評価装置として、光変調反射率測定により半導体領域からの測定光の反射率の変化割合を演算する構成としたので、半導体領域の結晶状態などを反映した反射率の変化割合によって得られる情報を利用して、チャンバー内で行われる加工処理の条件を制御する際のインラインでの評価を行うことができる。

【0207】

請求項6から17によれば、半導体領域上の絶縁膜の電気的特性を評価するための光学的評価装置として、光変調反射率測定により半導体領域からの測定光の反射率の変化割合を演算して、この反射率の変化割合の大小に基づき上記絶縁膜の電気的特性を評価する構成としたので、ゲート酸化膜等の絶縁膜中の電気的な欠陥についての情報が得られ、迅速かつ確実な絶縁膜の電気的特性の管理に供することができる。

【0208】

請求項18から21によれば、チャンバー内で半導体領域の加工処理を行う半導体装置の製造装置において、上述のような光学的評価装置の機能を付設する構成とし、反射率の変化割合に基づき加工処理条件を制御するようにしたので、チャンバー内で行われる加工処理の条件をインラインでの評価に基づいて制御することができ、よって、所望の特性を有する半導体装置を再現性よく形成することができる。

【0209】

請求項22から27によれば、チャンバー内で加工処理を施す際に加工処理の状態を評価するための光学的評価方法として、光変調反射率測定により半導体領域からの測定光の反射率の変化割合を演算するようにしたので、半導体領域の結晶状態などを反映した測定光の反射率の変化割合を利用して、加工処理の条件を制御するためのインラインでの光学的評価方法の提供を図ることができる。

【0210】

請求項28から40によれば チャンバー内で上述のような光変調反射率測定を行う半導体装置の製造装置の管理方法として、チャンバー内で上記基板に加工処理を施しながら、測定光の反射率の変化割合が所定値に達するまでの所定時間を監視して、所定時間が限界値を超えると装置のメンテナンスを行うようにしたので、チャンバー内の構成部材の劣化を検知して適正なタイミングでメンテナンスを行うことができ、よって、加工処理時間の過大に起因する半導体領域の不良の発生を回避することができる。

【図面の簡単な説明】

【図1】 実施形態に係る半導体装置の製造方法を示すフローチャート図である。

【図2】 実施形態に係る半導体装置の製造工程を示すウエハの断面図である。

【図3】 実施形態に係るウエハの上面図である。

【図4】 実施形態に係る半導体装置の製造装置であるプラズマ処理装置の断面図である。

【図5】 実施形態におけるエッチング時間とプローブ光の反射強度の変化割合との関係を示す特性図である。

【図6】 実施形態におけるエッチング時間とコンタクト抵抗との関係を示す特性図である。

【図7】 実施形態のライトエッチング方法と従来のライトエッチング方法とをそれぞれ用いて形成された半導体装置のコンタクト抵抗値のバラツキの相違を示す図である。

【図8】 第2の実施形態に係る半導体装置の光学的モニターシステムを概略的に示す斜視図である。

【図9】 第2の実施形態に係る半導体装置の製造工程を示すウエハの断面図である。

【図10】 第2の実施形態のプラズマ処理を行ったサンプルとプラズマ処理を行っていないサンプルとについて、励起光の強度−プローブ光の反射率変化特性の相違を示すデータである。

【図11】 第3の実施形態に係る半導体装置の光学的モニターシステムを概略的に示す斜視図である。

【図12】 第4の実施形態に係る半導体装置の光学的モニターシステムを概略的に示す斜視図である。

【図13】 第4の実施形態の光学的モニターシステムを利用して、20秒間ライトエッチングを行ったときのプローブ光の反射強度の変化割合をRFパワーを変化させてプロットした図である。

【図14】 第5の実施形態に係る半導体装置の光学的モニターシステムを概略的に示す斜視図である。

【図15】 第5の実施形態の光学的モニターシステムを利用して、20秒間ライトエッチングを行ったときのプローブ光の反射強度の変化割合をRFパワーを変化させてプロットした図である。

【図16】 第5の実施形態におけるエッチング時間とプローブ光の反射強度の変化割合との関係を示す特性図である。

【図17】 第3〜第5の実施形態の光学的モニターシステムをプラズマ加工装置に取り付けた状態を概略的に示す断面図である。

【図18】 第6の実施形態に係る半導体の熱処理装置の構成を概略的に示す断面図である。

【図19】 第6の実施形態におけるアニール処理時間による反射率の変化割合のスペクトル形状の変化を示すスペクトル線図である。

【図20】 第6の実施形態におけるアニール処理時間に対する極小ピーク値の変化を示す図である。

【図21】 第7の実施形態におけるイオン注入時のドーズ量と極小ピーク値との関係を示す図である。

【図22】 ヒ素イオンがドーズ量1×1015cm-2で導入され熱処理が施された後の反射率の変化割合のスペクトル線図である。

【図23】 第6の実施形態における熱処理中の極小ピーク値が所定値に達するまでの所要時間のウエハ処理枚数に対する変化を示す図である。

【図24】 第8の実施形態に係る光学的評価装置の構成を部分的に斜視図で示すブロック図である。

【図25】 第8の実施形態で光学的評価を行うために使用した被測定物の構造を示す断面図である。

【図26】 第8の実施形態におけるプローブ光の半導体領域からの反射強度の変化割合に関する信号のスペクトル図である。

【図27】 励起光が照射されたときのシリコン酸化膜とn型半導体領域におけるエネルギーバンド図と、励起光が照射されないときのシリコン酸化膜及びn型半導体領域におけるエネルギーバンド図である。

【図28】 プローブ光の反射強度の変化割合のスペクトル中のピーク強度と酸化膜中のトラップ電子の密度との関係を示す図である。

【図29】 第8の実施形態を利用して光学的評価を試作品の酸化工程の管理に使用した場合におけるウエハ処理枚数と3.35eV付近の反射強度の変化割合との関係を示す図である。

【図30】 第9の実施形態に係る半導体装置の製造工程を示すウエハの断面図である。

【図31】 第9の実施形態における測定光の反射率の変化割合の変化を示すスペクトル線図である。

【図32】 第10の実施形態におけるプラズマドーピングの処理時間と測定光の反射率の変化割合のピーク強度との関係を示す図である。

【符号の説明】

101 n型半導体領域

103 ウエハ

104 層間絶縁膜

105 フォトレジストマスク

106 ゲート電極

107 ゲート酸化膜

108 n型ソース領域

109 n型ドレイン領域

110a〜c 開口

200 反応処理室

211 高周波電源

212 カップリングコンデンサ

213 アノード電極

214 カソード電極

215 終点検出用窓

216 終点検出システム

217 ミラー

218 プローブ光入射用窓

219 反射光観測用窓

220 反射強度観測システム

221 信号経路

222 エッチング制御システム

223 チョッパ

301 Arイオンレーザー(第1の光源)

302 Xeランプ(第2の光源)

401 プラズマ

402 励起光

403 プローブ光

404 反射プローブ光

502 Xeランプ(第2の光源)

503 Arイオンレーザー(第1の光源)

504 ウエハステージ

505 顕微鏡システム

506 ミラー

507 プローブ光

508 反射プローブ光

509 観測システム兼解析システム

510 チョッパ

511 励起光

512 反射励起光

513 反射励起光観測システム

525 フィルター

530 光学システム

701 半導体基板

701a 本体部

701b n型半導体領域

701c シリコン酸化膜

702 ウエハステージ

703 Xeランプ(第2の光源)

704 偏光子

705 検出器

706 プローブ光

707 反射プローブ光

708 信号線

709 Arイオンレーザ(第1の光源)

710 チョッパー

711 励起光

712 信号線

713 制御・解析システム

Rtp チップ領域

Rmn モニター領域

Rdm1〜3 ダメージ層[0001]

BACKGROUND OF THE INVENTION

The present invention relates to an optical evaluation apparatus and an optical evaluation method suitable for in-line characteristic evaluation in a semiconductor device manufacturing process., HalfHow to manage conductor equipment manufacturing equipment and semiconductor equipment manufacturing equipmentTo the lawRelated.

[0002]

[Prior art]

In recent years, high integration of semiconductor integrated circuits has been greatly advanced, and in a MOS type semiconductor device, transistor elements have been miniaturized and high performance has been achieved. Realization of highly functional MOS devices has become necessary. In order to improve the reliability of the MOS device, it is necessary that each part constituting the MOS device has high reliability.

[0003]

An important part that affects the reliability of such a MOS device is, for example, the reliability of the contact portion that is affected by the method of forming the contact window. The damage layer of the semiconductor substrate caused by dry etching used to form the contact window is removed by wet etching after dry etching. By measuring the electrical characteristics of a wafer, etc., the depth of the damaged layer generated under the dry etching conditions can be ascertained, or wet etching to remove the damaged layer from the measurement result of the electrical characteristics. Conditions such as time and temperature are set. In this manner, in the conventional method for manufacturing a semiconductor device, control is performed so that the processing conditions during the manufacturing process of the semiconductor device are appropriate based on the electrical characteristics obtained using the monitor wafer.

[0004]

Further, among the processes for forming each element of the semiconductor device, for example, the impurity introduction technique is an important process for determining the operating characteristics of the semiconductor device. For the introduction of impurities, an ion implantation method, that is, a method in which ions are accelerated by an electric field and the impurity ions are introduced into a semiconductor substrate or an electrode is the mainstream. At this time, the impurity ions are usually accelerated with an energy of several tens of keV and implanted into a semiconductor substrate or the like. However, as a result of the implantation of the impurity ions, a damaged layer having broken crystallinity is generated on the surface layer of the semiconductor substrate or the like, the impurities are not activated as carriers, and the impurity concentration distribution is also desired. It is not in the distribution state. Therefore, heat treatment (annealing) is performed after ion implantation in order to activate impurities, recover damage, and optimize profiles. Conventionally, the annealing process time, temperature, and the like are determined by design (device simulation) and optimization of conditions, and basically, annealing conditions are set based on experience. In particular, the annealing process for recovering the surface defect layer of the semiconductor substrate has been based on experience.

[0005]

Next, gate insulating films used in MOS devices are rapidly becoming thinner, and it is expected that very thin insulating films of 4 nm or less will be used in the 21st century. In MOS devices having such an extremely thin insulating film, it is said that the characteristics of the insulating film determine the characteristics of the entire MOS device and further the electrical characteristics of the entire semiconductor integrated circuit, and the characteristics of the insulating film are particularly important. Is being viewed.

[0006]

The characteristics of such a gate insulating film have been conventionally managed by forming a MOS capacitor or a MOS transistor and evaluating the electrical characteristics. The evaluation of the electrical characteristics is performed by taking out the wafer on which the MOS device is mounted from the chamber during or after the manufacture of the MOS device.

[0007]

[Problems to be solved by the invention]

By the way, with the miniaturization of the MOS device as described above, the above-described conventional evaluation method has the following problems in the above etching process, impurity introduction process, and gate insulating film formation process.

[0008]

First, the etching process has the following problems. While the planar size (lateral size) of the contact window is reduced, the depth of the contact window must not be reduced, and as a result, the aspect ratio (= depth / lateral size) is increased. In order to form a contact window having such a high aspect ratio, for example, a high vacuum / high density plasma is used in a dry etching process. In the high-vacuum and high-density plasma process, deep contact windows are formed using ions with high energy and directivity. However, unlike the conventional level of defects caused by dry etching with relatively low vacuum and low density plasma due to the impact of high energy ions, the depth of damage layer and damage caused by the semiconductor crystal at the bottom of the contact The degree is getting bigger. Also, when evaluating the damage layer using light in the microwave region (infrared rays or the like), the light itself penetrates from the Si substrate to a depth of 1 μm or more, so that damage to the Si substrate at a level of several tens of nanometers by actual plasma Could not be accurately evaluated. That is, with the miniaturization of LSIs in the future, it has become impossible to give an accurate result to the evaluation of a damage layer that is thinly formed near the surface layer or an extremely miniaturized region.

[0009]

Therefore, it is difficult to remove the damaged layer reliably or to remove the damaged layer with good control only by using the conventional evaluation method.

[0010]

Next, there are the following problems in the impurity introduction process and the annealing process. As each element in a semiconductor device is miniaturized and the importance of impurity introduction and profile control in a minute region increases, the setting of annealing conditions based on the above experience often results in an optimum profile. There was no result, and there was a problem that the processing was finished with defects remaining in the semiconductor substrate. In addition, there is an urgent need to shorten the development period of the desired semiconductor device. If the annealing conditions are optimized by the conventional process → analysis → process → analysis procedure, the development efficiency is significantly reduced. End up. Therefore, recently, a process control technique based on an in-situ observation technique of the annealing process has been eagerly desired. In addition, when performing heat treatment using a single-wafer type heat treatment apparatus, unlike the conventional batch type, subtle variations in the amount of heat treatment between wafers have occurred due to variations in the characteristics of the heat treatment apparatus and changes over time. . Furthermore, it has been difficult to accurately grasp the actual dose amount at the time of impurity introduction and the effective impurity concentration introduced into the substrate after the heat treatment.

[0011]

In the process of forming the gate insulating film, there are the following problems. When managing the characteristics of the gate insulating film by evaluating the electrical characteristics as described above, the process is completed even if any trouble occurs in the insulating film formation process during the manufacture of the MOS device. The defect is found only after the wafer is taken out of the chamber and the electrical characteristics are evaluated. Therefore, until then, a defective gate insulating film is continuously formed, resulting in a decrease in productivity (efficiency).

[0012]

The first object of the present invention is to provide an optical evaluation apparatus and method capable of reliably grasping in-line the factors affecting the characteristics of the semiconductor device during the manufacturing process as described above and realizing good and uniform characteristics. It is to provide.

[0013]

The second object of the present invention is to pay attention to the fact that there is a correlation between the optical characteristics of the semiconductor region and the state of the semiconductor region, and inline various processes for the semiconductor device using the evaluation of the optical characteristics. Controlled semiconductor devicesSetIt is to provide a manufacturing apparatus.

[0014]

A third object of the present invention is to provide a semiconductor device manufacturing apparatus management method for performing maintenance of a chamber of a semiconductor device manufacturing apparatus using a change in evaluation accuracy of optical characteristics.

[0015]

[Means for Solving the Problems]

In order to achieve the first object, the present invention provides a first claim.To 3Means relating to the first optical evaluation device described in

[0016]

In order to achieve the second object, the present invention claims18 to 21For manufacturing apparatus of semiconductor device described in 1TheI'm taking it.

[0017]

In order to achieve the third object, the present invention claims28 to 40The measures regarding the management method of the manufacturing apparatus of the semiconductor device described in 1 are taken.

[0018]

A first optical evaluation apparatus according to the present invention is an optical evaluation apparatus used when a substrate having a semiconductor region is processed in a chamber, as described in

[0019]

By using this optical evaluation device, the following effects can be obtained. When excitation light guided by the first light guiding member is irradiated onto the semiconductor region, carriers in the semiconductor region are excited and an electric field is generated by the carriers. Due to this electric field, the reflectivity of the measurement light guided to the semiconductor region by the second light guide member changes with and without excitation light irradiation, and this rate of change depends on the magnitude of the electric field strength and the measurement. It varies depending on the wavelength of light. On the other hand, if there is a defect that becomes a recombination center of carriers in the semiconductor region, the lifetime of the excited carriers is shortened, so that the electric field strength formed by the carriers is reduced. In other words, since the rate of change in reflectivity with and without excitation light irradiation changes depending on the number of defects in the semiconductor region, the change calculation means uses the detection value of the reflectivity detection means to detect the semiconductor region. When the change rate of the reflectivity of the measurement light at is calculated, the change rate of the reflectivity reflects the crystal state of the semiconductor region and the like. Therefore, it is possible to control the conditions of the processing performed in the chamber based on the in-line evaluation of the semiconductor region.

[0020]

In addition, since the light source is unified, the structure of the optical evaluation device is extremely simplified.

[0021]

According to a second aspect of the present invention, in the first aspect, the second light guide member transmits the measurement light to the surface of the substrate.DrippingIt is preferable that the light is incident from a straight direction.

[0022]

This allows the measurement light to beDrippingSince it is configured to irradiate from a straight direction, a change in reflectance can be evaluated quickly and accurately for a minute semiconductor region. That is, an optical evaluation apparatus capable of performing optical evaluation in the manufacturing process of a semiconductor device to be miniaturized is obtained.

[0023]

According to a third aspect of the present invention, in the second aspect, the first light guiding member transmits the excitation light to the surface of the substrate.DrippingIt is preferable that the light is incident from a straight direction.

[0024]

ThisMeasurement light and excitation light are on the surface of the semiconductor regionDrippingSince the light is irradiated from a straight direction, even when the semiconductor region is extremely narrow, it is possible to perform optical evaluation using the change rate of the reflectance of the measurement light. Therefore, an optical evaluation device particularly suitable for detecting the processing state in the semiconductor region in real time can be obtained.

[0025]

A second optical evaluation apparatus according to the present invention is an optical evaluation apparatus used when processing a substrate having a semiconductor region in a chamber as described in claim 4, wherein the excitation light A first light source that generates the measurement light, a second light source that generates the measurement light, and an excitation generated by the first light source. A first light guiding member for intermittently irradiating the semiconductor region of the semiconductor substrate in the chamber with a first light guide member for irradiating the semiconductor region with the measurement light generated by the second light source. 2 light guide members, reflectance detection means for detecting the reflectance of the measurement light applied to the semiconductor region, and measurement light reflected from the semiconductor region for entering the reflectance detection means The difference in reflectance of the measurement light between the third light guide member and the output of the reflectance detection means and when the semiconductor region is irradiated with excitation light and when excitation light is not irradiated Change calculation means for calculating a value obtained by dividing the reflectance of the measurement light when the excitation light is not irradiated as a change ratio of the reflectance of the measurement light, and the change calculation means includes the reflectance of the measurement light. Poles in the spectrum of the change rate of Only the change rate of the reflectance of the measurement light at a specific energy value of the measurement light that gives computing.

[0026]

By using this optical evaluation device, the following effects can be obtained. When excitation light guided by the first light guiding member is irradiated onto the semiconductor region, carriers in the semiconductor region are excited and an electric field is generated by the carriers. Due to this electric field, the reflectivity of the measurement light guided to the semiconductor region by the second light guide member changes with and without excitation light irradiation, and this rate of change depends on the magnitude of the electric field strength and the measurement. It varies depending on the wavelength of light. On the other hand, if there is a defect that becomes a recombination center of carriers in the semiconductor region, the lifetime of the excited carriers is shortened, so that the electric field strength formed by the carriers is reduced. In other words, since the rate of change in reflectivity with and without excitation light irradiation changes depending on the number of defects in the semiconductor region, the change calculation means uses the detection value of the reflectivity detection means to detect the semiconductor region. When the change rate of the reflectivity of the measurement light at is calculated, the change rate of the reflectivity reflects the crystal state of the semiconductor region and the like. Therefore, it is possible to control the conditions of the processing performed in the chamber based on the in-line evaluation of the semiconductor region.

[0027]

AlsoOnly the change in the reflectance of the measurement light having the specific wavelength that is most desirable can be detected. Therefore, optical evaluation without noise and high sensitivity is possible.

[0028]

Claim5As claimed in4In the above, it is preferable that the specific energy value of the measurement light be any value included in the range of 3.2 to 3.6 eV.

[0029]

First of the present invention3The optical evaluation device of claim6An optical evaluation apparatus for evaluating electrical characteristics of an insulating film formed on a semiconductor region of a substrate, comprising: a first light source that generates excitation light; and measurement light. A second light source to be generated, a first light guiding member for intermittently irradiating the semiconductor region directly below the insulating film through the insulating film with the excitation light generated by the first light source; A second light guide member for irradiating the semiconductor region with the measurement light generated by the second light source through the insulating film and irradiating the semiconductor region irradiated with the excitation light intermittently; A reflectance detecting means for detecting the reflectance of the measured light, a third light guide member for causing the measuring light reflected from the semiconductor region to enter the reflectance detecting means, and the reflectance detecting means. In response to the output, the semiconductor region is irradiated with excitation light By dividing the difference in the reflectance of the measurement light from when the excitation light is not irradiated by the reflectance of the measurement light when the excitation light is not irradiated, the change rate of the reflectance of the measurement light is obtained. And a change calculating means for calculating, and an evaluating means for evaluating the electrical characteristics of the insulating film based on the change rate of the reflectance of the measurement light.

[0030]

As a result, information about electrical defects in the insulating film, particularly the gate insulating film, can be obtained. That is, when the semiconductor region is irradiated with excitation light, carriers are excited, and the electric field strength changes with the change in the number of carriers, so that the reflectance of the measurement light in a certain wavelength region from the semiconductor region changes. At that time, if an insulating film is formed on the semiconductor region, a defect site serving as a carrier trap exists in the surface layer of the semiconductor region, so that the change rate of the reflectance of the measurement light is reduced. However, if the number of defects (trap electrons) in the insulating film is large, the amount of increase in the electric field strength in the adjacent semiconductor region increases, and the rate of change in the reflectance of the measurement light increases. Therefore, it is possible to quickly and surely manage the electrical characteristics of the insulating film by determining that the reflectance of the measurement light is outside the predetermined range by the evaluation means as being defective.

[0031]

Claim7As claimed in6In the spectrum of the change rate of the reflectance of the measurement light.PoleIt can be determined that the non-defective product is determined only when the change ratio of the reflectance of the measurement light at the specific energy value of the measurement light that gives the value is a value corresponding to the appropriate capacitance value of the insulating film.

[0032]

Claim8As claimed in6, The specific energy value of the measurement light can be any value within the range of 3.2 to 3.6 eV.

[0033]

Claim7Or8As a result, the optical evaluation is performed at a location where the sensitivity for detecting the difference in the electrical characteristics of the insulating film is the best in the spectrum of the change ratio of the reflectance indicating the characteristic shape.

[0034]

Claim9As claimed in6 to 8In any one of the above, a spectroscopic unit that receives the measurement light reflected from the semiconductor region, splits the measurement light, and sends the measurement light to the reflectance detection unit can be further provided.

[0035]

Thereby, since the spectrum of the change ratio of the reflectance of the measurement light is detected, it becomes possible to perform highly accurate optical evaluation based on the information of the entire spectrum shape.

[0036]

Claim10As claimed in6 to 8In any one of the above, the measurement light reflected from the semiconductor region is received, and only the measurement light in the wavelength range corresponding to the specific energy value of the measurement light is transmitted and sent to the reflectance detection means The filter may be further provided.

[0037]

Accordingly, since a change in reflectance in a desired wavelength range can be detected without providing a spectroscopic means, the structure of the optical evaluation device is simplified, and rapid optical evaluation is possible.

[0038]

Claim11As claimed in6In the above, it is preferable that the reflectance detection means detects the reflectance of measurement light in a wavelength range of 600 nm or less.

[0039]

Claim12As claimed in11In the above, it is more preferable that the reflectance detection means detects the reflectance of measurement light in the wavelength range of 300 to 600 nm.

[0040]

Claim11Or12By using the fact that the measurement light in the visible light region and the wavelength region below it does not reach a depth of several hundred nm or more in the semiconductor region, the region affected by trapped electrons in the insulating film in the semiconductor region The optical evaluation can be performed based on the change rate of the reflectance only from the above.

[0041]

Claim13As claimed in6 to 12In any one of the above, the optical evaluation device can be configured using an ellipsometry spectrometer.

[0042]

This makes it possible to configure an optical evaluation apparatus at low cost by using an ellipsometry spectrometer used for measuring the thickness of a gate oxide film or the like.

[0043]

Claim14As claimed in6 to 13In any one of them, the optical evaluation device is preferably attached to a chamber used for forming an oxide film of a semiconductor device.

[0044]

Thereby, the quality of the insulating film can be evaluated without taking out the semiconductor substrate from the manufacturing apparatus, so that the evaluation apparatus is suitable for in-line characteristic evaluation.

[0045]

Claim15As claimed in6The second light source may be an Xe lamp.

[0046]

Claim16As claimed in6The first light source may be an Ar ion laser or a He—Ne laser.

[0047]

Claim17As claimed in6 to 16In any one of the above, it is preferable that the first light guide member is configured to irradiate the excitation light intermittently at a frequency of 1 kHz or less.

[0048]