JP2014023156A - レシーバ利得適応に基づいてトランスミッタ等化係数を適応させるための方法および装置 - Google Patents

レシーバ利得適応に基づいてトランスミッタ等化係数を適応させるための方法および装置 Download PDFInfo

- Publication number

- JP2014023156A JP2014023156A JP2013148220A JP2013148220A JP2014023156A JP 2014023156 A JP2014023156 A JP 2014023156A JP 2013148220 A JP2013148220 A JP 2013148220A JP 2013148220 A JP2013148220 A JP 2013148220A JP 2014023156 A JP2014023156 A JP 2014023156A

- Authority

- JP

- Japan

- Prior art keywords

- amplifier

- request

- receiver

- gain value

- adaptation

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L27/00—Modulated-carrier systems

- H04L27/01—Equalisers

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/03—Shaping networks in transmitter or receiver, e.g. adaptive shaping networks

- H04L25/03006—Arrangements for removing intersymbol interference

- H04L25/03343—Arrangements at the transmitter end

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Power Engineering (AREA)

- Dc Digital Transmission (AREA)

- Cable Transmission Systems, Equalization Of Radio And Reduction Of Echo (AREA)

Abstract

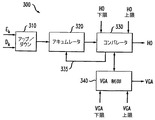

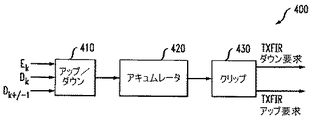

【解決手段】チャネルを介してレシーバと通信するトランスミッタの等化係数は、レシーバの中の増幅器についての利得値が、増幅器の限度内にあるかどうかを決定すること、および利得値が増幅器の上限または下限を満たさない場合に、トランスミッタの等化係数に対する1つまたは複数の調整を防止することにより適応させられる。利得調整は、例えば、トランスミッタの等化係数についてのアップ要求およびダウン要求を含んでいる。1つまたは複数のイネーブル・フラグは、オプションとして、利得値が、増幅器の限度内にあるかどうかに基づいて、設定され得る。

【選択図】図1

Description

DFE係数、cn、についてのLMS適応アルゴリズムは、データ・アイ当たりに1つのエラー・スライサについての例示の場合において、以下の式によって記述され得る。

概して、等化は、データ・アイのサイズを開く(すなわち、データ・マージンを増大させる)ことを目指している。それにもかかわらず、等化は、外部アイ520が低減する量よりも少ない量だけ内部アイ510を増大させる(例えば、外部アイ520は、内部アイ510が開くよりももっと閉じる)ことができることが分かっている。これは、内部アイ510と、外部アイ520との間の統計的中央値を低減するようにさせることになり、またエラー・ラッチ240−Eiについてのオフセット・レベルH0は、より低い値に再適応させることになる。H0レベルへの低減は、次には、図3に関連して上記で考察されるように、VGA利得調整における増大を引き起こす可能性がある。

Claims (10)

- チャネルを介してレシーバと通信するトランスミッタの中の等化器の係数を適応させる方法であって、

前記レシーバの中の増幅器についての利得値が前記増幅器の限度内にあるかどうかを決定するステップと、

前記利得値が前記増幅器の前記限度を満たさないときには、前記等化器係数に対する1つまたは複数の調整を防止するステップとを備える、方法。 - 前記調整は前記等化器係数についてのアップ要求およびダウン要求を含む、請求項1に記載の方法。

- 前記利得値が前記増幅器の前記限度内にあるかどうかに基づいて、1つまたは複数のフラグを設定するステップをさらに備える、請求項1に記載の方法。

- 前記等化器は、送信有限インパルス応答(TXFIR)フィルタおよび可変利得増幅器のうちの1つまたは複数を備える、請求項1に記載の方法。

- チャネルを介してレシーバと通信するトランスミッタの中の等化器の1つまたは複数の係数を適応させる装置であって、

メモリと、

前記メモリに結合された少なくとも1つのハードウェア・デバイスであって、

前記レシーバの中の増幅器についての利得値が前記増幅器の限度内にあるかどうかを決定し、そして、

前記利得値が前記増幅器の前記限度を満たさないときには、前記等化器係数に対する1つまたは複数の調整を防止する、ように動作可能である前記少なくとも1つのハードウェア・デバイスとを備える、装置。 - 前記調整は前記係数についてのアップ要求およびダウン要求を含む、請求項5に記載の装置。

- 前記少なくとも1つのハードウェア・デバイスは、前記利得値が前記増幅器の前記限度内にあるかどうかに基づいて、1つまたは複数のフラグを設定するようにさらに構成される、請求項5に記載の装置。

- チャネルを介してレシーバと通信するトランスミッタの中の等化器の係数を適応させる製品であって、実行されるときに、

前記レシーバの中の増幅器についての利得値が前記増幅器の限度内にあるかどうかを決定するステップと、

前記利得値が前記可変利得増幅器の前記限度を満たさないときには、前記係数に対する1つまたは複数の調整を防止するステップと、

を実施する1つまたは複数のプログラムを含む有形の機械読取可能記録可能媒体を備える、製品。 - チャネルを介してレシーバと通信するトランスミッタの中の等化器の係数を適応させる集積回路であって、

前記レシーバの中の増幅器についての利得値が前記増幅器の限度内にあるかどうかを決定するように動作可能な利得制限回路と、

前記利得値が前記増幅器の前記限度を満たさないときには、前記係数に対する1つまたは複数の調整を防止するように動作可能な要求ゲート回路と、

を備える集積回路。 - 前記調整は前記係数についてのアップ要求およびダウン要求を含む、請求項9に記載の集積回路。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/552,012 US9385897B2 (en) | 2012-07-18 | 2012-07-18 | Methods and apparatus for adapting transmitter equalization coefficients based on receiver gain adaptation |

| US13/552,012 | 2012-07-18 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014023156A true JP2014023156A (ja) | 2014-02-03 |

| JP2014023156A5 JP2014023156A5 (ja) | 2016-08-04 |

Family

ID=49035264

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013148220A Withdrawn JP2014023156A (ja) | 2012-07-18 | 2013-07-17 | レシーバ利得適応に基づいてトランスミッタ等化係数を適応させるための方法および装置 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US9385897B2 (ja) |

| EP (1) | EP2688260B1 (ja) |

| JP (1) | JP2014023156A (ja) |

| KR (1) | KR20140011286A (ja) |

| CN (1) | CN103581079B (ja) |

| TW (1) | TW201406085A (ja) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9503717B2 (en) | 2012-01-09 | 2016-11-22 | Texas Instruments Incorporated | Context adaptive binary arithmetic coding (CABAC) with scalable throughput and coding efficiency |

| US8848769B2 (en) * | 2012-10-09 | 2014-09-30 | Lsi Corporation | Joint transmitter and receiver gain optimization for high-speed serial data systems |

| US9197458B1 (en) * | 2014-05-01 | 2015-11-24 | Samsung Display Co., Ltd. | Edge equalization via adjustment of unroll threshold for crossing slicer |

| TWI597610B (zh) * | 2014-05-07 | 2017-09-01 | 円星科技股份有限公司 | 基於接收單元之等化器的資訊而收發訊號的方法以及訓練等化器的方法 |

| TWI574512B (zh) * | 2015-09-03 | 2017-03-11 | 威盛電子股份有限公司 | 切分器裝置及其校準方法 |

| US9866412B2 (en) * | 2016-01-29 | 2018-01-09 | Samsung Display Co., Ltd. | Equalization in high speed links through in-situ channel estimation |

| CN107241160B (zh) * | 2016-03-28 | 2021-03-23 | 华为技术有限公司 | 确定参数的方法和装置 |

| CN106953818B (zh) * | 2017-02-10 | 2020-10-20 | 张家港康得新光电材料有限公司 | 均衡器设置装置 |

| US10153917B1 (en) * | 2017-07-21 | 2018-12-11 | Huawei Technologies Co., Ltd. | Frequency/phase-shift-keying for back-channel serdes communication |

| CN107508618B (zh) * | 2017-08-29 | 2021-03-19 | 苏州裕太微电子有限公司 | 一种基于有线通信的抗信号衰减的方法及通信设备 |

| CN112117606A (zh) * | 2019-06-21 | 2020-12-22 | 默升科技集团有限公司 | 具有预设预均衡的有源以太网电缆 |

| US11463284B1 (en) * | 2021-07-09 | 2022-10-04 | Cadence Design Systems, Inc. | Programmable correlation computation system |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5678198A (en) | 1991-05-22 | 1997-10-14 | Southwestern Bell Technology Resources, Inc. | System for controlling signal level at both ends of a transmission link, based upon a detected value |

| US5991311A (en) * | 1997-10-25 | 1999-11-23 | Centillium Technology | Time-multiplexed transmission on digital-subscriber lines synchronized to existing TCM-ISDN for reduced cross-talk |

| US6141634A (en) * | 1997-11-26 | 2000-10-31 | International Business Machines Corporation | AC power line network simulator |

| DE10141597B4 (de) * | 2001-08-24 | 2017-11-09 | Lantiq Deutschland Gmbh | Verfahren zum Rekonstruieren von über eine Übertragungsstrecke übertragenen Daten in einem Empfänger und entsprechende Vorrichtung |

| US7589927B2 (en) * | 2005-08-30 | 2009-09-15 | International Business Machines Corporation | Dynamically adapting a read channel equalizer |

| US8428111B2 (en) * | 2006-05-23 | 2013-04-23 | Broadcom Corporation | Crosstalk emission management |

| US7711043B2 (en) | 2006-09-29 | 2010-05-04 | Agere Systems Inc. | Method and apparatus for determining latch position for decision-feedback equalization using single-sided eye |

| US20090097538A1 (en) | 2007-10-10 | 2009-04-16 | Aziz Pervez M | Methods And Apparatus For Adaptive Equalization Using Pattern Detection Methods |

| CN102113221A (zh) * | 2008-08-05 | 2011-06-29 | 富士通株式会社 | 发送装置以及调整值测定方法 |

| US8848774B2 (en) | 2008-08-19 | 2014-09-30 | Lsi Corporation | Adaptation of a linear equalizer using a virtual decision feedback equalizer (VDFE) |

| US8135100B2 (en) | 2008-08-20 | 2012-03-13 | International Business Machines Corporation | Adaptive clock and equalization control systems and methods for data receivers in communications systems |

| US8472513B2 (en) | 2009-01-14 | 2013-06-25 | Lsi Corporation | TX back channel adaptation algorithm |

| US8229020B2 (en) | 2009-03-23 | 2012-07-24 | Oracle America, Inc. | Integrated equalization and CDR adaptation engine with single error monitor circuit |

| US8432955B2 (en) * | 2009-07-10 | 2013-04-30 | Futurewei Technologies, Inc. | Method for robust crosstalk precoder training in channels with impulse noise |

| US8432960B2 (en) | 2010-03-18 | 2013-04-30 | Freescale Semiconductor, Inc. | Digital adaptive channel equalizer |

-

2012

- 2012-07-18 US US13/552,012 patent/US9385897B2/en active Active

-

2013

- 2013-07-17 JP JP2013148220A patent/JP2014023156A/ja not_active Withdrawn

- 2013-07-17 KR KR1020130084345A patent/KR20140011286A/ko not_active Application Discontinuation

- 2013-07-17 TW TW102125628A patent/TW201406085A/zh unknown

- 2013-07-18 EP EP13177107.3A patent/EP2688260B1/en active Active

- 2013-07-18 CN CN201310381433.1A patent/CN103581079B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20140023131A1 (en) | 2014-01-23 |

| EP2688260A3 (en) | 2015-10-07 |

| CN103581079B (zh) | 2018-06-22 |

| US9385897B2 (en) | 2016-07-05 |

| CN103581079A (zh) | 2014-02-12 |

| TW201406085A (zh) | 2014-02-01 |

| EP2688260B1 (en) | 2017-05-31 |

| KR20140011286A (ko) | 2014-01-28 |

| EP2688260A2 (en) | 2014-01-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11115247B2 (en) | Methods and circuits for asymmetric distribution of channel equalization between devices | |

| JP2014023156A (ja) | レシーバ利得適応に基づいてトランスミッタ等化係数を適応させるための方法および装置 | |

| US9705708B1 (en) | Integrated circuit with continuously adaptive equalization circuitry | |

| US9294314B2 (en) | Receiver having limiter-enhanced data eye openings | |

| US9025655B1 (en) | Transmitter training using receiver equalizer coefficients | |

| US8705672B2 (en) | Method of compensating for nonlinearity in a DFE-based receiver | |

| US9191244B2 (en) | Equalizer and semiconductor device | |

| US8831142B2 (en) | Adaptive cancellation of voltage offset in a communication system | |

| US20150381393A1 (en) | Adaptive Cancellation of Voltage Offset in a Communication System | |

| US20150256364A1 (en) | Group delay based back channel post cursor adaptation | |

| US8848769B2 (en) | Joint transmitter and receiver gain optimization for high-speed serial data systems | |

| US8687682B2 (en) | Transmitter adaptation loop using adjustable gain and convergence detection | |

| US20170288915A1 (en) | Systems and Methods for Mitigating Over-Equalization in a Short Channel | |

| US20240333559A1 (en) | Adaptive Preset-Based Feed-Forward Equalization | |

| CN118694439A (zh) | 信号处理方法和装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20140812 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20140829 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20140829 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160616 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160616 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20160616 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20160622 |