FR2753031A1 - Procedes et dispositifs pour le traitement de donnees video - Google Patents

Procedes et dispositifs pour le traitement de donnees video Download PDFInfo

- Publication number

- FR2753031A1 FR2753031A1 FR9710439A FR9710439A FR2753031A1 FR 2753031 A1 FR2753031 A1 FR 2753031A1 FR 9710439 A FR9710439 A FR 9710439A FR 9710439 A FR9710439 A FR 9710439A FR 2753031 A1 FR2753031 A1 FR 2753031A1

- Authority

- FR

- France

- Prior art keywords

- sep

- data

- address

- register

- bit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000013598 vector Substances 0.000 claims abstract description 178

- 238000012545 processing Methods 0.000 claims abstract description 100

- 238000000034 method Methods 0.000 claims abstract description 52

- 230000008569 process Effects 0.000 claims abstract description 39

- 230000009466 transformation Effects 0.000 claims abstract description 10

- 238000000844 transformation Methods 0.000 abstract description 2

- BZQFBWGGLXLEPQ-REOHCLBHSA-N phosphoserine Chemical compound OC(=O)[C@@H](N)COP(O)(O)=O BZQFBWGGLXLEPQ-REOHCLBHSA-N 0.000 description 8112

- 239000000872 buffer Substances 0.000 description 170

- 230000015654 memory Effects 0.000 description 159

- 238000012546 transfer Methods 0.000 description 86

- 230000033001 locomotion Effects 0.000 description 69

- 238000012360 testing method Methods 0.000 description 48

- 238000010586 diagram Methods 0.000 description 38

- 238000003817 vacuum liquid chromatography Methods 0.000 description 38

- 238000010200 validation analysis Methods 0.000 description 31

- 238000011069 regeneration method Methods 0.000 description 29

- 230000008929 regeneration Effects 0.000 description 26

- 238000012876 topography Methods 0.000 description 23

- 230000008859 change Effects 0.000 description 20

- 230000001360 synchronised effect Effects 0.000 description 18

- 101100067427 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) FUS3 gene Proteins 0.000 description 14

- 101100015484 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) GPA1 gene Proteins 0.000 description 14

- 230000002093 peripheral effect Effects 0.000 description 12

- 102100040862 Dual specificity protein kinase CLK1 Human genes 0.000 description 11

- 230000006870 function Effects 0.000 description 11

- 102100040844 Dual specificity protein kinase CLK2 Human genes 0.000 description 10

- 101000749294 Homo sapiens Dual specificity protein kinase CLK1 Proteins 0.000 description 10

- 101000749291 Homo sapiens Dual specificity protein kinase CLK2 Proteins 0.000 description 10

- 238000004891 communication Methods 0.000 description 9

- 238000000605 extraction Methods 0.000 description 9

- 238000007667 floating Methods 0.000 description 9

- 230000002457 bidirectional effect Effects 0.000 description 8

- 238000013461 design Methods 0.000 description 8

- 108010057081 Merozoite Surface Protein 1 Proteins 0.000 description 7

- 230000036316 preload Effects 0.000 description 7

- 238000013139 quantization Methods 0.000 description 7

- 238000005070 sampling Methods 0.000 description 7

- 101000969688 Homo sapiens Macrophage-expressed gene 1 protein Proteins 0.000 description 6

- 102100021285 Macrophage-expressed gene 1 protein Human genes 0.000 description 6

- 238000006243 chemical reaction Methods 0.000 description 6

- 230000009977 dual effect Effects 0.000 description 6

- 238000007726 management method Methods 0.000 description 6

- LZHSWRWIMQRTOP-UHFFFAOYSA-N N-(furan-2-ylmethyl)-3-[4-[methyl(propyl)amino]-6-(trifluoromethyl)pyrimidin-2-yl]sulfanylpropanamide Chemical compound CCCN(C)C1=NC(=NC(=C1)C(F)(F)F)SCCC(=O)NCC2=CC=CO2 LZHSWRWIMQRTOP-UHFFFAOYSA-N 0.000 description 5

- 238000007792 addition Methods 0.000 description 5

- 238000007906 compression Methods 0.000 description 5

- 230000006835 compression Effects 0.000 description 5

- 239000000284 extract Substances 0.000 description 5

- 230000001343 mnemonic effect Effects 0.000 description 5

- 101100218322 Arabidopsis thaliana ATXR3 gene Proteins 0.000 description 4

- 102100032742 Histone-lysine N-methyltransferase SETD2 Human genes 0.000 description 4

- 101100149326 Homo sapiens SETD2 gene Proteins 0.000 description 4

- 101100533304 Plasmodium falciparum (isolate 3D7) SETVS gene Proteins 0.000 description 4

- 101150117538 Set2 gene Proteins 0.000 description 4

- 230000005540 biological transmission Effects 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 4

- 238000013479 data entry Methods 0.000 description 4

- 230000006837 decompression Effects 0.000 description 4

- 238000009432 framing Methods 0.000 description 4

- 239000003292 glue Substances 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 4

- 239000000463 material Substances 0.000 description 4

- 230000004044 response Effects 0.000 description 4

- 101100327050 Caenorhabditis elegans cbp-1 gene Proteins 0.000 description 3

- 101100494729 Syncephalastrum racemosum SPSR gene Proteins 0.000 description 3

- 238000004364 calculation method Methods 0.000 description 3

- 238000001914 filtration Methods 0.000 description 3

- 238000011068 loading method Methods 0.000 description 3

- 230000002441 reversible effect Effects 0.000 description 3

- 238000003786 synthesis reaction Methods 0.000 description 3

- 101100424823 Arabidopsis thaliana TDT gene Proteins 0.000 description 2

- 102100029768 Histone-lysine N-methyltransferase SETD1A Human genes 0.000 description 2

- 101000865038 Homo sapiens Histone-lysine N-methyltransferase SETD1A Proteins 0.000 description 2

- 241001582888 Lobus Species 0.000 description 2

- 230000002159 abnormal effect Effects 0.000 description 2

- 238000009825 accumulation Methods 0.000 description 2

- 230000009471 action Effects 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 229960000265 cromoglicic acid Drugs 0.000 description 2

- IMZMKUWMOSJXDT-UHFFFAOYSA-N cromoglycic acid Chemical compound O1C(C(O)=O)=CC(=O)C2=C1C=CC=C2OCC(O)COC1=CC=CC2=C1C(=O)C=C(C(O)=O)O2 IMZMKUWMOSJXDT-UHFFFAOYSA-N 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 239000003999 initiator Substances 0.000 description 2

- PWPJGUXAGUPAHP-UHFFFAOYSA-N lufenuron Chemical compound C1=C(Cl)C(OC(F)(F)C(C(F)(F)F)F)=CC(Cl)=C1NC(=O)NC(=O)C1=C(F)C=CC=C1F PWPJGUXAGUPAHP-UHFFFAOYSA-N 0.000 description 2

- 238000012423 maintenance Methods 0.000 description 2

- 239000002674 ointment Substances 0.000 description 2

- 238000012805 post-processing Methods 0.000 description 2

- 238000011045 prefiltration Methods 0.000 description 2

- 238000011084 recovery Methods 0.000 description 2

- 230000000630 rising effect Effects 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 238000012384 transportation and delivery Methods 0.000 description 2

- GMRQFYUYWCNGIN-ZVUFCXRFSA-N 1,25-dihydroxy vitamin D3 Chemical compound C1([C@@H]2CC[C@@H]([C@]2(CCC1)C)[C@@H](CCCC(C)(C)O)C)=CC=C1C[C@@H](O)C[C@H](O)C1=C GMRQFYUYWCNGIN-ZVUFCXRFSA-N 0.000 description 1

- CDSZITPHFYDYIK-UHFFFAOYSA-N 2-[[ethyl(2-methylpropoxy)phosphinothioyl]sulfanylmethyl]isoindole-1,3-dione Chemical compound C1=CC=C2C(=O)N(CSP(=S)(OCC(C)C)CC)C(=O)C2=C1 CDSZITPHFYDYIK-UHFFFAOYSA-N 0.000 description 1

- VBRBNWWNRIMAII-WYMLVPIESA-N 3-[(e)-5-(4-ethylphenoxy)-3-methylpent-3-enyl]-2,2-dimethyloxirane Chemical compound C1=CC(CC)=CC=C1OC\C=C(/C)CCC1C(C)(C)O1 VBRBNWWNRIMAII-WYMLVPIESA-N 0.000 description 1

- SYQQWGGBOQFINV-FBWHQHKGSA-N 4-[2-[(2s,8s,9s,10r,13r,14s,17r)-10,13-dimethyl-17-[(2r)-6-methylheptan-2-yl]-3-oxo-1,2,6,7,8,9,11,12,14,15,16,17-dodecahydrocyclopenta[a]phenanthren-2-yl]ethoxy]-4-oxobutanoic acid Chemical compound C1CC2=CC(=O)[C@H](CCOC(=O)CCC(O)=O)C[C@]2(C)[C@@H]2[C@@H]1[C@@H]1CC[C@H]([C@H](C)CCCC(C)C)[C@@]1(C)CC2 SYQQWGGBOQFINV-FBWHQHKGSA-N 0.000 description 1

- 101150008604 CAN1 gene Proteins 0.000 description 1

- 101150063504 CAN2 gene Proteins 0.000 description 1

- 101100058989 Candida albicans (strain SC5314 / ATCC MYA-2876) CAN3 gene Proteins 0.000 description 1

- 101100003180 Colletotrichum lindemuthianum ATG1 gene Proteins 0.000 description 1

- 101100490184 Drosophila melanogaster Ack gene Proteins 0.000 description 1

- 241001501930 Gavia Species 0.000 description 1

- 101100356020 Haemophilus influenzae (strain ATCC 51907 / DSM 11121 / KW20 / Rd) recA gene Proteins 0.000 description 1

- 101000577202 Homo sapiens Neurogenic locus notch homolog protein 3 Proteins 0.000 description 1

- 101000634707 Homo sapiens Nucleolar complex protein 3 homolog Proteins 0.000 description 1

- 101000641224 Homo sapiens Vimentin-type intermediate filament-associated coiled-coil protein Proteins 0.000 description 1

- 102100025247 Neurogenic locus notch homolog protein 3 Human genes 0.000 description 1

- 102100029099 Nucleolar complex protein 3 homolog Human genes 0.000 description 1

- RSPISYXLHRIGJD-UHFFFAOYSA-N OOOO Chemical compound OOOO RSPISYXLHRIGJD-UHFFFAOYSA-N 0.000 description 1

- 101000701286 Pseudomonas aeruginosa (strain ATCC 15692 / DSM 22644 / CIP 104116 / JCM 14847 / LMG 12228 / 1C / PRS 101 / PAO1) Alkanesulfonate monooxygenase Proteins 0.000 description 1

- 101100178280 Rattus norvegicus Homer1 gene Proteins 0.000 description 1

- 101710094840 Sirohydrochlorin ferrochelatase Proteins 0.000 description 1

- 101000983349 Solanum commersonii Osmotin-like protein OSML13 Proteins 0.000 description 1

- 101000983338 Solanum commersonii Osmotin-like protein OSML15 Proteins 0.000 description 1

- 101710188946 Uroporphyrinogen-III C-methyltransferase Proteins 0.000 description 1

- 102100034331 Vimentin-type intermediate filament-associated coiled-coil protein Human genes 0.000 description 1

- 101100524347 Xenopus laevis req-b gene Proteins 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- 230000006978 adaptation Effects 0.000 description 1

- 230000003044 adaptive effect Effects 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- QWCRAEMEVRGPNT-UHFFFAOYSA-N buspirone Chemical compound C1C(=O)N(CCCCN2CCN(CC2)C=2N=CC=CN=2)C(=O)CC21CCCC2 QWCRAEMEVRGPNT-UHFFFAOYSA-N 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 238000012508 change request Methods 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 238000013480 data collection Methods 0.000 description 1

- 238000013144 data compression Methods 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 238000013501 data transformation Methods 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 230000001934 delay Effects 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000011156 evaluation Methods 0.000 description 1

- 239000011536 extraction buffer Substances 0.000 description 1

- 230000005764 inhibitory process Effects 0.000 description 1

- 230000000977 initiatory effect Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000009191 jumping Effects 0.000 description 1

- 238000002372 labelling Methods 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 239000003550 marker Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 230000008520 organization Effects 0.000 description 1

- 238000013439 planning Methods 0.000 description 1

- 238000005086 pumping Methods 0.000 description 1

- 238000011002 quantification Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 238000012552 review Methods 0.000 description 1

- 239000004576 sand Substances 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 230000002123 temporal effect Effects 0.000 description 1

- 238000012549 training Methods 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 238000013519 translation Methods 0.000 description 1

- 230000001960 triggered effect Effects 0.000 description 1

- 229940040153 vectical Drugs 0.000 description 1

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3877—Concurrent instruction execution, e.g. pipeline or look ahead using a slave processor, e.g. coprocessor

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline or look ahead

- G06F9/3877—Concurrent instruction execution, e.g. pipeline or look ahead using a slave processor, e.g. coprocessor

- G06F9/3879—Concurrent instruction execution, e.g. pipeline or look ahead using a slave processor, e.g. coprocessor for non-native instruction execution, e.g. executing a command; for Java instruction set

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06T—IMAGE DATA PROCESSING OR GENERATION, IN GENERAL

- G06T9/00—Image coding

- G06T9/008—Vector quantisation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/42—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals characterised by implementation details or hardware specially adapted for video compression or decompression, e.g. dedicated software implementation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/60—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using transform coding

- H04N19/61—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals using transform coding in combination with predictive coding

Landscapes

- Engineering & Computer Science (AREA)

- Software Systems (AREA)

- Theoretical Computer Science (AREA)

- Multimedia (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Signal Processing (AREA)

- General Engineering & Computer Science (AREA)

- Compression Or Coding Systems Of Tv Signals (AREA)

Abstract

L'invention concerne un système pour le codage ou le décodage de données vidéo. Selon l'invention, le système comprend un processeur vectoriel (220) pour accomplir une transformation linéaire sur des données vidéo, un processeur de train de bits (245) pour comprimer une sortie du processeur vectoriel ou décomprimer les données vidéo pour une entrée au processeur vectoriel; et un circuit de contrôle (248) pour synchroniser le fonctionnement du processeur vectoriel et du processeur du train de bits, le processeur du train de bits (245) pouvant être interrompu par le circuit de contrôle (248) pour arrêter le traitement d'un train de données vidéo et commencer le traitement d'un train différent de données vidéo de façon que le processeur de train de bits soit capable de traiter les deux trains de données vidéo sensiblement concurremment pour permettre au système de coder ou de décoder deux trains de données vidéo en temps réel. L'invention s 'applique notamment aux télécommunications.

Description

La présente invention se rapporte au traitement de données par des ordinateurs et, plus particulièrement, au traitement de données vidéo par des ordinateurs.

Les ordinateurs ont été utilisés pour comprimer et décomprimer les données de systèmes. Les données de systèmes comprennent les données vidéo qui comprennent des images à l'arrêt et/ou des images mobiles. Les données de systèmes peuvent également comprendre des données audio, par exemple une piste sonore d'une image en mouvement. I1 est souhaitable de prévoir des méthodes et des circuits qui permettent un traitement rapide des données vidéo.

La présente invention procure des méthodes et circuits qui permettent un traitement rapide des données vidéo. Dans certains modes de réalisation, un système d'ordinateur de la présente invention comprend trois processeurs capables de fonctionner concurremment : un processeur scalaire, un processeur vectoriel et un processeur du train de bits. Dans le codage ou le décodage des données vidéo, le processeur vectoriel effectue des opérations qui peuvent être efficacement accomplies par un processeur de données multiples à une; seule instruction (SIMD). De telles opérations comprennent : 1) une transformation de données linéaires comme une transformation cosinusoïdale discrète (DCT) et 2) une compensation du mouvement. Le processeur du train de bits accomplit des opérations qui comprennent des opérations sur des bits particuliers plutôt que sur des mots ou des demi-mots. De telles opérations comprennent un codage ou un décodage de Huffman et RLC utilisés, par exemple, avec les standards MPEG-1, MPEG-2,

H.261 et H.263. Le processeur scalaire accomplit un traitement vidéo de haut niveau (par exemple, traitement du niveau de l'image), synchronise le fonctionnement des processeurs vectoriel et du train de bits et contrôle l'interface avec des dispositifs externes.

H.261 et H.263. Le processeur scalaire accomplit un traitement vidéo de haut niveau (par exemple, traitement du niveau de l'image), synchronise le fonctionnement des processeurs vectoriel et du train de bits et contrôle l'interface avec des dispositifs externes.

Dans certains modes de réalisation, le système d'ordinateur peut traiter plusieurs courants de données concurremment. Par suite, l'utilisateur du système d'ordinateur peut avoir une conférence vidéo avec deux correspondants ou plus. Des trains de données multiples peuvent être traités concurremment parce que le processeur du train de bits peut commuter des contextes pour coder ou décoder différents trains de données concurremment en temps réel.

Dans certains modes de réalisation, les processeurs scalaire et vectoriel sont programmables dans le sens que chacun des deux processeurs peut être programmé pour exécuter une seule instruction arithmétique ou booléenne.

Le processeur du train de bits n'est pas programmable dans le sens que le processeur du train de bits ne peut être programmé pour exécuter une instruction arithmétique ou booléenne. Par ailleurs, le processeur du train de bits peut être programmé pour accomplir une opération de traitement total des données vidéo sur un groupe de données vidéo. En rendant incapable le processeur du train de bits d'être programmé pour exécuter une seule instruction arithmétique ou booléenne, cela permet au processeur du train de bits d'être plus rapide. La programmabilité des processeurs scalaire et vectoriel facilite l'adaptation du systeme à des changements des standards de codage et de décodage de données vidéo.

L'invention sera mieux comprise et d'autres buts, caractéristiques, détails et avantages de celle-ci apparaîtront plus clairement au cours de la description explicative qui va suivre faite en référence aux dessins schématiques annexés donnés uniquement à titre d'exemple illustrant plusieurs modes de réalisation de l'invention et dans lesquels

- la figure 1 donne un schéma bloc d'une carte de support selon la présente invention;

- la figure 2 donne un schéma bloc d'un processeur multimédia selon la présente invention

- la figure 3 donne un schéma bloc d'un processeur du train de bits qui fait partie du processeur de la figure 2

- les figures 4-6 sont des schémas blocs de systèmes d'ordinateurs selon la présente invention

- la figure 7 illustre une architecture de microprogrammation dans le processeur de la figure 9

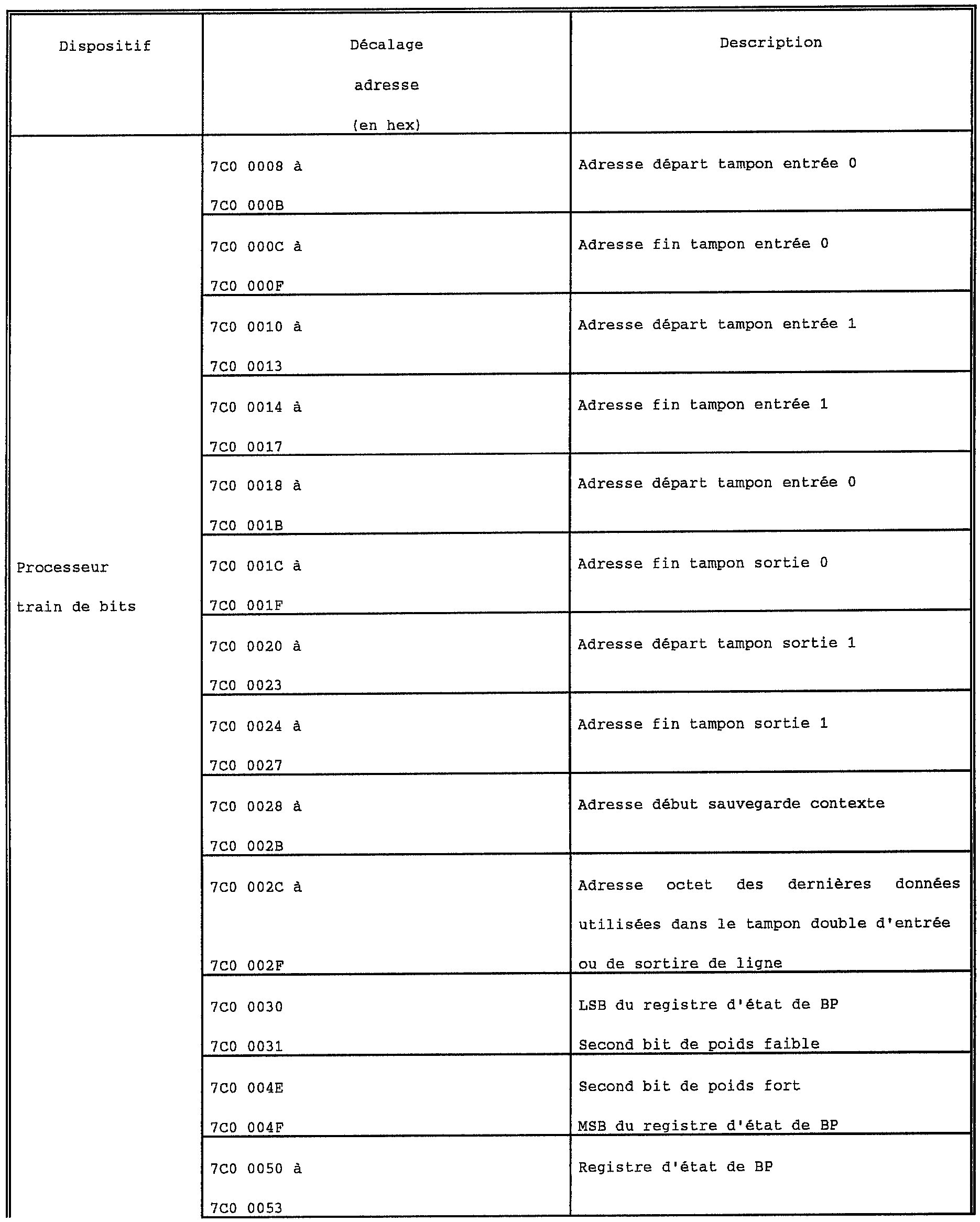

- les figures 8-9 montrent des topographies d'adresses pour le système de la figure 1

- la figure 10 donne un schéma bloc du noyau de DSP du processeur de la figure 2

- la figure 11 illustre un pipeline employé dans un processeur vectoriel qui fait partie du processeur de la figure 2

- la figure 12 est un schéma bloc fonctionnel du processeur vectoriel de la figure 11 ;

- la figure 13 illustre des trajets de données d'exécution dans le processeur vectoriel de la figure 11;

- la figure 14 illustre des trajets de données de charge et d'enregistrement dans le processeur vectoriel de la figure 11 ;

- la figure 15 est un schéma bloc d'un système d'antémémoire du processeur de la figure 2

- la figure 16 illustre l'antémémoire des données d'instructions dans le système d'antémémoire de la figure 15

- la figure 17 illustre un pipeline du trajet de données dans une unité de contrôle d'antémémoire dans le processeur de la figure 2

- la figure 18 illustre des trajets de données pour un pipeline de traitement d'adresse dans une unité de contrôle d'antémémoire dans le système de la figure 2

- les figures 19-22 illustrent des machines d'état dans le processeur de la figure 2

- la figure 23 illustre des formats d'adresse utilisés dans le système d'antémémoire de la figure 15

- la figure 24 illustre un bus dans le processeur de la figure 2

- la figure 25 illustre une unité de contrôle d'arbitrage dans le processeur de la figure 2

- les figures 26-29 sont des diagrammes des temps pour le processeur de la figure 2

- les figures 30-32 montrent des signaux de demande de mémoire dans le processeur de la figure 2

- la figure 33 illustre une unité de contrôle d'arbitrage de bus dans le processeur de la figure 2

- les figures 34-36 sont des diagrammes des temps pour le processeur de la figure 2

- les figures 37-38 illustrent un ensemble de circuits d'interface de bus dans le processeur de la figure 2

- les figures 39-40 illustre une mémoire tampon de blocs virtuels (VFB) pour le système de la figure 1

- la figure 41 illustre un ensemble de circuits d'interface de bus pour le système de la figure 1

- les figures 42-43 illustrent un contrôleur de mémoire pour le système de la figure 1

- la figure 44 illustre un contrôleur d'adresse pour le système de la figure 1

- les figures 45 et 46 illustrent des formats utilisés dans le système de la figure 1

- la figure 47 illustre une machine d'état dans le système de la figure 1

- la figure 48 est un schéma bloc d'un contrôleur de données pour le système de la figure 1

- les figures 49-51 sont des diagrammes des temps pour le système de la figure 1

- les figures 52-53 illustrent un ensemble de circuits d'interface de dispositifs dans le processeur de la figure 2

- les figures 54-56 sont des schémas blocs de portions du système de la figure 1

- les figures 57-59 illustrent des registres dans le système de la figure 1

- la figure 60 illustre des tampons de blocs et des fenêtres vidéo dans le système de la figure 1

- la figure 61 est un diagramme des temps pour le système de la figure 1

- la figure 62 illustre un registre dans le système de la figure 1

- la figure 63 est un diagramme des temps pour le systeme de la figure 1 ; et

- les figures 64-66 illustrent des tampons utilisés dans le système de la figure 1.

- la figure 1 donne un schéma bloc d'une carte de support selon la présente invention;

- la figure 2 donne un schéma bloc d'un processeur multimédia selon la présente invention

- la figure 3 donne un schéma bloc d'un processeur du train de bits qui fait partie du processeur de la figure 2

- les figures 4-6 sont des schémas blocs de systèmes d'ordinateurs selon la présente invention

- la figure 7 illustre une architecture de microprogrammation dans le processeur de la figure 9

- les figures 8-9 montrent des topographies d'adresses pour le système de la figure 1

- la figure 10 donne un schéma bloc du noyau de DSP du processeur de la figure 2

- la figure 11 illustre un pipeline employé dans un processeur vectoriel qui fait partie du processeur de la figure 2

- la figure 12 est un schéma bloc fonctionnel du processeur vectoriel de la figure 11 ;

- la figure 13 illustre des trajets de données d'exécution dans le processeur vectoriel de la figure 11;

- la figure 14 illustre des trajets de données de charge et d'enregistrement dans le processeur vectoriel de la figure 11 ;

- la figure 15 est un schéma bloc d'un système d'antémémoire du processeur de la figure 2

- la figure 16 illustre l'antémémoire des données d'instructions dans le système d'antémémoire de la figure 15

- la figure 17 illustre un pipeline du trajet de données dans une unité de contrôle d'antémémoire dans le processeur de la figure 2

- la figure 18 illustre des trajets de données pour un pipeline de traitement d'adresse dans une unité de contrôle d'antémémoire dans le système de la figure 2

- les figures 19-22 illustrent des machines d'état dans le processeur de la figure 2

- la figure 23 illustre des formats d'adresse utilisés dans le système d'antémémoire de la figure 15

- la figure 24 illustre un bus dans le processeur de la figure 2

- la figure 25 illustre une unité de contrôle d'arbitrage dans le processeur de la figure 2

- les figures 26-29 sont des diagrammes des temps pour le processeur de la figure 2

- les figures 30-32 montrent des signaux de demande de mémoire dans le processeur de la figure 2

- la figure 33 illustre une unité de contrôle d'arbitrage de bus dans le processeur de la figure 2

- les figures 34-36 sont des diagrammes des temps pour le processeur de la figure 2

- les figures 37-38 illustrent un ensemble de circuits d'interface de bus dans le processeur de la figure 2

- les figures 39-40 illustre une mémoire tampon de blocs virtuels (VFB) pour le système de la figure 1

- la figure 41 illustre un ensemble de circuits d'interface de bus pour le système de la figure 1

- les figures 42-43 illustrent un contrôleur de mémoire pour le système de la figure 1

- la figure 44 illustre un contrôleur d'adresse pour le système de la figure 1

- les figures 45 et 46 illustrent des formats utilisés dans le système de la figure 1

- la figure 47 illustre une machine d'état dans le système de la figure 1

- la figure 48 est un schéma bloc d'un contrôleur de données pour le système de la figure 1

- les figures 49-51 sont des diagrammes des temps pour le système de la figure 1

- les figures 52-53 illustrent un ensemble de circuits d'interface de dispositifs dans le processeur de la figure 2

- les figures 54-56 sont des schémas blocs de portions du système de la figure 1

- les figures 57-59 illustrent des registres dans le système de la figure 1

- la figure 60 illustre des tampons de blocs et des fenêtres vidéo dans le système de la figure 1

- la figure 61 est un diagramme des temps pour le système de la figure 1

- la figure 62 illustre un registre dans le système de la figure 1

- la figure 63 est un diagramme des temps pour le systeme de la figure 1 ; et

- les figures 64-66 illustrent des tampons utilisés dans le système de la figure 1.

La figure 1 montre une carte de support 100 comprenant un processeur multimédia 110. Dans certains modes de réalisation, le processeur 110 est un processeur du type MSP-lEX (marque déposée) dont la description est produite par Samsung Semiconductor Corporation de San

Jose, Californie. Le processeur MSP-lEX est décrit dans l'Appendice A ci-dessous.

Jose, Californie. Le processeur MSP-lEX est décrit dans l'Appendice A ci-dessous.

Le processeur 110 communique avec un système d'ordinateur hôte (non représenté) via un bus local 105.

Dans certains modes de réalisation, le bus 105 est un bus

PCI de 32 bits, 33 MHz. Une sortie de données vidéo numériques du processeur 110 est connectée au convertisseur numérique/analogique 112. En plus de la portion vidéo, les données vidéo numériques peuvent inclure une portion audio, par exemple une piste sonore d'un film. La sortie du convertisseur 112 est appropriée pour une connexion à un téléviseur (non représenté) ou un autre système qui traite des données analogiques. Dans certains modes de réalisation, le processeur 110 comporte également un port d'accès d'entrée pour recevoir les données vidéo numériques d'un convertisseur analogique/numérique (voir figures 4-6).

PCI de 32 bits, 33 MHz. Une sortie de données vidéo numériques du processeur 110 est connectée au convertisseur numérique/analogique 112. En plus de la portion vidéo, les données vidéo numériques peuvent inclure une portion audio, par exemple une piste sonore d'un film. La sortie du convertisseur 112 est appropriée pour une connexion à un téléviseur (non représenté) ou un autre système qui traite des données analogiques. Dans certains modes de réalisation, le processeur 110 comporte également un port d'accès d'entrée pour recevoir les données vidéo numériques d'un convertisseur analogique/numérique (voir figures 4-6).

Le processeur 110 est connecté au Codec 114. Le

Codec 114 reçoit les données audio analogiques d'un enregistreur sur bande (non représenté) ou un autre dispositif. Le Codec 114 reçoit des données téléphoniques analogiques de lignes téléphoniques (non représentées).

Codec 114 reçoit les données audio analogiques d'un enregistreur sur bande (non représenté) ou un autre dispositif. Le Codec 114 reçoit des données téléphoniques analogiques de lignes téléphoniques (non représentées).

Le Codec 114 met les données analogiques sous forme numérique et les transmet au processeur 110. Le Codec 114 reçoit les données numériques du processeur 110, convertit ces données en une forme analogique et transmet les données analogiques selon la nécessité.

Le processeur 110 est connecté à une mémoire 120 par un bus 122. Sur la figure 1, la mémoire 120 est une mémoire SDRAM (mémoire à accès aléatoire numérique synchrone) et le bus 122 est un bus à 64 bits, 80 MHz.

D'autres mémoires, largeurs de bus, et vitesses de bus sont utilisées dans d'autres modes de réalisation. Des mémoires et bus asynchrones sont utilisés dans certains modes de réalisation.

Certains modes de réalisation de la carte 100 sont décrits dans la demande de brevet US "Multiprocessor

Operation in a Multimedia Signal Processor"(dossier numéro M-4354 US) déposée par Le Nguyen le même jour que la présente demande et incorporée ici par référence.

Operation in a Multimedia Signal Processor"(dossier numéro M-4354 US) déposée par Le Nguyen le même jour que la présente demande et incorporée ici par référence.

La figure 2 donne un schéma bloc d'un mode de réalisation du processeur 110. Le processeur 110 comprend un processeur scalaire 210, un coprocesseur vectoriel ("VP") 220, et un processeur du train de bits ("BP") 245.

Dans certains modes de réalisation, le processeur 210 est un processeur RISC à 32 bits qui fonctionne à 40 MHz et se conforme au groupe d'instructions standards de ARM7 connu. Le processeur vectoriel 220 est un processeur de données multiples à une seule instruction (SIMD) fonctionnant à 80 MHz et ayant des registres vectoriels de 288 bits. Un mode de réalisation du VP 220 est décrit dans la demande de brevet US "Efficient Context Saving and Restoring in a Multitasking Computing System

Environment" (dossier numéro M-4365 US) déposée par Song et al. à la même date que la présente demande et incorporée ici par référence. Les processeurs 210 et 220 peuvent être programmés pour exécuter une seule instruction arithmétique ou booléenne ou bien une séquence de telles instructions.

Environment" (dossier numéro M-4365 US) déposée par Song et al. à la même date que la présente demande et incorporée ici par référence. Les processeurs 210 et 220 peuvent être programmés pour exécuter une seule instruction arithmétique ou booléenne ou bien une séquence de telles instructions.

Dans certains modes de réalisation, afin d'obtenir une haute vitesse de traitement des données vidéo, le processeur 245 du train de bits est rendu incapable d'être programmé pour exécuter une seule instruction arithmétique ou booléenne. En particulier, BP 245 ne peut être programmé pour exécuter une seule instruction telle que ADDITION, OU, "ADDITION ET ACCUMULATION" et ainsi de suite. Par ailleurs, BP 245 peut recevoir l'instruction d'accomplir l'opération de traitement de données vidéo comme décrit dans l'Appendice A, Chapitre 10. En même temps, le processeur scalaire 210 et le processeur vectoriel 220 peuvent être programmés pour exécuter une seule instruction arithmétique ou booléenne. Par conséquent, le processeur 110 peut être adapté à des changements des standards vidéo.

Comme le montre la figure 2, le processeur scalaire 210 et le processeur vectoriel 220 sont connectés au sous-système d'antémémoire 230. Le sous-système d'antémémoire 230 est connecté au bus 240 ("IOBUS") et au bus 250 (1,FBUS"). Dans certains modes de réalisation,

IOBUS 240 est un bus à 32 bits, 40 MHz et FBUS 250 est un bus à 64 bits, 80 MHz.

IOBUS 240 est un bus à 32 bits, 40 MHz et FBUS 250 est un bus à 64 bits, 80 MHz.

IOBUS 240 est connecté au processeur du train de bits 245, au contrôleur d'interruption 248, à l'unité

UART en duplex intégral 243 et aux quatre temporisateurs 242. FBUS 250 est connecté au contrôleur de mémoire 258 qui à son tour est connecté au bus de mémoire 122 (figure 1). FBUS 250 est connecté au circuit d'interface 255 du bus PCI qui est connecté au bus PCI 105. FBUS 250 est également connecté au circuit d'interface de dispositifs 252 (appelé également "ASIC Client") qui comporte un ensemble de circuits pour une interface avec le convertisseur numérique/analogique vidéo 112 (figure 1), le Codec 114 et peut être un convertisseur analogique/numérique vidéo (tel que montré aux figures 46). Le processeur 110 comporte également un appareil de transfert de données de mémoire 290.

UART en duplex intégral 243 et aux quatre temporisateurs 242. FBUS 250 est connecté au contrôleur de mémoire 258 qui à son tour est connecté au bus de mémoire 122 (figure 1). FBUS 250 est connecté au circuit d'interface 255 du bus PCI qui est connecté au bus PCI 105. FBUS 250 est également connecté au circuit d'interface de dispositifs 252 (appelé également "ASIC Client") qui comporte un ensemble de circuits pour une interface avec le convertisseur numérique/analogique vidéo 112 (figure 1), le Codec 114 et peut être un convertisseur analogique/numérique vidéo (tel que montré aux figures 46). Le processeur 110 comporte également un appareil de transfert de données de mémoire 290.

Le processeur 110 peut traiter plusieurs trains de données en une fois. Par exemple, si un utilisateur du processeur 110 est en conférence vidéo avec deux correspondants ou plus, le processeur 110 produit un traitement vidéo et audio qui permet à l'utilisateur de voir et d'entendre les multiples correspondants. Pour traiter des trains de données vidéo multiples, le processeur 110 supporte un changement de contexte. Cela signifie que BP 245 change entre des trains de données multiples. Dans une conférence vidéo, chaque train de données peut provenir d'un correspondant éloigné séparé.

Alternativement, des trains additionnels de données peuvent provenir de canaux de film pour permettre à l'utilisateur de participer à la conférence vidéo et de regarder une ou plusieurs présentations de films en même temps. Un changement de contexte est décrit à l'Appendice

A, Section 10.12. Quand les contextes doivent être changés, le processeur scalaire 210 sauvegarde les contextes courants et initialise BP 245 pour traiter un contexte différent.

A, Section 10.12. Quand les contextes doivent être changés, le processeur scalaire 210 sauvegarde les contextes courants et initialise BP 245 pour traiter un contexte différent.

BP 245 peut traiter les formats de données vidéo qui suivent

1. MPEG-1 décrit dans la norme ISO/IEC 11172 (1992);

2. MPEG-2 décrit dans le document ISO/IEC JTC 1/SC 29 N 0981 Révision (31 mars 1995)

3. H.261 décrit dans "ITU-T Recommendation H.261" (mars 1993) ; et

4. H.263 décrit dans "Draft ITU-T Recommendation

H.263" (2 mai 1996).

1. MPEG-1 décrit dans la norme ISO/IEC 11172 (1992);

2. MPEG-2 décrit dans le document ISO/IEC JTC 1/SC 29 N 0981 Révision (31 mars 1995)

3. H.261 décrit dans "ITU-T Recommendation H.261" (mars 1993) ; et

4. H.263 décrit dans "Draft ITU-T Recommendation

H.263" (2 mai 1996).

Le traitement des données vidéo est divisé entre le processeur scalaire 210, le processeur vectoriel 220 et le processeur du train de bits 245 afin d'obtenir une vitesse élevée de traitement. plus particulièrement, le processeur vectoriel 220 accomplit des transformations linéaires (comme DCT-transformation cosinusoïdale discrète - ou son inverse IDCT) et accomplit une compensation du mouvement. Ces opérations sont appropriées pour un processeur vectoriel parce que ces opérations nécessitent fréquemment d'accomplir la même instruction sur des pièces multiples de données. Le processeur de train de bits 245 accomplit un décodage et un codage de HUFFMAN et un traitement de train de bits en zigzag. Le processeur scalaire 210 accomplit des tâches de démultiplexage et de synchronisation vidéo et audio, et de mise en interface E/O (entrée/sortie).

Des exemples des opérations de codage et de décodage sont donnés à l'Appendice A, Sections 10.6.1 et 10.6.2. Dans une opération de codage, les données numériques non comprimées arrivent de la mémoire 120 ou du système hôte (non représenté) par le bus 105. Dans certains modes de réalisation, le circuit d'interface 252 des dispositifs comprend un convertisseur analogique/numérique vidéo et les données non compriées arrivent du convetisseur. Le processeur vectoriel 220 accomplit une quantification, DCT et une compensation du mouvement. Le processeur du train de bits 245 reçoit la sortie de VP 220 et produit des GOB (GROUPES DE BLOCS) ou tranches. En particulier, BP 245 accomplit un codage de

HUFFMAN et RLC et un traitement du train de bits en zigzag. Le processeur scalaire 210 reçoit la sortie de BP 245 et accomplit un codage en couches de l'image, un codage GOP (groupe d'images) et un codage en couches de séquences. Le processeur scalaire 210 multiplexe alors les données audio et vidéo et transfère les données codées à un dispositif d'enregistrement (via le bus 105 ou 122) ou un réseau. Le transfert à un réseau implique le transfert au circuit d'interface de dispositifs 252 qui est connecté à un réseau dans certains modes de réalisation.

HUFFMAN et RLC et un traitement du train de bits en zigzag. Le processeur scalaire 210 reçoit la sortie de BP 245 et accomplit un codage en couches de l'image, un codage GOP (groupe d'images) et un codage en couches de séquences. Le processeur scalaire 210 multiplexe alors les données audio et vidéo et transfère les données codées à un dispositif d'enregistrement (via le bus 105 ou 122) ou un réseau. Le transfert à un réseau implique le transfert au circuit d'interface de dispositifs 252 qui est connecté à un réseau dans certains modes de réalisation.

Dans le décodage, le procédé est inversé. Le processeur scalaire 210 démultiplexe les données du système en composantes audio et vidéo et accomplit un décodage en couches de séquences, GOP, et de l'image des données vidéo. Les GOB résultants ou tranches sont appliqués au processeur 245 de train de bits. Le processeur 245 accomplit un traitement en zigzag et un décodage de HUFFMAN et RLC. VP 220 reçoit la sortie de BP 245 et accomplit une quantification, IDCT et une compensation du mouvement. VP 220 accomplit tout posttraitement qui peut être nécessaire (par exemple, pour lisser les bords des images) et produit des images numériques reconstruites pour le circuit d'interface de dispositifs 252 ou un dispositif d'enregistrement. Le processeur scalaire 210, le processeur vectoriel 220 et le processeur de train de bits 245 peuvent fonctionner sur différents blocs de données en parallèle.

Le fait que le processeur scalaire 210 traite la couche d'image et les couches supérieures réduit une communication entre processeurs. Cela est du au fait que la couche d'image et les couches supérieures contiennent une information qui est utilisée par le processeur scalaire 210 pour le contrôle et les fonctions E/S mais qui n'est pas utilisé par le processeur vectoriel 220 ou le processeur 245 de train de bits. Un exemple d'une telle information est une fréquence d'image utilisée par le processeur scalaire 210 pour transmettre les images au circuit d'interface de dispositifs 252.

La figure 3 est un schéma bloc d'un mode de réalisation du processeur 245 du train de bits. Les signaux montrés à la figure 3 sont décrits à l'Appendice

A, Section 10.5. Ces signaux permettent une interface entre le processeur de train de bits 245 et IOBUS 240 (figure 2). Dans BP 245, ces signaux sont traités par l'Unité d'Interface de IOBUS 310 qui comprend SRAM 320.

A, Section 10.5. Ces signaux permettent une interface entre le processeur de train de bits 245 et IOBUS 240 (figure 2). Dans BP 245, ces signaux sont traités par l'Unité d'Interface de IOBUS 310 qui comprend SRAM 320.

BP 345 comporte également l'unité FIFO (ler entré, premier sorti) de VLC 330, la mémoire morte ou rombe LUT 340 VLC, la machine d'état de contrôle 250 et l'unité de noyau de BP 360 qui comporte un fichier de registres et une SRAM. Les blocs de la figure 3 sont décrits à l'Appendice A, Section 10.4.

La ROM 340 contient des tables de consultation utilisées pour le codage et le décodage de HUFFMAN pour les 4 standards : MPEG 1, MPEG2 H.261 et H.263. Malgré la grande quantité d'informations stockées dans les tables, la ROM 340 est de petite dimension de 768 x 12 bits. La petite dimension est obtenue en partageant les tables et par d'autres techniques décrites à l'Appendice B, Section 4.

L'invention n'est pas limitée par les modes de réalisation décrits ci-dessus et les appendices cidessous. En particulier, l'invention n'est pas limitée par un ensemble de circuits, des fréquences d'horloge ou des temporisations de ces modes de réalisation.

APPENDICE A

DESCRIPTION SYSTEME MSP-1 EX

CHAPITRE 1 -- VUE GENERALE TECHNIQUE

Ce chapitre décrit une vue générale technique du

Processeur de Signaux Multimédia ("MSP-x") vu par les concepteurs de matériel et de logiciel.

DESCRIPTION SYSTEME MSP-1 EX

CHAPITRE 1 -- VUE GENERALE TECHNIQUE

Ce chapitre décrit une vue générale technique du

Processeur de Signaux Multimédia ("MSP-x") vu par les concepteurs de matériel et de logiciel.

1.1 FONCTIONNALITE

Les Processeurs de Signaux Multimédia (MSP-x) forment une famille de dispositifs VLSI monopuce conçus pour produire une large gamme de fonctionnalité intégrée pour des ordinateurs personnels et des applications de produuits de consommation.

Les Processeurs de Signaux Multimédia (MSP-x) forment une famille de dispositifs VLSI monopuce conçus pour produire une large gamme de fonctionnalité intégrée pour des ordinateurs personnels et des applications de produuits de consommation.

La famille MSP est basée sur une architecture puissante du Processeur Vectoriel employant un modèle de calcul à Données Multiples à Simple Instruction (SIMD) pour de meilleurs prix/performance. Ses caractéristiques comprennent

Pleine programmabilité

Basé sur l'Architecture du Groupe d'Instructions

de ARM

Noyau CPU RISC ARM 7 40 MHz Intégré

Processeur Vectoriel 80 MHz pour traitement de

signaux numériques haute performance

2,56 Gop pour opérations ALU sur entiers 9 bits

2,56 Gop pour opérations Accumululation

Multiplication sur entiers 16 bits

640 Mflop pour addition point flottant IEEE 32

bits

1280 Mflop pour multiplication et addition point

flottant IEEE 32 bits

10 k.portes non utilisées pour personnalisation

ou fonctionnalité graphique facultatives

A base de technologie CMOS 0,65 pm 3,3 v/5v

Module 128 broches à 256 broches

MSP supportera initialement 4 fonctionnalités

majeures

Vidéo

Audio/son

Télécommunications

Graphique 2D/3D (factulatif) 1.1.1 Vidéo

Toute fonctionnalité est programmable en micro

programmation

Décodage et codage MPEG-1 en temps réel

Décodage MPEG-2 en temps réel

Codage MPEG-2 presqu'en temps réel

Décodage et codage H.324 en temps réel

Cadrage de l'image pour toute grandeur de l'écran

ou résolution

Conversion espace couleur entre RGB et YUV

Filtration de l'image pour enrichissement du

modèle et réduction du bruit

Conversion appel 4/3 1.1.2 Audio/Son

Toute fonctionnalité est programmable en micro

programmation

Décodage et codage audio MPEG-I en temps réel

Décodage et codage audio MPEG-2 en temps réel

Décodage et codage audio H.320 et H.324 en temps

réel

Codage parole G.728 et le G.723 en temps réel

Emulation programmateur son en temps réel

Synthèse table d'ondes

Synthèse FM 1. 1.3 Télécommunications 1.1.3.1 Modem

Interface port COM asynchrone standard

(compatible NS 16550A UART)

V.34 de 28,8 K A 2,4 k pb

CCITT-V 32 bits avec fréquences des données de

4800, 9600 sans codage et 9600 pb en codage Trellis

Compatiblité ensemble commande AT de Hayes

Moniteur progression appel

Appel automatique V.25bis

DTMF et appel pulsé

Protocole récupération erreur asynchrone

Correction erreur V.42 1.1.3.2 Fac similé

e V.29 à 9600 pb ou 7200 pb

V.27ter à 4800 pb ou 2400 pb

Moniteur progression appel

Appel automatique

DTMF et appel pulsé

Transferts G3

Opérations T.4/T.30 1.1.3.3 Réponse par téléphone

Enregistrement des salutations via l'appareil

téléphonique ou le microphone

e Réponse automatique au téléphone et réponse avec

message pré-enregistré

Enregistrement d'un message d'une personne qui

appelle

Restitution des messages laissés par une personne

ayant appelé 1.1.4 Graphique2D/3D (facultatif)

BITBLT

Dessin et ombrage lignes et polygones 2D

Calcul géométrie et éclairage pour point, lignes

et triangles 3D

Calcul couleur 3D avec topographie texture

Mélange 1.2 Architecture du matériel 1.1.2 Vue générale

La famille des Coprocesseurs Multimédia MSP-1 est conçue pour répondre à diverses conditions comprenant le niveau d'intégration, le prix et la performance. Un schéma bloc d'un système comprenant un processeur MSP-1 apparaît à la figure 4.

Pleine programmabilité

Basé sur l'Architecture du Groupe d'Instructions

de ARM

Noyau CPU RISC ARM 7 40 MHz Intégré

Processeur Vectoriel 80 MHz pour traitement de

signaux numériques haute performance

2,56 Gop pour opérations ALU sur entiers 9 bits

2,56 Gop pour opérations Accumululation

Multiplication sur entiers 16 bits

640 Mflop pour addition point flottant IEEE 32

bits

1280 Mflop pour multiplication et addition point

flottant IEEE 32 bits

10 k.portes non utilisées pour personnalisation

ou fonctionnalité graphique facultatives

A base de technologie CMOS 0,65 pm 3,3 v/5v

Module 128 broches à 256 broches

MSP supportera initialement 4 fonctionnalités

majeures

Vidéo

Audio/son

Télécommunications

Graphique 2D/3D (factulatif) 1.1.1 Vidéo

Toute fonctionnalité est programmable en micro

programmation

Décodage et codage MPEG-1 en temps réel

Décodage MPEG-2 en temps réel

Codage MPEG-2 presqu'en temps réel

Décodage et codage H.324 en temps réel

Cadrage de l'image pour toute grandeur de l'écran

ou résolution

Conversion espace couleur entre RGB et YUV

Filtration de l'image pour enrichissement du

modèle et réduction du bruit

Conversion appel 4/3 1.1.2 Audio/Son

Toute fonctionnalité est programmable en micro

programmation

Décodage et codage audio MPEG-I en temps réel

Décodage et codage audio MPEG-2 en temps réel

Décodage et codage audio H.320 et H.324 en temps

réel

Codage parole G.728 et le G.723 en temps réel

Emulation programmateur son en temps réel

Synthèse table d'ondes

Synthèse FM 1. 1.3 Télécommunications 1.1.3.1 Modem

Interface port COM asynchrone standard

(compatible NS 16550A UART)

V.34 de 28,8 K A 2,4 k pb

CCITT-V 32 bits avec fréquences des données de

4800, 9600 sans codage et 9600 pb en codage Trellis

Compatiblité ensemble commande AT de Hayes

Moniteur progression appel

Appel automatique V.25bis

DTMF et appel pulsé

Protocole récupération erreur asynchrone

Correction erreur V.42 1.1.3.2 Fac similé

e V.29 à 9600 pb ou 7200 pb

V.27ter à 4800 pb ou 2400 pb

Moniteur progression appel

Appel automatique

DTMF et appel pulsé

Transferts G3

Opérations T.4/T.30 1.1.3.3 Réponse par téléphone

Enregistrement des salutations via l'appareil

téléphonique ou le microphone

e Réponse automatique au téléphone et réponse avec

message pré-enregistré

Enregistrement d'un message d'une personne qui

appelle

Restitution des messages laissés par une personne

ayant appelé 1.1.4 Graphique2D/3D (facultatif)

BITBLT

Dessin et ombrage lignes et polygones 2D

Calcul géométrie et éclairage pour point, lignes

et triangles 3D

Calcul couleur 3D avec topographie texture

Mélange 1.2 Architecture du matériel 1.1.2 Vue générale

La famille des Coprocesseurs Multimédia MSP-1 est conçue pour répondre à diverses conditions comprenant le niveau d'intégration, le prix et la performance. Un schéma bloc d'un système comprenant un processeur MSP-1 apparaît à la figure 4.

La famile de MSP-1 comporte les options suivantes

MSP-1 est conçu pour être utilisé en tant que

niveau d'entrée sans SDRAM externe

MSP-lEX comporte un bus de mémoire à 32 bits pour

une mise en interface avec SDRAM externe

MSP-lF comporte un bus de mémoire à 64 bits pour

une mise en interface avec SDRAM externe

MPS-lG comporte un contrôleur SVGA intégré,

RAMDAC plus accélération graphique 3D assez

rapide.

MSP-1 est conçu pour être utilisé en tant que

niveau d'entrée sans SDRAM externe

MSP-lEX comporte un bus de mémoire à 32 bits pour

une mise en interface avec SDRAM externe

MSP-lF comporte un bus de mémoire à 64 bits pour

une mise en interface avec SDRAM externe

MPS-lG comporte un contrôleur SVGA intégré,

RAMDAC plus accélération graphique 3D assez

rapide.

La figure 5 montre un schéma bloc d'un système comprenant un processeur MSP-1E 1.2.2 CODEC externes

La figure 6 montre un schéma bloc d'un système

comprenant un processeur MSP-1 avec codec externes 1.2.2.1 Nomenclature MSP-lEX

Une nomenclature suggérée pour MSP-lEX est donnée

ci-dessous

MSP-lEX

DRAM synchrone 512 K x 32 bits

Codeur NTSC/PAL (KS0119 DE SAMSUNG)

Codec Audio et Télécommunications (AD1843 de

ANALOG DEVICES)

Divers (condensateurs, résistances,

amplificateurs, connecteurs etc..)

Planche de Circuit Imprimé 1.3 MICRO ARCHITECTURE 1.3.1 Vue générale

La micro-architecture de MSP se compose à la base

d'un NOYAU très puissant de DSP et d'une Mémoire

spécifique du client et de sous-systèmes E/S. Voir

figure 2. Le NOYAU de DSP comporte

Une CPU RISC de ARM7 de 32 bits fonctionnant à

40 MHz et qui est utilisée pour un traitement

général et

Un Processeur Vectoriel fonctionnant à 80 MHz et

qui est utilisé pour le traitement des signaux

Un sous-Système Antémémoire partagé fonctionnant

à 80 MHz et qui contient une antémémoire

d'instructions de 2 KB, une antémémoire de

données de 5 KB et une antémémoire de ROM de 16

KB.

La figure 6 montre un schéma bloc d'un système

comprenant un processeur MSP-1 avec codec externes 1.2.2.1 Nomenclature MSP-lEX

Une nomenclature suggérée pour MSP-lEX est donnée

ci-dessous

MSP-lEX

DRAM synchrone 512 K x 32 bits

Codeur NTSC/PAL (KS0119 DE SAMSUNG)

Codec Audio et Télécommunications (AD1843 de

ANALOG DEVICES)

Divers (condensateurs, résistances,

amplificateurs, connecteurs etc..)

Planche de Circuit Imprimé 1.3 MICRO ARCHITECTURE 1.3.1 Vue générale

La micro-architecture de MSP se compose à la base

d'un NOYAU très puissant de DSP et d'une Mémoire

spécifique du client et de sous-systèmes E/S. Voir

figure 2. Le NOYAU de DSP comporte

Une CPU RISC de ARM7 de 32 bits fonctionnant à

40 MHz et qui est utilisée pour un traitement

général et

Un Processeur Vectoriel fonctionnant à 80 MHz et

qui est utilisé pour le traitement des signaux

Un sous-Système Antémémoire partagé fonctionnant

à 80 MHz et qui contient une antémémoire

d'instructions de 2 KB, une antémémoire de

données de 5 KB et une antémémoire de ROM de 16

KB.

L'antémémoire de données peut être contrôlée par

le matériel ou le logiciel.

le matériel ou le logiciel.

Un bus 64-bit rapide (FBUS) fonctionnant à 80 MHz

et qui est en interface avec un certain nombre de

périphériques de FBUS interne.

et qui est en interface avec un certain nombre de

périphériques de FBUS interne.

Un bus plus lent de 32-bit (IOBUS) fonctionnant à

40 MHz et en interface avec un certain nombre de

périphériques de IOBUS.

40 MHz et en interface avec un certain nombre de

périphériques de IOBUS.

Les périphériques de FBUS interne comprennent

Une interface bus PCI 32-bit 33 MHz

Un contrôleur de mémoire SDRAM 64-bit

Un contrôleur de DMA 8 canaux

Un bloc logique ASIC Client. Le bloc logique ASIC

Client produit un total de 10 k-portes qui comporte à la fois les interfaces vers divers CODEC analogiques et dispositifs E/S spécifiques du client. la logique d'interface supporte le Codeur

NTSC KS1019 de SAMSUNG et les CODEC AD183 de ANALOG

DEVICES.

Une interface bus PCI 32-bit 33 MHz

Un contrôleur de mémoire SDRAM 64-bit

Un contrôleur de DMA 8 canaux

Un bloc logique ASIC Client. Le bloc logique ASIC

Client produit un total de 10 k-portes qui comporte à la fois les interfaces vers divers CODEC analogiques et dispositifs E/S spécifiques du client. la logique d'interface supporte le Codeur

NTSC KS1019 de SAMSUNG et les CODEC AD183 de ANALOG

DEVICES.

Un Appareil de Transfert de Données de Mémoire

qui est utilisé pour les données DMA de la

mémoire hôte (Pentlure) à la mémoire SDRAM locale

de MSP

Les périphériques de 1'IOBUS interne comprennent

Un Processeur du Train de Bits responsable du

traitement du train de bits vidéo

Une Ligne en Série UART 16450

Un temporisateur compatible 8254 e Un Contrôleur d'Interruption compatible 8259

MSP comporte également un registre spécial (Registre

Contrôle MSP) qui est utilisé pour l'initialisation et les interruptions contrôlées par le logiciel.

qui est utilisé pour les données DMA de la

mémoire hôte (Pentlure) à la mémoire SDRAM locale

de MSP

Les périphériques de 1'IOBUS interne comprennent

Un Processeur du Train de Bits responsable du

traitement du train de bits vidéo

Une Ligne en Série UART 16450

Un temporisateur compatible 8254 e Un Contrôleur d'Interruption compatible 8259

MSP comporte également un registre spécial (Registre

Contrôle MSP) qui est utilisé pour l'initialisation et les interruptions contrôlées par le logiciel.

1.4 DESCRIPTION DES BROCHES DE MSP-lEX 1.4.1 Total : 256 broches 1.4.2 Interface Bus PCI (53 broches)

CLK Broche d'Entrée d'Horloge

RSTL Broche Entrée Remise à l'Etat Initial, Bas actif.

CLK Broche d'Entrée d'Horloge

RSTL Broche Entrée Remise à l'Etat Initial, Bas actif.

AD[31:0] Broche Bus Adresses et Données

C~BEOL Broche Validation Contrôle et Octet 0, Bas actif.

C~BEOL Broche Validation Contrôle et Octet 0, Bas actif.

C BEL Broche Validation Contrôle et Octet 1, Bas actif.

C~BE2L Broche Validation Contrôle et Octet 2, Bas actif.

C~BE3L Broche Validation Contrôle et Octet 3, Bas actif.

PAR Broche Parité

FRAMEL Broche Bloc Cycle, Bas actif.

FRAMEL Broche Bloc Cycle, Bas actif.

IRDYL Broche Initiateur Prêt, Bas actif.

TRDYL Broche Cible Prête, Bas actif.

STOPL Broche Arrêt Transaction, Bas actif.

LOCKL Broche Blocage Transaction, Bas actif.

IDSEL Broche Entrée Sélection Initialisation Dispositif

DEVSEL Broche Sélection Dispositif, Bas actif.

DEVSEL Broche Sélection Dispositif, Bas actif.

REQL Broche Demande Bus, Bas actif.

GNTL Broche Accord Bus, Bas actif.

PERRL Broche Erreur Parité, Bas actif.

SERRL Broche Erreur Système, Bas actif.

INTAL Broche Interruption A, Bas actif.

1.4.3 Divers (6 broches)

TCK Broche Entrée Horloge Test JTAG

TD1 Broche Entrée Données Test JTAG

TD0 Broche Sortie Données Test JTAG

TMS Broche Entrée Sélection Mode Test JTAG

TRSTL Broche Entrée Remise Etat Initial Test JTAG

CLK Entrée Horloge. C'est la broche d'entrée d'horloge

à 40 MHz 1.4.4 Interface NTSC K0119/Codeur PAL (24 broches)

SFRS Sortie synchronisation bloc vers KS0119 pour

interface hôte 3 fils

SCLK Sortie horloge en série vers KS0119

SDAT Données série E/S

BGHS Signal Synchronisation Horizontale, entrée vers MSP

BGVS Signal Synchronisation Verticale, entrée vers MSP

MSSEL Sélection Pilote PD[15:0] Sortie Données Elément d'Image vers KS0119

BGCLK Sortie Horloge Elément d'Image vers KS0119

PROMCSL Sélection Puce PROM BIOS 1.4.5 InterfaceCODEC audio et télécommunications AD1843 (6 broches)

A43SCLK Horloge en série, entrée/sortie. SCLK est un signal

bidirectionnel qui fournit l'horloge comme sortie

au bus en série quand la broche du Bus Maître (BM)

est entrainée vers le haut et accepte l'horloge

comme entrée quand la broche de BM est entrainée

vers le bas.

TCK Broche Entrée Horloge Test JTAG

TD1 Broche Entrée Données Test JTAG

TD0 Broche Sortie Données Test JTAG

TMS Broche Entrée Sélection Mode Test JTAG

TRSTL Broche Entrée Remise Etat Initial Test JTAG

CLK Entrée Horloge. C'est la broche d'entrée d'horloge

à 40 MHz 1.4.4 Interface NTSC K0119/Codeur PAL (24 broches)

SFRS Sortie synchronisation bloc vers KS0119 pour

interface hôte 3 fils

SCLK Sortie horloge en série vers KS0119

SDAT Données série E/S

BGHS Signal Synchronisation Horizontale, entrée vers MSP

BGVS Signal Synchronisation Verticale, entrée vers MSP

MSSEL Sélection Pilote PD[15:0] Sortie Données Elément d'Image vers KS0119

BGCLK Sortie Horloge Elément d'Image vers KS0119

PROMCSL Sélection Puce PROM BIOS 1.4.5 InterfaceCODEC audio et télécommunications AD1843 (6 broches)

A43SCLK Horloge en série, entrée/sortie. SCLK est un signal

bidirectionnel qui fournit l'horloge comme sortie

au bus en série quand la broche du Bus Maître (BM)

est entrainée vers le haut et accepte l'horloge

comme entrée quand la broche de BM est entrainée

vers le bas.

A43SDFS Synchronisation Trame Données Série, entrée/sortie.

SDFS est un signal bidirectionnel qui fournit le

signal de synchronisation de trame comme sortie

vers le bus série quand la borne du Bus Maître (BM)

est entrainée vers le haut et accepte le signal de

synchronisation de trame comme entrée quand la

broche de BM est entrainée vers le bas.

signal de synchronisation de trame comme sortie

vers le bus série quand la borne du Bus Maître (BM)

est entrainée vers le haut et accepte le signal de

synchronisation de trame comme entrée quand la

broche de BM est entrainée vers le bas.

A43SDI Entrée Données Série vers AD1843, sortie de MSP.

Tous les transferts de contrôle et de réstitution ont 16-bit de lont, MSB d'abord.

A43SDO Sortie Données Série de AD1843, entrée vers MSP.

Tout les transferts de lecture et de restitution

des registres d'état et de contrôle ont 16-bit de

long, MSB premier 1.4.6 InterfaseBus Mémoire (87 broches)

RAS1L Broche de sortie (Bas actif). Ce sont des

Echantillons d'Adresse de Rangée pour

verrouiller les adresses de rangée MA [11:0]

dans le tampon d'adresses de rangée interne de

la rangée de SDRAM sélectionnée.

des registres d'état et de contrôle ont 16-bit de

long, MSB premier 1.4.6 InterfaseBus Mémoire (87 broches)

RAS1L Broche de sortie (Bas actif). Ce sont des

Echantillons d'Adresse de Rangée pour

verrouiller les adresses de rangée MA [11:0]

dans le tampon d'adresses de rangée interne de

la rangée de SDRAM sélectionnée.

CAS 1L Broche de sortie (Bas actif). Ce sont des

échantillons d'adresse de colonne pour verrouiller

les adresses de colonne de MA [11:0] dans le tampon

d'adresse de colonne interne de la rangée de SDRAM

sélectionnée.

échantillons d'adresse de colonne pour verrouiller

les adresses de colonne de MA [11:0] dans le tampon

d'adresse de colonne interne de la rangée de SDRAM

sélectionnée.

MWEL Broche de sortie (Bas actif) c'est une

Validation d'Ecriture vers la SDRAM MAI[11:0] Broche de sortie. Signaux multiplexés d'adresse de

rangée et de colonne vers SDRAM

MD [63:0] Broche de données de SDRAM d'entrée/sortie.

Validation d'Ecriture vers la SDRAM MAI[11:0] Broche de sortie. Signaux multiplexés d'adresse de

rangée et de colonne vers SDRAM

MD [63:0] Broche de données de SDRAM d'entrée/sortie.

MA23 Broche de sortie. Bit Adresse Mémoire < 23 >

MDA24 Broche de sortie. Bit d'Adresse de Mémoire < 24 >

DQM Broche de sortie. Donne à la sortie de données de

SDRAM une haute impédance après l'horloge et

masque la sortie (cette broche est utilisée pour

interface DRAM synchrone uniquement)

MCKE Broche de sortie. Masque l'horloge du système de la

SDRAM pour geler l'opération à partir du cycle

d'horloge suivant.

MDA24 Broche de sortie. Bit d'Adresse de Mémoire < 24 >

DQM Broche de sortie. Donne à la sortie de données de

SDRAM une haute impédance après l'horloge et

masque la sortie (cette broche est utilisée pour

interface DRAM synchrone uniquement)

MCKE Broche de sortie. Masque l'horloge du système de la

SDRAM pour geler l'opération à partir du cycle

d'horloge suivant.

MCSOL Broche de sortie (Bas actif). Sélection Puce SDRAM

pour 32-bits Bas

MCS1L Broche de sortie (Bas actif). Sélection Puce SDRAM

32-bit hauts

MR.DYH Broche de sortie. Signal SDRAM prête.

pour 32-bits Bas

MCS1L Broche de sortie (Bas actif). Sélection Puce SDRAM

32-bit hauts

MR.DYH Broche de sortie. Signal SDRAM prête.

MEMCLK Broche de sortie c'est la broche de sortie

d'horloge vers la SDRAM 1.4.7 Alimentations en courant

VDD Broches Puissance 3,3 volts

VCC Broches Puissance 5 volts

VSS Broches masse

Tableau 1 Assignation Broches MSP-1 EX

d'horloge vers la SDRAM 1.4.7 Alimentations en courant

VDD Broches Puissance 3,3 volts

VCC Broches Puissance 5 volts

VSS Broches masse

Tableau 1 Assignation Broches MSP-1 EX

<tb> <SEP> Plot <SEP> Broche <SEP> Type <SEP> Nom <SEP> Description

<tb> Puce <SEP> N <SEP> Module

<tb> <SEP> N

<tb> <SEP> 1 <SEP> 202 <SEP> EN <SEP> VDD <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 3,3 <SEP> V

<tb> <SEP> 2 <SEP> 1 <SEP> E/S <SEP> AD31 <SEP> Adresse <SEP> et <SEP> Données <SEP> pour <SEP> bus <SEP> PCI

<tb> <SEP> 3 <SEP> 2 <SEP> E/S <SEP> AD30

<tb> <SEP> 4 <SEP> 3 <SEP> E/S <SEP> AD29

<tb> <SEP> 5 <SEP> 4 <SEP> E/S <SEP> AD28

<tb> <SEP> 6 <SEP> ~ <SEP> 5 <SEP> E/S <SEP> AD27

<tb> <SEP> 7 <SEP> 205 <SEP> EN <SEP> GND <SEP> Terre

<tb> <SEP> 8 <SEP> 6 <SEP> EN <SEP> VCC <SEP> Alimentation <SEP> en <SEP> courant <SEP> S <SEP> V

<tb> <SEP> 9 <SEP> 7 <SEP> E/S <SEP> AD26 <SEP> Adresse <SEP> et <SEP> Données <SEP> pour <SEP> bus <SEP> PCI

<tb> <SEP> 10 <SEP> S <SEP> E/S <SEP> AD25~S09 <SEP> Adresse <SEP> et <SEP> Données <SEP> pour <SEP> bus <SEP> PCI/test

<tb> <SEP> Série <SEP> sortie

<tb> <SEP> 11 <SEP> 9 <SEP> E/S <SEP> AD24~SO8 <SEP> Adresse <SEP> et <SEP> données <SEP> pour <SEP> bus <SEP> PCI/test

<tb> <SEP> Série <SEP> sortie

<tb> <SEP> 12 <SEP> 10 <SEP> E/S <SEP> C <SEP> BE3L <SEP> Validation <SEP> contrôl/octet <SEP> pour <SEP> PCI

<tb> <SEP> 13 <SEP> 208 <SEP> EN <SEP> VDD <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 3,3 <SEP> V

<tb> <SEP> 14 <SEP> 11 <SEP> EN <SEP> IDSEL <SEP> Initialisation <SEP> Sélection <SEP> pour <SEP> PCI

<tb> <SEP> 15 <SEP> 12 <SEP> ; <SEP> E/S <SEP> AD23 <SEP> SP7 <SEP> Adresse <SEP> et <SEP> Données <SEP> pour <SEP> bus <SEP> PCI/Test

<tb> <SEP> Série <SEP> sortie

<tb> <SEP> 16 <SEP> 13 <SEP> E/S <SEP> AD22 <SEP> 506

<tb> <SEP> 17 <SEP> 14 <SEP> E/S <SEP> AD21 <SEP> SO5

<tb> <SEP> 18 <SEP> 15 <SEP> E/S <SEP> AD20 <SEP> S04

<tb> <SEP> 19 <SEP> 209 <SEP> EN <SEP> GND <SEP> Terre

<tb> <SEP> 20 <SEP> 16 <SEP> EN <SEP> VCC <SEP> Alimentation <SEP> en <SEP> Courant <SEP> S <SEP> V

<tb> <SEP> 21 <SEP> 17 <SEP> E/S <SEP> AD19~SO3 <SEP> Adresse <SEP> et <SEP> Données <SEP> pour <SEP> bus <SEP> PCI/Test

<tb> <SEP> Série <SEP> sortie

<tb> <SEP> 22 <SEP> 18 <SEP> E/S <SEP> AD18~SO2

<tb> <SEP> 23 <SEP> 19 <SEP> E/S <SEP> AD17~SO1

<tb> <SEP> 24 <SEP> 210 <SEP> EN <SEP> VDD <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 3,3 <SEP> V

<tb> <SEP> 25 <SEP> 20 <SEP> E/S <SEP> AD16~SO0 <SEP> Adresse <SEP> et <SEP> données <SEP> pour <SEP> bus <SEP> PCI/Test

<tb> <SEP> Serie <SEP> sortie

<tb>

<tb> Puce <SEP> N <SEP> Module

<tb> <SEP> N

<tb> <SEP> 1 <SEP> 202 <SEP> EN <SEP> VDD <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 3,3 <SEP> V

<tb> <SEP> 2 <SEP> 1 <SEP> E/S <SEP> AD31 <SEP> Adresse <SEP> et <SEP> Données <SEP> pour <SEP> bus <SEP> PCI

<tb> <SEP> 3 <SEP> 2 <SEP> E/S <SEP> AD30

<tb> <SEP> 4 <SEP> 3 <SEP> E/S <SEP> AD29

<tb> <SEP> 5 <SEP> 4 <SEP> E/S <SEP> AD28

<tb> <SEP> 6 <SEP> ~ <SEP> 5 <SEP> E/S <SEP> AD27

<tb> <SEP> 7 <SEP> 205 <SEP> EN <SEP> GND <SEP> Terre

<tb> <SEP> 8 <SEP> 6 <SEP> EN <SEP> VCC <SEP> Alimentation <SEP> en <SEP> courant <SEP> S <SEP> V

<tb> <SEP> 9 <SEP> 7 <SEP> E/S <SEP> AD26 <SEP> Adresse <SEP> et <SEP> Données <SEP> pour <SEP> bus <SEP> PCI

<tb> <SEP> 10 <SEP> S <SEP> E/S <SEP> AD25~S09 <SEP> Adresse <SEP> et <SEP> Données <SEP> pour <SEP> bus <SEP> PCI/test

<tb> <SEP> Série <SEP> sortie

<tb> <SEP> 11 <SEP> 9 <SEP> E/S <SEP> AD24~SO8 <SEP> Adresse <SEP> et <SEP> données <SEP> pour <SEP> bus <SEP> PCI/test

<tb> <SEP> Série <SEP> sortie

<tb> <SEP> 12 <SEP> 10 <SEP> E/S <SEP> C <SEP> BE3L <SEP> Validation <SEP> contrôl/octet <SEP> pour <SEP> PCI

<tb> <SEP> 13 <SEP> 208 <SEP> EN <SEP> VDD <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 3,3 <SEP> V

<tb> <SEP> 14 <SEP> 11 <SEP> EN <SEP> IDSEL <SEP> Initialisation <SEP> Sélection <SEP> pour <SEP> PCI

<tb> <SEP> 15 <SEP> 12 <SEP> ; <SEP> E/S <SEP> AD23 <SEP> SP7 <SEP> Adresse <SEP> et <SEP> Données <SEP> pour <SEP> bus <SEP> PCI/Test

<tb> <SEP> Série <SEP> sortie

<tb> <SEP> 16 <SEP> 13 <SEP> E/S <SEP> AD22 <SEP> 506

<tb> <SEP> 17 <SEP> 14 <SEP> E/S <SEP> AD21 <SEP> SO5

<tb> <SEP> 18 <SEP> 15 <SEP> E/S <SEP> AD20 <SEP> S04

<tb> <SEP> 19 <SEP> 209 <SEP> EN <SEP> GND <SEP> Terre

<tb> <SEP> 20 <SEP> 16 <SEP> EN <SEP> VCC <SEP> Alimentation <SEP> en <SEP> Courant <SEP> S <SEP> V

<tb> <SEP> 21 <SEP> 17 <SEP> E/S <SEP> AD19~SO3 <SEP> Adresse <SEP> et <SEP> Données <SEP> pour <SEP> bus <SEP> PCI/Test

<tb> <SEP> Série <SEP> sortie

<tb> <SEP> 22 <SEP> 18 <SEP> E/S <SEP> AD18~SO2

<tb> <SEP> 23 <SEP> 19 <SEP> E/S <SEP> AD17~SO1

<tb> <SEP> 24 <SEP> 210 <SEP> EN <SEP> VDD <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 3,3 <SEP> V

<tb> <SEP> 25 <SEP> 20 <SEP> E/S <SEP> AD16~SO0 <SEP> Adresse <SEP> et <SEP> données <SEP> pour <SEP> bus <SEP> PCI/Test

<tb> <SEP> Serie <SEP> sortie

<tb>

<tb> <SEP> Plot <SEP> Broche <SEP> Type <SEP> Nom <SEP> Description

<tb> <SEP> Puce <SEP> N <SEP> Module

<tb> <SEP> N

<tb> <SEP> 26 <SEP> 21 <SEP> E/S <SEP> C <SEP> BE2t <SEP> Validation <SEP> Contrôle/Octet <SEP> pour <SEP> PCI

<tb> <SEP> 27 <SEP> 22 <SEP> E/S <SEP> FRAMEL <SEP> Début <SEP> du <SEP> cycle <SEP> du <SEP> bus <SEP> PCI

<tb> <SEP> 28 <SEP> 23 <SEP> E/S <SEP> IRDYL <SEP> Initiateur <SEP> prêt <SEP> sur <SEP> PCI <SEP> (Pilote)

<tb> <SEP> 29 <SEP> 211 <SEP> EN <SEP> GND <SEP> Terre

<tb> <SEP> 30 <SEP> 24 <SEP> E/S <SEP> TRDYL <SEP> Cible <SEP> prête <SEP> sur <SEP> PCI <SEP> (Esclave)

<tb> <SEP> 31 <SEP> 25 <SEP> EN <SEP> VCC <SEP> Alimentation <SEP> en <SEP> Courant

<tb> <SEP> 32 <SEP> 26 <SEP> E/S <SEP> DVSELL <SEP> Sélection <SEP> Dispositif <SEP> sur <SEP> PCI

<tb> <SEP> 33 <SEP> 27 <SEP> E/S <SEP> STOPL <SEP> Arrêt <SEP> Transaction <SEP> Courante <SEP> sur <SEP> PCI

<tb> <SEP> 34 <SEP> 28 <SEP> E/S <SEP> LOCKL <SEP> Bloquage <SEP> Transaction <SEP> Courante <SEP> sur

<tb> <SEP> PCI

<tb> <SEP> 35 <SEP> 214 <SEP> EN <SEP> VDD <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 3,3 <SEP> V

<tb> <SEP> 36 <SEP> 29 <SEP> E/S <SEP> PERRL <SEP> Erreur <SEP> Parité <SEP> sur <SEP> PCI

<tb> <SEP> 37 <SEP> 30 <SEP> E/S <SEP> SERRL <SEP> Erreur <SEP> Système <SEP> sur <SEP> PCI

<tb> <SEP> 38 <SEP> 31 <SEP> EN <SEP> TCA <SEP> Horloge <SEP> Test <SEP> A

<tb> <SEP> 39 <SEP> 32 <SEP> E/S <SEP> PAR <SEP> Parité <SEP> sur <SEP> PCI

<tb> <SEP> 40 <SEP> 215 <SEP> EN <SEP> GND <SEP> Terre

<tb> <SEP> 41 <SEP> 33 <SEP> E/S <SEP> C <SEP> BEIL <SEP> Validation <SEP> Contrôle/Octet <SEP> pour <SEP> PCI

<tb> <SEP> 42 <SEP> 34 <SEP> E/S <SEP> AD15 <SEP> S19 <SEP> Adresse <SEP> et <SEP> Données <SEP> pour <SEP> bus <SEP> PCI/Test

<tb> <SEP> Série <SEP> entrée

<tb> <SEP> 43 <SEP> 35 <SEP> EN <SEP> VCC <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 5 <SEP> V

<tb> <SEP> 44 <SEP> 36 <SEP> E/S <SEP> AD14 <SEP> S18 <SEP> Adresse <SEP> et <SEP> Données <SEP> pour <SEP> bus <SEP> PCI/Test

<tb> <SEP> de <SEP> Série <SEP> Entrée <SEP> PCI

<tb> <SEP> 45 <SEP> 37 <SEP> E/S <SEP> AD13 <SEP> S17

<tb> <SEP> 46 <SEP> 38 <SEP> E/S <SEP> AD12@S16

<tb> <SEP> 47 <SEP> 218 <SEP> EN <SEP> VDD <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 3.3 <SEP> V

<tb> <SEP> 48 <SEP> 39 <SEP> E/S <SEP> AD11~S15 <SEP> Adresse <SEP> et <SEP> données <SEP> pour <SEP> bus <SEP> PCI/test <SEP>

<tb> <SEP> serie <SEP> entrée

<tb> <SEP> 49 <SEP> 40 <SEP> E/S <SEP> AD10 <SEP> S14

<tb> 50 <SEP> 41 <SEP> E/S <SEP> AD09 <SEP> S13 <SEP>

<tb> <SEP> 51 <SEP> 42 <SEP> E/S <SEP> AD08 <SEP> S12

<tb> <SEP> 52 <SEP> 221 <SEP> EN <SEP> GND <SEP> Terre

<tb> <SEP> 53 <SEP> 43 <SEP> E/S <SEP> C <SEP> BEOL <SEP> Validation <SEP> Contrle/Octet <SEP> pour <SEP> PCI

<tb>

<tb> <SEP> Puce <SEP> N <SEP> Module

<tb> <SEP> N

<tb> <SEP> 26 <SEP> 21 <SEP> E/S <SEP> C <SEP> BE2t <SEP> Validation <SEP> Contrôle/Octet <SEP> pour <SEP> PCI

<tb> <SEP> 27 <SEP> 22 <SEP> E/S <SEP> FRAMEL <SEP> Début <SEP> du <SEP> cycle <SEP> du <SEP> bus <SEP> PCI

<tb> <SEP> 28 <SEP> 23 <SEP> E/S <SEP> IRDYL <SEP> Initiateur <SEP> prêt <SEP> sur <SEP> PCI <SEP> (Pilote)

<tb> <SEP> 29 <SEP> 211 <SEP> EN <SEP> GND <SEP> Terre

<tb> <SEP> 30 <SEP> 24 <SEP> E/S <SEP> TRDYL <SEP> Cible <SEP> prête <SEP> sur <SEP> PCI <SEP> (Esclave)

<tb> <SEP> 31 <SEP> 25 <SEP> EN <SEP> VCC <SEP> Alimentation <SEP> en <SEP> Courant

<tb> <SEP> 32 <SEP> 26 <SEP> E/S <SEP> DVSELL <SEP> Sélection <SEP> Dispositif <SEP> sur <SEP> PCI

<tb> <SEP> 33 <SEP> 27 <SEP> E/S <SEP> STOPL <SEP> Arrêt <SEP> Transaction <SEP> Courante <SEP> sur <SEP> PCI

<tb> <SEP> 34 <SEP> 28 <SEP> E/S <SEP> LOCKL <SEP> Bloquage <SEP> Transaction <SEP> Courante <SEP> sur

<tb> <SEP> PCI

<tb> <SEP> 35 <SEP> 214 <SEP> EN <SEP> VDD <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 3,3 <SEP> V

<tb> <SEP> 36 <SEP> 29 <SEP> E/S <SEP> PERRL <SEP> Erreur <SEP> Parité <SEP> sur <SEP> PCI

<tb> <SEP> 37 <SEP> 30 <SEP> E/S <SEP> SERRL <SEP> Erreur <SEP> Système <SEP> sur <SEP> PCI

<tb> <SEP> 38 <SEP> 31 <SEP> EN <SEP> TCA <SEP> Horloge <SEP> Test <SEP> A

<tb> <SEP> 39 <SEP> 32 <SEP> E/S <SEP> PAR <SEP> Parité <SEP> sur <SEP> PCI

<tb> <SEP> 40 <SEP> 215 <SEP> EN <SEP> GND <SEP> Terre

<tb> <SEP> 41 <SEP> 33 <SEP> E/S <SEP> C <SEP> BEIL <SEP> Validation <SEP> Contrôle/Octet <SEP> pour <SEP> PCI

<tb> <SEP> 42 <SEP> 34 <SEP> E/S <SEP> AD15 <SEP> S19 <SEP> Adresse <SEP> et <SEP> Données <SEP> pour <SEP> bus <SEP> PCI/Test

<tb> <SEP> Série <SEP> entrée

<tb> <SEP> 43 <SEP> 35 <SEP> EN <SEP> VCC <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 5 <SEP> V

<tb> <SEP> 44 <SEP> 36 <SEP> E/S <SEP> AD14 <SEP> S18 <SEP> Adresse <SEP> et <SEP> Données <SEP> pour <SEP> bus <SEP> PCI/Test

<tb> <SEP> de <SEP> Série <SEP> Entrée <SEP> PCI

<tb> <SEP> 45 <SEP> 37 <SEP> E/S <SEP> AD13 <SEP> S17

<tb> <SEP> 46 <SEP> 38 <SEP> E/S <SEP> AD12@S16

<tb> <SEP> 47 <SEP> 218 <SEP> EN <SEP> VDD <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 3.3 <SEP> V

<tb> <SEP> 48 <SEP> 39 <SEP> E/S <SEP> AD11~S15 <SEP> Adresse <SEP> et <SEP> données <SEP> pour <SEP> bus <SEP> PCI/test <SEP>

<tb> <SEP> serie <SEP> entrée

<tb> <SEP> 49 <SEP> 40 <SEP> E/S <SEP> AD10 <SEP> S14

<tb> 50 <SEP> 41 <SEP> E/S <SEP> AD09 <SEP> S13 <SEP>

<tb> <SEP> 51 <SEP> 42 <SEP> E/S <SEP> AD08 <SEP> S12

<tb> <SEP> 52 <SEP> 221 <SEP> EN <SEP> GND <SEP> Terre

<tb> <SEP> 53 <SEP> 43 <SEP> E/S <SEP> C <SEP> BEOL <SEP> Validation <SEP> Contrle/Octet <SEP> pour <SEP> PCI

<tb>

<tb> <SEP> Plot <SEP> Broche <SEP> Type <SEP> Nom <SEP> Description

<tb> Puce <SEP> N <SEP> Module

<tb> <SEP> N

<tb> <SEP> 54 <SEP> 44 <SEP> EN <SEP> TCB <SEP> Horloge <SEP> Test <SEP> B

<tb> <SEP> 55 <SEP> 45 <SEP> EN <SEP> VCC <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 5 <SEP> V

<tb> <SEP> 56 <SEP> 46 <SEP> EN <SEP> TM <SEP> Mode <SEP> de <SEP> Test

<tb> <SEP> 57 <SEP> 47 <SEP> E/S <SEP> AD07~511 <SEP> Adresse <SEP> et <SEP> données <SEP> pour <SEP> bus <SEP> PCI/Test

<tb> <SEP> Série <SEP> entrée

<tb> <SEP> 58 <SEP> 48 <SEP> E/S <SEP> AD06 <SEP> S10 <SEP> Adresse <SEP> et <SEP> données <SEP> pour <SEP> bus <SEP> PCI/Test

<tb> <SEP> Série <SEP> Entrée

<tb> <SEP> 59 <SEP> 222 <SEP> EN <SEP> VDD <SEP> Alimentation <SEP> Courant <SEP> 3,3 <SEP> V

<tb> <SEP> 60 <SEP> 49 <SEP> E/S <SEP> AD05~MT5 <SEP> Adresse <SEP> et <SEP> données <SEP> pour <SEP> bus

<tb> <SEP> PCI/Données <SEP> Test <SEP> Mem

<tb> <SEP> 61 <SEP> 50 <SEP> E/s <SEP> AD04~MT4 <SEP> Adresse <SEP> et <SEP> données <SEP> pour <SEP> bus

<tb> <SEP> PCI/données <SEP> Test <SEP> Mem

<tb> <SEP> 62 <SEP> 226 <SEP> EN <SEP> VDD <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 3,3 <SEP> V

<tb> <SEP> 63 <SEP> 227 <SEP> EN <SEP> GND <SEP> Terre

<tb> <SEP> 64 <SEP> 51 <SEP> EN <SEP> VCC <SEP> Alimentation <SEP> en <SEP> Courant <SEP> 5 <SEP> v

<tb> <SEP> 65 <SEP> 52 <SEP> E/S <SEP> AD03~MT3 <SEP> Adresse <SEP> et <SEP> données <SEP> pour <SEP> bus

<tb> <SEP> PCI/Données <SEP> Test <SEP> Mem

<tb> <SEP> 66 <SEP> 53 <SEP> E/S <SEP> AD02 <SEP> MT2 <SEP> Adresse <SEP> et <SEP> données <SEP> pour <SEP> bus

<tb> <SEP> PCI/Données <SEP> Test <SEP> Mem

<tb> <SEP> 67 <SEP> 227 <SEP> EN <SEP> GND <SEP> Terre