CN106130552B - 一种流水线式模数转换器 - Google Patents

一种流水线式模数转换器 Download PDFInfo

- Publication number

- CN106130552B CN106130552B CN201610435061.XA CN201610435061A CN106130552B CN 106130552 B CN106130552 B CN 106130552B CN 201610435061 A CN201610435061 A CN 201610435061A CN 106130552 B CN106130552 B CN 106130552B

- Authority

- CN

- China

- Prior art keywords

- switch

- signal

- sub

- module

- switching

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/10—Calibration or testing

- H03M1/1009—Calibration

- H03M1/1014—Calibration at one point of the transfer characteristic, i.e. by adjusting a single reference value, e.g. bias or gain error

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/124—Sampling or signal conditioning arrangements specially adapted for A/D converters

- H03M1/1245—Details of sampling arrangements or methods

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/14—Conversion in steps with each step involving the same or a different conversion means and delivering more than one bit

- H03M1/16—Conversion in steps with each step involving the same or a different conversion means and delivering more than one bit with scale factor modification, i.e. by changing the amplification between the steps

- H03M1/164—Conversion in steps with each step involving the same or a different conversion means and delivering more than one bit with scale factor modification, i.e. by changing the amplification between the steps the steps being performed sequentially in series-connected stages

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Analogue/Digital Conversion (AREA)

- Amplifiers (AREA)

Abstract

本发明公开了一种流水线式模数转换器,解决了目前电容失配导致流水线式ADC非线性度增大的问题,所述流水线式模数转换器包括流水级电路(1~N),任一单级电路包括子模数转换器(10)、子数模转换器(20)和余量放大器模块(30);余量放大器模块(30)包括开关模块(31)、电容模块(32)、运算放大器(33)和电容选择控制子电路(34);电容选择控制子电路(34)用于控制开关模块(31)的开关状态,以从电容模块(32)的多个电容中随机选择电容分别对应与子数模转换器(20)的输出端和运算放大器(33)的输出端连接。实现了将电容失配引起的固定误差转换为随机误差,使得整个流水线式ADC的线性度免受电容失配的影响。

Description

技术领域

本发明涉及模数转换处理技术领域,尤其涉及一种流水线式模数转换器。

背景技术

随着互补金属氧化物半导体(CMOS,Complementary Metal OxideSemiconductor)集成电路工艺的发展,数字电路相对于模拟电路愈加体现出集成度高、抗干扰强、易于实现和成本低等诸多优势。因此,人们常用数字电路代替模拟电路完成信号处理。然而,现实世界中的信号大多是模拟的,如声音、图像、温度和压力等信号均为模拟信号。在进行数字信号处理之前需要将模拟信号转换为数字信号,实现这一功能的器件即为模数转换器(ADC,Analog to Digital Converter)。随着移动通信系统向第三代过渡,实现灵活且可配置的无线移动收发机技术的要求日益迫切。宽带高性能数据转换集成电路是新一代宽带移动通信基站的核心技术。其应用包括时分同步的码分多址技术(TD-SCDMA,TimeDivision-Synchronous Code Division Multiple Access)基站、长期演进技术(LTE,LongTerm Evolution)基站、家庭基站、短距离高速无线通信系统,如无载波通信技术(UWB,Ultra Wideband)、无线局域网络(W-LAN,Wireless Local Area Networks)等。新一代无线通信基站的应用要求模数转换器具有足够的信号带宽以覆盖其全部工作频带,同时需要其具有足够大的动态范围以防止邻道信号阻塞。

当模拟信号的带宽较宽时,要求ADC的采样速度很快,并且要求12比特左右的采样精度,流水线式模数转换器(Pipelined Analog-To-Digital Converter,以下简称:流水线式ADC)是最常采用的模数转换方案。具体的,流水线式ADC可以在功率、速度、集成电路芯片面积上取得不错的平衡点,故可以用来实现采样频率在百万赫兹等级的高精度ADC运算。

图1是传统流水线式ADC结构框图,模拟输入信号Vi经过采样保持电路100之后,再通过若干级电路模块200和后级模数转换电路模块300进行量化,最后将各级电路模块得到的量化值通过延时及错位相加模块400根据时间延时以及权重进行错位相加,输出最终数字信号Dout。

图2是传统流水线式ADC中单级电路模块的单端结构框图,它由两项非交叠时钟控制,结合图3,为现有技术中施加在ADC上的两项非交叠时钟信号的波形示意图,施加在ADC上的时钟信号有两个:采样时钟信号和建立时钟信号,在采样时钟信号为高电平(称为:时钟采样相,用“相位1”表示)时为ADC的采样时间,在建立时钟信号为高电平(称为:时钟建立相,用“相位2”表示)时为ADC的建立时间,相位1和相位2之间的空闲时间为非交叠时间。在相位1内,采样保持电路210对模拟输入信号Vi进行采样,子模数转换模块220对输入信号进行粗量化得到量化值D;在相位2内,子数模转换器230将上述粗量化值D转换成对应的模拟信号,然后将该模拟信号输送至减法器240中与模拟输入信号Vi相减得到量化余量,该量化余量再经过余量放大器250的放大得到信号Vo,最终输出给下一级电路模块。每一级电路模块都这样流水线工作,包括:采样,粗量化,余量放大,输出到下一级电路模块,最后一级电路模块的输出送到后级模数转换模块中300中,同时每一级电路模块的粗量化值和后级模数转换模块的量化值还要输出给延时及错位相加模块400。

但是由于实现流水线式ADC电路中的电容不可能制造的完美匹配(即相等),造成信号传输时出现误差,导致ADC的传输曲线不再是理想的直线,而是稍微弯曲的曲线,ADC的非线性便由此产生。在正交频分复用技术(OFDM,Orthogonal Frequency DivisionMultiplexing)系统中,ADC是必须的器件,将射频前端接收到的模拟信号转换为数字信号,然后传送给基带进行处理,ADC量化的整个频带被分成了多个子频带,每个子频带的带宽很小,所以热噪声对信噪比不会造成严重的下降,但是ADC的非线性失真会导致子频带上的信号出现谐波杂散,并且混入到其他子频带内,多个子频带上的谐波失真杂散相互混叠,导致每一子频带内的信噪比都下降。

为了克服电容失配的问题,传统的方法是增大电容的面积、版图匹配技术、修调等。因为版图的匹配度与电容的面积成反比,通过增大电容的面积来增加电容的匹配度,通过适当的器件摆放方式以及连线方式,可以做到很好的系统匹配和寄生匹配,此外还可以通过在制造完成后用激光进行再次修调,对失配进行修正。

但是随着无线通信系统对ADC的要求提高,传统的克服电容失配的方法受到了挑战,按照目前的半导体制造的一般水平,增大电容面积和版图技术所得到的电容匹配精度只能制造出有效位数在10比特左右、总谐波失真(THD,Total Harmonic Distortion)在-70dB、无杂散动态范围(SFDR,Spurious-free Dynamic Range)在75dB左右水平的ADC,与有些系统的高要求(有效位数10比特以上、THD在-90dB以下、SFDR在90dB以上)存在较大的差距,如若仅仅依赖后期的修调技术,其成本很高,操作性不强,可靠性差,不适应于批量生产,只适用于制造试验室样品。

另外,随着CMOS数字集成电路技术的高速发展,针对电容失配、运放有限增益的问题出现了数字校正技术,这些数字校正算法的主要手段是通过提取流水级的增益误差(包括电容失配导致的增益误差),在最终ADC的输出数字信号上进行补偿,根据这些算法是否会中断模数转换器正常工作的角度划分,校准可以分为前台校准和后台校准。前台校准是指在模数转换器需要校准时,强制停止对输入信号的转换;后台校准则不需要这样一个过程,它的校准过程不会影响到模数转换器的正常工作,所以后台校正技术得到了广泛的运用,其中最常用的是基于扰动注入提取误差的方法,其工作原理是在流水级余量放大时随机注入一个信号,再利用统计相关理论提取电容失配等误差,再进行校正。但是数字校正也有其缺点:首先是不易进行设计,除了数字电路复杂难设计之外,还需要这些校正算法与电路实际情况高度符合,否则没有校正效果,往往这些算法需要大量的采样周期进行校正,耗时长。

也就是说,现有技术中存在,电容失配导致流水线式ADC非线性度增大,而传统方法(如增大电容面积、版图匹配技术等)不能很好的解决电容失配,且通过数字校正技术解决电容失配时复杂度高、难以设计和难以进行错误排查的技术问题。

发明内容

本发明针对现有技术中存在的,电容失配导致流水线式ADC非线性度增大,而传统方法(如增大电容面积、版图匹配技术等)不能很好的解决电容失配,且通过数字校正技术解决电容失配时复杂度高、难以设计和难以进行错误排查的技术问题,提供了一种流水线式模数转换器,通过随机的选择流水级电路中的反馈电容,将电容失配引起的固定误差转换为随机误差,即将该固定误差转换为具有随机特性的噪声,使得整个流水线式ADC的线性度免受电容失配的影响,ADC的性能指标能够达到一些无线通信系统的高要求(如有效位数10比特以上、THD在-90dB以下、SFDR在90dB以上等),同时该技术实现起来方便,不必像算法校正一样需要大量的数字电路和校正收敛时间,只需要在传统电路上进行电路改进即可。

本发明提供了一种流水线式模数转换器,包括流水级电路,所述流水级电路中任一单级电路包括子模数转换器和子数模转换器,所述任一单级电路还包括余量放大器模块;

所述余量放大器模块包括:开关模块、电容模块、运算放大器和电容选择控制子电路;

所述开关模块的输入端用于接收模拟输入信号和所述子数模转换器的输出信号;所述开关模块的输出端通过所述电容模块与所述运算放大器的输入端连接、并直接与所述运算放大器的输出端连接;所述电容模块包括多个电容,所述多个电容的数量依据所述任一单级电路的流水级比特数而定;

所述电容选择控制子电路与所述开关模块连接,用于输出控制信号来控制所述开关模块的开关状态,以从所述电容模块的多个电容中随机选择电容分别对应与所述子数模转换器的输出端和所述运算放大器的输出端连接。

可选的,所述电容选择控制子电路包括:

伪随机序列发生器,用于基于第一时钟信号生成二进制格式伪随机数;

编码子模块,用于基于所述二进制格式伪随机数生成编码序列;

与门子模块,用于对第二时钟信号和所述编码序列进行求与计算,以生成第一控制序列信号;

非门子模块,用于对所述第一控制序列信号进行求非计算,以生成第二控制序列信号;

其中,所述第一时钟信号和所述第二时钟信号为非交叠时钟信号;所述控制信号包括所述第一控制序列信号和所述第二控制序列信号。

可选的,所述编码序列包括多个二进制位,所述与门子模块包括多个与门,所述非门子模块包括多个非门;

其中,所述编码序列的多个二进制位一一对应输送至所述多个与门,以与所述第二时钟信号进行求与计算,进而生成包括多个二进制位的第一控制序列信号;所述第一控制序列信号的多个二进制位一一对应输送至所述多个非门进行求非计算,以生成包括多个二进制位的第二控制序列信号。

可选的,所述开关模块包括第一开关组件、第二开关组件和第三开关组件,所述电容模块包括第一电容组件;

所述第一开关组件的输入端与所述子数模转换器的同相信号输出端相连,所述第一开关组件的输出端通过所述第一电容组件与所述运算放大器的同相信号输入端相连、还通过所述第二开关组件与所述运算放大器的反相信号输出端相连;所述第三开关组件的输入端用于接收同相模拟输入信号,所述第三开关组件的输出端通过所述第一电容组件与所述运算放大器的同相信号输入端相连、还通过所述第二开关组件与所述运算放大器的反相信号输出端相连;

所述电容选择控制子电路与所述第一开关组件和所述第二开关组件相连,用于输出所述第二控制序列信号控制所述第一开关组件的开关状态、以及输出所述第一控制序列信号控制所述第二开关组件的开关状态,以从所述第一电容组件中随机选择电容分别对应与所述子数模转换器的同相信号输出端和所述运算放大器的反相信号输出端连接。

可选的,所述第三开关组件通过所述第一时钟信号进行控制。

可选的,所述第一开关组件包括并联的多个第一开关件,所述第二开关组件包括并联的多个第二开关件,所述第三开关组件包括并联的多个第三开关件,所述第一电容组件包括并联的多个第一电容;

所述多个第一开关件一一对应与所述多个第二开关件连接,所述多个第一开关件一一对应与所述多个第一电容连接,所述多个第三开关件一一对应与所述多个第一电容连接;

其中,所述多个第一电容的个数基于所述任一单级电路的流水级比特数而定;所述第一控制序列信号用于控制调整所述多个第二开关件中各开关件的开关状态,所述第二控制序列信号用于控制调整所述多个第一开关件中各开关件的开关状态。

可选的,所述开关模块还包括第四开关组件、第五开关组件和第六开关组件;所述电容模块包括第二电容组件;

所述第四开关组件的输入端与所述子数模转换器的反相信号输出端相连,所述第四开关组件的输出端通过所述第二电容组件与所述运算放大器的反相信号输入端相连、还通过所述第五开关组件与所述运算放大器的同相信号输出端相连;所述第六开关组件的输入端用于接收反相模拟输入信号,所述第六开关组件的输出端通过所述第二电容组件与所述运算放大器的反相信号输入端相连、还通过所述第五开关组件与所述运算放大器的同相信号输出端相连;

所述电容选择控制子电路与所述第四开关组件和所述第五开关组件相连,用于输出所述第二控制序列信号控制所述第四开关组件的开关状态、以及输出所述第一控制序列信号控制所述第五开关组件的开关状态,以从所述第二电容组件中随机选择电容分别对应与所述子数模转换器的反相信号输出端和所述运算放大器的同相信号输出端连接。

可选的,所述第六开关组件通过所述第二时钟信号进行控制。

可选的,所述第四开关组件包括并联的多个第四开关件,所述第五开关组件包括并联的多个第五开关件,所述第六开关组件包括并联的多个第六开关件,所述第二电容组件包括并联的多个第二电容;

所述多个第四开关件一一对应与所述多个第五开关件连接,所述多个第四开关件一一对应与所述多个第二电容连接,所述多个第六开关件一一对应与所述多个第二电容连接;

其中,所述多个第二电容的个数基于所述任一单级电路的流水级比特数而定;所述第一控制序列信号用于控制调整所述多个第五开关件中各开关件的开关状态,所述第二控制序列信号用于控制调整所述多个第四开关件中各开关件的开关状态。

可选的,所述余量放大器模块还包括通过所述第二时钟信号进行控制的第七开关件和第八开关件;

所述子数模转换器的同相信号输出端通过所述第七开关件与所述第一开关组件连接,所述子数模转换器的反相信号输出端通过所述第八开关件与所述第四开关组件连接。

本发明中提供的一个或多个技术方案,至少具有如下技术效果或优点:

由于在本发明中,流水线式模数转换器中流水级电路中任一单级电路除了包括传统流水线式ADC电路中的子模数转换器和子数模转换器之外,还包括余量放大器模块,用于实现传统流水线式ADC电路中采样保持电路、减法器和余量放大器的功能;所述余量放大器模块包括:开关模块、电容模块、运算放大器和电容选择控制子电路;所述开关模块的输入端用于接收模拟输入信号和所述子数模转换器的输出信号;所述开关模块的输出端通过所述电容模块与所述运算放大器的输入端连接、并直接与所述运算放大器的输出端连接;所述电容模块包括多个电容,所述多个电容的数量依据所述任一单级电路的流水级比特数而定;所述电容选择控制子电路与所述开关模块连接,用于输出控制信号来控制所述开关模块的开关状态,以从所述电容模块的多个电容中随机选择电容分别对应与所述子数模转换器的输出端和所述运算放大器的输出端连接。也就是说,通过随机选择流水级电路中的反馈电容,将电容失配引起的固定误差转换为随机误差,即将该固定误差转换为具有随机特性的噪声,使得整个流水线式ADC的线性度免受电容失配的影响,ADC的性能指标能够达到一些无线通信系统的高要求(如有效位数10比特以上、THD在-90dB以下、SFDR在90dB以上等),同时本技术方案实现起来方便,不必像算法校正一样需要大量的数字电路和校正收敛时间,只需要在传统电路上增加少量模块即可。可见,本技术方案有效地解决了现有技术中电容失配导致流水线式ADC非线性度增大,而传统方法(如增大电容面积、版图匹配技术等)不能很好的解决电容失配,且通过数字校正技术解决电容失配时复杂度高、难以设计和难以进行错误排查的技术问题。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其它的附图。

图1为本发明背景技术提供的传统流水线式模数转换器结构示意图;

图2为本发明背景技术提供的传统流水线式模数转换器中单级电路模块结构示意图;

图3为本发明背景技术提供的施加在模数转换器上的时钟信号的波形示意图;

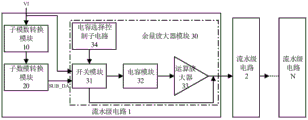

图4为本发明实施例提供的一种流水线式模数转换器结构示意图;

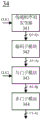

图5为本发明实施例提供的电容选择控制子电路的结构示意图;

图6为本发明实施例提供的余量放大器模块的结构示意图;

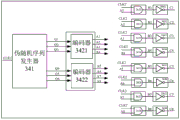

图7为本发明实施例提供的1.5比特流水级电路的电路原理图;

图8为本发明实施例提供的1.5比特流水级电路的电容选择控制子电路的电路原理图。

具体实施方式

本发明实施例通过提供一种流水线式模数转换器,解决了现有技术中存在的,电容失配导致流水线式ADC非线性度增大,而传统方法(如增大电容面积、版图匹配技术等)不能很好的解决电容失配,且通过数字校正技术解决电容失配时复杂度高、难以设计和难以进行错误排查的技术问题,通过随机的选择流水级电路中的反馈电容,将电容失配引起的固定误差转换为随机误差,即将该固定误差转换为具有随机特性的噪声,使得整个流水线式ADC的线性度免受电容失配的影响,ADC的性能指标能够达到一些无线通信系统的高要求(如有效位数10比特以上、THD在-90dB以下、SFDR在90dB以上等),同时该技术实现起来方便,不必像算法校正一样需要大量的数字电路和校正收敛时间,只需要在传统电路上进行电路改进即可。

本发明实施例的技术方案为解决上述技术问题,总体思路如下:

本发明实施例提供了一种流水线式模数转换器,包括流水级电路,所述流水级电路中任一单级电路包括子模数转换器和子数模转换器,所述任一单级电路还包括余量放大器模块;所述余量放大器模块包括:开关模块、电容模块、运算放大器和电容选择控制子电路;所述开关模块的输入端用于接收模拟输入信号和所述子数模转换器的输出信号;所述开关模块的输出端通过所述电容模块与所述运算放大器的输入端连接、并直接与所述运算放大器的输出端连接;所述电容模块包括多个电容,所述多个电容的数量依据所述任一单级电路的流水级比特数而定;所述电容选择控制子电路与所述开关模块连接,用于输出控制信号来控制所述开关模块的开关状态,以从所述电容模块的多个电容中随机选择电容分别对应与所述子数模转换器的输出端和所述运算放大器的输出端连接。

可见,在本发明实施例中,对传统的流水级电路进行改进,依据流水级电路中任一单级电路的流水级比特数确定电容模块中电容个数,并通过电容选择控制子电路控制开关模块的开关状态,以从所述电容模块的多个电容中随机选择电容分别对应与所述子数模转换器的输出端和所述运算放大器的输出端连接,随机选择流水级电路中的反馈电容,将电容失配引起的固定误差转换为随机误差,即将该固定误差转换为具有随机特性的噪声,使得整个流水线式ADC的线性度免受电容失配的影响,ADC的性能指标能够达到一些无线通信系统的高要求(如有效位数10比特以上、THD在-90dB以下、SFDR在90dB以上等),同时本技术方案实现起来方便,不必像算法校正一样需要大量的数字电路和校正收敛时间,只需要在传统电路上增加少量模块即可。可见,本技术方案有效地解决了现有技术中电容失配导致流水线式ADC非线性度增大,而传统方法(如增大电容面积、版图匹配技术等)不能很好的解决电容失配,且通过数字校正技术解决电容失配时复杂度高、难以设计和难以进行错误排查的技术问题。

为了更好的理解上述技术方案,下面将结合说明书附图以及具体的实施方式对上述技术方案进行详细的说明,应当理解本发明实施例以及实施例中的具体特征是对本申请技术方案的详细的说明,而不是对本申请技术方案的限定,在不冲突的情况下,本发明实施例以及实施例中的技术特征可以相互组合。

请参考图4,本发明实施例提供了一种流水线式模数转换器,包括流水级电路(1~N),流水级电路(1~N)中任一单级电路(图4中以流水级电路1为例)包括子模数转换器10和子数模转换器20,所述任一单级电路还包括余量放大器模块30;

余量放大器模块30包括:开关模块31、电容模块32、运算放大器33和电容选择控制子电路34;

开关模块31的输入端用于接收模拟输入信号VI和子数模转换器20的输出信号SUB_DA;开关模块31的输出端通过电容模块32与运算放大器33的输入端连接、并直接与运算放大器33的输出端连接;电容模块32包括多个电容,所述多个电容的数量依据所述任一单级电路的流水级比特数而定;

电容选择控制子电路34与开关模块31连接,用于输出控制信号来控制开关模块31的开关状态,以从电容模块32的多个电容中随机选择电容分别对应与子数模转换器20的输出端和运算放大器33的输出端连接。

其中,流水级电路(1~N-1)中每一级电路单元的输出作为下一级电路单元的输入。

在具体实施过程中,流水级电路(1~N)中任一单级电路均由两项非交叠时钟信号(即第一时钟信号CLK1和第二时钟信号CLK2)控制,具体的,第一时钟信号CLK1对应图3中的采样时钟信号,第二时钟信号CLK2对应图3中的建立时钟信号。请参考图5,电容选择控制子电路34包括:

伪随机序列发生器341,用于基于第一时钟信号CLK1生成二进制格式伪随机数(Q1~Qi);其中,i为该伪随机数的二进制位数,i大于等于6;

编码子模块342,用于基于所述二进制格式伪随机数(Q1~Qi)生成编码序列(A1~Aj);其中,j为该编码序列的二进制位数,j大于等于8;

与门子模块343,用于对第二时钟信号CLK2和所述编码序列进行求与计算,以生成第一控制序列信号(B1~Bj);

非门子模块344,用于对所述第一控制序列信号(B1~Bj)进行求非计算,以生成第二控制序列信号(C1~Cj);

其中,所述控制信号包括所述第一控制序列信号(B1~Bj)和所述第二控制序列信号(C1~Cj)。

具体的,所述编码序列包括多个二进制位,所述与门子模块343包括多个与门,所述非门子模块344包括多个非门;其中,所述编码序列的多个二进制位(A1~Aj)一一对应输送至所述多个与门,以与所述第二时钟信号CLK2进行求与计算,进而生成包括多个二进制位的第一控制序列信号(B1~Bj);所述第一控制序列信号的多个二进制位(B1~Bj)一一对应输送至所述多个非门进行求非计算,以生成包括多个二进制位的第二控制序列信号(C1~Cj)。

具体的,电容选择控制子电路34的与门子模块343和非门子模块344分别包含多个与门和多个非门;与门子模块343中部分与门的输出端与第二开关组件342连接,以对第二开关组件342进行控制;与门子模块343中另一部分与门的输出端与第五开关组件345连接,以对第五开关组件345进行控制;非门子模块344中部分非门的输出端与第一开关组件341连接,以对第一开关组件341进行控制;非门子模块344中另一部分非门的输出端与第四开关组件344连接,以对第四开关组件344进行控制。

在具体实施过程中,请参考图6,开关模块31包括第一开关组件311、第二开关组件312和第三开关组件313,电容模块32包括第一电容组件321;

第一开关组件311的输入端与子数模转换器20的同相信号输出端相连,用于接收子数模转换器20的正输出信号SUB_DAP;第一开关组件311的输出端通过第一电容组件321与运算放大器33的同相信号输入端相连、还通过第二开关组件312与运算放大器33的反相信号输出端相连;第三开关组件313的输入端用于接收同相模拟输入信号VIP,第三开关组件313的输出端通过第一电容组件321与运算放大器33的同相信号输入端相连、还通过第二开关组件312与运算放大器33的反相信号输出端相连;

电容选择控制子电路34与第一开关组件311和第二开关组件312相连,用于输出所述第二控制序列信号控制第一开关组件311的开关状态、以及输出所述第一控制序列信号控制第二开关组件312的开关状态,以从第一电容组件321中随机选择电容分别对应与子数模转换器20的同相信号输出端和运算放大器33的反相信号输出端连接;其中,第三开关组件313通过第一时钟信号CLK1进行控制。

在具体实施过程中,仍请参考图6,开关模块31还包括第四开关组件314、第五开关组件315和第六开关组件316;电容模块32包括第二电容组件322;

第四开关组件314的输入端与子数模转换器20的反相信号输出端相连,用于接收子数模转换器20的负输出信号SUB_DAN;第四开关组件314的输出端通过第二电容组件322与运算放大器33的反相信号输入端相连、还通过第五开关组件315与运算放大器33的同相信号输出端相连;第六开关组件316的输入端用于接收反相模拟输入信号VIN,第六开关组件316的输出端通过第二电容组件322与运算放大器33的反相信号输入端相连、还通过第五开关组件315与运算放大器33的同相信号输出端相连;

电容选择控制子电路34与第四开关组件314和第五开关组件315相连,用于输出所述第二控制序列信号控制第四开关组件314的开关状态、以及输出所述第一控制序列信号控制第五开关组件315的开关状态,以从第二电容组件322中随机选择电容分别对应与子数模转换器20的反相信号输出端和运算放大器33的同相信号输出端连接;其中,第六开关组件316通过第二时钟信号CLK2进行控制。

在具体实施过程中,第一开关组件311包括并联的多个第一开关件,第二开关组件312包括并联的多个第二开关件,第三开关组件313包括并联的多个第三开关件,第一电容组件321包括并联的多个第一电容;

所述多个第一开关件一一对应与所述多个第二开关件连接,所述多个第一开关件一一对应与所述多个第一电容连接,所述多个第三开关件一一对应与所述多个第一电容连接;

其中,所述多个第一电容的个数基于所述任一单级电路的流水级比特数而定;所述第一控制序列信号用于控制调整所述多个第二开关件中各开关件的开关状态,所述第二控制序列信号用于控制调整所述多个第一开关件中各开关件的开关状态。

在具体实施过程中,第四开关组件314包括并联的多个第四开关件,第五开关组件315包括并联的多个第五开关件,第六开关组件316包括并联的多个第六开关件,第二电容组件322包括并联的多个第二电容;

所述多个第四开关件一一对应与所述多个第五开关件连接,所述多个第四开关件一一对应与所述多个第二电容连接,所述多个第六开关件一一对应与所述多个第二电容连接;

其中,所述多个第二电容的个数基于所述任一单级电路的流水级比特数而定;所述第一控制序列信号用于控制调整所述多个第五开关件中各开关件的开关状态,所述第二控制序列信号用于控制调整所述多个第四开关件中各开关件的开关状态。

在具体实施过程中,仍请参考图6,余量放大器模块30还包括通过第二时钟信号CLK2进行控制的第七开关件317和第八开关件318;

子数模转换器20的同相信号输出端通过第七开关件317与第一开关组件311连接,子数模转换器20的反相信号输出端通过第八开关件318与第四开关组件314连接。

具体的,请参考图7,以余量放大器模块为1.5比特流水级电路为例,第一电容组件321拆分为四个并联的第一电容(C11~C14)。对应地,第一开关组件311包括四个并联的第一开关件(K11~K14),一一对应与四个并联的第一电容(C11~C14)连接;第二开关组件312包括四个并联的第二开关件(K21~K24)一一对应与四个并联的第一开关件(K11~K14)和四个并联的第一电容(C11~C14)连接;第三开关组件包括四个并联的第三开关件(K31~K34),一一对应与四个并联的第一开关件(K11~K14)、四个并联的第二开关件(K21~K24)和四个并联的第一电容(C11~C14)连接;四个第一开关件(K11~K14)的输入端通过第七开关件317与子数模转换器20的同相信号输出端相连,用于接收子数模转换器20的正输出信号SUB_DAP;四个第三开关件(K31~K34)的输入端接收同相模拟输入信号VIP;四个第一电容(C11~C14)的不与第一开关组件311相连的一端通过第九开关件319接收采样参考电压VB、还直接与运算放大器33的同相信号输入端相连。

同样的,第二电容组件322拆分为四个并联的第二电容(C21~C24)。对应地,第四开关组件314包括四个并联的第一开关件(K41~K44),一一对应与四个并联的第二电容(C21~C24)连接;第五开关组件315包括四个并联的第五开关件(K51~K54)一一对应与四个并联的第四开关件(K41~K44)和四个并联的第二电容(C21~C24)连接;第六开关组件包括四个并联的第六开关件(K61~K64),一一对应与四个并联的第四开关件(K41~K44)、四个并联的第五开关件(K51~K54)和四个并联的第二电容(C21~C24)连接;四个第四开关件(K41~K44)的输入端通过第八开关件318与子数模转换器20的反相信号输出端相连,用于接收子数模转换器20的负输出信号SUB_DAN;四个第六开关件(K61~K64)的输入端接收反相模拟输入信号VIN;四个第二电容(C21~C24)的不与第四开关组件314相连的一端通过第十开关件3110接收采样参考电压VB、还直接与运算放大器33的反相信号输入端相连。

接着,请参考图8,伪随机序列发生器341按照设计要求在第一时钟信号CLK1的上升沿到来时,生成一组二进制格式伪随机数(Q1~Q6);进一步,根据运算放大器33外围电路对称的特性,可将编码子模块342设置为包含两个编码器(3421、3422),分别接收二进制格式伪随机数(Q1~Q3)和二进制格式伪随机数(Q4~Q6);编码器3421基于二进制格式伪随机数(Q1~Q3)生成编码序列(A1~A4),编码器3422基于二进制格式伪随机数(Q4~Q6)生成编码序列(A5~A8);对应地,与门子模块343设置为包含8个与门(3431~3438),一一对应输入编码序列(A1~A8),并分别与第二时钟信号CLK2进行求与计算,以生成第一控制序列信号(B1~B8);进一步,非门子模块344设置为包含8个非门(3441~3448),一一对应输入编码序列(B1~B8),并分别进行求非计算,以生成第二控制序列信号(C1~C8)。其中,第一控制序列信号(B1~B4)用于一一对应控制四个第二开关件(K21~K24)的开关状态,第一控制序列信号(B5~B8)用于一一对应控制四个第五开关件(K51~K54)的开关状态,第二控制序列信号(C1~C4)用于一一对应控制四个第一开关件(K11~K14)的开关状态,第二控制序列信号(C5~C8)用于一一对应控制四个第四开关件(K41~K44)的开关状态。

下面结合图7和图8详细叙述本方案中1.5比特流水级电路的工作原理,并说明本技术如何解决电容失配引起的ADC非线性失真问题。本方案流水级电路工作在两个阶段,这两个阶段受非交叠时钟CLK1和CLK2控制,下面按照其工作阶段进行介绍。

当第一时钟信号CLK1为高电平时,受CLK1控制的第三开关件(K31~K34)、第六开关件(K61~K64)、第九开关件319和第十开关件3110导通,其余开关件截止,这时四个第一电容(C11~C14)以及四个第二电容(C21~C24)对同相、反相模拟输入信号(VIP、VIN)进行采样,同时,在CLK1的上升沿伪随机序列发生器341更新一次,两个编码器(3421、3422)分别对二进制格式伪随机数(Q1~Q3)和二进制格式伪随机数(Q4~Q6)进行编码,用于生成编码序列(A1~A8),其编码器的编码规则如下表所示,图中的两个编码器(3421、3422)的编码规则一样,下面仅以编码器3421为例:

对于任何的输入Q1、Q2、Q3信号,输出信号A1、A2、A3、A4中总是有两个信号为高“1”,另外两个信号为“0”。

当第二时钟信号CLK2为高电平时,受CLK2控制的第七开关件317和第八开关件318导通,同时信号A1、A2、A3、A4、A5、A6、A7、A8通过与门进行传输,这时有B1=A1、B2=A2、B3=A3、B4=A4、B5=A5、B6=A6、B7=A7、B8=A8,根据编码规则,B1~B4中有两个信号为高电平、另外两个信号为低电平,B5~B8中有两个信号为高电平、另外两个为低电平,受高电平控制的开关导通,受低电平控制的开关截止,此时,第一电容(C11~C14)中的两个电容与运算放大器33的反相信号输出端连接,另外两个电容与子数模转换器20的同相信号输出端连接,例如,当Q1、Q2、Q3分别取值为0、0、0时,A1、A2、A3、A4分别取值为1、1、0、0,可知:B1、B2、B3、B4分别取值为1、1、0、0,C1、C2、C3、C4s分别取值为0、0、1、1,此时第一开关件(K13、K14)导通,第一开关件(K11、K12)断开,第二开关件(K21、K22)导通,第二开关件(K23、K24)断开,也就是说,第一电容(C11、C12)与子数模转换器20的同相信号输出端连接,第一电容(C13、C14)与运算放大器33的同相信号输入端连接。同理,第二电容组件(C21~C24)中的两个电容与运算放大器33的反相信号输入端连接,而另外两个电容与子数模转换器20的反相信号输出端连接。如此便构成闭环的负反馈放大器,实现余量放大。

由于二进制格式伪随机数(Q1~Q6)是随机的,所以编码后的输出也是随机的,即第一电容(C11~C14)和第二电容(C21~C24)与运算放大器33输出端连接还是与子数模转换器20输出端连接也是随机的。

相应地,本方案中的流水级电路的传输函数如下式(I)所示:

其中,Vin为上述图7中同相模拟输入信号VIP与反相模拟输入信号VIN的差值,Vref上述图7中的子数模转换器20的同相输出信号SUB_DAP与反相输出信号SUB_DAN的差值,Vres为上述图7中的运算放大器33的同相输出信号VOP与反相输出信号VON的差值,Cs表示与子数模转换器20的同相信号输出端(或反相信号输出端)连接的总电容值,Cf表示与运算放大器33的反相信号输出端(或同相信号输出端)连接的总电容值。以Cs表示与子数模转换器20的同相信号输出端连接的总电容值、Cf表示与运算放大器33的反相信号输出端连接的总电容值为例,Cs=C1i+C1j、Cf=C1m+C1n;集合{i,j,m,n}={1,2,3,4},合并上式可以写为:

在理想情况下,电容Cs和电容Cf绝对相等,此时该传输函数为线性函数,但考虑在实际应用中电容Cs与电容Cf失配,Cs=Cf+ΔC,则上式(II)变为:

对于传统的1.5比特流水级而言,Cs和Cf是不变的,即电容失配引入的误差不变,这会造成流水线式ADC的传输曲线弯曲,但是,通过采取本申请技术方案,Cs和Cf的值是随机变化的,所以电容失配引起的误差量也是随机变化的,并且该误差的数学期望为0,传输曲线的统计期望曲线与理想传输曲线是一致的,故可以将电容失配引起的误差认为是噪声,这样整体流水线式ADC的线性度就不再受电容失配的影响了。需要指出的是:

1)在1.5比特流水级电路中,第一电容组件341和第二电容组件342分别由四个电容构成,对应的第一至第六开关组件(311~316)分别包含的开关件的个数与各电容组件包含的电容个数相等(即为4个),电容选择控制子电路34输出的第一控制序列信号和第二控制序列信号分别包含的用于进行开关控制的二进制信号位数与需要控制的开关件的个数相对应,例如:第一控制序列信号用于同时控制第二开关组件312和第五开关组件313,则第一控制序列信号所包含的用于进行开关控制的二进制信号位数为第二开关组件312和第五开关组件313的开关件个数的总和(即为8个),结合图5可确定j=8;

在1.5比特流水级电路中,以运算放大器33的负输入和正输出侧的单端电路为例,随机选取的Cs或Cf的情况种数为种,从而可以确定伪随机序列发生器341输出的用于控制该单端电路的二进制格式伪随机数的位数M,具体的,M应满足,即M≥3,结合图5可确定i=2M≥6;

2)本方案还适用于多比特流水级电路(如2.5比特流水级电路、3.5比特流水级电路、4.5比特流水级电路等),改进流水级电路结构与1.5比特流水级电路类似。具体的,在2.5比特流水级电路中,第一电容组件341和第二电容组件342分别由八个电容构成,对应的第一至第六开关组件(311~316)分别包含的开关件的个数与各电容组件包含的电容个数相等(即为8个),电容选择控制子电路34输出的第一控制序列信号和第二控制序列信号分别包含的用于进行开关控制的二进制信号位数与需要控制的开关件的个数相对应,例如:第一控制序列信号用于同时控制第二开关组件312和第五开关组件313,则第一控制序列信号所包含的用于进行开关控制的二进制信号位数为第二开关组件312和第五开关组件313的开关件个数的总和(即为16个),结合图5可确定j=16;

在2.5比特流水级电路中,以运算放大器33的负输入和正输出侧的单端电路为例,随机选取的Cs或Cf的情况种数为种,从而可以确定伪随机序列发生器341输出的用于控制该单端电路的二进制格式伪随机数的位数M,具体的,M应满足即M≥7,结合图5可确定i=2M≥14;

对于3.5比特流水级电路、4.5比特流水级电路等可以此类推,这里不再一一赘述。

综上所述,在本发明实施例中,对传统的流水级电路进行改进,依据所述余量放大器模块的比特数确定电容模块中电容个数,并通过电容选择控制子电路控制开关模块的开关状态,以从所述电容模块的多个电容中随机选择电容分别对应与所述子数模转换器的输出端和所述运算放大器的输出端连接,随机选择流水级电路中的反馈电容,将电容失配引起的固定误差转换为随机误差,即将该固定误差转换为具有随机特性的噪声,使得整个流水线式ADC的线性度免受电容失配的影响,ADC的性能指标能够达到一些无线通信系统的高要求(如有效位数10比特以上、THD在-90dB以下、SFDR在90dB以上等),同时本技术方案实现起来方便,不必像算法校正一样需要大量的数字电路和校正收敛时间,只需要在传统电路上增加少量模块即可。可见,本技术方案有效地解决了现有技术中电容失配导致流水线式ADC非线性度增大,而传统方法(如增大电容面积、版图匹配技术等)不能很好的解决电容失配,且通过数字校正技术解决电容失配时复杂度高、难以设计和难以进行错误排查的技术问题。

尽管已描述了本发明的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例做出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本发明范围的所有变更和修改。

显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

Claims (8)

1.一种流水线式模数转换器,包括流水级电路(1~N),所述流水级电路(1~N)中任一单级电路包括子模数转换器(10)和子数模转换器(20),其特征在于,所述任一单级电路还包括余量放大器模块(30);

所述余量放大器模块(30)包括:开关模块(31)、电容模块(32)、运算放大器(33)和电容选择控制子电路(34);

所述开关模块(31)的输入端用于接收模拟输入信号(VI)和所述子数模转换器(20)的输出信号(SUB_DA);所述开关模块(31)的输出端通过所述电容模块(32)与所述运算放大器(33)的输入端连接、并直接与所述运算放大器(33)的输出端连接;所述电容模块(32)包括多个电容,所述多个电容的数量依据所述任一单级电路的流水级比特数而定;

所述电容选择控制子电路(34)与所述开关模块(31)连接,用于输出控制信号来控制所述开关模块(31)的开关状态,以从所述电容模块(32)的多个电容中随机选择电容分别对应与所述子数模转换器(20)的输出端和所述运算放大器(33)的输出端连接;

其中所述电容选择控制子电路(34)包括:

伪随机序列发生器(341),用于基于第一时钟信号(CLK1)生成二进制格式伪随机数;

编码子模块(342),用于基于所述二进制格式伪随机数生成编码序列;

与门子模块(343),用于对第二时钟信号(CLK2)和所述编码序列进行求与计算,以生成第一控制序列信号;

非门子模块(344),用于对所述第一控制序列信号进行求非计算,以生成第二控制序列信号;

其中,所述第一时钟信号(CLK1)和所述第二时钟信号(CLK2)为非交叠时钟信号;所述控制信号包括所述第一控制序列信号和所述第二控制序列信号;

所述开关模块(31)包括第一开关组件(311)、第二开关组件(312)和第三开关组件(313),所述电容模块(32)包括第一电容组件(321);

所述第一开关组件(311)的输入端与所述子数模转换器(20)的同相信号输出端相连,所述第一开关组件(311)的输出端通过所述第一电容组件(321)与所述运算放大器(33)的同相信号输入端相连、还通过所述第二开关组件(312)与所述运算放大器(33)的反相信号输出端相连;所述第三开关组件(313)的输入端用于接收同相模拟输入信号(VIP),所述第三开关组件(313)的输出端通过所述第一电容组件(321)与所述运算放大器(33)的同相信号输入端相连、还通过所述第二开关组件(312)与所述运算放大器(33)的反相信号输出端相连;

所述电容选择控制子电路(34)与所述第一开关组件(311)和所述第二开关组件(312)相连,用于输出所述第二控制序列信号控制所述第一开关组件(311)的开关状态、以及输出所述第一控制序列信号控制所述第二开关组件(312)的开关状态,以从所述第一电容组件(321)中随机选择电容分别对应与所述子数模转换器(20)的同相信号输出端和所述运算放大器(33)的反相信号输出端连接;

其中,所述第一控制序列信号为8个(B1~B8),所述第二控制序列信号为8个(C1~C8);所述第一控制序列信号中的4个(B1~B4)控制所述第二开关组件(312)的开关状态;所述第二控制序列信号中的4个(C1~C4)控制所述第一开关组件(311)的开关状态。

2.如权利要求1所述的流水线式模数转换器,其特征在于,所述编码序列包括多个二进制位,所述与门子模块(343)包括多个与门,所述非门子模块(344)包括多个非门;

其中,所述编码序列的多个二进制位一一对应输送至所述多个与门,以与所述第二时钟信号(CLK2)进行求与计算,进而生成包括多个二进制位的第一控制序列信号;所述第一控制序列信号的多个二进制位一一对应输送至所述多个非门进行求非计算,以生成包括多个二进制位的第二控制序列信号。

3.如权利要求1所述的流水线式模数转换器,其特征在于,所述第三开关组件(313)通过所述第一时钟信号(CLK1)进行控制。

4.如权利要求1所述的流水线式模数转换器,其特征在于,所述第一开关组件(311)包括并联的多个第一开关件,所述第二开关组件(312)包括并联的多个第二开关件,所述第三开关组件(313)包括并联的多个第三开关件,所述第一电容组件(321)包括并联的多个第一电容;

所述多个第一开关件一一对应与所述多个第二开关件连接,所述多个第一开关件一一对应与所述多个第一电容连接,所述多个第三开关件一一对应与所述多个第一电容连接;

其中,所述多个第一电容的个数基于所述任一单级电路的流水级比特数而定;所述第一控制序列信号用于控制调整所述多个第二开关件中各开关件的开关状态,所述第二控制序列信号用于控制调整所述多个第一开关件中各开关件的开关状态。

5.如权利要求1所述的流水线式模数转换器,其特征在于,所述开关模块(31)包括第四开关组件(314)、第五开关组件(315)和第六开关组件(316);所述电容模块(32)包括第二电容组件(322);

所述第四开关组件(314)的输入端与所述子数模转换器(20)的反相信号输出端相连,所述第四开关组件(314)的输出端通过所述第二电容组件(322)与所述运算放大器(33)的反相信号输入端相连、还通过所述第五开关组件(315)与所述运算放大器(33)的同相信号输出端相连;所述第六开关组件(316)的输入端用于接收反相模拟输入信号(VIN),所述第六开关组件(316)的输出端通过所述第二电容组件(322)与所述运算放大器(33)的反相信号输入端相连、还通过所述第五开关组件(315)与所述运算放大器(33)的同相信号输出端相连;

所述电容选择控制子电路(34)与所述第四开关组件(314)和所述第五开关组件(315)相连,用于输出所述第二控制序列信号控制所述第四开关组件(314)的开关状态、以及输出所述第一控制序列信号控制所述第五开关组件(315)的开关状态,以从所述第二电容组件(322)中随机选择电容分别对应与所述子数模转换器(20)的反相信号输出端和所述运算放大器(33)的同相信号输出端连接。

6.如权利要求5所述的流水线式模数转换器,其特征在于,所述第六开关组件(316)通过所述第二时钟信号(CLK2)进行控制。

7.如权利要求5所述的流水线式模数转换器,其特征在于,所述第四开关组件(314)还包括并联的多个第四开关件,所述第五开关组件(315)包括并联的多个第五开关件,所述第六开关组件(316)包括并联的多个第六开关件,所述第二电容组件(322)包括并联的多个第二电容;

所述多个第四开关件一一对应与所述多个第五开关件连接,所述多个第四开关件一一对应与所述多个第二电容连接,所述多个第六开关件一一对应与所述多个第二电容连接;

其中,所述多个第二电容的个数基于所述任一单级电路的流水级比特数而定;所述第一控制序列信号用于控制调整所述多个第五开关件中各开关件的开关状态,所述第二控制序列信号用于控制调整所述多个第四开关件中各开关件的开关状态。

8.如权利要求5所述的流水线式模数转换器,其特征在于,所述余量放大器模块(30)还包括通过所述第二时钟信号(CLK2)进行控制的第七开关件(317)和第八开关件(318);

所述子数模转换器(20)的同相信号输出端通过所述第七开关件(317)与所述第一开关组件(311)连接,所述子数模转换器(20)的反相信号输出端通过所述第八开关件(318)与所述第四开关组件(314)连接。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201610435061.XA CN106130552B (zh) | 2016-06-16 | 2016-06-16 | 一种流水线式模数转换器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201610435061.XA CN106130552B (zh) | 2016-06-16 | 2016-06-16 | 一种流水线式模数转换器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN106130552A CN106130552A (zh) | 2016-11-16 |

| CN106130552B true CN106130552B (zh) | 2023-06-23 |

Family

ID=57469763

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201610435061.XA Active CN106130552B (zh) | 2016-06-16 | 2016-06-16 | 一种流水线式模数转换器 |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN106130552B (zh) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN114879808B (zh) * | 2022-04-08 | 2024-01-23 | 北京智芯微电子科技有限公司 | 温度检测芯片及其ptat电路、温度传感器 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5635937A (en) * | 1993-12-31 | 1997-06-03 | Korea Academy Of Industrial Technology | Pipelined multi-stage analog-to-digital converter |

| CN102751990A (zh) * | 2012-06-18 | 2012-10-24 | 东南大学 | 一种可提高动态性能的流水线式模数转换器 |

| CN103916125A (zh) * | 2013-01-06 | 2014-07-09 | 上海华虹宏力半导体制造有限公司 | 流水线模数转换器 |

| CN205754281U (zh) * | 2016-06-16 | 2016-11-30 | 武汉芯泰科技有限公司 | 一种流水线式模数转换器 |

-

2016

- 2016-06-16 CN CN201610435061.XA patent/CN106130552B/zh active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5635937A (en) * | 1993-12-31 | 1997-06-03 | Korea Academy Of Industrial Technology | Pipelined multi-stage analog-to-digital converter |

| CN102751990A (zh) * | 2012-06-18 | 2012-10-24 | 东南大学 | 一种可提高动态性能的流水线式模数转换器 |

| CN103916125A (zh) * | 2013-01-06 | 2014-07-09 | 上海华虹宏力半导体制造有限公司 | 流水线模数转换器 |

| CN205754281U (zh) * | 2016-06-16 | 2016-11-30 | 武汉芯泰科技有限公司 | 一种流水线式模数转换器 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN106130552A (zh) | 2016-11-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| Chuang et al. | A digitally self-calibrating 14-bit 10-MHz CMOS pipelined A/D converter | |

| Ingino et al. | A continuously calibrated 12-b, 10-MS/s, 3.3-VA/D converter | |

| Li et al. | A 1.8-V 22-mW 10-bit 30-MS/s pipelined CMOS ADC for low-power subsampling applications | |

| Tseng et al. | A 10-b 320-MS/s stage-gain-error self-calibration pipeline ADC | |

| CN102751990A (zh) | 一种可提高动态性能的流水线式模数转换器 | |

| CN106899301B (zh) | 用于在连续输入adc处的可调电阻的保护电路 | |

| Liu et al. | A continuous-time MASH 1-1-1 Delta–Sigma modulator with FIR DAC and encoder-embedded loop-unrolling quantizer in 40-nm CMOS | |

| Chen et al. | A 12-ENOB second-order noise-shaping SAR ADC with PVT-insensitive voltage–time–voltage converter | |

| US7973687B2 (en) | Differential switch, D/A converter, semiconductor integrated circuit and communication apparatus | |

| Miki et al. | An 11-b 300-MS/s double-sampling pipelined ADC with on-chip digital calibration for memory effects | |

| CN106130552B (zh) | 一种流水线式模数转换器 | |

| Murshed et al. | A 10-bit high speed pipelined ADC | |

| Choi et al. | A 1.2-V 12-b 120-MS/s SHA-free dual-channel Nyquist ADC based on midcode calibration | |

| Balasubramanian et al. | Architectural trends in current-steering digital-to-analog converters | |

| Ha et al. | A 0.5-V, 1.47-$\mu\hbox {W} $40-kS/s 13-bit SAR ADC With Capacitor Error Compensation | |

| Saalfeld et al. | A 2.3 mW quadrature bandpass continuous-time ΔΣ modulator with reconfigurable quantizer | |

| An et al. | A two-Channel 10b 160 MS/s 28 nm CMOS asynchronous pipelined-SAR ADC with low channel mismatch | |

| Shin et al. | A 10-bit 100-MS/s dual-channel pipelined ADC using dynamic memory effect cancellation technique | |

| WO2007008044A1 (en) | Series sampling capacitor and analog-to-digital converter using the same | |

| Larsson et al. | A 360 fJ/conversion-step, 14-bit, 100 MS/s, digitally background calibrated pipelined ADC in 130-nm CMOS | |

| CN205754281U (zh) | 一种流水线式模数转换器 | |

| Elkafrawy et al. | Design of a current steering DAC for a high speed current mode SAR ADC | |

| Nazari et al. | A 12-b, 650-MSps time-interleaved pipeline analog to digital converter with 1.5 GHz analog bandwidth for digital beam-forming systems | |

| CN104092465B (zh) | 一种基于时域比较器的宽输入摆幅Flash ADC电路 | |

| Gao et al. | A Calibration-Free Pipelined-SAR ADC With Cross-Stage Gain-Mismatch Error Shaping and Inherent Noise Shaping |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |