JP5331389B2 - 表示装置の作製方法 - Google Patents

表示装置の作製方法 Download PDFInfo

- Publication number

- JP5331389B2 JP5331389B2 JP2008151264A JP2008151264A JP5331389B2 JP 5331389 B2 JP5331389 B2 JP 5331389B2 JP 2008151264 A JP2008151264 A JP 2008151264A JP 2008151264 A JP2008151264 A JP 2008151264A JP 5331389 B2 JP5331389 B2 JP 5331389B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- semiconductor film

- thin film

- gas

- film transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 23

- 238000000034 method Methods 0.000 title claims description 54

- 239000004065 semiconductor Substances 0.000 claims abstract description 193

- 239000000758 substrate Substances 0.000 claims description 117

- 239000012535 impurity Substances 0.000 claims description 57

- 238000006243 chemical reaction Methods 0.000 claims description 49

- 238000012545 processing Methods 0.000 claims description 36

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 claims description 32

- 229910052990 silicon hydride Inorganic materials 0.000 claims description 27

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 16

- 239000001301 oxygen Substances 0.000 claims description 16

- 229910052760 oxygen Inorganic materials 0.000 claims description 15

- 238000005530 etching Methods 0.000 claims description 10

- 239000007795 chemical reaction product Substances 0.000 claims 2

- 230000002140 halogenating effect Effects 0.000 claims 1

- 238000005121 nitriding Methods 0.000 claims 1

- 239000010408 film Substances 0.000 abstract description 450

- 239000010409 thin film Substances 0.000 abstract description 171

- 239000003963 antioxidant agent Substances 0.000 abstract description 44

- 230000003078 antioxidant effect Effects 0.000 abstract description 44

- 230000003247 decreasing effect Effects 0.000 abstract description 3

- 230000000593 degrading effect Effects 0.000 abstract 1

- 239000013081 microcrystal Substances 0.000 abstract 1

- 239000007789 gas Substances 0.000 description 156

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 58

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 46

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 44

- 229910052710 silicon Inorganic materials 0.000 description 39

- 239000010703 silicon Substances 0.000 description 39

- 229910052734 helium Inorganic materials 0.000 description 35

- 239000001307 helium Substances 0.000 description 35

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 35

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 35

- 239000004973 liquid crystal related substance Substances 0.000 description 31

- 230000001681 protective effect Effects 0.000 description 31

- 230000015572 biosynthetic process Effects 0.000 description 29

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 28

- 239000010410 layer Substances 0.000 description 28

- 229910052757 nitrogen Inorganic materials 0.000 description 27

- 229910052581 Si3N4 Inorganic materials 0.000 description 26

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 26

- 229910052786 argon Inorganic materials 0.000 description 23

- 239000001257 hydrogen Substances 0.000 description 22

- 229910052739 hydrogen Inorganic materials 0.000 description 22

- 229960001730 nitrous oxide Drugs 0.000 description 22

- 239000013078 crystal Substances 0.000 description 19

- 235000013842 nitrous oxide Nutrition 0.000 description 19

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 16

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 16

- -1 silicon halide Chemical class 0.000 description 16

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 14

- 239000000565 sealant Substances 0.000 description 14

- 238000005401 electroluminescence Methods 0.000 description 13

- 239000011737 fluorine Substances 0.000 description 12

- 229910052731 fluorine Inorganic materials 0.000 description 12

- 229910052814 silicon oxide Inorganic materials 0.000 description 12

- 230000006870 function Effects 0.000 description 11

- 239000000463 material Substances 0.000 description 11

- 239000007788 liquid Substances 0.000 description 10

- 229910052782 aluminium Inorganic materials 0.000 description 9

- 125000006850 spacer group Chemical group 0.000 description 9

- 238000002834 transmittance Methods 0.000 description 9

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 8

- 239000012298 atmosphere Substances 0.000 description 8

- 239000002585 base Substances 0.000 description 8

- 239000000460 chlorine Substances 0.000 description 8

- 229910052736 halogen Inorganic materials 0.000 description 8

- 150000002367 halogens Chemical class 0.000 description 8

- 230000003647 oxidation Effects 0.000 description 8

- 238000007254 oxidation reaction Methods 0.000 description 8

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 7

- 239000004020 conductor Substances 0.000 description 7

- 150000002431 hydrogen Chemical class 0.000 description 7

- 229910052743 krypton Inorganic materials 0.000 description 7

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 238000004544 sputter deposition Methods 0.000 description 7

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 6

- 229910021529 ammonia Inorganic materials 0.000 description 6

- 125000004429 atom Chemical group 0.000 description 6

- 239000000919 ceramic Substances 0.000 description 6

- 229910001882 dioxygen Inorganic materials 0.000 description 6

- 238000005192 partition Methods 0.000 description 6

- 229920005989 resin Polymers 0.000 description 6

- 239000011347 resin Substances 0.000 description 6

- 239000002356 single layer Substances 0.000 description 6

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 5

- 238000000151 deposition Methods 0.000 description 5

- 230000008021 deposition Effects 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 238000007599 discharging Methods 0.000 description 5

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 5

- 229910000077 silane Inorganic materials 0.000 description 5

- 229910052719 titanium Inorganic materials 0.000 description 5

- 239000010936 titanium Substances 0.000 description 5

- ZCYVEMRRCGMTRW-UHFFFAOYSA-N 7553-56-2 Chemical compound [I] ZCYVEMRRCGMTRW-UHFFFAOYSA-N 0.000 description 4

- WKBOTKDWSSQWDR-UHFFFAOYSA-N Bromine atom Chemical compound [Br] WKBOTKDWSSQWDR-UHFFFAOYSA-N 0.000 description 4

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 4

- 239000000956 alloy Substances 0.000 description 4

- GDTBXPJZTBHREO-UHFFFAOYSA-N bromine Substances BrBr GDTBXPJZTBHREO-UHFFFAOYSA-N 0.000 description 4

- 229910052794 bromium Inorganic materials 0.000 description 4

- 229910052801 chlorine Inorganic materials 0.000 description 4

- 229910001873 dinitrogen Inorganic materials 0.000 description 4

- 239000000945 filler Substances 0.000 description 4

- 238000007667 floating Methods 0.000 description 4

- 239000011521 glass Substances 0.000 description 4

- 229910003437 indium oxide Inorganic materials 0.000 description 4

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 4

- 239000011630 iodine Substances 0.000 description 4

- 229910052740 iodine Inorganic materials 0.000 description 4

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 4

- 239000000203 mixture Substances 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 239000011733 molybdenum Substances 0.000 description 4

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 4

- 229920003023 plastic Polymers 0.000 description 4

- 239000004033 plastic Substances 0.000 description 4

- 238000009751 slip forming Methods 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 229910001930 tungsten oxide Inorganic materials 0.000 description 4

- 229910052724 xenon Inorganic materials 0.000 description 4

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 4

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 4

- 229910000838 Al alloy Inorganic materials 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 239000011651 chromium Substances 0.000 description 3

- 238000004140 cleaning Methods 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- 238000002425 crystallisation Methods 0.000 description 3

- 230000008025 crystallization Effects 0.000 description 3

- 230000006378 damage Effects 0.000 description 3

- 238000001678 elastic recoil detection analysis Methods 0.000 description 3

- 238000002347 injection Methods 0.000 description 3

- 239000007924 injection Substances 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 229910052754 neon Inorganic materials 0.000 description 3

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- 239000001272 nitrous oxide Substances 0.000 description 3

- 229920006267 polyester film Polymers 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 229920002620 polyvinyl fluoride Polymers 0.000 description 3

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 3

- 238000003860 storage Methods 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- 229910017073 AlLi Inorganic materials 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- 229910003902 SiCl 4 Inorganic materials 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- WGLPBDUCMAPZCE-UHFFFAOYSA-N Trioxochromium Chemical compound O=[Cr](=O)=O WGLPBDUCMAPZCE-UHFFFAOYSA-N 0.000 description 2

- 230000003064 anti-oxidating effect Effects 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- SLLGVCUQYRMELA-UHFFFAOYSA-N chlorosilicon Chemical compound Cl[Si] SLLGVCUQYRMELA-UHFFFAOYSA-N 0.000 description 2

- 229910000423 chromium oxide Inorganic materials 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 238000007865 diluting Methods 0.000 description 2

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 239000000284 extract Substances 0.000 description 2

- 239000011152 fibreglass Substances 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- AHLBNYSZXLDEJQ-FWEHEUNISA-N orlistat Chemical compound CCCCCCCCCCC[C@H](OC(=O)[C@H](CC(C)C)NC=O)C[C@@H]1OC(=O)[C@H]1CCCCCC AHLBNYSZXLDEJQ-FWEHEUNISA-N 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 2

- 229920000915 polyvinyl chloride Polymers 0.000 description 2

- 239000004800 polyvinyl chloride Substances 0.000 description 2

- 239000002994 raw material Substances 0.000 description 2

- 239000003566 sealing material Substances 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 238000001771 vacuum deposition Methods 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910019974 CrSi Inorganic materials 0.000 description 1

- 206010052128 Glare Diseases 0.000 description 1

- 229910016006 MoSi Inorganic materials 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 238000006124 Pilkington process Methods 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 239000003513 alkali Substances 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 239000005354 aluminosilicate glass Substances 0.000 description 1

- 239000010405 anode material Substances 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 239000011324 bead Substances 0.000 description 1

- 238000009835 boiling Methods 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 229910010293 ceramic material Inorganic materials 0.000 description 1

- 239000000356 contaminant Substances 0.000 description 1

- 239000002178 crystalline material Substances 0.000 description 1

- 238000010494 dissociation reaction Methods 0.000 description 1

- 230000005593 dissociations Effects 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000005538 encapsulation Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 239000003779 heat-resistant material Substances 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 239000005001 laminate film Substances 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- GVGCUCJTUSOZKP-UHFFFAOYSA-N nitrogen trifluoride Chemical compound FN(F)F GVGCUCJTUSOZKP-UHFFFAOYSA-N 0.000 description 1

- 239000012788 optical film Substances 0.000 description 1

- 238000007500 overflow downdraw method Methods 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 229910000034 oxygen hydride Inorganic materials 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 239000000049 pigment Substances 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920001296 polysiloxane Polymers 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 230000000644 propagated effect Effects 0.000 description 1

- 238000005086 pumping Methods 0.000 description 1

- 238000000746 purification Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 239000000376 reactant Substances 0.000 description 1

- 239000012495 reaction gas Substances 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 150000003377 silicon compounds Chemical class 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 238000006557 surface reaction Methods 0.000 description 1

- TXEYQDLBPFQVAA-UHFFFAOYSA-N tetrafluoromethane Chemical compound FC(F)(F)F TXEYQDLBPFQVAA-UHFFFAOYSA-N 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1288—Multistep manufacturing methods employing particular masking sequences or specially adapted masks, e.g. half-tone mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/314—Inorganic layers

- H01L21/3143—Inorganic layers composed of alternated layers or of mixtures of nitrides and oxides or of oxinitrides, e.g. formation of oxinitride by oxidation of nitride layers

- H01L21/3145—Inorganic layers composed of alternated layers or of mixtures of nitrides and oxides or of oxinitrides, e.g. formation of oxinitride by oxidation of nitride layers formed by deposition from a gas or vapour

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02126—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material containing Si, O, and at least one of H, N, C, F, or other non-metal elements, e.g. SiOC, SiOC:H or SiONC

- H01L21/0214—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material containing Si, O, and at least one of H, N, C, F, or other non-metal elements, e.g. SiOC, SiOC:H or SiONC the material being a silicon oxynitride, e.g. SiON or SiON:H

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/02274—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition in the presence of a plasma [PECVD]

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Electroluminescent Light Sources (AREA)

- Formation Of Insulating Films (AREA)

Description

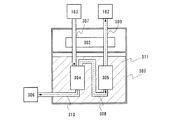

本発明の表示装置の作製方法について説明する。はじめに、表示装置の一形態とし液晶表示装置を用いて説明する。図1乃至図3に、駆動回路に用いられる薄膜トランジスタの断面図と、画素部に用いられる薄膜トランジスタの断面図を示す。なお、微結晶半導体膜を有する薄膜トランジスタはp型よりもn型の方が、移動度が高いので駆動回路に用いるのにより適しているが、本発明では、薄膜トランジスタはn型であってもp型であってもどちらでも良い。いずれの極性の薄膜トランジスタを用いる場合でも、同一の基板上に形成する薄膜トランジスタを全て同じ極性にそろえておくことが、工程数を抑えるためにも望ましい。

次に、本発明の表示装置の一形態である表示パネルの構成について、以下に示す。

本発明により得られる液晶表示装置や発光装置等の表示装置によって、様々なモジュール(アクティブマトリクス型液晶モジュール、アクティブマトリクス型ELモジュール)に用いることができる。即ち、それらを表示部に組み込んだ電子機器全てに本発明を実施できる。

Claims (2)

- 基板上にゲート電極を形成する第1の工程と、

前記ゲート電極上にゲート絶縁膜を形成する第2の工程と、

前記ゲート絶縁膜上に微結晶半導体膜を形成する第3の工程と、

前記微結晶半導体膜上に非晶質半導体膜を形成する第4の工程と、

前記非晶質半導体膜上に一導電型を付与する不純物を含む第1の半導体膜を形成する第5の工程と、

前記第1の半導体膜上に第1の導電膜を形成する第6の工程と、

前記第1の導電膜、前記第1の半導体膜、前記非晶質半導体膜、及び前記微結晶半導体膜を島状に加工する第7の工程と、

島状に加工された前記第1の導電膜をエッチングして一対の第2の導電膜を形成する第8の工程と、

島状に加工された前記第1の半導体膜をエッチングして一対の第2の半導体膜を形成する第9の工程と、を有し、

前記第2の工程と前記第3の工程とは同一の反応室内で行われ、

前記第3の工程において、前記反応室内に水素化珪素を導入し、前記反応室内の酸素と前記水素化珪素と反応させることにより生じた反応物を前記反応室外に排出した後に前記微結晶半導体膜を形成し、

前記第4の工程の後であって前記第5の工程の前に、前記非晶質半導体膜表面をハロゲン化することを特徴とする表示装置の作製方法。 - 基板上にゲート電極を形成する第1の工程と、

前記ゲート電極上にゲート絶縁膜を形成する第2の工程と、

前記ゲート絶縁膜上に微結晶半導体膜を形成する第3の工程と、

前記微結晶半導体膜上に非晶質半導体膜を形成する第4の工程と、

前記非晶質半導体膜上に一導電型を付与する不純物を含む第1の半導体膜を形成する第5の工程と、

前記第1の半導体膜上に第1の導電膜を形成する第6の工程と、

前記第1の導電膜、前記第1の半導体膜、前記非晶質半導体膜、及び前記微結晶半導体膜を島状に加工する第7の工程と、

島状に加工された前記第1の導電膜をエッチングして一対の第2の導電膜を形成する第8の工程と、

島状に加工された前記第1の半導体膜をエッチングして一対の第2の半導体膜を形成する第9の工程と、を有し、

前記第2の工程と前記第3の工程とは同一の反応室内で行われ、

前記第3の工程において、前記反応室内に水素化珪素を導入し、前記反応室内の酸素と前記水素化珪素と反応させることにより生じた反応物を前記反応室外に排出した後に前記微結晶半導体膜を形成し、

前記第4の工程の後であって前記第5の工程の前に、前記非晶質半導体膜表面を窒素化することを特徴とする表示装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008151264A JP5331389B2 (ja) | 2007-06-15 | 2008-06-10 | 表示装置の作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007159372 | 2007-06-15 | ||

| JP2007159372 | 2007-06-15 | ||

| JP2008151264A JP5331389B2 (ja) | 2007-06-15 | 2008-06-10 | 表示装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009021571A JP2009021571A (ja) | 2009-01-29 |

| JP2009021571A5 JP2009021571A5 (ja) | 2011-05-26 |

| JP5331389B2 true JP5331389B2 (ja) | 2013-10-30 |

Family

ID=40131459

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008151264A Expired - Fee Related JP5331389B2 (ja) | 2007-06-15 | 2008-06-10 | 表示装置の作製方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8300168B2 (ja) |

| JP (1) | JP5331389B2 (ja) |

Families Citing this family (214)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20070084897A1 (en) | 2003-05-20 | 2007-04-19 | Shelton Frederick E Iv | Articulating surgical stapling instrument incorporating a two-piece e-beam firing mechanism |

| US9060770B2 (en) | 2003-05-20 | 2015-06-23 | Ethicon Endo-Surgery, Inc. | Robotically-driven surgical instrument with E-beam driver |

| US11890012B2 (en) | 2004-07-28 | 2024-02-06 | Cilag Gmbh International | Staple cartridge comprising cartridge body and attached support |

| US7669746B2 (en) | 2005-08-31 | 2010-03-02 | Ethicon Endo-Surgery, Inc. | Staple cartridges for forming staples having differing formed staple heights |

| US11246590B2 (en) | 2005-08-31 | 2022-02-15 | Cilag Gmbh International | Staple cartridge including staple drivers having different unfired heights |

| US10159482B2 (en) | 2005-08-31 | 2018-12-25 | Ethicon Llc | Fastener cartridge assembly comprising a fixed anvil and different staple heights |

| US20070106317A1 (en) | 2005-11-09 | 2007-05-10 | Shelton Frederick E Iv | Hydraulically and electrically actuated articulation joints for surgical instruments |

| US8708213B2 (en) | 2006-01-31 | 2014-04-29 | Ethicon Endo-Surgery, Inc. | Surgical instrument having a feedback system |

| US20110295295A1 (en) | 2006-01-31 | 2011-12-01 | Ethicon Endo-Surgery, Inc. | Robotically-controlled surgical instrument having recording capabilities |

| US20120292367A1 (en) | 2006-01-31 | 2012-11-22 | Ethicon Endo-Surgery, Inc. | Robotically-controlled end effector |

| US11793518B2 (en) | 2006-01-31 | 2023-10-24 | Cilag Gmbh International | Powered surgical instruments with firing system lockout arrangements |

| US8186555B2 (en) | 2006-01-31 | 2012-05-29 | Ethicon Endo-Surgery, Inc. | Motor-driven surgical cutting and fastening instrument with mechanical closure system |

| US8820603B2 (en) | 2006-01-31 | 2014-09-02 | Ethicon Endo-Surgery, Inc. | Accessing data stored in a memory of a surgical instrument |

| US7845537B2 (en) | 2006-01-31 | 2010-12-07 | Ethicon Endo-Surgery, Inc. | Surgical instrument having recording capabilities |

| US10568652B2 (en) | 2006-09-29 | 2020-02-25 | Ethicon Llc | Surgical staples having attached drivers of different heights and stapling instruments for deploying the same |

| US11980366B2 (en) | 2006-10-03 | 2024-05-14 | Cilag Gmbh International | Surgical instrument |

| US8684253B2 (en) | 2007-01-10 | 2014-04-01 | Ethicon Endo-Surgery, Inc. | Surgical instrument with wireless communication between a control unit of a robotic system and remote sensor |

| US8540128B2 (en) | 2007-01-11 | 2013-09-24 | Ethicon Endo-Surgery, Inc. | Surgical stapling device with a curved end effector |

| US11564682B2 (en) | 2007-06-04 | 2023-01-31 | Cilag Gmbh International | Surgical stapler device |

| US8931682B2 (en) | 2007-06-04 | 2015-01-13 | Ethicon Endo-Surgery, Inc. | Robotically-controlled shaft based rotary drive systems for surgical instruments |

| US8921858B2 (en) * | 2007-06-29 | 2014-12-30 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device |

| US9176353B2 (en) * | 2007-06-29 | 2015-11-03 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

| US11849941B2 (en) | 2007-06-29 | 2023-12-26 | Cilag Gmbh International | Staple cartridge having staple cavities extending at a transverse angle relative to a longitudinal cartridge axis |

| US8334537B2 (en) * | 2007-07-06 | 2012-12-18 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device |

| TWI456663B (zh) | 2007-07-20 | 2014-10-11 | Semiconductor Energy Lab | 顯示裝置之製造方法 |

| US8330887B2 (en) * | 2007-07-27 | 2012-12-11 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and electronic device |

| JP5058909B2 (ja) | 2007-08-17 | 2012-10-24 | 株式会社半導体エネルギー研究所 | プラズマcvd装置及び薄膜トランジスタの作製方法 |

| US8030147B2 (en) * | 2007-09-14 | 2011-10-04 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing thin film transistor and display device including the thin film transistor |

| US20090090915A1 (en) | 2007-10-05 | 2009-04-09 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor, display device having thin film transistor, and method for manufacturing the same |

| JP5311955B2 (ja) * | 2007-11-01 | 2013-10-09 | 株式会社半導体エネルギー研究所 | 表示装置の作製方法 |

| US8187956B2 (en) * | 2007-12-03 | 2012-05-29 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing microcrystalline semiconductor film, thin film transistor having microcrystalline semiconductor film, and photoelectric conversion device having microcrystalline semiconductor film |

| US8591650B2 (en) * | 2007-12-03 | 2013-11-26 | Semiconductor Energy Laboratory Co., Ltd. | Method for forming crystalline semiconductor film, method for manufacturing thin film transistor, and method for manufacturing display device |

| KR101446249B1 (ko) | 2007-12-03 | 2014-10-01 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 제조방법 |

| RU2493788C2 (ru) | 2008-02-14 | 2013-09-27 | Этикон Эндо-Серджери, Инк. | Хирургический режущий и крепежный инструмент, имеющий радиочастотные электроды |

| US11986183B2 (en) | 2008-02-14 | 2024-05-21 | Cilag Gmbh International | Surgical cutting and fastening instrument comprising a plurality of sensors to measure an electrical parameter |

| US8636736B2 (en) | 2008-02-14 | 2014-01-28 | Ethicon Endo-Surgery, Inc. | Motorized surgical cutting and fastening instrument |

| US8247315B2 (en) * | 2008-03-17 | 2012-08-21 | Semiconductor Energy Laboratory Co., Ltd. | Plasma processing apparatus and method for manufacturing semiconductor device |

| CN102007585B (zh) * | 2008-04-18 | 2013-05-29 | 株式会社半导体能源研究所 | 薄膜晶体管及其制造方法 |

| KR101455317B1 (ko) | 2008-04-18 | 2014-10-27 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 박막 트랜지스터 및 그 제작 방법 |

| JP5436017B2 (ja) * | 2008-04-25 | 2014-03-05 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| WO2009157573A1 (en) | 2008-06-27 | 2009-12-30 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor, semiconductor device and electronic device |

| EP2291856A4 (en) * | 2008-06-27 | 2015-09-23 | Semiconductor Energy Lab | THIN FILM TRANSISTOR |

| JP5627071B2 (ja) | 2008-09-01 | 2014-11-19 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US11648005B2 (en) | 2008-09-23 | 2023-05-16 | Cilag Gmbh International | Robotically-controlled motorized surgical instrument with an end effector |

| US8210411B2 (en) | 2008-09-23 | 2012-07-03 | Ethicon Endo-Surgery, Inc. | Motor-driven surgical cutting instrument |

| US9005230B2 (en) | 2008-09-23 | 2015-04-14 | Ethicon Endo-Surgery, Inc. | Motorized surgical instrument |

| US9386983B2 (en) | 2008-09-23 | 2016-07-12 | Ethicon Endo-Surgery, Llc | Robotically-controlled motorized surgical instrument |

| US8608045B2 (en) | 2008-10-10 | 2013-12-17 | Ethicon Endo-Sugery, Inc. | Powered surgical cutting and stapling apparatus with manually retractable firing system |

| JP5498762B2 (ja) * | 2008-11-17 | 2014-05-21 | 株式会社半導体エネルギー研究所 | 薄膜トランジスタの作製方法 |

| TWI501319B (zh) | 2008-12-26 | 2015-09-21 | Semiconductor Energy Lab | 半導體裝置及其製造方法 |

| US8278657B2 (en) | 2009-02-13 | 2012-10-02 | Semiconductor Energy Laboratory Co., Ltd. | Transistor, semiconductor device including the transistor, and manufacturing method of the transistor and the semiconductor device |

| US8247812B2 (en) * | 2009-02-13 | 2012-08-21 | Semiconductor Energy Laboratory Co., Ltd. | Transistor, semiconductor device including the transistor, and manufacturing method of the transistor and the semiconductor device |

| TWI556309B (zh) | 2009-06-19 | 2016-11-01 | 半導體能源研究所股份有限公司 | 電漿處理裝置,形成膜的方法,和薄膜電晶體的製造方法 |

| US8258025B2 (en) * | 2009-08-07 | 2012-09-04 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing microcrystalline semiconductor film and thin film transistor |

| US9177761B2 (en) | 2009-08-25 | 2015-11-03 | Semiconductor Energy Laboratory Co., Ltd. | Plasma CVD apparatus, method for forming microcrystalline semiconductor film and method for manufacturing semiconductor device |

| JP5709579B2 (ja) * | 2010-03-02 | 2015-04-30 | 株式会社半導体エネルギー研究所 | 微結晶半導体膜の作製方法 |

| US8431496B2 (en) * | 2010-03-05 | 2013-04-30 | Semiconductor Energy Labortory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US11812965B2 (en) | 2010-09-30 | 2023-11-14 | Cilag Gmbh International | Layer of material for a surgical end effector |

| US10945731B2 (en) | 2010-09-30 | 2021-03-16 | Ethicon Llc | Tissue thickness compensator comprising controlled release and expansion |

| US9629814B2 (en) | 2010-09-30 | 2017-04-25 | Ethicon Endo-Surgery, Llc | Tissue thickness compensator configured to redistribute compressive forces |

| US9168038B2 (en) | 2010-09-30 | 2015-10-27 | Ethicon Endo-Surgery, Inc. | Staple cartridge comprising a tissue thickness compensator |

| US9282962B2 (en) | 2010-09-30 | 2016-03-15 | Ethicon Endo-Surgery, Llc | Adhesive film laminate |

| US11849952B2 (en) | 2010-09-30 | 2023-12-26 | Cilag Gmbh International | Staple cartridge comprising staples positioned within a compressible portion thereof |

| US9320523B2 (en) | 2012-03-28 | 2016-04-26 | Ethicon Endo-Surgery, Llc | Tissue thickness compensator comprising tissue ingrowth features |

| CA2834649C (en) | 2011-04-29 | 2021-02-16 | Ethicon Endo-Surgery, Inc. | Staple cartridge comprising staples positioned within a compressible portion thereof |

| JP5931573B2 (ja) * | 2011-05-13 | 2016-06-08 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US9072535B2 (en) | 2011-05-27 | 2015-07-07 | Ethicon Endo-Surgery, Inc. | Surgical stapling instruments with rotatable staple deployment arrangements |

| BR112014024098B1 (pt) | 2012-03-28 | 2021-05-25 | Ethicon Endo-Surgery, Inc. | cartucho de grampos |

| MX358135B (es) | 2012-03-28 | 2018-08-06 | Ethicon Endo Surgery Inc | Compensador de grosor de tejido que comprende una pluralidad de capas. |

| US9101358B2 (en) | 2012-06-15 | 2015-08-11 | Ethicon Endo-Surgery, Inc. | Articulatable surgical instrument comprising a firing drive |

| US9282974B2 (en) | 2012-06-28 | 2016-03-15 | Ethicon Endo-Surgery, Llc | Empty clip cartridge lockout |

| US9364230B2 (en) | 2012-06-28 | 2016-06-14 | Ethicon Endo-Surgery, Llc | Surgical stapling instruments with rotary joint assemblies |

| US9289256B2 (en) | 2012-06-28 | 2016-03-22 | Ethicon Endo-Surgery, Llc | Surgical end effectors having angled tissue-contacting surfaces |

| US20140001231A1 (en) | 2012-06-28 | 2014-01-02 | Ethicon Endo-Surgery, Inc. | Firing system lockout arrangements for surgical instruments |

| MX368026B (es) | 2013-03-01 | 2019-09-12 | Ethicon Endo Surgery Inc | Instrumento quirúrgico articulable con vías conductoras para la comunicación de la señal. |

| BR112015026109B1 (pt) | 2013-04-16 | 2022-02-22 | Ethicon Endo-Surgery, Inc | Instrumento cirúrgico |

| US9445813B2 (en) | 2013-08-23 | 2016-09-20 | Ethicon Endo-Surgery, Llc | Closure indicator systems for surgical instruments |

| US9826977B2 (en) | 2014-03-26 | 2017-11-28 | Ethicon Llc | Sterilization verification circuit |

| JP6532889B2 (ja) | 2014-04-16 | 2019-06-19 | エシコン エルエルシーEthicon LLC | 締結具カートリッジ組立体及びステープル保持具カバー配置構成 |

| JP6612256B2 (ja) | 2014-04-16 | 2019-11-27 | エシコン エルエルシー | 不均一な締結具を備える締結具カートリッジ |

| CN106456176B (zh) | 2014-04-16 | 2019-06-28 | 伊西康内外科有限责任公司 | 包括具有不同构型的延伸部的紧固件仓 |

| US20150297222A1 (en) | 2014-04-16 | 2015-10-22 | Ethicon Endo-Surgery, Inc. | Fastener cartridges including extensions having different configurations |

| KR102245497B1 (ko) * | 2014-08-08 | 2021-04-29 | 삼성디스플레이 주식회사 | 표시 기판 및 이의 제조 방법 |

| BR112017004361B1 (pt) | 2014-09-05 | 2023-04-11 | Ethicon Llc | Sistema eletrônico para um instrumento cirúrgico |

| US9737301B2 (en) | 2014-09-05 | 2017-08-22 | Ethicon Llc | Monitoring device degradation based on component evaluation |

| US9924944B2 (en) | 2014-10-16 | 2018-03-27 | Ethicon Llc | Staple cartridge comprising an adjunct material |

| US11141153B2 (en) | 2014-10-29 | 2021-10-12 | Cilag Gmbh International | Staple cartridges comprising driver arrangements |

| US10517594B2 (en) | 2014-10-29 | 2019-12-31 | Ethicon Llc | Cartridge assemblies for surgical staplers |

| US9987000B2 (en) | 2014-12-18 | 2018-06-05 | Ethicon Llc | Surgical instrument assembly comprising a flexible articulation system |

| US10085748B2 (en) | 2014-12-18 | 2018-10-02 | Ethicon Llc | Locking arrangements for detachable shaft assemblies with articulatable surgical end effectors |

| US9968355B2 (en) | 2014-12-18 | 2018-05-15 | Ethicon Llc | Surgical instruments with articulatable end effectors and improved firing beam support arrangements |

| MX2017008108A (es) * | 2014-12-18 | 2018-03-06 | Ethicon Llc | Instrumento quirurgico con un yunque que puede moverse de manera selectiva sobre un eje discreto no movil con relacion a un cartucho de grapas. |

| US11154301B2 (en) | 2015-02-27 | 2021-10-26 | Cilag Gmbh International | Modular stapling assembly |

| JP2020121162A (ja) | 2015-03-06 | 2020-08-13 | エシコン エルエルシーEthicon LLC | 測定の安定性要素、クリープ要素、及び粘弾性要素を決定するためのセンサデータの時間依存性評価 |

| US10441279B2 (en) | 2015-03-06 | 2019-10-15 | Ethicon Llc | Multiple level thresholds to modify operation of powered surgical instruments |

| US10433844B2 (en) | 2015-03-31 | 2019-10-08 | Ethicon Llc | Surgical instrument with selectively disengageable threaded drive systems |

| US10105139B2 (en) | 2015-09-23 | 2018-10-23 | Ethicon Llc | Surgical stapler having downstream current-based motor control |

| US11890015B2 (en) | 2015-09-30 | 2024-02-06 | Cilag Gmbh International | Compressible adjunct with crossing spacer fibers |

| US10736633B2 (en) | 2015-09-30 | 2020-08-11 | Ethicon Llc | Compressible adjunct with looping members |

| US10292704B2 (en) | 2015-12-30 | 2019-05-21 | Ethicon Llc | Mechanisms for compensating for battery pack failure in powered surgical instruments |

| CN108882932B (zh) | 2016-02-09 | 2021-07-23 | 伊西康有限责任公司 | 具有非对称关节运动构造的外科器械 |

| US11213293B2 (en) | 2016-02-09 | 2022-01-04 | Cilag Gmbh International | Articulatable surgical instruments with single articulation link arrangements |

| US10448948B2 (en) | 2016-02-12 | 2019-10-22 | Ethicon Llc | Mechanisms for compensating for drivetrain failure in powered surgical instruments |

| US10357247B2 (en) | 2016-04-15 | 2019-07-23 | Ethicon Llc | Surgical instrument with multiple program responses during a firing motion |

| US10426467B2 (en) | 2016-04-15 | 2019-10-01 | Ethicon Llc | Surgical instrument with detection sensors |

| US10828028B2 (en) | 2016-04-15 | 2020-11-10 | Ethicon Llc | Surgical instrument with multiple program responses during a firing motion |

| US20170296173A1 (en) | 2016-04-18 | 2017-10-19 | Ethicon Endo-Surgery, Llc | Method for operating a surgical instrument |

| US10433840B2 (en) | 2016-04-18 | 2019-10-08 | Ethicon Llc | Surgical instrument comprising a replaceable cartridge jaw |

| US20180168625A1 (en) | 2016-12-21 | 2018-06-21 | Ethicon Endo-Surgery, Llc | Surgical stapling instruments with smart staple cartridges |

| US10537325B2 (en) | 2016-12-21 | 2020-01-21 | Ethicon Llc | Staple forming pocket arrangement to accommodate different types of staples |

| US10835245B2 (en) | 2016-12-21 | 2020-11-17 | Ethicon Llc | Method for attaching a shaft assembly to a surgical instrument and, alternatively, to a surgical robot |

| US20180168615A1 (en) | 2016-12-21 | 2018-06-21 | Ethicon Endo-Surgery, Llc | Method of deforming staples from two different types of staple cartridges with the same surgical stapling instrument |

| US11191540B2 (en) | 2016-12-21 | 2021-12-07 | Cilag Gmbh International | Protective cover arrangements for a joint interface between a movable jaw and actuator shaft of a surgical instrument |

| JP7010956B2 (ja) | 2016-12-21 | 2022-01-26 | エシコン エルエルシー | 組織をステープル留めする方法 |

| US10307170B2 (en) | 2017-06-20 | 2019-06-04 | Ethicon Llc | Method for closed loop control of motor velocity of a surgical stapling and cutting instrument |

| US11653914B2 (en) | 2017-06-20 | 2023-05-23 | Cilag Gmbh International | Systems and methods for controlling motor velocity of a surgical stapling and cutting instrument according to articulation angle of end effector |

| US10779820B2 (en) | 2017-06-20 | 2020-09-22 | Ethicon Llc | Systems and methods for controlling motor speed according to user input for a surgical instrument |

| US10881399B2 (en) | 2017-06-20 | 2021-01-05 | Ethicon Llc | Techniques for adaptive control of motor velocity of a surgical stapling and cutting instrument |

| US11517325B2 (en) | 2017-06-20 | 2022-12-06 | Cilag Gmbh International | Closed loop feedback control of motor velocity of a surgical stapling and cutting instrument based on measured displacement distance traveled over a specified time interval |

| US10993716B2 (en) | 2017-06-27 | 2021-05-04 | Ethicon Llc | Surgical anvil arrangements |

| US11678880B2 (en) | 2017-06-28 | 2023-06-20 | Cilag Gmbh International | Surgical instrument comprising a shaft including a housing arrangement |

| EP4070740A1 (en) | 2017-06-28 | 2022-10-12 | Cilag GmbH International | Surgical instrument comprising selectively actuatable rotatable couplers |

| USD906355S1 (en) | 2017-06-28 | 2020-12-29 | Ethicon Llc | Display screen or portion thereof with a graphical user interface for a surgical instrument |

| US20190000459A1 (en) | 2017-06-28 | 2019-01-03 | Ethicon Llc | Surgical instruments with jaws constrained to pivot about an axis upon contact with a closure member that is parked in close proximity to the pivot axis |

| US10765427B2 (en) | 2017-06-28 | 2020-09-08 | Ethicon Llc | Method for articulating a surgical instrument |

| US11564686B2 (en) | 2017-06-28 | 2023-01-31 | Cilag Gmbh International | Surgical shaft assemblies with flexible interfaces |

| US10932772B2 (en) | 2017-06-29 | 2021-03-02 | Ethicon Llc | Methods for closed loop velocity control for robotic surgical instrument |

| US11944300B2 (en) | 2017-08-03 | 2024-04-02 | Cilag Gmbh International | Method for operating a surgical system bailout |

| US11974742B2 (en) | 2017-08-03 | 2024-05-07 | Cilag Gmbh International | Surgical system comprising an articulation bailout |

| US10842490B2 (en) | 2017-10-31 | 2020-11-24 | Ethicon Llc | Cartridge body design with force reduction based on firing completion |

| US10779826B2 (en) | 2017-12-15 | 2020-09-22 | Ethicon Llc | Methods of operating surgical end effectors |

| US20190192148A1 (en) | 2017-12-21 | 2019-06-27 | Ethicon Llc | Stapling instrument comprising a tissue drive |

| US11207065B2 (en) | 2018-08-20 | 2021-12-28 | Cilag Gmbh International | Method for fabricating surgical stapler anvils |

| CN109037037B (zh) * | 2018-09-27 | 2023-09-01 | 武汉华星光电技术有限公司 | 低温多晶硅层、薄膜晶体管及其制作方法 |

| US11696761B2 (en) | 2019-03-25 | 2023-07-11 | Cilag Gmbh International | Firing drive arrangements for surgical systems |

| US11648009B2 (en) | 2019-04-30 | 2023-05-16 | Cilag Gmbh International | Rotatable jaw tip for a surgical instrument |

| US11903581B2 (en) | 2019-04-30 | 2024-02-20 | Cilag Gmbh International | Methods for stapling tissue using a surgical instrument |

| US11638587B2 (en) | 2019-06-28 | 2023-05-02 | Cilag Gmbh International | RFID identification systems for surgical instruments |

| US11627959B2 (en) | 2019-06-28 | 2023-04-18 | Cilag Gmbh International | Surgical instruments including manual and powered system lockouts |

| US11771419B2 (en) | 2019-06-28 | 2023-10-03 | Cilag Gmbh International | Packaging for a replaceable component of a surgical stapling system |

| US11350938B2 (en) | 2019-06-28 | 2022-06-07 | Cilag Gmbh International | Surgical instrument comprising an aligned rfid sensor |

| US11523822B2 (en) | 2019-06-28 | 2022-12-13 | Cilag Gmbh International | Battery pack including a circuit interrupter |

| US11660163B2 (en) | 2019-06-28 | 2023-05-30 | Cilag Gmbh International | Surgical system with RFID tags for updating motor assembly parameters |

| US11684434B2 (en) | 2019-06-28 | 2023-06-27 | Cilag Gmbh International | Surgical RFID assemblies for instrument operational setting control |

| US11553971B2 (en) | 2019-06-28 | 2023-01-17 | Cilag Gmbh International | Surgical RFID assemblies for display and communication |

| US11559304B2 (en) | 2019-12-19 | 2023-01-24 | Cilag Gmbh International | Surgical instrument comprising a rapid closure mechanism |

| US11607219B2 (en) | 2019-12-19 | 2023-03-21 | Cilag Gmbh International | Staple cartridge comprising a detachable tissue cutting knife |

| US11529137B2 (en) | 2019-12-19 | 2022-12-20 | Cilag Gmbh International | Staple cartridge comprising driver retention members |

| US11504122B2 (en) | 2019-12-19 | 2022-11-22 | Cilag Gmbh International | Surgical instrument comprising a nested firing member |

| US11529139B2 (en) | 2019-12-19 | 2022-12-20 | Cilag Gmbh International | Motor driven surgical instrument |

| US11844520B2 (en) | 2019-12-19 | 2023-12-19 | Cilag Gmbh International | Staple cartridge comprising driver retention members |

| US11576672B2 (en) | 2019-12-19 | 2023-02-14 | Cilag Gmbh International | Surgical instrument comprising a closure system including a closure member and an opening member driven by a drive screw |

| US11701111B2 (en) | 2019-12-19 | 2023-07-18 | Cilag Gmbh International | Method for operating a surgical stapling instrument |

| US11911032B2 (en) | 2019-12-19 | 2024-02-27 | Cilag Gmbh International | Staple cartridge comprising a seating cam |

| USD975850S1 (en) | 2020-06-02 | 2023-01-17 | Cilag Gmbh International | Staple cartridge |

| USD976401S1 (en) | 2020-06-02 | 2023-01-24 | Cilag Gmbh International | Staple cartridge |

| USD974560S1 (en) | 2020-06-02 | 2023-01-03 | Cilag Gmbh International | Staple cartridge |

| USD975851S1 (en) | 2020-06-02 | 2023-01-17 | Cilag Gmbh International | Staple cartridge |

| US11871925B2 (en) | 2020-07-28 | 2024-01-16 | Cilag Gmbh International | Surgical instruments with dual spherical articulation joint arrangements |

| US11534259B2 (en) | 2020-10-29 | 2022-12-27 | Cilag Gmbh International | Surgical instrument comprising an articulation indicator |

| US11517390B2 (en) | 2020-10-29 | 2022-12-06 | Cilag Gmbh International | Surgical instrument comprising a limited travel switch |

| US11717289B2 (en) | 2020-10-29 | 2023-08-08 | Cilag Gmbh International | Surgical instrument comprising an indicator which indicates that an articulation drive is actuatable |

| US11931025B2 (en) | 2020-10-29 | 2024-03-19 | Cilag Gmbh International | Surgical instrument comprising a releasable closure drive lock |

| US11779330B2 (en) | 2020-10-29 | 2023-10-10 | Cilag Gmbh International | Surgical instrument comprising a jaw alignment system |

| US11844518B2 (en) | 2020-10-29 | 2023-12-19 | Cilag Gmbh International | Method for operating a surgical instrument |

| US11617577B2 (en) | 2020-10-29 | 2023-04-04 | Cilag Gmbh International | Surgical instrument comprising a sensor configured to sense whether an articulation drive of the surgical instrument is actuatable |

| USD1013170S1 (en) | 2020-10-29 | 2024-01-30 | Cilag Gmbh International | Surgical instrument assembly |

| USD980425S1 (en) | 2020-10-29 | 2023-03-07 | Cilag Gmbh International | Surgical instrument assembly |

| US11896217B2 (en) | 2020-10-29 | 2024-02-13 | Cilag Gmbh International | Surgical instrument comprising an articulation lock |

| US11678882B2 (en) | 2020-12-02 | 2023-06-20 | Cilag Gmbh International | Surgical instruments with interactive features to remedy incidental sled movements |

| US11737751B2 (en) | 2020-12-02 | 2023-08-29 | Cilag Gmbh International | Devices and methods of managing energy dissipated within sterile barriers of surgical instrument housings |

| US11890010B2 (en) | 2020-12-02 | 2024-02-06 | Cllag GmbH International | Dual-sided reinforced reload for surgical instruments |

| US11653915B2 (en) | 2020-12-02 | 2023-05-23 | Cilag Gmbh International | Surgical instruments with sled location detection and adjustment features |

| US11627960B2 (en) | 2020-12-02 | 2023-04-18 | Cilag Gmbh International | Powered surgical instruments with smart reload with separately attachable exteriorly mounted wiring connections |

| US11744581B2 (en) | 2020-12-02 | 2023-09-05 | Cilag Gmbh International | Powered surgical instruments with multi-phase tissue treatment |

| US11849943B2 (en) | 2020-12-02 | 2023-12-26 | Cilag Gmbh International | Surgical instrument with cartridge release mechanisms |

| US11653920B2 (en) | 2020-12-02 | 2023-05-23 | Cilag Gmbh International | Powered surgical instruments with communication interfaces through sterile barrier |

| US11944296B2 (en) | 2020-12-02 | 2024-04-02 | Cilag Gmbh International | Powered surgical instruments with external connectors |

| US11701113B2 (en) | 2021-02-26 | 2023-07-18 | Cilag Gmbh International | Stapling instrument comprising a separate power antenna and a data transfer antenna |

| US11950779B2 (en) | 2021-02-26 | 2024-04-09 | Cilag Gmbh International | Method of powering and communicating with a staple cartridge |

| US11950777B2 (en) | 2021-02-26 | 2024-04-09 | Cilag Gmbh International | Staple cartridge comprising an information access control system |

| US11980362B2 (en) | 2021-02-26 | 2024-05-14 | Cilag Gmbh International | Surgical instrument system comprising a power transfer coil |

| US11730473B2 (en) | 2021-02-26 | 2023-08-22 | Cilag Gmbh International | Monitoring of manufacturing life-cycle |

| US11749877B2 (en) | 2021-02-26 | 2023-09-05 | Cilag Gmbh International | Stapling instrument comprising a signal antenna |

| US11751869B2 (en) | 2021-02-26 | 2023-09-12 | Cilag Gmbh International | Monitoring of multiple sensors over time to detect moving characteristics of tissue |

| US11812964B2 (en) | 2021-02-26 | 2023-11-14 | Cilag Gmbh International | Staple cartridge comprising a power management circuit |

| US11696757B2 (en) | 2021-02-26 | 2023-07-11 | Cilag Gmbh International | Monitoring of internal systems to detect and track cartridge motion status |

| US11723657B2 (en) | 2021-02-26 | 2023-08-15 | Cilag Gmbh International | Adjustable communication based on available bandwidth and power capacity |

| US11793514B2 (en) | 2021-02-26 | 2023-10-24 | Cilag Gmbh International | Staple cartridge comprising sensor array which may be embedded in cartridge body |

| US11744583B2 (en) | 2021-02-26 | 2023-09-05 | Cilag Gmbh International | Distal communication array to tune frequency of RF systems |

| US11925349B2 (en) | 2021-02-26 | 2024-03-12 | Cilag Gmbh International | Adjustment to transfer parameters to improve available power |

| US11717291B2 (en) | 2021-03-22 | 2023-08-08 | Cilag Gmbh International | Staple cartridge comprising staples configured to apply different tissue compression |

| US11723658B2 (en) | 2021-03-22 | 2023-08-15 | Cilag Gmbh International | Staple cartridge comprising a firing lockout |

| US11759202B2 (en) | 2021-03-22 | 2023-09-19 | Cilag Gmbh International | Staple cartridge comprising an implantable layer |

| US11826042B2 (en) | 2021-03-22 | 2023-11-28 | Cilag Gmbh International | Surgical instrument comprising a firing drive including a selectable leverage mechanism |

| US11737749B2 (en) | 2021-03-22 | 2023-08-29 | Cilag Gmbh International | Surgical stapling instrument comprising a retraction system |

| US11806011B2 (en) | 2021-03-22 | 2023-11-07 | Cilag Gmbh International | Stapling instrument comprising tissue compression systems |

| US11826012B2 (en) | 2021-03-22 | 2023-11-28 | Cilag Gmbh International | Stapling instrument comprising a pulsed motor-driven firing rack |

| US11849944B2 (en) | 2021-03-24 | 2023-12-26 | Cilag Gmbh International | Drivers for fastener cartridge assemblies having rotary drive screws |

| US11786243B2 (en) | 2021-03-24 | 2023-10-17 | Cilag Gmbh International | Firing members having flexible portions for adapting to a load during a surgical firing stroke |

| US11944336B2 (en) | 2021-03-24 | 2024-04-02 | Cilag Gmbh International | Joint arrangements for multi-planar alignment and support of operational drive shafts in articulatable surgical instruments |

| US11896219B2 (en) | 2021-03-24 | 2024-02-13 | Cilag Gmbh International | Mating features between drivers and underside of a cartridge deck |

| US11903582B2 (en) | 2021-03-24 | 2024-02-20 | Cilag Gmbh International | Leveraging surfaces for cartridge installation |

| US11786239B2 (en) | 2021-03-24 | 2023-10-17 | Cilag Gmbh International | Surgical instrument articulation joint arrangements comprising multiple moving linkage features |

| US11832816B2 (en) | 2021-03-24 | 2023-12-05 | Cilag Gmbh International | Surgical stapling assembly comprising nonplanar staples and planar staples |

| US11744603B2 (en) | 2021-03-24 | 2023-09-05 | Cilag Gmbh International | Multi-axis pivot joints for surgical instruments and methods for manufacturing same |

| US11849945B2 (en) | 2021-03-24 | 2023-12-26 | Cilag Gmbh International | Rotary-driven surgical stapling assembly comprising eccentrically driven firing member |

| US11793516B2 (en) | 2021-03-24 | 2023-10-24 | Cilag Gmbh International | Surgical staple cartridge comprising longitudinal support beam |

| US11857183B2 (en) | 2021-03-24 | 2024-01-02 | Cilag Gmbh International | Stapling assembly components having metal substrates and plastic bodies |

| US11896218B2 (en) | 2021-03-24 | 2024-02-13 | Cilag Gmbh International | Method of using a powered stapling device |

| US20220378425A1 (en) | 2021-05-28 | 2022-12-01 | Cilag Gmbh International | Stapling instrument comprising a control system that controls a firing stroke length |

| US11980363B2 (en) | 2021-10-18 | 2024-05-14 | Cilag Gmbh International | Row-to-row staple array variations |

| US11937816B2 (en) | 2021-10-28 | 2024-03-26 | Cilag Gmbh International | Electrical lead arrangements for surgical instruments |

| CN114361338A (zh) * | 2022-01-07 | 2022-04-15 | 天津大学 | 一种增强n型半导体稳定性的方法 |

Family Cites Families (30)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS56122123A (en) | 1980-03-03 | 1981-09-25 | Shunpei Yamazaki | Semiamorphous semiconductor |

| JPS6262073A (ja) | 1985-09-11 | 1987-03-18 | Ishikawajima Harima Heavy Ind Co Ltd | ポペツト弁の温度制御装置 |

| JPH0253941A (ja) | 1988-08-17 | 1990-02-22 | Tsudakoma Corp | 織機の運転装置 |

| JPH03278466A (ja) * | 1990-03-27 | 1991-12-10 | Toshiba Corp | 薄膜トランジスタおよびその製造方法 |

| KR950013784B1 (ko) | 1990-11-20 | 1995-11-16 | 가부시키가이샤 한도오따이 에네루기 겐큐쇼 | 반도체 전계효과 트랜지스터 및 그 제조방법과 박막트랜지스터 |

| US5514879A (en) | 1990-11-20 | 1996-05-07 | Semiconductor Energy Laboratory Co., Ltd. | Gate insulated field effect transistors and method of manufacturing the same |

| JP2791422B2 (ja) | 1990-12-25 | 1998-08-27 | 株式会社 半導体エネルギー研究所 | 電気光学装置およびその作製方法 |

| US5849601A (en) | 1990-12-25 | 1998-12-15 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and method for manufacturing the same |

| US7115902B1 (en) | 1990-11-20 | 2006-10-03 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and method for manufacturing the same |

| US7576360B2 (en) | 1990-12-25 | 2009-08-18 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device which comprises thin film transistors and method for manufacturing the same |

| US7098479B1 (en) | 1990-12-25 | 2006-08-29 | Semiconductor Energy Laboratory Co., Ltd. | Electro-optical device and method for manufacturing the same |

| US6835523B1 (en) | 1993-05-09 | 2004-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Apparatus for fabricating coating and method of fabricating the coating |

| US6171674B1 (en) | 1993-07-20 | 2001-01-09 | Semiconductor Energy Laboratory Co., Ltd. | Hard carbon coating for magnetic recording medium |

| JPH0963955A (ja) * | 1995-08-23 | 1997-03-07 | Toyota Central Res & Dev Lab Inc | 成膜装置、成膜方法および単結晶膜の製造方法 |

| KR100257158B1 (ko) * | 1997-06-30 | 2000-05-15 | 김영환 | 박막 트랜지스터 및 그의 제조 방법 |

| JP2000277439A (ja) | 1999-03-25 | 2000-10-06 | Kanegafuchi Chem Ind Co Ltd | 結晶質シリコン系薄膜のプラズマcvd方法およびシリコン系薄膜光電変換装置の製造方法 |

| JP4700160B2 (ja) * | 2000-03-13 | 2011-06-15 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| SG142160A1 (en) * | 2001-03-19 | 2008-05-28 | Semiconductor Energy Lab | Method of manufacturing a semiconductor device |

| JP4782316B2 (ja) * | 2001-06-29 | 2011-09-28 | 東京エレクトロン株式会社 | 処理方法及びプラズマ装置 |

| JP2004014958A (ja) | 2002-06-11 | 2004-01-15 | Fuji Electric Holdings Co Ltd | 薄膜多結晶太陽電池とその製造方法 |

| JP4748954B2 (ja) | 2003-07-14 | 2011-08-17 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| US8319219B2 (en) * | 2003-07-14 | 2012-11-27 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device |

| DE10334265A1 (de) * | 2003-07-25 | 2005-02-24 | Basf Ag | Thermoplastisches Polyurethan enthaltend Silangruppen |

| JP2005050905A (ja) | 2003-07-30 | 2005-02-24 | Sharp Corp | シリコン薄膜太陽電池の製造方法 |

| JP2005167051A (ja) * | 2003-12-04 | 2005-06-23 | Sony Corp | 薄膜トランジスタおよび薄膜トランジスタの製造方法 |

| TWI234288B (en) * | 2004-07-27 | 2005-06-11 | Au Optronics Corp | Method for fabricating a thin film transistor and related circuits |

| JP2006148082A (ja) * | 2004-10-19 | 2006-06-08 | Semiconductor Energy Lab Co Ltd | 配線基板及び半導体装置の作製方法 |

| JP5013393B2 (ja) | 2005-03-30 | 2012-08-29 | 東京エレクトロン株式会社 | プラズマ処理装置と方法 |

| JP4597792B2 (ja) | 2005-06-27 | 2010-12-15 | 東京エレクトロン株式会社 | 処理ガス供給構造およびプラズマ処理装置 |

| JP4777717B2 (ja) | 2005-08-10 | 2011-09-21 | 東京エレクトロン株式会社 | 成膜方法、プラズマ処理装置および記録媒体 |

-

2008

- 2008-06-10 JP JP2008151264A patent/JP5331389B2/ja not_active Expired - Fee Related

- 2008-06-13 US US12/213,105 patent/US8300168B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US8300168B2 (en) | 2012-10-30 |

| JP2009021571A (ja) | 2009-01-29 |

| US20080308807A1 (en) | 2008-12-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5331389B2 (ja) | 表示装置の作製方法 | |

| JP7290769B2 (ja) | 半導体装置 | |

| JP5364293B2 (ja) | 表示装置の作製方法およびプラズマcvd装置 | |

| JP5435907B2 (ja) | 表示装置の作製方法 | |

| JP5542269B2 (ja) | 発光装置 | |

| US8633485B2 (en) | Display device and manufacturing method thereof | |

| US7998800B2 (en) | Method for manufacturing semiconductor device | |

| JP5311955B2 (ja) | 表示装置の作製方法 | |

| US8951849B2 (en) | Method for manufacturing semiconductor device including layer containing yttria-stabilized zirconia | |

| JP2009071284A (ja) | 表示装置 | |

| JP5288597B2 (ja) | 半導体装置の作製方法 | |

| JP2009130229A (ja) | 半導体装置の作製方法 | |

| JP5324837B2 (ja) | 表示装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110412 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110412 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130416 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130418 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130424 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130723 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130729 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5331389 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |