JP3634465B2 - Connectionless communication system, its test method, and in-station control system - Google Patents

Connectionless communication system, its test method, and in-station control system Download PDFInfo

- Publication number

- JP3634465B2 JP3634465B2 JP26134695A JP26134695A JP3634465B2 JP 3634465 B2 JP3634465 B2 JP 3634465B2 JP 26134695 A JP26134695 A JP 26134695A JP 26134695 A JP26134695 A JP 26134695A JP 3634465 B2 JP3634465 B2 JP 3634465B2

- Authority

- JP

- Japan

- Prior art keywords

- path

- route

- cell

- station

- exchange

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Monitoring And Testing Of Exchanges (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

- Telephonic Communication Services (AREA)

Description

【0001】

【発明の属する技術分野】

本発明は、高速データ伝送を行うコネクションレス通信システムとその試験方法に関し、また、高速データ伝送のための交換局の局内制御方式に関する。

【0002】

【従来の技術】

近年、ワークステーションやパーソナルコンピュータ等の情報処理装置の高性能化に伴い、多数の情報処理装置を高速LAN (ローカル・エリア・ネットワーク)で接続した分散処理が広く行われている。そして、これらLAN 間を接続するネットワークに対しても高速化が要求されている。

上述のような高速データ通信を実現するサービスの一つとしてSMDSが知られている。SMDS(Switched Multi−megabit Data Service )は、1.5Mbps 及び45Mbpsの転送速度を基本としたコネクションレス型のデータ交換サービスである。

ところで、広帯域ISDNを実現する方法としては、ATM 方式が知られているが、ATM ネットワークの中でSMDSを提供することができる。この場合、所定のATM 交換機に対してSMDS処理用サーバ(SMDSメッセージハンドラ)を設ける。そして、SMDS加入者とそのSMDS加入者を収容するSMDS処理用サーバとの間を、PVC (Permanent Virtual Circuit またはPermanent Virtual Channel )で接続し、SMDS加入者から出力されるコネクションレスデータをSMDS処理用サーバへ転送して、そのサーバにおいてルーティング処理等を実行させる。

ここで、上記コネクションレスデータは、一般に、可変長のパケット(データフレーム)であるが、上記PVC はATM ネットワーク上に設定されるパスであるので、コネクションレスデータは、ATM 交換機に入力される前にATM セル形式に変換(分解)して転送される。このセルは、48バイトのペイロード部と、5バイトのヘッダ部とからなる53バイト構成を基本としている。

そして、このATM セル形式のデータは、図897に示すように、SMDS処理用サーバでいったんL3−PDU(レイヤ3プロトコル・データ・ユニット)あるいはさらに上位レイヤのデータ形式に組立られ、L3−PDUに格納されている着信先アドレスDA、送信元アドレスSA等に基づいてルーティング情報などの解析が行われる。その後、再びセルに分解されて、上記解析した情報に基づいてルーティングされる。

上述したように、従来のSMDSにおいては、SMDS処理用サーバでルーティング処理等を行うときに、入力セルを上位レイヤのデータ形式(たとえば、L3−PDU)に組み立てて、マイコン・プログラム等のソフトウェアによってその処理を行っていたため、高速化には限界があった。また、着信先アドレスDAとしてグループアドレスが指定されていた場合のデータコピー処理、トラフィックの平滑化処理、EOM セル(End of Message:L3−PDUを複数のセルに分解した場合、そのL3−PDUの最後の部分のデータを格納するセル)の不着信時の処理等も、全てマイコン等によりソフト的に処理されていた。

このように、従来のSMDSでは、SMDS処理用サーバでの処理に様々なソフトウェア処理が含まれていたため、その高速化には限界があった。したがって、SMDSを用いてコネクションレス通信のデータ伝送を行う場合、伝送路・交換機の速度を高速化しても、SMDS処理用サーバでの処理がボトルネックとなって、実際の高速化が妨げられていた。さらに、SMDS処理用サーバにおいて上記組立処理を行う場合、各L3−PDUを構成するセルをいったんすべて格納する必要があるので、そのためのバッファ容量が大きくなってしまうという問題もあった。

次に、SMDSにおいては、サービス提供時に、以下に示すようなプロトコル・パフォーマンス・モニタリングを行う。すなわち、データに含まれる様々なパラメータについて、そのフォーマットチェック等を行う。そして、このチェックにおいて、NGとなったデータ(正常性を確認できなかったデータ)の個数をカウントする。また、予め決められた特定の種別のチェックに関しては、そのNG個数に対して所定のアルゴリズムに従った計数処理を行い、その結果が、予め設定した閾値を超過した場合はTCA (threshold crossing alart:閾値を越えたことを示すアラート) を出力する。さらに、特定の種別のチェックに関しては、NG検出時にエラーログを収集する。

エラーログにおいて収集すべきパラメータを以下に示す。

(1) 着信先アドレスDA(Destination Address )

(2) 送信元アドレスSA(Source Address)

(3) SNI 番号(Subscriber Network Interface No.)

(4) エラー種別

ところで、ユーザ(加入者)とSMDS処理用サーバとの間のPVC 上においては、前述したように、セルフォーマット(実際は、ATM セル形式で送受信が行われ、SMDS処理用サーバではL2−PDUで処理が行われる。ATM セル及びL2−PDUは、共に53バイトを基本構成としており、ここでは簡単のため、双方を単にセルと呼んでいる)でデータの転送を行う。ところが、上記のようなエラーログの収集はレイヤ3に関するものが多いため、SMDS処理用サーバにおいては、セル形式で受信したデータをいったんL3−PDUに組み立ててからその処理を行う。

上述のように、従来のSMDSにおいては、エラーログを収集する場合にも入力セルを上位レイヤのデータ形式(たとえば、L3−PDU)に組み立てて処理していた。このことが、SMDSにおける高速化処理の妨げとなっていた。

次に、上述のようなサービスは、ネットワークを構成する伝送路の物理的品質の信頼性が高いことを前提としている。このため、これらのネットワークの伝送品質を試験・評価することは重要である。

このような伝送路の試験・評価としては、コネクションレス通信サービスを提供しているネットワーク内において、OSセンター(ネットワークを管理するオペレーション・センター)から起動し、任意の局間リンク(交換機間のパス)の正常性を確かめる「局間ループバック試験」が行われている。この局間ループバック試験を、図898を参照しながら説明する。ここでは、SW局3とSW局6との間のリンクの試験を行うものとする。

試験の開始は、同図に示すように、まず、OSセンタ−1からSW局3に対して、試験用コネクションレスパケット送出要求メッセージ(試験開始要求)を送出する。この要求メッセージには、パケットの終着SW局6を示す識別情報IDが含まれている。SW局3は、その終着SW局6の識別アドレスを着信先アドレスDAとし、自局(SW局3)の識別アドレスを送信元アドレスSAとして試験用パケットを生成する。そして、その試験用パケットを終着SW局6に向けて出力する。

SW局4,SW局5においては、試験用パケットに対して通常のパケットと同様の処理を行い、終着SW局6へ転送する。終着SW局6では、試験用パケットを受信すると、そのパケットが有するDAとSAとを反転させて出力する。すなわち、上記終着SW局6から上記発SW局3へ向けてパケットが返送され、発SW局3に再び着信した時点でOSセンタ−1にその旨が報告される。

こうして、OSセンタ−1では、ネットワーク内でのパケットの伝達が正常に行われるかどうかの確認、すなわち伝送路(ここでは、SW局3とSW局6との間のリンク)の正常性を確認できる。また、この手順のなかで、発SW局3と終着SW局6はパケットのペイロード部分にタイムスタンプを刻印するため、この情報によりOSセンタ−1では、パケットの伝達時間を知ることができる。

しかし、上述の試験方式においては、その試験によって得られる情報はOSセンタ−(オペレーション・センター)のためのものであり、現在までのところ、加入者(図898における、端末2)がネットワークの伝送品質(伝達遅延時間等)を自主的に知る手段は提供されていなかった。このため、発信加入者からのパケットが着信先加入者に正常に届かないような場合、その加入者自身が加入者端末またはネットワーク側伝送路のどちらに障害要因があるのかを切り分けることがでず、障害からの復旧のためにはOSセンタ−を呼ぶ必要があり、そのために多大な時間とコストがかかっていた。

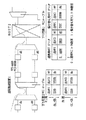

次に、図899に、SMDSの一実施形態を示す。同図において、SMDSサポートモジュールは、着信先アドレスDAの解析や各種チェックを行う。SMDSサポートモジュールS 部は、複数個の発SMDS加入者(a),(b) を収容し、DA解析や各種チェック等を行う。SMDSサポートモジュールR 部は、複数個の着SMDS加入者(x),(y) を収容し、各種チェック等を行う。これらS 部およびR 部から構成されるモジュールが、上述のSMDS処理用サーバ(SMDSメッセージハンドラ)に対応する。

各発SMDS加入者(a), (b)とSMDSサポートモジュールS 部との間はそれぞれPVC1,2によって接続され、SMDSサポートモジュールS 部とR 部との間はPVC 3によって接続され、そしてSMDSサポートモジュールR 部と各着SMDS加入者(x), (y)との間はそれぞれPVC 4,5で接続されている。

同図に示すSWをATM スイッチで構成した場合、発SMDS加入者(a),(b) から出力されるコネクションレスデータ(SMDSメッセージ)は、不図示のインタフェース部でセル形式に変換され、そのセルのヘッダ部に、着信先としてSMDSサポートモジュールを指定する特定のVPI/VCI 値(PVC 1,2を指定するVPI/VCI 値)を付与して転送することによって、SMDSサポートモジュールS 部に転送される。SMDSサポートモジュールS 部とR 部との間の転送では、PVC 3を示すVPI/VCI 値が付与されて出力され、さらに、SMDSサポートモジュールR 部から着SMDS加入者(x),(y) へ転送されるセルは、PVC 4,5を示す特定のVPI/VCI 値でSMDSサポートモジュールR 部から出力されて、着SMDS加入者(x),(y) に着信する。尚、各PVC はシステム初期設定時に確立される。

また、SMDSサポートモジュールS 部、R 部共に、収容可能な発・着SMDS加入者数には限度があるので、1つのSW局内にその最大収容数を超過するSMDS加入者を収容する場合は、複数個のSMDSサポートモジュールを用意する。この例を、図900に示す。この場合も、各接続は、PVC によって行う。同図は、SMDS加入者(a), (b), (x), (y)が、SMDSサポートモジュール▲1▼に収容され、SMDS加入者(c), (d), (v), (w)が、SMDSサポートモジュール▲2▼に収容される例を示しているである。なお、SMDSサポートモジュール▲1▼と▲2▼間にもPVC による接続が存在する。

上述のように、SMDSにおいては、データを転送するパスをPVC としてシステム初期設定時に確立してある。そして、発加入者(a),(b) がSMDSメッセージを出力すると、そのメッセージは上記PVC 1,2に沿ってSMDSサポートモジュールS 部に導かれ、PVC 3およびPVC 4,5を介して着SMDS加入者(x),(y) へ転送されるので、発SMDS加入者(a),(b) から出力されたSMDSメッセージが上記PVC に沿って確実に着SMDS加入者(x),(y) に届いているかのかを簡単に検証できない。

もし、上述のようなデータ転送が失敗した場合には、発加入者(a),(b) または着SMDS加入者(x),(y) からの苦情(コンプレイン)が発生することが予想されるが、この加入者コンプレインに対して、適切に(迅速に)上記検証がなされることが望まれる。また、このような検証を行う場合、出来るだけ低コストで実現することが望まれる。

ところで、PVC 試験および伝送時間などに関する試験については上述したが、SMDSにおいては、伝送されるSMDSデータの正常性の確認もする必要がある。データの正常性の確認方法としては、L3−PDUのBA−size, BE−tag, L2−PDU のLENGTHのチェック等が行われる。

BA−size チェックでは、L3−PDU(CPCS−PDU)のペイロード長を設定する値が正常かどうか確認する。BE−tag(Beginning Tag : 先頭タグ,End Tag : 最終タグ)チェックでは、L3−PDUの先頭と末尾の2つのタグが同一であることを検証することによってL3−PDUデータの正常性を確認する。LENGTHチェックは、L2−PDUの有効ペイロード長を示す値と、上記L3−PDUのBA−size との関係を検証することにより、L3−PDUとL2−PDUとの間での分解・組立が正常に行われたかを確認する。

しかし、この場合、L2−PDUに分解された状態でL3−PDUの正常性確認しようとすると、そのための回路の規模が極めて大きなものとなってしまう。また、L3−PDUのBA−size, BE−tag, L2−PDU LENGTHのチェックはそれぞれ互いに密接な関係があるため、各セル毎(L2−PDU毎)に処理を行うことは困難であった。一方、SMDS処理用サーバに入力されるセル形式のデータ(L2−PDU)を、いったんL3−PDUに組み立ててから処理すると、前述した問題と同様に、ソフトウェア処理が含まれることによって高速化が妨げられてしまう。

次に、ATM 交換ネットワークにおいてコネクションレス通信サービスを実現する場合には、コネクションレスデータ処理用サーバ(SMDSでは、SMDS処理用サーバ)を設け、加入者端末から出力されるコネクションレスデータのルーティング処理や各種チェック等を、そのサーバに依頼する。このようなコネクションレス通信サービスの実現方法の一例を図901に示す。

図901に示す構成は、基本的には図899に示した構成と同じである。すなわち、発信加入者(a) とコネクションレスデータ処理用サーバCLS 2との間にPVC 11が設定され、着信加入者(x) とコネクションレスデータ処理用サーバCLS 6との間にPVC 13が設定されている。これらのPVC は、コール・プロセッサCPR 3,7を用いて設定される。

図901に示す構成では、発信加入者(a) を収容するコネクションレスデータ処理用サーバCLS 2と着信加入者(x) を収容するコネクションレスデータ処理用サーバCLS 6とが異なる交換局に設けられた構成、即ち、コネクションレスデータ処理用サーバCLS 2は交換局SW1に対して設けられ、コネクションレスデータ処理用サーバCLS 6は交換局SW5に対して設けられた構成である。そして、これらコネクションレスデータ処理用サーバCLS 2,6間が、PVC 12によって接続されている。ここで、PVC 12が設定される大規模中継スイッチ4は、たとえば、SW1またはSW5と同じスイッチをいくつか中継させる構成、またはATM インターコネクション・スイッチ(AISW)である。

上記構成において、発信加入者(a) から着信加入者(x) にコネクションレスデータを転送する場合には、発信加入者(a) から出力されたデータは、PVC 11を介してコネクションレスデータ処理用サーバCLS 2に入力された後、PVC 12を介してコネクションレスデータ処理用サーバCLS 6へ転送される。そして、コネクションレスデータ処理用サーバCLS 6からPVC 13を介して着信加入者(x) へ転送される。これらPVC 上ではセル単位でのデータ転送が行われ、そのルーティング処理はコネクションレスデータ処理用サーバCLS 2および6によって行われる。

従来のコネクションレス通信サービスでは、図901に示したように、発信加入者(a) を収容するコネクションレスデータ処理用サーバCLS 2と着信加入者(x) を収容するコネクションレスデータ処理用サーバCLS 6とが異なる場合、それらコネクションレスデータ処理用サーバCLS 2,6間をPVC 12で接続している。そして、このPVC 12は、SW1,5および大規模中継スイッチ4と通過するように設定されている。このため、これらスイッチ内に予めコネクションレスサービス用の帯域リソースを確保し、その管理を行う必要がある。

したがって、従来のシステムでは、コネクションレスサービスのデータが流れていないときでも、各スイッチの帯域リソースを使用してしまっている。また、そのときの帯域リソースの管理も複雑なのもになっていた。

一方、ATM(Asynchronous Transfer Mode) サービス等の広帯域サービスを提供するB−ISDN (広帯域ISDN) 交換機、或いはSMDS(Switched Megabit Data Service) サービスを提供するSMDS交換機などの、セル交換を主体とした交換機は、従来の電話交換機又はN−IDSN (狭帯域ISDN) 交換機に比較して、格段に高い性能及び機能を有するため、その局内制御方式には独自の技術が必要とされる。

以下に、局内制御において本発明が対象とする従来技術及びその問題点について明らかにする。

まず、種々の伝送路インタフェース装置 (トランク) などの局内装置と交換機プロセッサとの間で制御情報の通信を行うための局内制御通信技術に関する課題について考察する。

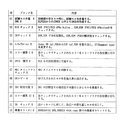

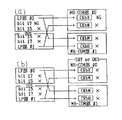

従来の交換システムにおける局内装置の制御においては、図902に示されるように、ATM スイッチ5と協調して動作する各局内装置6、7等が、入力制御装置4を介して、交換機プロセッサ(CC)1が接続されるシステムバス3に接続され、局内装置とCC1に接続される主記憶装置(MM)2との間で、DMA(ダイレクトメモリアクセス) 方式によって制御情報が転送されていた。

しかし、この方式では、全局内装置6、7をシステムバス3に接続しなくてはならず、各局内装置6、7とシステムバス3を接続するためのケーブルを装置数分用意する必要があり、局内装置6、7がシステムバス3から遠ければ遠いほどケーブルが長くなり接続構成上複雑になるという問題点を有している。

また、全局内装置6、7がシステムバス3に接続されることによりバスアクセスの際に必要となるアクセス権の獲得が競合し、バスアクセスが輻輳するという問題点も有している。

更に、システムバス3を各局内装置6、7まで延長することにより伝送品質が低下し、誤り制御手順を持たないDMA 手順では、データエラーやパリティエラーといった伝送エラーを発生するという問題点も有している。

次に、端末と交換機プロセッサなどの制御装置との間で呼設定情報等の制御情報の通信を行うための技術に関する課題につき考察する。

ATM交換システム等において、端末インタフェース装置を制御するには、交換機プロセッサ等の制御系装置との制御情報の通信が必要である。

制御情報の通信のための従来技術として、図903に示されるように、図902に示した場合と同様に、制御系装置(MPR1、PRIF2) から交換スイッチ(SW)3に接続される端末(TERM)4に、物理的なインタフェースが接続される方式がある。

しかし、この方式では、端末4毎に物理インタフェースが必要となるため、システム構成が複雑になり、また、端末4の増設が簡単ではないという問題点を有している。

次に、局内制御方式の1つである交換機の試験技術に関する課題につき考察する。

ATM 交換機等においては、セルが転送されるハイウエイに障害があるか否かの試験は、セルの送信や受信したセルの検索・収集を行うことのできる試験装置をハイウエイに接続することにより行われていた。この場合、宛先情報であるVPI (Virtual Path Identifier) 、VCI (Virtual Channel Identifier)、被試験装置内でセルを折り返す設定、その他LSI の設定などが試験装置から行われた後に、試験用のセルが送出されている。

しかし、このような方式では、複雑な構成の試験装置が必要となり、被試験装置への設定などに時間もかかるという問題点を有している。

次に、上述と同様の交換機の試験技術のうち、特にループバック試験に関する課題につき考察する。

音声・データ及び動画像などのようにトラヒック特性の異なる情報を結合して交換することのできるATM 交換機の普及とATM 交換網の拡大に従って、局間のパスの正常性を確認する試験の重要性も高くなっている。また、実際に運用に入っている状態で、いくつもの局を間に持つ2つの局の間に障害が発生した場合、より早期の障害の発見・修復が要求される。ATM 交換網のループバック試験方法はこの局間の障害の早期発見に有効な試験方法である。

ATM 交換機は市場に出始めたばかりである。ATM 交換網の局間試験について実例は未だない。しかし、従来の電子交換の試験方法の流れから次のような試験方法が、ATM 交換網の局間試験方法として考えられている。

この方法では試験装置がATM 交換機に接続され、オペレータによる操作によってループバック試験が行われる。試験時には相手局と連絡がとられ、相手局でも同様に試験装置がATM 交換機に接続され、連絡を取り合い、お互いの同期を取りながら試験が実施されることになる。

しかし、この方法では、ATM交換網の中に多数の局が存在した場合、それぞれの局に試験装置を配備する必要があるという問題点を有している。

また、試験装置の数が充分にない場合は、試験装置を持って各局を回り試験を行わなければならないという問題点も有している。

更に、局の中にはリモート局のように、オペレータが常時待機していない局もある。その場合、オペレータはその局まで行って試験を実施しなければならないという問題点を有している。

このように、上述の方法では、局間試験を行うためにオペレータに多大な労力が要求されるという問題点を有している。

次に、局内制御方式の1つである交換機スイッチ内のパフォーマンスの測定技術に関する課題につき考察する。

ATM を用いたSRM(Self Rooting Module)交換方式は、広帯域ISDNシステムを構築する際の前提条件であるが、このSRM 内のパフォーマンスを測定することは、従来困難であった。

次に、局内制御方式の1つである、ディジタル信号レベル3フォーマットであるDS3 フォーマットにインタフェースされる物理レイヤコンバージェンスプロトコルであるPLCPにおけるトレイラの制御に関する課題につき考察する。

B−ISDN又はSMDSのサービスにおいては、44.736MHz のサービスを実現するために、DS3(ディジタル信号レベル3) フォーマットが使用される。

本発明が対象とするシステム構成例を、図904及び図905に示す。図904は、BISDN端末がBISDN交換機に接続されている構成を示す。また、図905は、SMDS端末がSMDS交換機に接続されている構成を示す。本発明は、BISDN端末とBISDN交換機、又はSMDS端末とSMDS交換機の各送信部に関連する。

図906に、DS3 マルチフレーム構成を示す。DS3 のフレームは85ビット構成の基本フレームにより構成されている。基本フレームは1ビットのDS3 ヘッダと84ビットのDS3 ペイロードから構成されている。さらに8つの基本フレームで1つのサブフレームが構成されており、更に、7個のサブフレームで1つのマルチフレームが構成されている。即ち、1マルチフレームは、56個 (8×7) の基本フレームで構成されている。

BISDN のATM セルは53オクテット構成のセルであり、SMDSのL2−PDUセル (レベル2プロトコルデータユニットセル) も53バイト構成のセルである。即ち、基本構成は同じである。但し、ヘッダとペイロードの内容、HEC とHCS の値は異なっている。図907の(a) と(b) に、ATM セルとL2−PDUセルの構成を示す。

ATM セル又はL2−PDUセルは、直接DS3 基本フレームのペイロードに格納されるのではなく、PLCP (物理レイヤコンバージェンスプロトコル) のフレームを介して送信される。

図908に、DS3 フォーマットにインタフェースされるPLCPマルチフレームの構成を示す。

ATM セル又はL2−PDUセルは、PLCPフレーム内の53オクテットのPLCPペイロードにそれぞれ1セルずつ格納され、更に、PLCPマルチフレームは、それぞれ84ビットからなるセグメントに分割され、各セグメントがDS3 フレーム内の84オクテットのDS3 ペイロードに格納され、送信される。

PLCPフレームは4バイトのPLCPヘッダと53バイトのPLCPペイロードの繰り返し12個と、トレイラとからなる、マルチフレーム構成になっている。PLCPヘッダは、A1、A2バイトとPOHI、POH により構成される。トレイラ長は、13ニブル又は14ニブルである。ニブルとは4ビットのことであって、バイトの半分を示している。トレイラのデータは、4ビットのパターン”1100”が13個又は14個並べられたものである。

そして、PLCPの1マルチフレームは、平均して125 μsec(8KHz周期) で送信される。トレイラ長が可変であるため、平均値が規定される。

トレイラについて説明する。DS3 フレームは44.736MHz の伝送速度を有するため、以下の式から、125μsec の期間では、5592ビットが送信される。

【数1】

ビット数=44.736×106 (ビット/sec) ×125 ×10−6(sec) =5592ビット

しかし、DS3 フレームを構成するデータは、図906に示したように、1ビットのフレームビットデータと、84ビットのDS3 ペイロードとから構成されているため、125 μsec の期間のDS3 ペイロードの部分のビット数は5592×84/85=5526.211・・・となって、割り切れない。

また、PLCPマルチフレーム中のビット数は、トレイラ長が13ニブルの時に、57×12×8+13×4 =5524ビットであり、トレイラ長が14ニブルの時に、57×12×8+14×4 =5528ビットである。即ち、トレイラ長が13ニブルの場合には125 μsec の期間のDS3 ペイロードにおいて余りが生じ、トレイラ長が14ニブルの場合には125 μsec の期間のDS3 ペイロードにおいて不足が生じる。

そこで、PLCPマルチフレームを平均して125 μsec(8KHz周期) で送信するために、トレイラ長が13ニブルにされたり14ニブルにされたりしながら、PLCPマルチフレームが送出されることになる。

トレイラ長を表示するためには、C1バイトのサイクルスタッフカウンタが使用される (図908参照) 。図909に、サイクルスタッフカウンタに関する規定を示す。

図908に示されるように、C1バイトは3つのマルチフレーム周期でサイクリックに変化させられる。1番目のマルチフレームではC1は ”FFH ” で、この時のトレイラ長は13ニブル、2番目のマルチフレームではC1は ”00H ” で、この時のトレイラ長は14ニブル、3番目のマルチフレームではC1は ”66H ” か ”99H ” で、この時のトレイラ長は、C1=”66H ” の場合が13ニブル、C1=”99H ” の場合が14ニブルとなる。3番目のマルチフレームを13ニブルにするか14ニブルにするかは、PLCPマルチフレームの送出が平均して125 μsec(8KHz周期) になるように決定される。

そこで、3番目のマルチフレームのC1の値、即ち、トレイラの制御方法をどうするかという課題が生じる。以下に、従来のトレイラの制御方法について説明する。

3番目のマルチフレームを13ニブルにした場合のパターンをP、3番目のマルチフレームを14ニブルにした場合のパターンをQとすると、トレイラのニブル数のパターンは、Pパターンの場合は13→14→13のパターンになり、Qパターンの場合は13→14→14のパターンになる。

125 μsec の期間内において、DS3 ペイロードのビット数は5592×84/85=5526.211・・・であり、PLCPマルチフレーム中のビット数は、トレイラ長が13ニブルの時は5524ビット、トレイラ長が14ニブルの時は5528ビットである。従って、PLCPマルチフレームの周期は、PLCPマルチフレームのパターンがPである場合は125 μsec の周期に対して進み、PLCPマルチフレームのパターンがQである場合は125 μsec の周期に対して遅れることになる。

そのため、従来は、送信されるPLCPフレームの周期監視が行われ、その結果抽出されるクロックと44.736MHz を分周して得られる8KHzのクロックの位相が比較される。そして、位相が進んでいる時は送信されるPLCPマルチフレームのトレイラパターンがPに切り替えられ、位相が遅れている時は送信されるPLCPマルチフレームのトレイラパターンがQに切り替えられる。このようにして、PLCPマルチフレームの送信周期が調整される。

図910及び図911に、上記機能を実現する従来の回路構成及びその動作タイミングチャートを示す。

PLCPフレーム周期監視部7は、セレクタ3から送出されるPLCPフレームの送出周期を監視し、3つのPLCPフレームに1回、位相比較パルスSを出力する。分周部6は、クロック生成部5が生成する44.736MHz のクロックを5592分周することにより、8KHzのクロックを生成する。位相比較部8は、位相比較パルスSと8KHzクロックの位相を比較し、位相比較パルスSが遅れているときは値”1” の、位相比較パルスSが進んでいるときは値”0” のパターン切替え信号Cを出力する。

セレクタ3は、パターン切替え信号Cに基づいて、入力A1、A2を選択する。即ち、セレクタ3は、パターン切替え信号Cが、”0” の時はパターンPを選択し、”1” の時はパターンQを選択する。

パターンPとQのPLCPフレーム生成部1、2は、ATM セル又はL2−PDUセルを、PLCPペイロードに格納し、PLCPヘッダ及びトレイラを付加することにより、PLCPフレームを組み立てる。パターンP PLCP フレーム生成部1においては、ニブル数が13、14、13の3周期で繰り返すトレイラが付加され、パターンQ PLCP フレーム生成部2においては、ニブル数が13、14、14の3周期で繰り返すトレイラが付加される。

DS3 インタフェース部4は、PLCPフレームをDS3 ペイロードに挿入し、DS3 ヘッダを付加することにより、DS3 フレームを組み立てて送出する。

しかし、以上に示した従来技術では、トレイラパターンの選択が位相比較結果に基づいているため、パターンPとQの送信順序が極めて不規則である。

この結果、動作が複雑化し回路の複雑化を招いてしまうという問題点を有している。

加えて、送信タイミングの偏差が大きくなってしまうという問題点も有している。

次に、他の従来技術の問題点について説明する。

ATM 交換機においてマルチキャスト機能(ポイント・ツー・マルチポイント接続)を実現するためには以下の機能が必要となる。

▲1▼ セルのコピー機能

▲2▼ VPI/VCI の付け替え機能

セルのコピーは、交換機の出口に近い部分で行う方がスイッチとしてのリソースの利用効率が高くなる。コピーされたセルは、各加入者に分配されるが、この各加入者へ分配されるセルは互いに異なるVPI/VCI を有する。すなわち、各転送先加入者ごとにVPI/VCI 値を変換する必要がある。このVPI/VCI のビット数は、たとえば、22ビットまたはそれ以上であり、このような多数のビットを単純に変換すると、ハードウェア規模が大きくなってしまう。

ATM 交換機は、セルフルーティング方式でセル交換を行うが、大容量システムでセルフルーティング方式を行う場合は、スイッチ内部でマルチキャスト機能をサポートしたほうがスイッチの使用効率が高く、小型化が可能となり、また、コストを低く抑えることが出来る。

B−ISDNでサポートするサービスは、マルチキャスト機能ばかりでなく、ポイント・ツー・ポイントの接続のサービスも数多くサポートする必要がある。このため、交換機全体の規模を小さくするためには、ポイント・ツー・ポイント接続機能を実現するための構成にマルチキャスト機能を付加する場合、そのマルチキャスト機能としての追加機能を最小限としてシステムの大型化を防ぎ、コスト増加を小さくする必要がある。また、将来、マルチキャスト機能を増設する場合も考慮しなけらばならない。

また、ポイント・ツー・マルチポイント接続においては、セルのコピー数を指定する情報や、それらコピーされた各セルの転送先を示す情報等が必要になる。これらの情報は、セルが交換機に入力されるときにそのセルに付加されるタグ情報として設定する方法が一般的であるが、上記情報の情報量は少なくないので、タグ情報が数バイト〜10バイト程度となってしまう。このようなタグ情報をセルに付加すると、交換機内で処理されるセル長が長くなる。すなわち、タグ情報が大きくなると、セル全体に対する実データの割合が小さくなり、スループットの低下してしまう。

図912は、従来のマルチキャスト接続の一形態の構成図である。同図では、発信端末1が、ATM 交換機2を介して送信先端末4ー1〜4ー5へデータをマルチキャスト転送する例を示している。

発信端末1とATM 交換機2との間は、回線3で接続されているが、この回線3は、複数の呼(パス)を多重化して伝送することができる。また、ATM 交換機2と送信先端末4ー1〜4ー5との間もそれぞれ多重化伝送可能な加入者線で接続されている。ATM 交換機2内では、発信端末1から送出されるセル内に書き込まれている送信先情報に従って仮想的なパスが設定される。同図の例では、送信先端末4ー1〜4ー5へセルを転送するためのパスとして、仮想パス5ー1〜5ー5が設定されている。

上記マルチキャスト転送においては、セルは、発信端末1で送信先端末の数だけコピーされ、発信端末1と送信先端末4ー1〜4ー5との間でそれぞれ設定されるパスを介して転送される。このとき、回線3では、送信先端末4ー1〜4ー5へそれぞれセルを転送するために5チャネルが多重化されている。すなわち、5チャネル分の帯域が占有されている。

このように、図912に示す従来の方式では、1:Nのマルチキャスト転送を行うときに、発信端末と送信先端末との間にN本のパスを設定するので、回線3およびATM 交換機2のリソースを必要以上に使用していた。また、発信端末1の負担も大きい。

動画像通信の要求は、今後さらに増えることが予想される。たとえば、企業においては、遠距離に離れている社員と打合せを行う機会も多く、動画像を用いた会議電話機能の実現が待ち望まれる。このようなサービスは、個人加入者を満足させるだけでなく、企業においては地理的障壁を越えた円滑なビジネス推進をサポートすることが予想される。

ところが、現在までに提供されているサービスは必ずしも豊富ではない。すなわち、広帯域通信ネットワークでは、専用線サービスを除いて1対1の通信が主流であり、三者通話等の多端子接続を呼ごとに制御する方式はいまだ実用化されていない。

次に、回線を処理する交換機内装置に障害が発生した場合の処理に関する課題について考察する。

ATM 交換機においては、その交換機内の通話路系装置が、VPI/VCI によって規定される多数の仮想的な回線(以下、単に回線という)を処理する。従って、通話路系装置に障害が発生した場合に、その装置が処理している回線をどのように扱うかが、通信品質を確保する上で重要となる。

従来、交換機内の通話路系装置に障害が発生した場合、その装置が処理している回線を使用する呼接続は、全てシステムの障害監視処理から起動される強制解放処理により、強制終了させられている。このため、加入者からみれば、突然通話が出来なくなるという現象が発生するという問題点を有している。

また、従来、通話路系装置が処理する回線を管理する機構は、提供されていない。

次に、回線上で障害が検出された場合の処理に関する課題につき考察する。

従来、2重化されていない単一構成のATM 交換機において回線障害が検出された場合、加入者情報、課金情報、トラヒック情報、性能情報等の伝送情報は、予備回線等を用いた物理回線単位の回線切替え処理によって救済されている。

具体的には、例えば図913に示されるように、遠隔集線装置1とATM 交換機2が複数本の物理回線によって接続されている場合に、1つの物理回線で障害が発生すると、障害回線や他の回線に空き帯域があってもそれらは使用されず、保守運用端末3からの指示に基づいて、障害回線の状態がそっくりそのまま予備回線等の新たな代替回線に載せ換えられる。

このため、他回線に大きな空き帯域が存在していても、それらが有効に利用されず、回線の利用効率が低下してしまうという問題点を有している。

また、物理回線単位の回線切替え処理を行うためには、充分な予備回線を準備しておくか、各物理回線を2重化する必要があり、その結果、通信コストが非常に高くなってしまうという問題点を有している。

最後に、交換機内の通話路系装置等の局内装置は、通信の信頼性を確保するために一般に2重する必要がある。そして、運用系の局内装置に障害が発生した場合は、それに設定されている各種通信制御データを予備系の局内装置に転送した後に、今まで運用系装置であった局内装置の動作を停止させると共に今まで予備系であった局内装置を新たな運用系装置としてその動作を開始させる必要がある。

この場合に、従来は、運用系の局内装置に設定されている各種通信制御データは、その局内装置を制御するプロセッサによって、予備系の局内装置に転送されている。しかし、ATM 交換機等の場合には上記各種通信制御データのデータ量は膨大であるため、そのようなデータをプロセッサによって運用系の局内装置から予備系の局内装置に転送するためには、膨大な時間を必要として、障害発生時の交換機の信頼性の確保に影響を与えてしまうという問題点を有している。

【0003】

【発明が解決しようとする課題】

コネクションレス通信システムは、上述のSMDSも含めて、高い信頼性が要求されるが、現在までのところ全体システムとしてその品質を向上させる技術は確立されていなかった。本発明は、基本的に、コネクションレス通信システムの品質を向上させること、及びセル交換等を行う交換機の効率的な局内制御方式を提供することを目的とする。

本発明のより具体的な第1の課題は、高速データ交換に適したコネクションレス通信システムを提供することである。

本発明のより具体的な第2の課題は、SMDS処理用サーバのハードウェア構成を小さくすることである。

本発明のより具体的な第3の課題は、コネクションレス通信におけるエラーログ収集の処理を高速、かつ容易に行うことである。

本発明のより具体的な第4の課題は、加入者自身が、コネクションレス通信システムのネットワークの伝送試験を行えるようにすることである。

本発明の第5の課題は、コネクションレス通信システムのPVC 試験を適切に(迅速に)かつ低コストで実現することである。

本発明のより具体的な第6の課題は、コネクションレス通信システムにおいてSMDSデータの正常性確認を、低コストで比較的小規模な回路で実現することである。

本発明のより具体的な第7の課題は、コネクションレス通信において、スイッチの帯域リソースを有効に利用する方法を提供すること、および帯域の割当管理を削減することである。

本発明のより具体的な第8の課題は、局内装置の接続構成を単純化すると共に、バスアクセス時の競合を軽減し、更に、遠隔に配置される装置に対しても制御情報伝送時のエラーを速やかに復旧可能とすることにある。

本発明のより具体的な第9の課題は、端末を接続するためのシステム構成の簡略化と、端末の増設の容易化を可能とすることにある。

本発明のより具体的な第10の課題は、簡単な試験構成で被試験装置への設定も短時間で済む試験方式を実現することにある。

本発明のより具体的な第11の課題は、試験装置を必要とせず、各局間のループバック試験時においても、着側の局にオペレータを特に待機させる必要もなく、発側局からの簡単なコマンド入力により試験を可能とすることにある。

本発明のより具体的な第12の課題は、スイッチ内のトラヒック量を少ないハードウエアで計測可能とすることにより、スイッチのパフォーマンスの測定を可能とすることにある。

本発明のより具体的な第13の課題は、DS3 フォーマットにインタフェースされるPLCPマルチフレームのトレイラ制御において、動作の単純化を実現することにある。

本発明のより具体的な第14の課題は、交換システムの大型化を防ぎ、低コストで増設等が容易なポイント・ツー・マルチポイント接続機能を提供することである。

本発明のより具体的な第15の課題は、スイッチの外部に特別な装置を設けることなくポイント・ツー・マルチポイント接続機能を提供することである。

本発明のより具体的な第16の課題は、ハードウェア資源を効率的に使用できるマルチキャスト接続を提供することである。

本発明のより具体的な第17の課題は、広帯域通信ネットワークにおいて画像付き三者通話などの多端子接続サービスの呼処理機能を提供することである。

本発明のより具体的な第18の課題は、交換機内装置が処理する回線に関する情報の収集と、障害発生時の交換機内装置の安全な変更を実現することを目的とする。

本発明のより具体的な第19の課題は、回線上で障害が検出された場合に、帯域(VPI/VCI )単位での安全な回線切替えを実現することを目的とする。

本発明のより具体的な第20の課題は、上述の第19の課題と同様に回線上で障害が検出されたときに帯域(VPI/VCI )単位で回線切替えを行う場合に、特に遠隔集線装置とATM 交換機が接続される構成においてその回線切替えを行うための具体的な技術を提供することを目的とする。

本発明のより具体的な第21の課題は、運用系の局内装置に障害が発生した場合における、それに設定されている各種通信制御データの予備系の局内装置への転送を、安全かつ高速に実行可能とすることを目的とする。

【0004】

【発明の実施の形態の目次】

<パート1> 本実施例の全体説明

1. 本実施例が対象とするシステムの概観

1.1 概説

1.2 本実施例が提供するインタフェース及びサービス

1.2.1 加入者インタフェース(Subscriber Interfaces)

1.2.1.1 光ファイバインタフェース

1.2.1.2 メタリックインタフェース

1.2.2 ネットワークインタフェース

1.2.3 サービス

1.3 システム構成

1.3.1 広帯域交換機アーキテクチャ

1.3.2 スイッチトマルチメガビットデータサービス(SMDS)

2. 本実施例が対象とするハードウエアの説明

2.1 スモールホスト用ATM ネットワーク

2.1.1 ATM 加入者スイッチ(ASSW)

2.1.2 ASSWにおける加入者及びネットワークインタフェース

2.1.2.1 加入者インタフェースシェルフ(SIFSH)

2.1.2.2 ATM DS−1シェルフ(ADS1SH)

2.1.2.3 ファイバインタフェースシェルフ(FIFSH)

2.1.3 ASSW ATMスイッチモジュール

2.1.3.1 ATM スイッチングシェルフ (ASSWSH)

2.1.3.2 デイジーチェーン構成

2.1.4 ASSWにおけるその他のATM ネットワークサポート装置及びテストセル生成方式

2.1.4.1 ループバック用加入者インタフェースシェルフ (SIFSH)

2.1.4.2 テストセルジェネレータ用加入者インタフェースシェルフ

2.1.5 ASSWにおけるシグナリング装置

2.1.6 SMDSメッセージハンドラ

2.1.6.1 加入者メッセージハンドラシェルフ (SBMESH)

2.1.6.2 ゲートウエイメッセージハンドラシェルフ (GWMESH)

2.2 広帯域遠隔交換装置(BRSU)

2.3 広帯域遠隔回線集線装置(BRLC)

2.3.1 加入者入力ポート

2.3.2 アンビリカル装置

2.3.3 ネットワーク装置

3. 本実施例で実現される機能

3.1 概説

3.2 ホスト交換機

3.3 ATM 加入者スイッチ (ASSW)

3.3.1 ATM スイッチモジュール (ASM)

3.3.2 加入者/ネットワークインタフェース

3.3.3 広帯域シグナリング・コントローラ(BSGC)

3.3.4 メッセージ・ハンドラ(SMDS)

3.3.5 広帯域コール・プロセッサ(BCPR)

3.3.6 メンテナンス・アンド・オペレーション・システム(MOS)

3.3.7 オペレーション・アンド・メンテナンス・プロセッサ(OMP)

3.3.8 システム・インテグレーション・プロセッサ(SIP )

3.4 広帯域遠隔集線装置(BRLC)

3.5 広帯域遠隔交換装置(BRSU)

3.6 SMDSの実施態様

3.7 トラフィック管理

3.7.1 呼受付制御

3.7.2 ユーザ・パラメータ・コントロール(UPC )

3.7.3 セル・ルーティングの優先度

3.8 データ・コレクション

4. その他

<パート2> DS3−SMDSインタフェース

1. 概略説明

2. 回線インタフェースの説明

2.1 DS3 回線インタフェース

2.1.1 ペイロードマッピング

2.1.2 DS3 フレームフォーマット

3. PLCPフレームフォーマット

3.1 DS3 PLCPフレームフォーマット

4. DS3−SMDSインタフェース L2−PDUフォーマット

4.1 DS3−SMDS L2−PDU フォーマット

4.2 ネットワークコントロールインフォメーション

4.3 セグメントタイプ

4.4 メッセージ識別子

4.5 セグメンテーションユニット

4.6 ペイロードレングス

4.7 ペイロードCRC

5. L2−PDUとATM セルとの関係

6. DS3 アンビリカルリンクフォーマット

7. ハードウエアコンフィギュレーション

7.1 概略説明

7.2 DS3 レイヤ終端機能

7.2.1 回線障害処理

7.2.2 各種アラームの検出・復旧条件

7.3 DS3 PLCPレイヤ終端機能

7.3.1 PLCP障害処理

7.3.2 各種アラームの検出・復旧条件

7.4 L2−PDUヘッダチェック機能(HCS)

7.5 L2−PDUヘッダパターン生成機能

7.6 DQDB(Distributed Queue Dual Bus)シーケンス機能

7.7 DS3 レイヤ/PLCPレイヤパフォーマンスモニタ機能

7.7.1 DS3 レイヤ

7.7.2 DS3−PLCPレイヤ

7.8 受信L2−PDUデータ変換機能 (45Mbps→156Mbps)

7.9 送信L2−PDUデータビットレート変換機能(156Mbps→45Mbps)

7.10 SIFSH Commonに対するインタフェース機能

7.11 MSD/MSCN情報のLAP 終端機能

7.12 DS3−SMDS L2−PDU セル及びLAP セルのマルチプレクス機能

7.13 DS3−SMDS L2−PDU セル及びLAP セルのデマルチプレクス機能

7.14 特定VCI/VPI セルのループバック機能

7.14.1 “0”ビットが付加されたセルのループバック機能

7.14.2 特定VPI/VCI が付加されたセルのループバック機能

7.15 MSCNデータマルチプレクス機能

7.16 MSD データドロッパ機能

8. MSD(Maintenance Signal Driver)インタフェース

8.1 MSD情報

8.1.1 E−MSD ハードウエアインタフェース

8.1.2 DS3−SMDSインタフェースにおけるE−MSD 収容表

8.2 E−MSD詳細説明

8.2.1 ハードウエアリセット

8.2.2 ループバック

8.2.3 疑似障害ポイント

8.2.4 AIS 送出ポイント

9. MSCN(Maintenance SCaNer)インタフェース

9.1.1 E−MSCNのハードウエアインタフェース

9.1.2 E−MSCN の詳細

9.2 DS3−SMDSインタフェースでのE−MSCN処理

9.2.1 SIFSH Commonインタフェース障害

9.2.2 DS3−SMDSインタフェースハードウエア障害

9.2.3 局内制御通信が不可能となるDS3−SMDSインタフェースハードウエア障害

9.2.4 マイクロプロセッサ障害

9.2.5 タイマ障害

9.2.6 DS3 レイヤアラーム

9.2.7 パフォーマンスモニタ閾値交差アラート

9.2.8 DS3−SMDSインタフェースにおけるセル廃棄

9.2.9 診断結果通知

10. DS3−SMDSインタフェース簡易LAP−D プロトコル

10.1 ソフトウエアインタフェース

10.2 ハードウエアインタフェース

10.3 VPI/VCI の設定

10.4 誤り監視

10.5 AAL インタフェース

10.5.1 SAR−PDU フォーマット

10.6 AAL の機能

10.7 誤り監視

10.8 L2インタフェース

10.8.1 L2の機能

10.8.2 フレームフォーマット

10.8.3 コネクション設定手順

10.8.4 リンクの状態監視

10.8.5 確認手順

10.8.6 障害監視

10.9 L3インタフェース

10.9.1 L3フレームフォーマット

10.9.2 通信手順

10.9.3 誤り制御

11. DS3−SMDS インタフェースの状態管理

11.1 初期設定

11.2 閉塞

11.3 インサービス(In Service)化

11.4 未実装化

11.5 障害処理

11.5.1 障害監視

11.5.2 障害検出時の処理

11.5.3 障害の特定

11.5.4 復旧監視

11.6 各種処理シーケンス

12. DS3−SMDSインタフェースバッファ輻輳制御

13. 試験・保守

13.1 DS3−SMDSインタフェースが有するループバック機能

13.1.1 タグ領域に“0”ビットが付加されたセルのループバック機能

13.1.2 全セルのループバック機能

13.1.3 特定VPI/VCI が付加されたセルのループバック機能

13.1.4 ラインループバック機能

13.2 試験方法

13.2.1 DS3−SMDSラインループバック試験

13.2.1.1 DSX−3 でのラインループバック試験

13.2.1.2 RLC でのラインループバック試験

13.2.2 アクティブ系オンデマンド(ON−Demand) 試験

13.2.3 PVC パス導通試験

13.2.4 DS3−SMDSインタフェース試験、診断

13.2.4.1 DS3−SMDSインタフェースPCB におけるATM セル透過試験

13.2.4.2 DS3−SMDSインタフェースPCB におけるハードウエア正常性確認試験

14. 障害処理

14.1 障害検出ポイントと通知方式

14.1.1 障害内容

14.1.2 OBP 障害

14.1.3 個別部 (DS3−SMDSインタフェース)におけるOBP 障害

14.1.3.1 +5V OBP 障害

14.1.3.2 −5.2V OBP 障害

14.1.4 パッケージ抜け障害

14.1.5 ヒューズ断障害

14.1.6 パッケージ誤挿入障害

14.1.7 DS3−SMDSインタフェース個別部のPCB の障害

15. 各PCB の機能

15.1 各PCB の機能

15.1.1 HAFOOAの機能

15.1.1.1 MSD/MSCN情報のLAP 終端機能

15.1.1.2 SIFSH Commonに対するインタフェース機能

15.1.1.3 DS3−SMDS L2−PDU セル及びLAP セルのマルチプレクス/デマルチプレクス

15.1.1.4 特定VPI/VCI が付加されたセルのループバック機能

15.1.1.5 MSCNデータのマルチプレクス機能

15.1.1.6 MSD データドロッパ機能

15.1.1.7 アクティブコントロール機能

15.1.1.8 マイクロプロセッサインタフェース機能

15.1.2 HLPO1Aの機能

15.1.2.1 156Mbps →45Mbpsデータ変換機能

15.1.2.2 45Mbps→156Mbps データ変換機能

15.1.2.3 DQDB処理機能

15.1.3 HDTOOAの機能

15.1.3.1 DS3 レイヤ終端機能

15.1.3.2 DS3 PLCPレイヤ終端機能

15.1.3.3 受信L2−PDUヘッダチェック機能(HCS)

15.1.3.4 L2−PDUヘッダパターン生成機能

16. ファームウエアインタフェース

16.1 概略説明

16.2 ハードウエアとファームウエア間のインタフェースの概要

<パート3> SIFSH

1. 概説

1.1 SIFSH のシステム内における位置付け

1.2 機能概要

2. シェルフ構成

2.1 構成

2.1.1 SIFCOM

2.1.2 個別部

2.2 電源系統

2.2.1 −48V/CG

2.2.2 SAB/SABG

2.2.3 +5V/E

3. 物理インタフェース

3.1 スイッチインタフェース

3.1.1 622Mbps セルハイウエイインタフェース

3.1.2 系切替え信号

3.2 SYNSH インタフェース

3.3 個別部インタフェース

3.3.1 156Mbps セルハイウエイインタフェース

3.3.1.1 上り156Mbps セルハイウエイインタフェース

3.3.1.2 下り156Mbps セルハイウエイインタフェース

3.3.2 E−MSD/E−MSCNハイウエイインタフェース

3.3.2.1 系制御

3.3.2.2 物理仕様

3.3.2.3 論理仕様

3.3.2.3.1 個別部受信側仕様

3.3.2.3.2 フレーム同期

3.3.2.3.3 パイロット0/1 信号チェック (EMSDハイウエイのスタックの検出)

3.3.2.3.4 2度読み処理

3.3.2.3.5 個別部送信側仕様

3.3.2.3.6 障害検出

3.4 クロックインタフェース

4. ソフトウエアインタフェース

4.1 概要

4.2 局内制御通信のレイヤ構造

4.2.1 ATM レイヤセルフォーマット

4.2.2 SAR−PDU フォーマット

4.2.3 LAP−D フォーマット (レイヤ2)

5. タグの割当

6. 機能

6.1 MUX

6.1.1 概要

6.1.2 MUX 部の構成

6.1.3 多重制御方式

6.1.4 バッファ監視

6.1.5 書き込み制御

6.1.6 書き込み異常処理

6.1.6.1 セル長が短い場合

6.1.6.2 セル長が長い場合

6.1.7 読み出し制御

6.1.8 読み出し異常処理

6.1.9 バッファ輻輳制御

6.2 DMUX

6.2.1 概要

6.2.2 機能

6.2.3 ダイナミックタグマッチング

6.2.4 バッファ監視

6.3 VCC

6.3.1 VCC の位置

6.3.2 VCC 用メモリ量

6.3.3 系間VCC コピー

6.3.3.1 目的

6.3.3.2 系間コピーの契機

6.3.3.3 コピー対象情報

6.3.3.4 INS 化処理手順

6.3.3.5 コピー実行不可報告

6.3.4 VCC とSMDSサービスとの関係

6.4 シグナリング処理(EGCLAD)

6.4.1 概要

6.4.2 EGCLAD LSIの機能

6.4.2.1 ATM ヘッダチェック機能

6.4.2.2 ATM ヘッダインサート機能

7. 試験, 保守

7.1 MCによるパス品質の監視

7.2 TCG による試験セルの導通試験

8. 障害処理

8.1 障害検出ポイントと通知方式

8.1.1 障害モード

8.1.2 OBP 障害

8.1.2.1 個別部OBP 障害

8.1.2.2 SIFCOMにおけるOBP 障害

8.1.3 パッケージ抜け障害

8.1.3.1 個別部パッケージ 抜け

8.1.3.2 SIFCOMパッケージ抜け

8.1.3.3 パワーパッケージ抜け

8.1.4 ヒューズ断障害

8.1.4.1 個別部用ヒューズ断障害

8.1.4.2 SIFCOM用ヒューズ断障害

8.1.5 SIFCOMパッケージ前面コネクタ抜け障害

8.1.5.1 50芯同軸フラットケーブル障害

8.1.5.2 50芯TDバスケーブル障害

8.1.6 パッケージ 誤挿入障害

8.1.7 個別部パッケージ障害

8.1.8 SIFCOMパッケージ障害

9. 回線プロテクション(N+1方式)

9.1 N+1 プロテクション方式の概要

9.2 回線の切り替えのシーケンス

9.3 予備回線へのVCC の設定

9.4 予備回線への切り替え

9.5 切り替えコマンド

<パート4> ASSWSH

1. 概要

1.1 機能の概略

2. 装置構成

2.1 装置構成

3. インタフェース

3.1 通話路系

3.2 制御系

3.3 クロック系

3.4 ASSWSH−A内ブロック間インタフェース

4. 詳細機能

5. トラヒックコントロール

5.1 セル廃棄クラス

5.2 輻輳制御

5.2.1 SWMX内輻輳制御

5.2.2 SWMDX 内輻輳制御

5.2.3 セル廃棄

5.3 トラヒック測定処理

6. ファームウエア機能

6.1 INFAインタフェース

6.2 装置内ハードインタフェース

6.3 障害処理

6.3.1 障害検出

6.3.2 メッセージボックス

6.4 自己診断

7. 保守運用

7.1 ソフトウエア−ハードウエアインタフェース

7.2 運用処理

7.2.1 状態遷移

7.2.2 HMX03A指定搭載

7.3 障害処理

<パート5>

1. 概要

1.1 概要

1.1.1 システム内の位置付け

1.1.2 SMDSデータ処理の概要

1.2 方式構成

1.3 冗長構成

2. 処理方式

2.1 MH網の構成

2.2 ルーティング方式

2.3 VPI/VCI/MID の割当て法

2.3.1 VPI/VCI の割り当て方法

2.3.2 MID の割り当て方法

2.4 グループアドレス

2.5 多重化処理について

2.6 機能概略

3. SMDS

3.1 処理概要

3.2 構成

3.3 各機能ブロックとエラーフラグの対応

3.4 各ブロックの処理

4. RMLP

4.1 処理概要

4.2 構成

4.2.1 PVC 試験

4.2.2 MSCN

4.2.3 MSD

4.2.4 各機能ブロックとエラーフラグの対応

4.2.5 RMLPとLP−COMのデータインタフェース

4.3 HMH00A

4.3.1 交換セレクト

4.3.2 タイミング・ジェネレータ

4.3.3 アドレス・フィルタ

4.4 HMH01A

4.4.1 試験セル多重

4.4.2 MID チェック

4.4.3 SNチェック

4.4.4 エンキャプセレーション

4.4.5 エラー編集I

4.4.6 RMID獲得

4.4.7 MRI タイムアウトチェック

4.4.8 GAコピー

4.4.9 SNI 利用可能

4.4.10 エラー編集II

4.4.11 SAチェック

4.5 HMH04A

4.5.1 SAスクリーニング

4.6 HMH02A

4.6.1 構成概要

4.6.2 機能概要

4.6.3 インタフェース概要

4.6.4 詳細説明

5. MH−COM(MH共通部)

5.1 概要

5.2 RDMX/SMUX 機能(HMX10A)

5.3 SDMX/RMUX 機能(HMX11A)

5.4 VCC 機能/テストセルMUX 機能/スケジューラ機能(HMX12A)

5.4.1 VCC 機能

5.4.2 テストセル多重化機能

5.4.3 スケジュール機能

5.5 LAP 終端・始端、クロック分配(HSF05A)

5.5.1 LAP 終端・始端

5.5.2 クロック分配

6. プロトコル・パフォーマンス・モニタ

6.1 概要

6.2 L2プロトコル・パフォーマンス・モニタ

6.3 L3プロトコル・パフォーマンス・モニタ

6.4 Ingress 部 (イングレス部) におけるプロトコル・パフォーマンス・モニタ

6.4.1 処理方式

6.4.2 処理詳細

6.5 Egress部 (エグレス部) におけるプロトコル・パフォーマンス・モニタ

6.5.1 処理方式

6.5.2 処理詳細

7. ネットワーク・データ・コレクション

7.1 概要

7.2 ネットワーク・データ・コレクション・パラメータ

7.3 Ingress 部 (イングレス部) におけるネットワーク・データ・コレクション

7.3.1 処理方式

7.3.2 処理詳細

7.4 Egress部 (エグレス部) におけるネットワーク・データ・コレクション

7.4.1 処理方式

7.4.2 処理詳細

8. 課金機能

8.1 概要

8.2 課金処理

8.3 チェック機能

9. LP−COM部(INF インタフェース部)

9.1 概要

9.2 機能概要

9.3 INF インタフェース制御手順

9.3.1 INF インタフェース制御

9.3.2 INF インタフェース割り込み制御

9.4 SMLP/RMLP 制御

10. 各種インタフェース

11. ソフトインタフェース

11.1 初期設定

11.1.1 MH−COM部の初期設定

11.1.2 LP部の初期設定

11.2 INS 処理

11.2.1 MH−COM部のINS 処理

11.2.2 LP部のINS 処理

11.3 障害監視・系切替え

11.3.1 MH−COM部の障害監視

11.3.2 MH−COM部の障害通知・処理のシーケンス

11.3.3 LP部との間のINF を使用した通信に関する障害

11.3.4 LP部内のMSCNにて発見する障害

11.3.5 LP部のヘルスチェック

11.3.6 系切り換え

11.4 試験・診断

11.4.1 TCG を用いた試験

11.4.2 SBMESHでの折り返し試験

11.4.3 SNI−SBMESH間のPVC 試験

11.4.4 MESH−MH 間のPVC 試験

11.4.5 PVC 試験結果のチェック

11.4.6 MH−COMの診断

11.4.7 LP部の診断

11.5 MSCN

11.5.1 MH−COM部のMSCN

11.5.2 LP部のMSCN

11.6 MSD

11.6.1 MH−COM部のMSD

11.6.2 LP部のMSD

11.7 課金・統計処理

11.7.1 概要

11.7.2 課金処理

11.7.3 プロトコル・パフォーマンス・モニタ処理

11.7.4 ネットワーク・データコレクション処理

11.7.5 各種セル数の処理

<パート6> GWMESH

1. 概要

1.1 概要

1.1.1 システム内の位置付け

1.2 方式構成

1.3 冗長構成

2. 処理方式

2.1 ネットワーク方式

2.2 ルーティング方式

2.3 グループアドレスの処理

2.4 Load Splitting (ロード・スプリッティング:負荷分散)

2.4.1 ロード・スプリッティングの特徴

2.4.2 キー生成

2.4.3 キー割当

3. ICLP (インカミングLP)

3.1 処理概要

3.2 構成

3.3 各機能ブロックとエラーフラグの対応

3.4 ICLP入出力フォーマット

3.5 ICLP処理フロー

3.6 各PKG ブロック

3.6.1 HMH11A

3.6.2 HMH12A

3.6.3 HMH13A

4. OGLP (アウトゴーイングLP)

4.1 処理概要

4.2 構成

4.3 各機能ブロックとエラーフラグの対応

4.4 セルフォーマット

4.5 処理フロー

4.6 各PKG ブロック

4.6.1 HMH07A

4.6.2 HMH08A

4.6.3 HMH09A

4.6.4 HMH10A

5. MH−COM (MH共通部)

5.1 概要

5.2 HMX10A

5.3 HMX11A

5.4 HMX12A

5.5 HSF05A

6. プロトコル・パフォーマンス・モニタ

6.1 概要

6.2 L2プロトコル・パフォーマンス・モニタ

6.3 L3プロトコル・パフォーマンス・モニタ

6.4 Incoming部におけるプロトコル・パフォーマンス・モニタ

6.4.1 処理方法

6.4.2 処理詳細

6.5 0utgoing部におけるプロトコル・パフォーマンス・モニタ

6.5.1 処理方法

6.5.2 処理詳細

7. ネットワーク・データ・コレクション

7.1 概要

7.2 ネットワーク・データ・コレクション・パラメータ

7.3 Incoming部におけるネットワーク・データ・コレクション

7.3.1 処理方式

7.3.2 処理詳細

7.4 Outgoing部におけるネットワーク・データ・コレクション

7.4.1 処理方式

7.4.2 処理詳細

8. 課金

8.1 Data Generating (データ生成)

8.2 Data Aggregation (データ集計)

9. LP−COM部 (INF インタフェース部)

9.1 概要

9.2 機能概要

9.3 INF インタフェース制御手順

9.3.1 INF インタフェース制御

9.3.2 INF インタフェース割り込み制御

9.4 ICLP/OGLP 制御

10. ソフトインタフェース

10.1 初期設定

10.1.1 MH−COM部の初期設定

10.1.2 LP部の初期設定

10.2 INS 処理

10.2.1 MH−COM部のINS 化処理

10.2.2 LP部のINS 化

10.3 系切替え

10.3.1 MHCOM 部の系切替え

10.3.2 LP部の系切替え

10.4 障害監視

10.4.1 MH−COM部の障害監視

10.4.2 INF 通信に関する障害監視

10.5 試験、診断

10.5.1 TCG を用いた試験

10.5.2 ICI/ISSIとGWMESHとの間のPVC 試験

10.5.3 SBMESH / GEMESH とGWMESHとの間のPVC 試験

10.5.4 局間試験

10.5.5 各部の試験用機能

10.5.6 自己診断

<パート7> BSGCSH

1. 概説

1.1 BSGCSH及びBSGCの交換機システム内での位置

1.2 BSGCの機能分担

1.2.1 INFの機能

1.2.2 LAP−D の機能

1.2.3 局内制御通信リンク

1.2.4 ATM スイッチとのインタフェース

1.2.5 メタシグナリング(Meta−signaling) 通信

1.3 BSGCのポートの数と割当の条件

1.3.1 最大ポート数

1.3.2 必要ポート数

1.3.3 BSGCと他の装置の間の転送速度

1.3.4 BSGCの処理能力とポートの割当条件

2. BSGCH機能概要

2.1 緒元

2.2 上位インタフェース(INFインタフェース)

2.2.1 INF(周辺装置インタフェース) 制御におけるハードウエア構成

2.2.2 INF インタフェース制御手順

2.3 スイッチインタフェース (CARP及びVCC インタフェース)

2.3.1 スイッチ内2重化装置制御ハードウエア構成

2.3.2 スイッチ内信号制御

2.3.2.1 シグナリング用信号制御モデル (1重化装置を含む)

2.3.2.2 2重化装置用信号制御モデル (共通部用)

2.3.3 局内制御通信用VPI/VCI について

2.3.4 BSGC−COM におけるセル廃棄手段

2.4 BSGC 装置制御

2.4.2 BSGC障害処理

2.5 通信制御

2.5.1 Q.922からの差分

2.5.2 局内LAP−D 通信 (局内制御通信)

2.6 診断機能

2.6.1 診断対象項目

2.6.2 局内2重化装置診断用通信リンク

2.7 プログラムモジュールの構成

3. INF インタフェース

3.1 ハードウエア構成

3.2 DMA ビット配列

3.2.1 DAM 転送データのビット配列

3.3 INF 制御手順

3.3.1 コマンドキューとステータスキュー

3.3.2 コマンド起動とステータス起動の競合

3.3.3 輻輳制御

3.3.3.1 受信系輻輳制御

3.3.3.2 送信系輻輳制御

3.3.3.3 BSGC輻輳制御

3.4 INF の初期設定

3.5 INF の優先制御

4. スイッチインタフェース

4.1 タグ割当

4.1.1 タグ割当の概念

4.1.2 BSGCからASSW方向への通信におけるタグ割当

4.1.3 ASSWからBSGC方向への通信におけるタグ割当

4.2 CARP制御手順

4.2.1 ATM ヘッダ

4.2.2 CARP LSI の機能

4.2.3 統計機能

4.3 VCC 設定手順及びVCC コピー手順

5. BSGC装置制御手順

5.1 BSGC障害監視

5.1.1 BSGCSHの障害箇所

5.1.2 障害発生時の系管理

5.1.3 BSGCへの通知手段

5.1.4 復旧監視

5.1.4.2 交換機ソフトウエアにおける復旧監視

5.1.4.1 BSGCにおける復旧監視

5.1.5 BSGCハードウエアが検出する障害

5.1.6 BSGCファームウエアが検出する障害

5.1.6.1 BSGC−COMにおける障害 (BSGC自身の障害を除く)

5.1.6.2 スタンバイ系BSGCにおける障害

5.2 TM セーブ方式

5.3 統計機能

6. 通信制御

6.1 局内制御通信の制御

6.1.1 シグナリングセルフォーマット

6.1.2 改版LAPDとの差分

7. BSGC−COM

7.1 BSGC−COMのハードウエア構成

7.2 BSGC−COMの機能ブロック説明

7.3 スイッチインタフェース

7.4 SWTIFインタフェース

7.5 BSGCSHの上位/下位シェルフ構成

7.6 BSGC−COMループバック構成

7.6.1 BSGC、BSGC−COMともINS 状態でのセルループバック

7.6.2 BSGC、BSGC−COMともOUS 状態でのセルループバック

8. 2重化制御

8.1 ハードウエア構成

8.1.1 BSGCハードウエア構成

8.1.2 BSGCハードウエアの概要説明

8.1.3 メモリマップ

8.1.4 I/Oマップ

9. 保守・運用

9.1 診断機能

9.1.1 診断対象項目

9.1.2 診断担当

9.1.2.1 INF インタフェース→BCPRアクセス リード/ライト診断

9.1.2.2 INF インタフェース→DMA 転送 リード/ライト診断

9.1.2.3 BSGC内機能診断

9.1.2.4 BSGCとBSGC−COM間診断

9.1.2.5 VCC メモリテスト

9.1.2.6 BSGC−他装置間LAP リンク確立テスト

9.2 TC 機能

9.2.1 基本方針

9.2.2 セル BY セル折り返しについて(OUS 状態)

9.2.3 セル BY セル折り返し位置

9.2.4 OUS 試験時におけるアクティブ系BSGCでのTCストップ 機能

<パート8> 本発明に特に関連する構成及び機能等

【0005】

【発明の実施の形態】

以下、図面を参照しながら本発明の実施例につき詳細に説明する。

<パート1>

パート1では、本実施例の全体的な構成及び機能について説明する。

1.本実施例が対象とするシステムの概観

1.1 概説

図1は、本実施例による広帯域交換システムの全体構成図である。本実施例では、広帯域ホスト交換機(HOST:Broadband Host Switch)1には、加入者端末装置が直接接続されるほか、広帯域遠隔回線集線装置(BRLC:Broadband Remote Line Concentrator) 2、広帯域遠隔交換装置(BRSU:Broadband Remote Switching Unit)3等が接続され、これらの装置に加入者宅内装置(CPE:Customer Premises Equipment) 4が接続される。このような構成により、経済的な広帯域交換システムを構築することが可能となっている。

1.2 本実施例が提供するインタフェース及びサービス

次に、本実施例が対象とする各種インタフェースについて列挙する。

1.2.1 加入者インタフェース(Subscriber Interfaces)

1.2.1.1 光ファイバインタフェース

・B−ISDN (広帯域サービス統合ディジタルネットワーク) のユーザネットワークインタフェース(UNI) を提供する156Mbps インタフェース。

・B−ISDNのUNI を提供する622Mbps インタフェース。

1.2.1.2 メタリックインタフェース

・SMDS(Switched Multi−Megabit Data Services)、フレームリレー、サーキットエミュレーション等の加入者ネットワークインタフェース(SNI) を提供する1.5Mbps インタフェース。

・B−ISDNのUNI 、及び、SMDS、フレームリレー、サーキットエミュレーション等のSNI を提供する45Mbpsインタフェース。

1.2.2 ネットワークインタフェース

・B−ISDNのネットワークノードインタフェース(NNI) を提供する622Mbps 光ファイバインタフェース。

・B−ISDNのNNI を提供する156Mbps 光ファイバインタフェース。

・B−ISDN、SMDS、フレームリレー等のNNI を提供する45Mbpsメタリックインタフェース。

・フレームリレーのNNI を提供する1.5Mbps メタリックインタフェース。

1.2.3 サービス

本実施例が対象とする広帯域交換システムは、以下に示されるようなサービスを提供することができる。

・コネクション型ATM 高速データサービス。

・スイッチトマルチメガビットデータサービス(SMDS)に基づくコネクションレス高速データサービス。

・フレームリレーサービス。

・サーキットエミュレーションサービス。

1.3 システム構成

次に、本実施例のシステム構成について説明する。

1.3.1 広帯域交換機アーキテクチャ

図2に、本実施例による広帯域交換システムのバリエーションを示す。

広帯域交換機の基本構成は、ATM 加入者スイッチ(ASSW)モジュールである。ASSWモジュールは、冗長構成を有する10Gbps (ギガビット/秒) のATM スイッチングモジュール構造、2重化構成の交換機プロセッサ、種々の加入者インタフェース装置及びネットワークインタフェース装置を含む。単一のASSWモジュールは、スタンドアローン広帯域交換機として配置することができる。

ATM インターコネクションスイッチ(AISW)は、単一のASSWの容量以上の大規模容量スイッチとして有用である。AISWは、より大規模な広帯域交換形態の要求に対して、統合されたASSW間接続形態を提供する。大規模なオフィスを構成するために、多くのASSWモジュールをAISWによって相互接続し、160Gbps に達する容量を実現することができる。多くのASSWモジュールがAISWにより相互接続される大規模な構成においては、完全なサービスを提供できる広帯域遠隔交換装置(BRSU)として機能させるために1つ以上のASSWを遠隔配置させることができる。

また、ASSWは、広帯域遠隔回線集線装置(BRLC)に対するホスト交換機として機能させることもできる。

1.3.2 スイッチトマルチメガビットデータサービス(SMDS)

図3に、本実施例が対象とする広帯域交換機でのSMDSの実現方式を示す。

加入者ネットワークインタフェース(SNI) としては、OC−3C 及びDS1/DS3 という大きく分けて2つのタイプのインタフェースを使用することができる。前者は156Mbps の光ファイバインタフェースであり、後者は1.5Mbps/45Mbpsのメタリックインタフェースである。光ファイバインタフェースは、加入者回線上に、SMDS加入者装置と他のB−ISDN装置を混在させることができる。メタリックインタフェースは、SMDS専用のインタフェースとして規定される。本実施例が対象とする広帯域交換システムは、SMDS加入者ネットワークインタフェースを直接に扱うことができる。

SMDSは、ATM に良く適合するが (SMDSのセルフォーマットはATM のそれに類似する) 、SMDSは、SMDSメッセージハンドラ(SMDS−MH) と呼ばれる特別なメッセージ処理装置を使用する。SMDS−MH は、アドレススクリーニング、メッセージルーティング、グループアドレッシング (ポイント対マルチポイント接続) 、不当メッセージチェック等の、様々なSMDS特有のサービスを提供する。SMDSは、コネクションレスサービスであるため、SMDS−MHは、メッセージ毎及びセル毎の様々なサービスを提供する。このサービスは高速性が特徴であるため、ほとんどのサービスは、ソフトウエアではなくハードウエアによって提供される。

2.本実施例が対象とするハードウエアの説明

2.1 スモールホスト用ATM ネットワーク

図4に、本実施例が対象とする広帯域交換システムの代表的なハードウエア構成を示す。この図は、スモールホスト用ATM ネットワークを対象とする。

2.1.1 ATM 加入者スイッチ(ASSW)

ASSWは、種々のタイプの加入者に対するポート (加入者インタフェース) と、ネットワークインタフェースを提供する。加入者インタフェースには、SMDSにおける加入者−ネットワークインタフェース(SNI) 、フレームリレーにおけるユーザ−ネットワークインタフェース(UNI) 、及びB−ISDN ATM UNIが含まれる。ネットワークインタフェースには、フレームリレー、SMDS、及びB−ISDNにおけるネットワーク−ネットワークインタフェース(NNI) と共に、SMDSにおけるインターエクスチェンジキャリアインタフェース(ICI) 及びインタースイッチングシステムインタフェース(ISSI)が含まれる。加入者インタフェースは、また、サーキットエミュレーションにも適用することができる。

図5に、ASSWにおけるポート構成を示す。

2.1.2 ASSWにおける加入者及びネットワークインタフェース

加入者・ネットワークインタフェースは、いくつかのタイプのシェルフとして構成され提供される。これらのシェルフには、ATM DS−1シェルフ(ADS1SH)、加入者インタフェースシェルフ(SIFSH) 、及びファイバインタフェースシェルフ(FIFSH)がある。

2.1.2.1 加入者インタフェースシェルフ(SIFSH)

図6に、加入者インタフェースシェルフ(SIFSH) の構成を示す。

加入者インタフェースシェルフ(SIFSH) は、必要な電源、共通カード、及び種々のタイプのDS3 又はOC−3C インタフェースカードを8枚まで装着するためのマウントスロットを提供する。これらのインタフェースカードには、ATM OC−3C カード群(OC3CPG)、ATM DS−3カード群(ADS3PG)、フレームリレーDS−3カード群(FDS3PG)、サーキットエミュレーションDS−3カード群(CDS3PG)、及びADS1SHインタフェースカード(ADSINF)などがある。ATM DS−3カードは、ATM とSMDSの両方のインタフェースを提供する。

ATM OC−3C カード群(OC3CPG)は、B−ISDN UNIに接続されるATM 機器から受信された情報に対するATM セル交換を提供する。

DS−3カード群の機能は、回線速度がDS−1レートではなくDS−3レートで提供されるという点を除いて、ADS1SHに装着されるDS−1カード群と同様である。

また、SIFSH は、ADS1SHインタフェースカード(ADSINF)を扱うこともできる。ADSINFカードの組 (1組は2カード) のそれぞれは、4シェルフのADS1SHをインタフェースする。1つのSIFSH あたりでは、16シェルフのADS1SHがインタフェースされる。それぞれのADS1SHは8個のDS−1ポートを扱うことができ、また、後述するように2つのSIFSH シェルフをデイジーチェーン接続させることができるため、1組 (1組は2シェルフ) のSIFSH が接続されるポートにおいて、256個のDS−1カードを扱うことができる。

2.1.2.2 ATM DS−1シェルフ(ADS1SH)

図7に、SIFSH に対するADS1SH接続を示す。

ATM DS−1シェルフ(ADS1SH)は、種々のDS−1インタフェースカードを収容する。これらのカードには、フレームリレーDS−1カード群(FDS1PG)、SMDS DS−1 カード群(SDS1PG)、及びサーキットエミュレーションDS−1カード群(CDS1PG)がある。

フレームリレーDS−1カード群は、長いフレームリレーメッセージの個々のATM セルへの分割機能、セル交換のための必要なタグと共に仮想呼識別子を付与する機能等を提供する。また、このカード群は、ATM スイッチからセルを受信し、それらのセルからフレームリレーフォーマットを組み立てする機能を提供する。この適応処理は、分割/組み立て機能と呼ばれる。この機能は、ATM セル交換技術をフレームリレートラヒックに適用することを可能にする。

SMDS DS−1 カード群は、同様の機能を提供する。この機能は、データをセルの大きさのデータユニット列として提供するものである。

サーキットエミュレーションDS−1カード群は、完全同期トラヒックであるチャネルから受信された情報を、連続したセルに格納する機能を提供する。この機能も、ATM ネットワーク内を交換してゆくことができるように、情報をATM セル列に分解する。また、サーキットエミュレーションカード群は、情報信号がATM ネットワークから離れる際に、信号タイミングを回復させる機能も提供する。

ADS1SHシェルフは、必要な電源、共通カード、及び3タイプのDS−1カードを8枚まで装着するためのマウントスロットを提供する。このシェルフの出力は、加入者インタフェースシェルフ(SIFSH) にマウントされているADS1SHインタフェースカード(ADSINF)に接続される (図7参照) 。

2.1.2.3 ファイバインタフェースシェルフ(FIFSH)

ファイバインタフェースシェルフ(FIFSH) は、必要な電源と、OC−12Cインタフェースを4枚までマウントするためのスロットを提供する。それぞれのインタフェースには、ATM OC−12Cカード群(OC12PG)、及びファイバインタフェースカード(FIFCPG)の組 (1組は2枚) がある。

2.1.3 ASSW ATMスイッチモジュール

ATM スイッチモジュールは、最大で 10Gbps(ギガビット/秒) の容量を有するものとして構成することができる。このモジュールは、16ポートまでのトラヒックの出入口を供給する。スイッチ構造は、上り用と下り用の2つの分離された部分として構成される。加入者・ネットワークポートからやってくるトラヒックは、上り方向トラヒックを提供するATM ネットワーク上の16個のポートに供給される。加入者・ネットワークポートへ戻ってゆくトラヒックは、下り方向トラヒックを提供するATM ネットワーク上の16個のポートから取り出される。そのようなトラヒックは、ASSWに接続される種々の加入者・ネットワークインタフェースに対して送受信される。いくつかのネットワークポートは、ネットワークにおける一般的なシグナリング処理及びSMDSのためのメッセージ処理を行うサービス装置により使用される。図8に、ASSWを中心とするネットワークの構成例を示す。

2.1.3.1 ATM スイッチングシェルフ (ASSWSH)

ATM スイッチングシェルフ (ASSWSH) は、ATM スイッチングネットワーク全体と関連する電源を収容する。このスイッチングネットワークは、10Gbpsを提供する4×4のノンブロッキングスイッチとして構成される。このスイッチングネットワーク上のそれぞれ2.5Gbps の容量を有する4つのポートのそれぞれは、4つの関連するセルルーティングを多重するためのマルチプレクサカードを有する。従って、1つのポート内の1つのセルルーティングの容量は、2.5Gbps/4=622Mbps となる。この結果、スイッチングネットワークには、全体として、それぞれ622Mbps の容量を有する16組の入力が供給されることになる。

ATM スイッチモジュールは、常に同じ4×4のサイズを有するように構成される。

4つのネットワークポートのそれぞれを接続するための1組のマルチプレクサカードは、独立の装置構成とされる。

また、ASSWSHは、2組の共通カードと、タイミング生成用の1組のセルクロックジェネレータカード(CELCLK)と、プロセッサ装置の接続用の1組のパラレルATM インタフェースカード(PIAINF)を含む。

2.1.3.2 デイジーチェーン構成

加入者/ネットワークインタフェースを供給する前述したシェルフ群は、ATM スイッチングネットワーク上の16個のポートのそれぞれに接続される1つのシェルフによって、そのATM スイッチングネットワークに接続することができる。その1つのシェルフが622bpsの容量を完全に供給していない場合には、そのシェルフを他のもう1つのシェルフとデイジーチェーンさせることができる。デイジーチェーンでは、第1番目のシェルフがスイッチポートに接続され、第2番目のシェルフが第1番目のシェルフに接続される。図5に示したように、2つのSIFSH をデイジーチェーンさせることができる。このような配置は、ATM スイッチングネットワークに対する16個のポートに32個までのシェルフを接続することを可能とする。

2.1.4 ASSWにおけるその他のATM ネットワークサポート装置及びテストセル生成方式

上りスイッチ部分からのトラヒックは、2通りの方法によって下りスイッチ部分に接続させることができる。即ち、この機能は、ループバック回路又はATM インターコネクションスイッチ(AISW)によって実現される。ループバック配置は、どのようなASSW内接続をもサポートする。一方、ASSW間接続は、AISWを介した接続によってサポートされる。

2.1.4.1 ループバック用加入者インタフェースシェルフ (SIFSH)

図9に、SIFSH におけるループバック構成を示す。

SIFSH は、上りネットワークからの8個までの156Mbps の出口を下りネットワークへの8個までの156Mbps の入口に接続するための8個までのループバックカードグループ(LOOPPGA) を含む。また、このシェルフは、上記ループバックカードのための電源を内蔵する。将来的には、622Mbps のループバックカードグループを利用することができる。このカードは、156Mbps 以上の帯域幅のサービスが導入された場合に必要となる。

2.1.4.2 テストセルジェネレータ用加入者インタフェースシェルフ

図10に、SIFSH に接続されるテストセルジェネレータの構成を示す。

図10に示されるように、SIFSH は、試験に使用されるテストセルジェネレータアダプタ(TCGADPs) を内蔵できる。このTCGADPs は、ASSWの出入口上に配置されるSIFSH に内蔵される。テストセルジェネレータ(TCG) は、図10に示されるように、テストセルジェネレータシェルフ(TCGSH) 内に配置される。

2.1.5 ASSWにおけるシグナリング装置

システム上の各ポート装置のシェルフは、対応するマイクロプロセッサを有している。広帯域シグナリングコントローラシェルフ (BSGCSH) は、ASSWの広帯域コールプロセッサ (BCPR) と上述の種々のポート用マイクロプロセッサの間のシグナリング、及びB−ISDN UNIシグナリングを、処理する。

図11に、BSGCSHの構成を示す。このシェルフは、必ず配置され、電源と、共通カードと、6枚までの広帯域シグナリングコントローラカードグループ (BSGCPGA)を内蔵する。BSGCSH内のBSGCは、INFA (周辺インタフェースタイプA)及びINFT (周辺インタフェースタイプT)を介して、BCPRが接続されるシステムバス(BCPR Bus)に接続される。

2.1.6 SMDSメッセージハンドラ

SMDSメッセージ処理装置は、2つの異なるタイプのものがある。1つは、加入者SNI ポートに対応するシグナリング要求を処理し、他の1つは、ICI 及びISSIトランクポートに対応するシグナリングを処理する。

2.1.6.1 加入者メッセージハンドラシェルフ (SBMESH)

加入者メッセージハンドラシェルフ (SBMESH) は、SMDS加入者SNI ポートからのメッセージを処理する。このシェルフは、何れかのSMDS加入者SNI がASSW又はそれに接続されるBRLC上のポートに存在するならば必ず、或いは、SMDSトラヒックが加入者側のターミナルアダプタが接続されるATM UNI 設備を介して転送されてくるような場合に、用意される。

各SBMESHシェルフは、そのシェルフの容量までDS−1設備とDS−3設備を混在させてサービスを提供することができる。また、そのシェルフは、102Mbps の情報レートを有するSMDS情報を処理する。この場合、DS−3に対する最大情報レートは34Mbpsであり、DS−1に対するそれは1.17Mbpsである。また、1つのシェルフは、32SNI までを処理することができる。この基準によれば、1つのシェルフは、3本のDS−3伝送路又は32本のDS−1伝送路までを処理することができる。これらの制限に加えて、スイッチングネットワークは、1ポートあたり622Mbps までのトラヒック容量に制限される。

本実施例におけるシステムは、スイッチングネットワークの入口に対して4個のSBMESHまでをデイジーチェーン接続することができる。もし、スイッチングネットワークにSMDS DS−1 伝送路のみが接続されていると仮定すると、4つのデイジーチェーン接続されたSBMESHが接続された1つのネットワークポートは、12本までのDS−3伝送路、又は128 本までのDS−1伝送路、或いはそれらの混在形態を扱うことができる。もし、ASSWにおけるSMDSポート (トラヒック) が単一のメッセージハンドラグループのキャパシティを超えた場合には、より多くのメッセージハンドリング装置を提供するために、他の1つ又は幾つかのポートを選択することができる。

2.1.6.2 ゲートウエイメッセージハンドラシェルフ (GWMESH)

ゲートウエイメッセージハンドラシェルフ (GWMESH) は、ASSW上のSMDS ICI及びISSIポートに対するメッセージ処理及びシグナリング機能を提供する。

各GWMESHには、上述したSBMESHに対するのと同じ制限がある。SMDS ICI又はISSIがDS−3フォーマットで実現され、フル容量で運用されている場合、GWMESHに対する事実上の制限は、3本のDS−3 ICI、ISSIである。SMDS ICI又はISSIがOC−3C をフルに利用する形態で実現されている場合、1つのメッセージハンドラシェルフは、単一のOC−3C専用に使用されなければならない。本実施例によるシステムでは、スイッチングネットワークへの同一の入口に、4つまでのGWMESHシェルフをデイジーチェーン接続させることができる。この場合でもまた、トラヒックが単一のメッセージハンドラグループのキャパシティを超えた場合には、他の1つ又は幾つかのポートを追加することができる。

SMDSに対する要求が小さいオフィスでは、シェルフ毎の制限を超えず、かつ全体のトラヒックが622Mbps を超えない限りにおいて、1つ以上のSBMESHと1つ以上のGWMESHをデイジーチェーン接続させることができる。このような技術的配置は、SMDS機能に対するポート使用率を最小化する上で有用である。

2.2 広帯域遠隔交換装置(BRSU)

図12に、BRSUの主なハードウエア構成要素を示す。BRSUの構成要素は、ホスト交換機内のASSWのそれと同じである。

2.3 広帯域遠隔回線集線装置 (BRLC)

図13に、BRLCの主なハードウエア構成要素を示す。

ASSWに対して遠隔の配置で加入者インタフェースを収容する必要がある場合、広帯域遠隔回線集線装置 (BRLC) を使用することができる。BRLCは、ASSWに対して遠隔に配置され、スイッチング機能を実行する。

BRLCは、本質的には、顧客群からのトラヒックを集線し、それをASSW (1つ以上のアンビリカルリンクによって接続されている) に配信する。

BRLCは、ASSWにおけるものと同様のタイプの加入者/ネットワーク接続入力ポートを有する。コールプロセッサは存在しないが、ポートとアンビリカルリンクとの間のネットワークを交換するある種の汎用的な装置を有している。

図14に、BRLCにおける接続構成を示す。

2.3.1 加入者入力ポート

種々の加入者インタフェースが、BRLCのポートに接続されている。これらのポートは、種々のタイプのシェルフ装置手段により実現されている。それらには、図14に示されるように、ASSWにおいて実現されているものと同様の、ATM DS1 シェルフ(ADS1SH)及び加入者インタフェースシェルフ(SIFSH) などが含まれる。BRLC全体の最大容量は622Mbps であるため、ファイバインタフェースシェルフ(FIFSH) はBRLCでは使用されない。

ATM DS1 シェルフ(ADS1SH)は、種々のタイプのDS−1インタフェースカードグループを収容する。これらには、フレームリレーDS−1カードグループ(FDS1PG)、SMDS DS−1 カードグループ(SDS1PG)、及びサーキットエミュレーションカードグループ(CDS1PG)が含まれる。ADS1SHについては、2.1.2.2で説明した。

加入者インタフェースシェルフ(SIFSH) は、種々のネットワークインタフェースカードを収容する。SIFSHは、ATM OC−3Cカードグループ、種々のDS−3カード、又はATM DS−1シェルフインタフェースカード(ADSINF)を収容できる。SIFSHについては、2.1.2.1で説明した。

2.3.2 アンビリカル装置

BRLCとそれに対するサーバであるASSWとの間のアンビリカルリンクは、ADS3PGAを使用するDS−3設備又はOC3PGAを使用するOC−3C設備として構成することができる。また、このアンビリカルリンクは、OC12PGAカードグループを使用した単一のOC−12C としても提供することができる。BRLCの容量は622Mbpsに制限されているため、アンビリカルリンクの最大構成は、1本のOC−12C 又は4本のOC−3Cである。DS−3を使った最大構成では、12組のDS−3設備が提供され、約622Mbps のトラヒックを処理できる。任意のBRLCからの全てのアンビリカルリンクは、同一のASSWに接続されなければならない。

DS−3又はOC−3カードが使用される場合、最小構成として、最初の4枚のカードをRMXSH の予約スロットにマウントすることができる。カードの枚数が4枚を超えた場合、更に8枚のカードをマウントできるSIFSHを追加することができる。もし、OC−12Cにおいて必要ならば、FIFSHシェルフを使用することができる。SIFSH及びFIFSHについては、既に説明した。

2.3.3 ネットワーク装置

BRLCは、スイッチングネットワーク或いはASSWを有しない。この結果、ネットワークスイッチングシェルフ及び同期化シェルフは必要とされない。しかし、加入者ポート及びアンビリカルリンクを供給する種々のシェルフ装置は、ネットワーク装置にインタフェースされる必要があり、また、それらのシェルフ装置はネットワーク装置の所定の機能を要求する。このようなことから、BRLCは、ネットワークの代わりに機能するシェルフ装置を必要とする。この機能は、RMXSH シェルフによって実現される。

遠隔多重シェルフ(RMXSH) は、ネットワーク代用機能及び多重装置としての機能を提供する。このシェルフは、加入者インタフェースからのATM セルを受信して、提供されている種々のアンビリカルリンクに多重する。このシェルフは、また、多重機能に対するタイミングを確立しそれに基づく処理を実行する。

RMXSH シェルフは、その機能を実現するために、クロック回路と多重装置を有する。そして、このシェルフは、電源と共に、1組の遠隔多重タイミングジェネレータカードグループ(RMXTPG)、1組の遠隔多重ハイウエイカードグループ(RMXHPG)、及び1組の遠隔多重コントローラカードグループ(RMXCPG)を常に装備している。

3.本実施例で実現される機能

3.1 概説

この章では、本実施例が対象とする広帯域交換システムの構成要素について説明する。これらの構成要素は、以下の4つのカテゴリに分類される。

・ホスト交換機

・広帯域遠隔交換装置(BRSU)

・広帯域遠隔集線装置(BRLC)

・加入者宅内装置

3.2 ホスト交換機

ホスト交換機は、以下のような構成要素から構成される。

・ATM 加入者スイッチ(ASSW)

・ATM インターコネクションスイッチ(AISW)

・広帯域メインプロセッサ(BMPR)

・メンテナンス/オペレーションサブシステム(MOS)

・光リングバス

ホスト交換機は、更に以下の2つのタイプに分類される。

・スモールホスト交換機

・ラージホスト交換機

図15に、スモールホスト交換機とラージホスト交換機の構成を示す。ASSWが構成の基本となる。スモールホスト交換機は、1つのASSW、BMPR、及びMOS から構成される。ラージホスト交換機は、複数のASSWと、1つのAISWと、1つのBMPRと、1つのMOS から構成される。ラージホスト交換機において、AISWは複数のASSW間を接続する。スモールホスト交換機からラージホスト交換機への移行は、サービスを中断させることなく行うことができる。

光リングバスは、広帯域交換システム及び狭帯域交換システムが1つのシステムに統合される場合に使用される。

なお、本実施例は、主にスモールホスト交換機を対象として説明している。

3.3 ATM 加入者スイッチ (ASSW)

ATM 加入者スイッチ(ASSW)は、広帯域交換システムにおける基本的な構成要素である。図16に、ASSWの構成を示す。ASSWは、10Gbpsの容量のスループットを有し、以下の構成要素から構成される。

・ATM スイッチモジュール(ASM)

・加入者/ネットワークインタフェース

・広帯域シグナリングコントローラ(BSGC)

・SMDSメッセージハンドラ(SMDS−MH)

・広帯域コールプロセッサ(BCPR)

3.3.1 ATM スイッチモジュール(ASM)

広帯域交換機におけるATM スイッチモジュール(ASM) は、シングルステージ又はマルチステージのセルフルーティングモジュール(SRM) によって構成されている。SRMは、2.5Gbpsのリンクスピードを有するN×Nのスイッチングマトリックスにより構成される。図17に、SRM の原理を示す。SRM に流入されたATM セルは、各セルに付加されているタグに従って出力ポートへルーティングされる。

図18に、ASSWにおいて使用される4×4のSRM の構成を示す。4×4のSRM において、セルは、4つの入力ポートと4つの出力ポートとの間で交換される。SRMは、特別に設計されたバイポーラCMOS大規模集積回路(VLSI)によって構成される。このSRM は、2×2のスイッチマトリックスを含む。それぞれのクロスポイントは、2.5Gbpsのスイッチング容量を有する。

セルスイッチングの原理は次の通りである。ここでは、入力ハイウエイHW0 から出力ハイウエイHW2 へのセルスイッチングを例として説明する。

まず、各セルには、タグが付加されている。

例えば、HW0 から入力されたセルには、タグ2が付加されると仮定する。それぞれのスイッチングエレメントは、タグ値をチェックし、出力ポート番号に等しいタグを有するセルのみをスイッチする。図18の例では、スイッチングエレメントSW02が該当する。もし、複数のセルが1つの出力ポートに出力される場合には、アクセス制御機構が、各クロスポイント内のバッファを用いることにより、セルの競合を回避する。

図19に、仮想チャネル識別子コンバータ(VCC) の位置を示す。タグは、加入者/ネットワークインタフェースなどの周辺装置に配置されているVCC により、セルに付加される。VCC は、各セルのためのタグ値を特定する。タグ値は、呼接続における呼設定フェーズ又は半固定接続の設定フェーズにおいて処理されるソフトウエアテーブルに従って設定される。

タグ情報は、デマルチプレクサにおいても使用される。タグは、ATM スイッチモジュール及び周辺装置内のデマルチプレクサの出力ポートを特定する。

図20に、ASSWのATM スイッチモジュールの構成を示す。ASSWのATM スイッチモジュールは、上り用と下り用の2つに分離された各4×4のSRM により構成される。加入者/ネットワークインタフェース、広帯域シグナリングコントローラ(BSGC)、SMDSメッセージハンドラ(SMDS−MH) などの周辺装置インタフェースは、622Mbps の容量を有する。全ての加入者/ネットワークインタフェースは、ATM スイッチモジュールの一方の側に集合させられる。ATM スイッチモジュールの他方の側には、ASSW内トラヒックをルーティングするループバックリンクが配置される。AISWが使用されるラージホスト交換機においては、AISWのインタフェースがループバックリンクに置き換えられる。

3.3.2 加入者/ネットワークインタフェース

図21に、本実施例の加入者インタフェース(SNI )/ネットワークインタフェース(ICI/ISSI)を説明する構成図を示す。同図に示すように、加入者インタフェース/ネットワークインタフェースとして以下の3つの速度を提供する。

・高速:622 Mbps光インタフェース

・中速:156 Mbps光インタフェース,45 Mbps メタルインタフェース

・低速:1.5 Mbpsメタルインタフェース

上記3つの速度のインタフェースに対しては、それぞれ異なったシェルフが使用される。低速インタフェースの信号は、いったん8 Mbpsリンクに多重化された後に、中速インタフェースのシェルフに収容される。中速インタフェースのシェルフは、輻輳を考慮し、2シェルフまでイモヅル式に接続することができる。加入者インタフェースとネットワーク・インタフェースは共通であり、それら2つのシェルフを同一シェルフで構成できる。ただし、これらのシェルフはトラフィック集中が起こるので、加入者側とネットワーク側で異なるグレイドのサービスを要求するのであれば、それらシェルフを分離する必要がある。

加入者インタフェース/ネットワークインタフェースとしては、以下の4つのタイプに分類することができる。

・B−ISDN(ATM)

・SMDS

・フレーム・リレー

・サーキット・エミュレーション

上記各サービスに対して異なるインタフェース・カードが使用されるが、シェルフは共通とすることができる。これらインタフェース・カードは、サーキット・エミュレーションを除いて、加入者側とネットワーク側で異なる。

3.3.3 広帯域シグナリング・コントローラ(BSGC)

BSGC(Broadband Signaling Controller)はATM インタフェースとのHDLC(HighLevel Data Link Procedure)ハンドラである。図22はASSW内におけるBSGCの位置を示す図である。BSGCは、INF (Interface)経由でBCPR(Broadband Call Processor)によって制御され、B−ISDN UNIおよびB−ISDN NNIのためのLAPD(Link Access Procesure D−channel)もしくはCCS7シグナリングを提供する。BSGCは、BCPRとBRLC(Broadband Remote Line Concentrator)との間の通信と行うとともに、BCPRとSNI インタフェース装置との間の内部通信も行う。

3.3.4 メッセージ・ハンドラ(SMDS)

SMDS−MH (SMDSメッセージ・ハンドラ)は、アドレス・スクリーニング、メッセージ・ルーティング、グループ・アドレス処理(ポイント・トゥ・ポイント通信)、異常メッセージチェック、課金処理、データ・コレクション等のSMDS対応機能を提供する。図23は、ASSW内におけるSMDS−MH の位置を示した図である。この実施例では、SMDS−MH として、以下の2つのタイプを示す。

・SBMH(Subscriber Message Handle :加入者メッセージ・ハンドラ)

・GWMH(Gateway Message Handle :ゲートウェイ・メッセージ・ハンドラ)

SBMHは、SNI のためのメッセージ処理を行う。一方、GWMHは、ICI やISSIなどのスイッチ間インタフェースのためのメッセージ処理を行う。

3.3.5 広帯域コール・プロセッサ(BCPR)

図24にBCPR(Broadband Call Proseccor)の構成を示す。BCPRは、全てのSNIのための呼制御を行う。BCPRは、以下の各ユニットを含む。

・CPU

・メインメモリ

・イーサネット・インタフェース

・INF

イーサネット・インタフェースは、スモールホスト交換機内において、BCPRとBMPR(Broadband Main Processor)との間の通信に使用される。INF は、ATM スイッチモジュール、BSGC、SMDS−MH 等の各種ASSW内の装置とBCPRとの間のインタフェースを提供する。

3.3.6 メンテナンス・アンド・オペレーション・システム(MOS )

MOS(Maintenance and Operation System) は、各種メンテナンス及びオペレーションを行う。図25にMOS の構成を示す。MOS は以下の各ユニットを含む。

・アラーム・パネル・ユニット

・アラーム・コントロール・ユニット

・オペレーション・アンド・メンテナンス・プロセッサ

広帯域スイッチのみのシステムでは、MOS は、イーサネット・インタフェースを介して直接BMPRに接続され、BMPRとの連携動作によってオペレーションおよびメンテナンス機能を提供する。狭帯域および広帯域スイッチからなるシステムでは、MOS は、狭帯域および広帯域スイッチング・システムに光リング・バスで接続され、広帯域システム用BMPRおよび狭帯域システム用メイン・プロセッサとの連携動作によってオペレーションおよびメンテナンス機能を提供する。

3.3.7 オペレーション・アンド・メンテナンス・プロセッサ(OMP )

OMP(Operation and Maintenance Processor)は、本実施例のフロントエンド・プロセッサである。OMP は、システム管理・制御、およびラインやトランクの試験に加えて、本システムに複数のOSを接続する。OMP のハードウェア構成(図26参照)を以下に示す。

・CPU (メモリを含む)、ディスクドライブ、フロッピ・ディスクドライブ

・CRT ディスプレイ(GUI 使用)

・キーボード

・マウス

・ハードディスク

・カートリッジテープドライブ

・非同期通信サーバ

・プリンター

・X.25インタフェース

3.3.8 システム・インテグレーション・プロセッサ(SIP )

SIP(System Integration Processor) は、OMP を光リングバスに接続する場合に使われる。1つのOMP がSIP を介して光リングバスに接続されると、他のアプリケーション(狭帯域、広帯域、その他)で処理可能となる。

3.4 広帯域遠隔集線装置(BRLC)

BRLC(Broadband Remote Line Concentrator)の構成を図27に示す。BRLCは、ホスト交換機から遠隔地に加入者インタフェースを提供する。BRLCは、トラフィック集線を行うが、遠隔地での交換は行わない。オペレーション及びメンテナンス機能は、基本的にはホスト交換機から提供される。ネットワーク・インタフェースは、ホスト交換機とのアンビリカルからなる。このアンビリカルが切れた場合、BRLCは、スタンドアロンとして動作することはできない。

3.5 広帯域遠隔交換装置(BRSU)

BRSU(Broadband Remote Switching Unit) の構成を図28に示す。BRSUは、ホスト交換機からの遠隔地において、加入者インタフェース、ネットワーク・インタフェース、交換機能を提供する。BRSUは、AISWか設けられたラージ・ホスト交換機から制御される。オペレーションおよびメンテナンス機能は、基本的にはホスト交換機から提供されれるが、一部機能はBRSU自身が有する。BRSUは、ホスト交換機と同じ加入者インタフェース/ネットワークインタフェースを提供する。ホスト交換機とのアンビリカルは、BRLCの場合のそれと類似するが、BRSUでは、もしそのアンビリカルが切断された場合でもスタンドアロンとして動作し、スイッチ間サービスを提供しつづけることができる。

3.6 SMDSの実施態様

SMDSは、コネクションレス高速パケットデータサービスである。SMDSに関する装置を図29に示す。SMDSのトラフィックは、DS1/DS3 インタフェース部とSMDSメッセージ・ハンドラ部で処理される。

・DS1/DS3 インタフェース部

・加入者インタフェース/ネットワークインタフェースのレベル1(物理レイヤ)の終端

・SNI level−2 のATM レイヤの終端

・パフォーマンス・モニタ

・メッセージ・ハンドラ

・SNI level−2 のSAR の終端

・SNI level−3 機能(フォーマット・チェック、アドレス・スクリーニング、ルーティング、フロー制御)

・データ・コレクション(ネットワーク・トラフィック管理、ネットワーク・データコレクション、課金)

SMDSは、ターミナル・アダプタを介して、B−ISDN(ATM) 加入者インタフェースを用いて構成することができる。この場合、DS1/DS3 インタフェースをターミナル・アダプタで提供する。

レイヤ構造のSNI のプロトコルを図30に示す。また、SMDSは、図31に示すレイヤ構成を採用している。さらに、図32に、SMDSシステムにおけるセルのルーティングを示す。

フロー制御は、以下の2ヵ所で実行される。

・DS1/DS3 インタフェース部でのユーザ・パラメータ・コントロール(UPC)

・GWMHでのトラフィック・シェイピング

3.7 トラフィック管理

トラフィック管理は、以下のメカニズムによって実現される。

・呼受付制御

・使用量制御

・セル・ルーティングの優先度

3.7.1 呼受付制御

サービスの要求品質(たとえば、セル廃棄率やセル伝送遅延)を保証するために、システムは帯域を管理し、呼の受け付け時点で各呼ごとに要求された帯域が守られているこチェックする。呼に対する処理は、ピーク値、平均値、およびサービスの要求品質等に従って実行する。

システム内での帯域は、以下の3地点で仮想パス(Virtual Path)ごとに管理される。

・加入者インタフェース

・ネットワーク・インタフェース

・システム内の622 Mbps

上記仮想パスの容量は、以下の2点で管理される。

・各呼のクラスの帯域(W1):各呼のクラスに対して割り当てられ、管理される帯域

・共通帯域(W2):呼のクラスとは無関係に割り当てられ、管理される帯域

なお、W2領域は、W1からオーバーフローした呼、W1において設定されていない呼によって利用される。

3.7.2 ユーザ・パラメータ・コントロール(UPC )

UPC(User Parameter Control) は、各呼の実際のトラフィックを管理する。上記設定値を越えた呼が検出された場合には、システムは、その呼のセルを廃棄するか、そのセルに対して設定値を越えたことを示すタグを付与する。

UPC は、仮想チャネル(VC)、仮想パス、またはそれら両者に対して実行される。加入者線に対しては、UPC は加入者インタフェース部において仮想チャネル毎に行われる。上記設定値を越えたセルに対しては、以下の処理がなされる。

・B−ISDN:廃棄または設定値を越えたことを示すタグの付与

・SMDS :廃棄

ネットワーク側(たとえば、他の交換機やBRSU/BRLC とのインタフェース)では、ネットワーク・インタフェース部において、各仮想パス(または仮想チャネル)ごとに実行される。

3.7.3 セル・ルーティングの優先度

セル・ルーティングの優先度の制御は、システム内のMUX/DMUX部およびATM スイッチにおけるバッファで行われる。その制御は、以下に示す2つのスレッシュホルド値を用いてキュー(待ち行列)で実現される。

・重要でない加入者セルを廃棄するためのスレッシュホルド値

・CLP(cell loss priority) =1のセルを廃棄に関するスレッシュホルド値

3.8 データ・コレクション

本実施例のシステムでは、以下のデータを収集する。

・AMA (Automatic Message Accounting)データ

・パフォーマンス・モニタリング・データ

・ネットワーク・トラフィック管理データ

・NDC (ネットワーク・データ・コレクション)データ

AMA データは、例えば、BMPRまたはSIP の記憶装置に格納され、OSに転送される。

パフォーマンス・モニタリング・データは、15分間隔または24時間間隔で収集される。このデータは、BMPRの記憶装置に格納され、OSから要求があった場合に、OMP を介してOSに転送される。

ネットワーク・トラフィック管理データは、輻輳の検出・通知のためにに使用され、その輻輳レベルが所定のスレッシュホルド・レベルを越えたときに収集される。また、所定間隔(5分)での収集も行われ、OMP を介してリアルタイムでOSに転送される。

NDC データは、長期的な予測のために使用される。このデータは、OSからの要求があったときに、OMP を介してBMPRの記憶装置に格納される。

4.その他

以上説明した本実施例の全体構成のうち、例えば図8に示されるDS3−SMDSインタフェース(DS3) 、SIFSH 、ASSWSH、SBMESH、GWMESH、及びBSGCSHの詳細について、以下のパート2〜7で説明する。その後に、パート8において、本発明に特に関連する構成及び機能等について説明する。なお、DS1−SMDSインタフェース(DS1) については、伝送速度が異なるだけで、基本的な機能はDS3−SMDSインタフェースと同様であるため、その詳細については省略する。

【0006】

<パート2>

パート2では、DS3−SMDSインタフェースの詳細について説明する。

1.概略説明

DS3−SMDSインタフェースは、DS3 伝送路を使用してSMDSサービスを行うための回線インタフェースとして使用される。また、DS3−SMDSインタフェースは、BRLC(Broadband Remote Line Concentrator:広帯域遠隔回線集線装置) を接続してアンビリカルリンクを実現するためのインタフェースとして使用される。

SMDS(Switched Megabit Data Service) とは、高速のコネクションレスデータサービスの一種であり、LAN とLAN とを接続してデータを交換するサービスとして機能することを期待されている。

図33は、DS3−SMDSインタフェースを中心としたシステム構成の概略を示す図である。また、図34は、交換機1にBRLC2が接続される構成を示した図である。

図33に示されるDS3−SMDSインタフェース1、3は、SIFSH(Subscriber Interface Shelf) 6に搭載される。また、図34に示されるDS3−SMDSインタフェース3 (図ではDS3−ATM と記載されている) は、交換機1内のSIFSH 7又はBRLC2内のRMXSH(Remote Multiplexer Shelf) 7に搭載される。DS3−SMDSインタフェースは、それがSIFSH に搭載される場合、最大で8リンク分までSIFSH に搭載することができる。SIFSH は、ATM スイッチとのインタフェース部分である2重化された構成を有する共通部(SIFSH−COM or SIFSH Common) と、1重化された構成を有する回線個別部より構成される。DS3−SMDSインタフェースは、回線個別部に搭載される。また、SIFSH は、最大で2シェルフまでカスケードに接続され、4:1の集線化を行う。

図33において、DS3−SMDSインタフェース1は、SMDSサービスを提供するためのDS3 伝送路2上のDS3 レイヤーを終端し、DS3 伝送路2から入力されるDS3 フレームのインフォメーションペイロード部に収容されているPLCPレイヤーのフレームを取り出す。そして、DS3−SMDSインタフェース1は、取り出したPLCPレイヤーのフレームからL2プロトコルデータユニット(L2−PDU)を抜き出し、L2−PDUヘッダのHCS(HEC)チェックを行った後、53オクテットのL2−PDRU からATM スイッチ5内で処理可能な54オクテットのATM セルへの変換(53/54オクテット変換) を行い、そのATM セルを、622Mbps(メガビット/秒) の伝送速度を有する高速上りハイウエイ(Upward Highway)に多重して、ATM スイッチ3に送出する。

逆に、DS3−SMDSインタフェース1は、ATM スイッチ3から伸びている高速下りハイウエイ(Downward Highway)から分離したATM セルから、上述した手順と逆の手順によりDS3 フレームを組み立て、それをDS3 伝送路2に送出する。

一方、図34に示されるように、DS3 伝送路4にBRLC(Broadband Remote Line Concentrator:広帯域遠隔回線集線装置) が接続される場合には、DS3−SMDSインタフェース3は、アンビリカルリンクを実現する。この場合、図34において、交換機1内のDS3−SMDSインタフェース3は、DS3 伝送路4によってBRLC2内のDS3−SMDSインタフェース5と接続される。

2.回線インタフェースの説明

2.1 DS3 回線インタフェース

2.1.1 ペイロードマッピング

DS3 回線インタフェースにおいて、ATM スイッチ側のデータフォーマットであるATM セルと伝送路側のデータフォーマットであるDS3 フォーマットとの間のマッピングを、図35に示す。

2.1.2 DS3 フレームフォーマット

図33において、DS3−SMDSインタフェース1は、伝送路2上のフレームフォーマットである図35に示される非同期DS3 フレームフォーマット(Asynchronous DS3 FRAME FORMAT)(M13 Format) を終端する。このフレームフォーマットの更に詳細な構成を、図36に示す。

1つのマルチフレーム(Multiframe)は、7つのサブフレーム(Subframe)によって構成される。1つのサブフレームは更に、それぞれ85ビットからなる8個のブロックによって構成される。1つのブロック内の85ビットのうち、最初の1ビットはDS3 オーバーヘッド部であり、残りの84ビットが情報ペイロード部(INFO.PAYLOAD)である。

DS3 回線インタフェースにおいては、44.736MHz のビットレートで、1つのマルチフレームが、106.4 μsec(マイクロ秒) の周期で伝送される。

3.PLCPフレームフォーマット

3.1 DS3 PLCPフレームフォーマット

図37に、図35に示されるPLCPレイヤ(PLCP LAYER)に対応するDS3 PLCPフレームのフォーマットを示す。DS3 PLCPフレームは、図35に示される非同期DS3 フレームフォーマットにおけるサブフレーム内のインフォメーションペイロード(INFO.PAYLOAD)を使って伝送される。この場合、フレーム内の各オクテット(octets)は、4ビットからなるニブル(nibble)という単位で、順に伝送される。なお、図35に示されるDS3 フレームフォーマットのマルチフレーム又はサブフレームの先頭とDS3 PLCPフレームの先頭は、同期している必要はない。

4.DS3−SMDSインタフェース L2−PDUフォーマット

4.1 DS3−SMDS L2−PDU フォーマット

図38に、図35又は図37のPLCPフレームに挿入されるDS3−SMDS L2−PDU(L2 Protocol Data Unit)のフォーマットを示す。図38又は図35に示されるように、DS3−SMDS L2−PDU は、7オクテット(octets)のヘッダ(HEADER)と、44オクテットのインフォメーションフィールド(INFO.FIELD)、及び2オクテットのトレーラ部(TRAILER) によって構成されている。

まず、図38のヘッダ(HEADER)内のアクセスコントロールフィールド(Access Control 、又は図35のACF)は、DS3−SMDSインタフェースが終端する伝送路上におけるL2−PDUの伝送状態を検出するために使用される。DS3−SMDSインタフェースが終端する伝送路が、SNI(加入者−ネットワークインタフェース。例えば図33の伝送路2) である場合と、NNI(ネットワーク−ノードインタフェース。例えば図33の伝送路4) である場合のそれぞれ、並びに上り伝送路及び下り伝送路のそれぞれにおけるアクセスコントロールフィールドの内容を、図39に示す。

図39において、DS3−SMDSインタフェースが終端する伝送路がSNI である場合には、BUSYビットは、そのビットが含まれるL2−PDUが情報を含んでいるか否かを示す。また、DS3−SMDSインタフェースが終端する伝送路がSNI で、かつその伝送路が上り伝送路(ATMスイッチ側に入力する伝送路) である場合には、REQ0、REQ1、REQ2の各ビットは優先レベルを示す。一方、DS3−SMDSインタフェースが終端する伝送路がNNI である場合には、BUSYビットは、そのビットが含まれるL2−PDUが有効なセルであるか否かを示す。

4.2 ネットワークコントロールインフォメーション

図38に示されるヘッダ部内のネットワークコントロールインフォメーションフィールド(NETWORK CONTROL INFO 又は図35のNCI)は、32ビットのデータであって、図40に示されるように、20ビットのVCI 、2ビットのPT、2ビットのSP、及び8ビットのHCS によって構成される。図40に示されるように、VCI(Virtual Channel Identifier) は、L2−PDU内に情報が有る場合には全て“1”であり、そうでない場合には全て“0”である。PT(Payload Type)及びSP(Segment Priority)は、DS3−SMDS SNI(Subscriber Network Interface)において将来使用されるデータであり、現在は共に“00”である。

HCS(Header Check Sequence)は、ネットワークコントロールインフォメーションフィールド内のVCI 、PT、SPからなる3オクテットのデータ部に対する生成多項式(G(x)= X8 +X2 +X+1) を用いた計算によって得られる値である。この値を用いることにより、ネットワークコントロールインフォメーションフィールドのエラーチェックが行われる。VCI 、PT、SPからなる3オクテットは、図40に示されるように2種類の固定値を採るだけである。従って、HCS は、L2−PDU内に情報が有る場合は“00100010”の値を採り、そうでない合は“00000000”の値をとる。

4.3 セグメントタイプ

図38に示されるヘッダ部内のセグメントタイプ(SEGMENT TYPE 、又は図35のSEGT) の組合せを図41に示す。L2−PDUの種類が、COM(CONTINUATION MESSAGE) であるか、EOM(END OF MESSAGE) であるか、BOM(BEGINNING OF MESSAGE) であるか、SSM(SINGLE SEGMENT MESSAGE) であるかによって、セグメントタイプは、“00”、“01”、“10”、“11”の何れかの2ビットの値を採る。

4.4 メッセージ識別子

図38に示されるヘッダ部内のメッセージ識別子(MESSAGE IDENTIFIER 、又は図35のMID)はL3−PDUに関連するデータである。これについては、後述する。

4.5 セグメンテーションユニット

図38において、インフォメーションフィールド(INFO.FIELD)であるセグメンテーションユニット(SEGMENTATION UNIT、又は図35のSEG.UNIT) には、SMDSサービスにおけるL3−PDU(L3 プロトコルデータユニット) が格納される (後述する図42参照) 。

4.6 ペイロードレングス

図38に示されるトレーラ部(TRAILER) 内のペイロードレングス(PAYLOAD LENGTH 、又は図35のPLEN)には、上記セグメンテーションユニットに含まれる有効データの長さが格納される。L2−PDUがBOM 又はCOM である場合はPAYLOAD LENGTH = 44 であり、L2−PDUがEOM 又はSSM である場合はPAYLOAD LENGTH≦44であり、L2−PDUに情報が含まれていない場合は、PAYLOAD LENGTH = 00 となる。

4.7 ペイロードCRC

図38に示されるペイロードCRC(PAYLOAD CRC 又は図35のPCRC) は、図5に示されるSEGMENT TYPE 、MESSAGE IDENTIFIER 、SEGMENTATION UNIT 、PAYLOAD LENGTH、及びPAYLOAD CRC からなる48オクテットのデータ部に対する生成多項式( G(x)=X10+X9 +X5 +X4 +X+1) を用いた計算によって得られる値である。この値を用いることにより、上記48オクテットのデータ部のエラーチェックが行われる。なお、L2−PDUに情報がない場合には、PAYLOAD CRC =00 である。

5.L2−PDUとATM セルとの関係

図33に示されるDS3−SMDSインタフェース1は、4.2 において説明したように、伝送路2から入力されたL2−PDUのヘッダに対してHCS(HEC)チェックを実行した後、53オクテットのL2−PDRU からATM スイッチ5内で処理可能な54オクテットのATM セルへの変換を行う。この場合、図35に示されるように、L2−PDUのヘッダ部に含まれるセグメントタイプ(SEGT)とメッセージ識別子(MID) 、並びに、L2−PDUのペイロード部に含まれるセグメンテーションユニット(SEG.UNIT)、ペイロードレングス(PLEN)、及びペイロードCRC(PCRC) が、ATM セルのペイロード部(ATM CELL PAYLOAD)に格納される。また、L2−PDUのヘッダ部内のネットワークコントロールインフォメーションフィールド(NCI) に含まれる全てのビット (20ビット) が“1”であるVCI は、DS3−SMDSインタフェースとSIFSH Commonとのインタフェースとして規定される値:VPI=3F,VCI=03FFに変換されて、そのVPI/VCI がATM セルのヘッダ部に付加される。

以上説明したようにして、図33のDS3−SMDSインタフェースは、伝送路1上のDS3 フォーマットと、SIFSH 6内の共通部(COM) で処理可能なATM セルフォーマットとの間で、相互に変換を行う。この場合、SMDSサービスにおけるユーザデータを伝送するL3−PDU(L3 プロトコルデータユニット) は、上記両フォーマットを用いて伝送されるL2−PDUのペイロード部内のセグメンテーションユニットに格納されて伝送される。

即ち、図42に示されるように、DS3 伝送路を使って通信を行う送信側ユーザ端末においては、まず、通信データ (ユーザデータ) が、SMDSサービスにおいて規定されるL3−PDUのペイロード部に格納される。次に、送信側ユーザ端末においては、L3−PDUが、それぞれ44オクテットからなる1つ又は複数のセグメントに分割される。次に、その1つ又は複数のセグメントのそれぞれが各ペイロード部内のセグメンテーションユニットに格納された1つ又は複数のL2−PDUが組み立てられる。この場合、1つのL3−PDUから生成される1つ又は複数のL2−PDUには、同じ値を有するMID(Message Identifier, or Multiplexing Identification) と呼ばれる識別子 (図35、図38参照) が付与される。これは、SMDSサービスを提供するための後述するSBMESH(Subscriber Message Handler Shelf,図8参照) が、L3−PDUを認識することはせずにL2−PDUのヘッダ部のみをリアルタイムで認識してSMDSのデータを処理するために、必要な情報である。なお、ユーザは、1つのSNI(Subscriber Network Interface) 上において、同時に16種類のMID値を使用することができる。即ち、ユーザは、1つのSNI 上で同時に16種類のSMDSメッセージを通信することができる。続いて、送信側ユーザ端末においては、L2−PDUからPLCPフレームが組み立てられ、更にDS3 フレームのサブフレームが組み立てられ、最後にDS3 フレームのマルチフレームが組み立てられる (図35参照) 。このようにして送信側ユーザ端末で組み立てられたDS3 フレームが、DS3 伝送路に送出される。そして、DS3−SMDSインタフェースは、前述のようにして、DS3 フレームからPLCPフレームを抽出し、PLCPフレームからL2−PDUを抽出し、L2−PDUをATM セルに変換して、SIFSH Commonに送出する。このように、DS3−SMDSインタフェースは、SMDSサービスにおけるL3−PDUは一切認識する必要はない。

SIFSH Commonは、DS3−SMDSインタフェースから入力されたペイロード部にSMDSサービスのL2−PDUを含むATM セルのヘッダ部に付加されているVPI/VCI の値を、DS3−SMDSインタフェースで付加された値:VPI=3F,VCI=03FFから、SIFSH CommonとSBMESH (図8参照) の間に張られるPVC(Permanent Virtual Circuit:相手固定接続) を特定すると同時に、そのATM セルを送出したDS3−SMDSインタフェースが終端するDS3 伝送路であるSNI を特定するVPI/VCI の値に、付け替える。従って、SIFSH CommonとSBMESHの間に張られるPVC には、そのSIFSH Commonに接続されSMDSサービスに使用されるDS3−SMDSインタフェースを始めとする個別部が終端するSNI の数に対応する数のVPI/VCI の値が割り当てられることになる。また、SIFSH Commonは、そのATM セルの先頭に、そのATM セルがATM スイッチ内で自律的にスイッチングされてSBMESHに転送されるようにするための、タグを付加する。

ATM スイッチ(ASSWSH)に接続されSMDSサービスを提供する後述するSBMESH (図8参照) 等は、ATM スイッチから入力されるのATM セルのうち、ヘッダ部にSMDSサービスに使用されるPVC に対応する特定のVPI/VCI 値が付加されているATM セルを受信し、図42に示されるように、そのATM セルのペイロード部に格納されているL2−PDUを処理する。なお、ATM セルは、レイヤ2(L2)内のATM レイヤのプロトコル階層を有し、L2−PDUはレイヤ2(L2)のAAL(ATM Adaptation Layer) 内のSAR(Segmentation and Reassembly Sublayer) のプロトコル階層を有する。この場合、パート5等において後述するように、SBMESH等は、レイヤ3(L3)のプロトコル階層を有し、SMDSサービスにおけるユーザ情報(User data) が実際に格納されて伝送されるL3−PDU (図42) を認識することはせずに、ATM セルのヘッダ部及びL2−PDUのヘッダ部のみをリアルタイムで認識してSMDSのデータを処理する。具体的には、SBMESHは、ATM セルのヘッダ部に付与されているVPI/VCI の値によって判別されるSNI が同じで、かつL2−PDUのヘッダ部に付与されているMID の値が同じL2−PDUを、同じL3−PDUを転送するデータとして処理する。この結果、ATM 方式が有するリアルタイム性という特徴を損なわずにコネクションレスサービスであるSMDS サービスを提供することが可能となる。

一方、DS3 伝送路を使って通信を行う受信側ユーザ端末では、まず、DS3 伝送路から受信されたDS3 フレームからPLCPフレームが抽出され、PLCPフレームからL2−PDUが抽出される。そして、L2−PDUのペイロード部内のセグメンテーションユニットの内容が抽出され、L2−PDUのヘッダ部に付加されているMID に基づいてL3−PDUが組み立てられる。最後に、そのL3−PDUのペイロード部から通信データ (ユーザデータ) が抽出される。

6.DS3 アンビリカルリンクフォーマット

図34に示されるように、DS3 伝送路4にBRLC(Broadband Remote Line Concentrator:広帯域遠隔回線集線装置) が接続される場合には、DS3−SMDSインタフェース3は、アンビリカルリンクを実現する。

この場合、伝送路4上のデータは、図43に示される53オクテットからなるデータフォーマットにより伝送される。即ち、伝送路4上のデータは、通常のATM セルとして伝送される。

図43に示されるように、ヘッダ部(HEADER)には、VPI(Virtual Pass Identifier)、VCI(Virtual Channel Identifier) 、PTI(Payload Type)、CLP(Cell Loss Priority)、及びHEC(Header Error Check) からなる5オクテットのデータによって構成される。

HEC(Header Error Check) 部は、上記ヘッダ部に対する生成多項式(G(x)= X8 +X2 +X+1) を用いた計算によって得られる値である。この値を用いることによって、ヘッダ部のエラーチェックが行われる。

このエラーチェックの結果が正常である場合は、図44に示されるように、VIP とVCI の値が全て“0”であるか否かが判定されることにより、処理対象のATM セルが無効セル(UNASSIGNED CELL) であるか有効セル(ASSIDNED CELL) であるかが判定される。

また、エラーチェックの結果、1ビット誤りが検出された場合にはその誤りが訂正され、2ビット誤り以上の誤りが検出された場合にはその誤りは訂正されずにその誤りの検出のみが行われる。

DS3−SMDSインタフェース3は、伝送路4から受信したATM セルについて、そのヘッダ部の1オクテットのHEC を除去すると共に2オクテットのタグを付加することにより、伝送路4上で53オクテットからなるATM セルをATM スイッチ内で処理可能な54オクテットからなるATM セルに変換する。

この場合に、SMDSサービスにおけるL2−PDUは、図43に示されるATM セルのペイロード部(PAYLOAD)に格納される。

7.ハードウエアコンフィギュレーション

7.1 概略説明

ここまで説明してきたDS3−SMDS機能は、図33に示されるDS3−SMDSインタフェース1、3と、図8に示されるSBMESH(Subscriber Message Handler Shelf)及びGWMESH(GatewayMessage Handler Shelf)によって実現される。

これらの各部分の機能の分担は、以下の通りである。

1.DS3−SMDSインタフェース部

a.DS3 レイヤ終端機能

b.DS3 PLCP レイヤ終端機能

b.L2−PDUヘッダ終端機能

2.SBMESH/GWMESH インタフェース部

a.L2−PDUペイロード終端機能

b.L3−PDU終端機能

DS3−SMDSインタフェース部に搭載される機能を更に細分化して示すと、以下の通りになる。

a.DS3 レイヤ終端機能

b.DS3 PLCPレイヤ終端機能

c.受信L2−PDUヘッダチェック機能(HCS)

d.L2−PDUヘッダパターン生成機能

e.DQDB(Distributed Queue Dual Bus)シーケンス機能(REQビット処理機能)

f.DS3 レイヤパフォーマンスモニタ機能

g.PLCPレイヤパフォーマンスモニタ機能

h.受信L2−PDUデータ変換機能 (45Mbps→156Mbps)

i.送信L2−PDUデータビットレート変換機能(156Mbps→45Mbps)

j.MSD/MSCN情報のLAP 終端機能

k.SIFSH Commonに対するインタフェース機能 (53オクテット 8ビットパラレル−54オクテット 16ビットパラレル)

l.DS3−SMDS L2−PDU セル及びLAP セルのマルチプレクス/デマルチプレクス機能

m.特定VPI/VCI セルのループバック機能

n.MSCNデータのマルチプレクス機能

o.MSD データドロッパ機能

図45に、DS3−SMDSインタフェースの機能構成ブロック図を示す。

7.2 DS3 レイヤ終端機能

DS3−SMDSインタフェース部に搭載される機能の1つであるDS3 レイヤ終端機能では、2.1.2において図35を用いて前述した、DS3 フレームフォーマットの終端処理が実行される。

より具体的には、以下の処理が実行される。

A.受信側

a.PCM ライン符号 (B3ZS符号) に対する違反監視及びエラーカウント

b.フレーミングビット(FO/F1/MO/M1 :図36参照) に対する同期確立及 びエラーカウント

c. Pビット (パリティビット :図36参照) の確認及びそれに対するエ ラーカウント

d. AISパターン (図36参照) の確認

e.イエローアラームビット(Xビット :図36参照) の確認

B.送信側

a.フレーミングビット(FO/F1/MO/M1 :図36参照) の生成

b. Pビット (パリティビット :図36参照) の生成

c. AISパターン (図36参照) の生成 (ループバック指定時)

d.レッドCGA アラーム時におけるイエローアラームビット(Xビット :図39参照) の設定

e.PCM ライン符号 (B3ZS符号) の変換

7.2.1 回線障害処理

DS3−SMDSインタフェースは、回線障害を監視しており、障害発生時には障害を交換機システムへ通知する。この障害通知は、障害の復旧にともない自動的に正常通知に復旧する。障害監視中に複数の障害が検出された場合は、その根本原因となる障害に対してのみ監視処理が実行され、その障害に起因する他の障害に対しては監視処理は実行されない。

図46に、DS3 レイヤにおけるアラームのシーケンスを示す。まず、図46(a) において、伝送路上で障害が発生すると(1.)、DS3−SMDSインタフェースAは、レッドCGA(Carrier Group Alarm)を宣言し(2.)、続いてイエローアラームを送信する(3.)。この結果、DS3−SMDSインタフェースBは、イエローCFA(Carrier Failure Alarm)を宣言する(4.)。次に、図46(b) において、DS3−SMDSインタフェースAは、折り返し試験状態になると(1.)、AIS(Alarm Indication Signal)を送信し(2.)、この結果、DS3−SMDSインタフェースBはAIS 受信宣言を行う。

図47は、DS3 レイヤにおけるアラームの優先度を示す。例えば、LOS(LossOf Signal)が検出されると、AIS(Alarm Indication Signal)、OOF(Out Of Frame) 、YEL(Yellow Signal)、POOF(PLCP Out Of Frame) 、及びPYEL(PLCP Yellow Signal)の各アラームがマスクされる。

7.2.2 各種アラームの検出・復旧条件

図48に、各種アラームの検出・復旧条件を示す。また、図49に、アラームが宣言されるタイミングを示す。

7.3 DS3 PLCPレイヤ終端機能

DS3−SMDSインタフェース部に搭載される機能の1つであるDS3 PLCPレイヤ終端機能では、3.1において図37を用いて前述した、DS3 PLCPフレームフォーマットの終端処理が実行される。

より具体的には、以下の処理が実行される。

A.受信側

a.フレーミングビット(A1/A2 :図37参照)に対する同期確立及びエラーカウント

b.PLCP BIP−8(B1:図37参照) の確認及びそれに対するエラーカウント

c.PLCPパスステータス(G1:図37参照) の確認及びそれに対するエラーカウント

B.送信側

a.フレーミングビット(A1/A2 :図37参照) の生成

b.PLCP BIP−8(B1:図37参照) の生成

c.PLCPパスステータス(G1:図37参照) の生成

d.サイクル/スタッフカウンタ(C1:図37参照) の生成

e.SIP レベル1コントロールインフォメーション(M1/M2 :図37参照) の生成

7.3.1 PLCP障害処理

DS3−SMDSインタフェースは、PLCP障害を監視しており、障害発生時には障害を交換機システムへ通知する。この障害通知は、障害の復旧にともない自動的に正常通知に復旧する。障害監視中に複数の障害が検出された場合は、その根本原因となる障害に対してのみ監視処理が実行され、その障害に起因する他の障害については監視処理は実行されない。

図50に、DS3 PLCPレイヤにおけるアラームのシーケンスを示す。図50において、まず、DS3−SMDSインタフェースBにおいてPLCPフレームの送信障害が発生すると(1.)、DS3−SMDSインタフェースAはPLCPフレームの同期外れを検出した後にイエローシグナルを送信する。この結果、DS3−SMDSインタフェースBはイエローシグナルの受信宣言を行う。

7.3.2 各種アラームの検出・復旧条件

図51に、各種アラームの検出・復旧条件を示す。また、図52に、アラームが宣言されるタイミングを示す。

7.4 L2−PDUヘッダチェック機能(HCS)

前述の図33に示されるように、DS3−SMDSインタフェース1がSMDSサービスを提供するためのDS3 伝送路2上のDS3 レイヤーを終端する場合、DS3−SMDSインタフェース1は、DS3 伝送路2から入力されるDS3 フレームのインフォメーションペイロード部に収容されているPLCPレイヤーのフレームを取り出す。そして、DS3−SMDSインタフェース1は、取り出したPLCPレイヤーのフレームからL2プロトコルデータユニット(L2−PDU)を抜き出す (図35参照) 。更に、DS3−SMDSインタフェース1は、L2−PDUのヘッダ内のアクセスコントロールフィールド(ACF、図38、図39、図35参照) に含まれるBUSYビットを参照することによって、L2−PDUが有効セルの可能性があるか無効セルの可能性があるかを判定する。L2−PDUが有効セルの可能性がある場合、DS3−SMDSインタフェース1は、L2−PDUのヘッダ内のネットワークコントロールインフォメーションフィールド(NCI、図38、図35参照) の値が、図40に示されるように、11111111 11111111 11110000 00100010 であるかオール“0”であるかを判定する。NCI の値が11111111 11111111 11110000 00100010 である場合には、DS3−SMDSインタフェース1は、対象となっているL2−PDUを真に有効なセルとして処理する。逆に、NCI の値がオール“0”である場合には、DS3−SMDSインタフェース1は、HCS エラーのカウント値をインクリメントし、プロトコルモニタ処理を実行する。

一方、前述の図34に示されるように、DS3 伝送路4にBRLCが接続され、DS3−SMDSインタフェース3がアンビリカルリンクを実現している場合には、DS3−SMDSインタフェース3は、ATM ヘッダ部のHEC(図43参照) を計算し、その計算の結果ATM ヘッダ部でエラーが発生していないと判定した場合には、更に、対象となっているATM セルが空セルであるか否かをチェックした後に、対象となっているATM セルが有効なセルであるか否かを決定する。また、DS3−SMDSインタフェース3は、上記HEC 計算の結果ATM ヘッダ部でエラーが発生していると判定した場合には、HEC エラーのカウント値をインクリメントし、プロトコルモニタ処理を実行する。

7.5 L2−PDUヘッダパターン生成機能

前述の図33に示されるように、DS3−SMDSインタフェース1がSMDSサービスを提供するためのDS3 伝送路2上のDS3 レイヤーを終端する場合、DS3−SMDSインタフェース1は、図33のATM スイッチ(ASSWSH)5の側から転送されてくるATM セルが有効セルである場合、図35に示されるようにそのATM セルのペイロード部に含まれている情報の前部に、11111111 11111111 11110000 00100010 の値を有するネットワークコントロールインフォメーションフィールド(NCI) を付加し (図40参照) 、更にその前部にアクセスコントロールフィールド(ACF) を付加することによりL2−PDUを構築する。また、DS3−SMDSインタフェース1は、図33のATM スイッチ(ASSWSH)5の側から転送されてくるATM セルが無効セルである場合は、図35に示されるようにそのATM セルのペイロード部に含まれている情報の前部に、オール“0”であるNCI を付加し (図40参照) 、更にその前部にアクセスコントロールフィールド(ACF) を付加することによりL2−PDUを構築する。このように、ATM セルがL2−PDUに変換される際には、ATM セルのヘッダ情報(VPI/VCI等) は破棄される。その後、図35に示されるように、上述のようにして構築されたL2−PDUに基づいてPLCPレイヤーのフレームが構築され、更にこのPLCPレイヤーのフレームに基づいてDS3 フレームが構築され、そのDS3 フレームが図33のDS3 伝送路2に送出される。

一方、前述の図34に示されるように、DS3 伝送路4にBRLCが接続され、DS3−SMDSインタフェース3がアンビリカルリンクを実現している場合には、DS3−SMDSインタフェース3は、ATM スイッチ(ASSWSH)の側から転送されてくるATM セルに対して、そのヘッダ部の付替えは行わずに、そのヘッダ部に対するHEC 計算のみを行いその結果得られるHEC(図43参照) をそのヘッダ部に付加した後に、そのATM セルを図34の伝送路4に送出する。

7.6 DQDB(Distributed Queue Dual Bus)シーケンス機能

前述の図33に示されるように、DS3−SMDSインタフェース1がSMDSサービスを提供するためのDS3 伝送路2上のDS3 レイヤーを終端する場合において、そのDS3 伝送路2に接続されているユーザ端末であるCPE(Customer Premise Equipment) が例えばLAN に接続されるマルチCPE である場合に、次のような制御が行われる。即ち、CPE が空セルを捕捉できなかった場合に、そのCPE は、伝送路上のL2−PDUのヘッダ内のアクセスコントロールフィールド(ACF、図38、図35参照) に含まれるREQ0−REQ2 のビット (図39参照) をオンすることにより、空セルを要求する。そして、図33に示されるDS3−SMDSインタフェース1は、CPE から上記要求ビットを受信した場合に、空セルを送出する。

7.7 DS3 レイヤ/PLCPレイヤパフォーマンスモニタ機能

DS3−SMDSインタフェースは、回線のパフォーマンスをモニタしており、単位時間(15分及び1日) 間隔で、各種パフォーマンスパラメータの積算及びその結果得られる積算値に対する閾値アラームを交換機システムに通知する。

交換機システムは、閾値アラームの通知を受けても、そのアラームに対応する回線を閉塞せずにそのアラームを単なる警報として扱い、その事実を以後の保守計画に反映させる。

パフォーマンスパラメータは、DS3 レイヤに関するものとPLCPレイヤに関するものに大きく分類される。DS3 レイヤに関しては更に、回線に関する情報とパスに関する情報とに分類することができる。

DS3 レイヤにおける回線に関する情報としては、以下の3種類のパラメータについての観測が行われる。

1.LCV : Line Code Violation

2.LES : Line Errorred Second

3.LSES: Line Severly Errorred Second

DS3 レイヤにおけるパスに関する情報としては、以下の6種類のパラメータについての測定が行われる。

4.CV : P−bit Parity Code Violation

5.ES : Errorred Second

6.SES : Severly Errorred Second

7.SEFS: Severly Errorred Second

8.UAS : Unavailable Second

9.AISS: Alarm Indication Signal Second

PLCPレイヤに関する情報としては、以下の5種類のパラメータについての測定が行われる。

10.PLCP CV : PLCP Code Violation

11.PLCP ES : PLCP Errorred Second

12.PLCP SES: PLCP Severly Errorred Second

13.PLCP OOF: PLCP Out Of Frame

14.PLCP UAS: PLCP Unavailable Second

DS3−SMDSインタフェースは、15分毎に得られる過去1回分の測定結果を保持する。この測定結果は、交換機システムによって15分時間毎に読み出される。交換機システムは、15分毎に得られるその測定結果を、1日あたり過去32回分(8時間分) 保持し、更に過去7日分保持する。

また、PLCPフレームフォーマット内のG1ビット (図37参照) を用いて伝送されるFar End Block Error(FEBE) を使用したFAR END のパフォーマンスモニタ機能も提供される。この機能における閾値は、デフォルト値であって、ユーザが自由に設定できる。

7.7.1 DS3 レイヤ

図53に、DS3 レイヤに関するパフォーマンスパラメータの種類と、各パラメータの積算値のカウントアップ条件を示す。

7.7.2 DS3−PLCPレイヤ

図54に、DS3−PLCPレイヤに関するパフォーマンスパラメータの種類と、各パラメータの積算値のカウントアップ条件、各パラメータの積算値に対するアラート閾値を示す。

7.8 受信L2−PDUデータ変換機能 (45Mbps→156Mbps)

7.4で前述したL2−PDUヘッダチェック処理の結果、L2−PDUヘッダでエラーが発生しておらず、かつそのL2−PDUが有効セルであると判定された場合には、そのL2−PDUを変換して得られるATM セルが、SIFSH Commonを介してATM スイッチ(ASSWSH)に送出される (図8参照) 。この場合に、有効セルが連続的にユーザ側から送出されてくると、ATM スイッチで処理されるデータのバースト性が高くなり、ATM スイッチ内において輻輳が発生し、ATM スイッチ内においてセル紛失が発生する可能性がある。そのため、DS3−SMDSインタフェースは、バッファを用いることによって、45Mbpsのビットレートを有するDS3 伝送路から受信したL2−PDUをSIFSH Commonが終端する156Mbps のビットレートを有する交換機内ハイウエイに多重する場合に、そのハイウエイに多重される有効セルと無効セルの割合が3:1 となるようなシェーピングを行う。

7.9 送信L2−PDUデータビットレート変換機能(156Mbps→45Mbps)

SIFSH Commonより送出されるL2−PDUのビットレートは156Mbps である。このため、DS3−SMDSインタフェースは、156Mbps のビットレートを有するデータを、DS3 レイヤのビットレートである45Mbpsのビットレートに変換する。

7.10 SIFSH Commonに対するインタフェース機能

DS3−SMDS L2−PDU のセル長は53オクテットであり、SIFSH Common(SIFSH COM、図33参照) が処理するATM セルのセル長は54オクテットである。そのため、DS3−SMDSインタフェースとSIFSH Commonの間のインタフェースは、データ長の変換機能を有する必要がある。

DS3−SMDSインタフェースからSIFSH CommonへL2−PDUが転送される場合、DS3−SMDSインタフェースは、伝送路から入力されたL2−PDUのヘッダに対してHCS(HEC)チェックを実行した後、53オクテットのL2−PDUからATM スイッチ5内で処理可能な54オクテットのATM セルへの変換を行う。この場合に、図35に示されるように、L2−PDUのヘッダ部に含まれるセグメントタイプ(SEGT)とメッセージ識別子(MID) 、並びに、L2−PDUのペイロード部に含まれるセグメンテーションユニット(SEG.UNIT)、ペイロードレングス(PLEN)、及びペイロードCRC(PCRC) が、ATM セルのペイロード部(ATM CELL PAYLOAD)に格納される。また、L2−PDUのヘッダ部内のネットワークコントロールインフォメーションフィールド(NCI) に含まれる全てのビットが“1”であるVCI は、DS3 インタフェースとSIFSH Commonとのインタフェースとして規定される値:VPI=3F,VCI=03FFに変換され、そのVPI/VCI がATM セルのヘッダ部に付加される。また、ATM セルのヘッダ部には、それが各種多重化部及びATM スイッチ内で自律的にスイッチングされるための2オクテットからなるタグが付加される。

SIFSH CommonからDS3−SMDSインタフェースへATM セルが転送される場合は、DS3−SMDSインタフェースは、ATM セルにおける先頭のタグをチェックしその結果自身が出力すべきセルである場合にそのタグを削除する。その後、DS3−SMDSインタフェースは、DS3−SMDSインタフェースからSIFSH CommonへL2−PDUが転送される場合と全く逆の操作を行うことにより、54オクテットからなるATM セルを53オクテットからなるL2−PDUに変換する。

図55は、以上の変換処理をまとめて示した図である。アクセスコントロールフィールド(ACF、図35、図38参照)についても、図55に示されるように変換される。また、共にオール“0”の値を有するペイロードタイプ(PT)及びセグメントプライオリティ(SP) (共に図40参照) は、そのまま転送される。

DS3−SMDSインタフェースがアンビリカルリンクを実現する場合には、DS3−SMDSインタフェースは、伝送路から受信したATM セルについて、そのヘッダ部の1オクテットのHEC を除去すると共に2オクテットのタグを付加することにより、伝送路4上で53オクテットからなるATM セルをATM スイッチ内で処理可能な54オクテットからなるATM セルに変換し、それをSIFSH Commonに送出する。即ち、VPI/VCI の変換は行われない。SIFSH CommonからDS3−SMDSインタフェースにATM セルが転送される場合には、上記の場合と全く逆の操作が行われる。

7.11 MSD/MSCN情報のLAP 終端機能

交換機システムからDS3−SMDSインタフェースへ転送される制御情報(MSD情報) と、DS3−SMDSインタフェースから交換機システムへ転送される、パフォーマンスモニタ閾値交差アラート、パフォーマンスモニタカウンタ値等のDS3 レイヤ/PLCPレイヤ障害情報(MSCN)は、LAPD(Link Access Protocol)を用いて伝送される。そして、このLAPDは、タイプ3又は4のAAL(ATM Adaptation Layer) プロトコルタイプを用いてATM セルにマッピングされる。この結果、上記各情報は、ATM セルとして、ATM スイッチ(ASSWSH)を通って、DS3−SMDSインタフェースと交換機システム側のBSGCSH(Broadband Signaling Group Controller Shelf 、図8参照) との間を伝送されることになる。

なお、DS3−SMDSインタフェースのハードウエア障害(Parity Error 等の障害) は、SIFSH CommonがLAPDを用いて交換機システムに通知する。交換機内を転送されるデータがL2 PDUデータであるかLAPDデータであるかの区別は、ATM セルのヘッダ部のタグ領域内の特定のビットの値により区別される。図56に、交換機内を転送されるATM セルのフォーマットを示す。交換機内を転送されるデータがL2 PDUデータであるかLAPDデータであるかの区別は、ATM セルの先頭に付加される2オクテットからなるタグ領域内のSIG ビットの値により区別される。

このように、DS3−SMDSインタフェース及びSIFSH Commonなどを交換機システムのシステムバスに直接接続する必要がなくなるため、システムバスにかかる負荷を軽減させることができる。

7.12 DS3−SMDS L2−PDU セル及びLAP セルのマルチプレクス機能

DS3−SMDSインタフェースは、SIFSH Commonの方向へ転送するATM セルにおいて、L2 PDUデータに対してMSCN LAPD セルをマルチプレクスする。MSCN LAPD セルのマルチプレクスタイミングとして、交換機システム側よりMSD LAPDセルを用いてパフォーマンスモニタ情報等の要求があった時に、L2 PDUデータに対してMSCN

LAPD セルがマルチプレクスされる。

7.13 DS3−SMDS L2−PDU セル及びLAP セルのデマルチプレクス機能

SIFSH CommonからDS3−SMDSインタフェースへ転送されてくるATM セルにおいては、L2 PDUデータに対してMSD LAPDセルがマルチプレクスされている。そのため、DS3−SMDSインタフェースは、MSD LAPD情報を処理するために、MSD LAPDセルをデマルチプレクスする必要性がある。デマルチプレクス処理は、図56に示したATM セルのタグ領域内のSIG ビットの値を判定して行われる。

7.14 特定VPI/VCI セルのループバック機能

7.14.1 “0”ビットが付加されたセルのループバック機能

DS3−SMDSインタフェースには、メンテナンス機能として、図56に示されるATM セルのタグ領域の先頭に“0”ビットが付加された特定のセルをループバックする機能が搭載されている。

7.14.2 特定VPI/VCI が付加されたセルのループバック機能

DS3−SMDSインタフェースには、メンテナンス機能として、簡易LAP を用いて通知された特定VPI/VCI が付加されたセルのループバック機能が搭載される。このループバックは、簡易LAP フォーマットを用いてVPI/VCI 値が通知された後、E−MSD 情報によって起動される。但し、このループバック機能と、7.14.1に示した“0”ビットが付加されたセルのループバック機能は、ハードウエアの構成上、同時には起動されない。

7.15 MSCNデータマルチプレクス機能

DS3−SMDSインタフェースからMSCN LAPD セルを用いて通知できないDS3−SMDSインタフェースのハードウエア障害(Parity Error 等の障害) 情報は、SIFSH CommonがLAPDセルを用いて交換機システムに通知する。そのため、DS3−SMDSインタフェースからの障害情報は、1Mbps のシリアルデータとして送出される。

7.16 MSD データドロッパ機能

SIFSH に搭載されるラインインタフェースに転送される共通的な情報は、SIFSH Commonで終端される。そのために、DS3−SMDSインタフェースへ転送される情報は、7.15で説明した場合と同様に、1Mbps のシリアルデータとして転送されてくる。DS3−SMDSインタフェースは、このようにして転送されてくるMSD データを処理する。

8.MSD(Maintenance Signal Driver)インタフェース

8.1 MSD情報

交換機システムのソフトウエアからDS3−SMDSインタフェースへ通知される情報のうち以下に示すものは、局内制御通信を用いてBSGCSH (図8参照) 経由で、一旦、交換機システムのソフトウエアからSIFSH Commonに転送される。そして、SIFSH Commonが、これらの情報を、ソフトウエア処理によってDS3−SMDSインタフェースへ通知する。このような種類の情報は、E−MSDと称される。

1.各種リセット信号

2.DS3−SMDSインタフェース状態制御情報

3.ソフトウエア障害検出回路の疑似障害設定情報

4.時計情報等の、SIFSH CommonよりDS3−SMDSインタフェースをはじめとする各個別部へ同時に通知される情報

E−MSD 情報は2重化されたSIFSH Commonの両方の系で受信されるが、DS3−SMDSインタフェースは、アクティブなSIFSH Commonから転送されてきたE−MSD 情報を取り込む。ハードウエアの制限により、E−MSD 情報は、ビットスタック(stuck) 以外を検出する手段を持たない。このため、DS3−SMDSインタフェースは、SIFSH Commonの系の切替え時のクロック/フレームパルスの乱れに対処するため、受信したE−MSD 情報に対して保護処理を実行する。即ち、DS3−SMDSインタフェースは、SIFSH Commonから連続して2フレーム分の同じ情報を受信した場合に初めて、その情報を有効なデータとして処理する。

8.1.1 E−MSD ハードウエアインタフェース

E−MSD 情報の、SIFSH CommonとDS3−SMDSインタフェース間のインタフェースとは、クロック(1.215MHz)、FP (フレームパルス) 、データの3つの要素について規定される。E−MSD のデータ長は、256 ビットである。図57に、E−MSD 信号のタイミングチャートを示す。

8.1.2 DS3−SMDSインタフェースにおけるE−MSD 収容表

図58に、DS3−SMDSインタフェースとSIFSH Common間を転送されるE−MSD 情報の収容状態を表した表を示す。この表において、縦方向はバイト位置を示し、横方向はそれぞれのバイト位置内のビット位置を示す。SIFSH Commonから転送されてくるE−MSD データは、DS3−SMDSインタフェースで、第000 バイト第D0ビット→第255 バイト第D7ビットの順序で、シリアルに受信される。このフォーマットにおいて第000 バイト領域は、SIFSH Commonで生成されるため、第001 バイトが設定されるデータの実質的な先頭になる。

DS3−SMDSインタフェースは、ハードウエアリセット信号を含む各種リセット信号を自動的に解除しないため、それらのリセット信号は、それらが設定された後は必ず解除される必要がある。

図59に、E−MSD 情報の各ビットの内容を示す。

8.2 E−MSD詳細説明

8.2.1 ハードウエアリセット

DS3−SMDSインタフェースにおいては、ハードウエア障害発生時のリセットタイミングとして、以下に示す2種類のリセットポイントが規定される。

1.SDFRST (ハードウエア障害リセット)

2.μPRST (マイクロプロセッサリセット)

これらのリセットは、ハードウエアによって自動的にそのリセットタイミングのエッジが生成されないため、セット時に“1”、リセット時に“0”が設定される必要がある。

8.2.2 ループバック

DS3−SMDSインタフェースにおいては、メンテナンスのために、以下に示す3種類の全セルに対するループバックの起動ポイントと、セル by セルのループバックの起動ポイントが規定される。

1.LOOP−1 (DS3−SMDSインタフェース入力部 (ASSW側) での全セルのループバック指示)

2.LOOP−2 (DS3−SMDSインタフェース出力部 (回線側) での全セルのループバック指示)

3.LOOP−3 (入力DS3 伝送路からの全セルの出力DS3 伝送路へのラインループバ

ック指示) 4.O−LOOP (“0”ビットが付加されたセルのループバック指示)

5.V−LOOP (特定VPI/VCI が付加されたセルのループバック指示)

8.2.3 疑似障害ポイント

DS3−SMDSインタフェースが受信するE−MSD には、インタフェース内に設けられているハードウエアチェッカに対して指定される疑似障害ポイントが収容される。疑似障害ポイントとしては、以下に示す5種類が規定される。

1.PF−CK(クロック断チェッカに対する疑似障害ポイント)

2.PF−CK(セルフレームパルス断チェッカに対する疑似障害ポイント)

3.PF−PTY (データパリティチェッカに対する疑似障害ポイント)

4.PF−WDT (ウオッチドッグタイマチェッカに対する疑似障害ポイント)

5.PTYRST (データパリティエラーリセット)