以下に、本発明の実施の形態を図面に基づいて説明する。ただし、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。

(実施の形態1)

本実施形態では、本発明の駆動方法を6ビット表示(64階調)の場合に適用した例について述べる。

本実施形態に係る駆動方法は、1つの画素を複数のサブ画素に分割し、点灯しているサブ画素の個数や面積を制御して階調を表現する面積階調方式と、1フレームを複数のサブフレームに分割し、各サブフレームに、発光回数や発光時間などの重み付けを行い、重み付けの総量を階調ごとに差を付けることによって階調を表現する時間階調方式を組み合わせた駆動方法である。つまり、1つの画素を、m個(mはm≧2の整数)のサブ画素に分割し、m個のサブ画素において、(s+1)番目の(1≦s≦m−1)サブ画素の面積は、s番目のサブ画素の面積の2倍である、すなわち、s番目のサブ画素の面積と(s+1)番目のサブ画素の面積の比は、1:2である。また、1フレームをn個のサブフレームに分割し、n個のサブフレームにおいて、(p+1)番目(1≦p≦n−1)のサブフレームの点灯期間の長さは、p番目のサブフレームの点灯期間の長さの2m倍である。すなわち、p番目のサブフレームの点灯期間の長さと(p+1)番目のサブフレームの点灯期間の長さの比は、1:2mである。さらに、n個のサブフレームの中の少なくとも1個のサブフレームを、複数のサブフレームに分割して、n個のサブフレームをt個(t>n)のサブフレームとし、各サブ画素において、発光強度が等しくなるサブフレームに対して重ね合わせ時間階調方式を適用する。すなわち、階調が大きくなるに従って、点灯するサブフレームが連続的に増えていくようにする。そして、各サブフレームにおいてm個の各サブ画素の点灯のさせ方を制御することにより、階調を表現する。なお、本発明では、各サブ画素の面積と各サブフレームの点灯期間の積を、発光強度とする。

始めに、サブ画素及びサブフレームの分割の仕方について説明する。本実施形態では、1つの画素を、各サブ画素の面積比が1:2となるように、2個のサブ画素(SP1、SP2)に分割するとともに、1フレームを、各サブフレームの点灯期間の比率が1:4:16となるように、3個のサブフレーム(SF1、SF2、SF3)に分割し、さらに、3個のサブフレーム(SF1〜SF3)の中の1個のサブフレームを、2個のサブフレームに分割した場合を例に挙げて説明する。なお、この例は、m=2、n=3に対応する。

ここで、各サブ画素の面積を、SP1=1、SP2=2、各サブフレームの点灯期間を、SF1=1、SF2=4、SF3=16とする。

本実施形態では、点灯期間の比率が1:4:16となるように、3個に分割されたサブフレーム(SF1〜SF3)の中の1個のサブフレームを、さらに2個のサブフレームに分割する。例えば、2個のサブフレームに分割するサブフレームをSF3とした場合、点灯期間16を有するSF3を、点灯期間8を有する2個のサブフレームSF31、SF32に分割する。

これにより、1フレームは4個のサブフレームに分割され、各サブフレームの点灯期間は、SF1=1、SF2=4、SF31=8、SF32=8となる。

この場合の、各階調を表現するためのサブ画素及びサブフレームの選択方法の一例を図1に示す。なお、図1の見方として、各サブフレームにおいて○印(丸印)がついているサブ画素は点灯し、×印(バツ印)がついているサブ画素は非点灯であることを示している。

本発明では、各サブ画素の面積と各サブフレームの点灯期間の積を、発光強度とする。例えば、図1において、点灯期間1を有するSF1では、面積1のサブ画素1(SP1)のみが点灯した場合の発光強度は1×1=1となり、面積2のサブ画素2(SP2)のみが点灯した場合の発光強度は2×1=2となる。同様に、点灯期間4を有するSF2では、SP1のみが点灯した場合の発光強度は4となり、SP2のみが点灯した場合の発光強度は8となる。同様に、点灯期間8を有するSF31、SF32では、SP1のみが点灯した場合の発光強度は8となり、SP2のみが点灯した場合の発光強度は16となる。このように、サブ画素の面積とサブフレームの点灯期間の組合せによって、異なる発光強度を作り出すことができ、この発光強度を用いて階調を表現する。

なお、各サブ画素において、発光強度が等しくなるサブフレームに対して、重ね合わせ時間階調方式を適用する。つまり、階調が大きくなるに従って、点灯するサブフレームが連続的に増えていくようにし、小さい階調において点灯しているサブフレームを、大きい階調においても点灯したままにする。

図1に示した例の場合、SP1は、SF31とSF32での発光強度が8となるため、SF31とSF32に重ね合わせ時間階調方式を適用する。つまり、SP1は、階調8以上の階調を表現する場合は常にSF31で点灯し、階調16以上の階調を表現する場合は常にSF32で点灯する。同様に、SP2は、SF31とSF32での発光強度が16となるため、SF31とSF32に重ね合わせ時間階調方式を適用する。つまり、SP2は、階調32以上の階調を表現する場合は常にSF31で点灯し、階調48以上の階調を表現する場合は常にSF32で点灯する。

次に、各階調を表現するためのサブ画素及びサブフレームの選択方法について説明する。

例えば、図1に示したサブ画素及びサブフレームの選択方法において、階調1を表現する場合は、SF1でSP1を点灯させる。また、階調2を表現する場合は、SF1でSP2を点灯させる。また、階調3を表現する場合は、SF1でSP1とSP2を点灯させる。また、階調6を表現する場合は、SF1でSP2を点灯させ、SF2でSP1を点灯させる。また、階調32を表現する場合は、SF31でSP1とSP2を点灯させ、SF32でSP1を点灯させる。その他の階調についても同様に、各サブフレームで点灯させる各サブ画素を選択する。

以上のように、各サブフレームで点灯させるサブ画素を選択することにより、6ビット階調(64階調)を表現することができる。

本発明の駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。例えば、図1に示したサブ画素及びサブフレームの選択方法を用いて、画素Aでは、階調31を表示し、画素Bでは、階調32で表示しているとする。その場合の、各サブフレームにおける各サブ画素の点灯・非点灯の状態を、図2に示す。

ここで、図2の見方を説明する。図2は、1フレームでの画素の点灯・非点灯の状態を示す図である。図2の横方向は時間を示し、縦方向は画素の位置を示している。そして、図2に示された四角形の縦方向の長さが、各サブ画素の面積比を示し、横方向の長さが、各サブフレームの点灯期間の長さの比を示している。また、図2に描かれたそれぞれの四角形の面積が、発光強度を示している。

例えば、視線が動いたとすると、視線の追い方によって、あるときは階調が29(=1+4+8+8+8)と感じ、あるときは、階調が32(=16+8+8)と感じる。本来は、階調が31と32に見えるべきであるのに、階調が29や32に見えてしまい、擬似輪郭が発生してしまう。しかし、階調のずれが従来の駆動方法よりも小さくなるため、擬似輪郭が低減される。

なお、点灯期間の長さは、全体の階調数(ビット数)や全体のサブフレーム数などにより、適宜変わるものである。よって、点灯期間の長さが同じであっても、全体の階調数(ビット数)や全体のサブフレーム数が変われば、実際に点灯している期間の長さ(例えば、何μsであるか)については、変わる可能性がある。

なお、点灯期間は、ずっと点灯し続ける場合に用いるものであり、点灯回数は、ある時間内において、点滅し続ける場合に用いるものである。点灯回数を用いる代表的なディスプレイは、プラズマディスプレイである。点灯期間を用いる代表的なディスプレイは、有機ELディスプレイである。

なお、図1に示した例では、SF3を2個のサブフレームに分割したが、SF3を3個以上のサブフレームに分割してもよい。例えば、図1において、SF3を4個のサブフレームに分割した場合のサブ画素及びサブフレームの選択方法を、図3に示す。

図3に示した例では、点灯期間の比率が1:4:16となるように、3個に分割されたサブフレーム(SF1〜SF3)の中で、点灯期間16を有するSF3を、点灯期間4を有する4個のサブフレームSF31、SF32、SF33、SF34に分割する。

これにより、1フレームは6個のサブフレームに分割され、各サブフレームの点灯期間は、SF1=1、SF2=4、SF31=4、SF32=4、SF33=4、SF34=4となる。

なお、各サブ画素において、発光強度が等しくなるサブフレームに対して、重ね合わせ時間階調方式を適用する。つまり、階調が大きくなるに従って、点灯するサブフレームが連続的に増えていくようにし、小さい階調において点灯しているサブフレームを、大きい階調においても点灯したままにする。

図3に示した例の場合、SP1は、SF2、SF31〜SF34での発光強度が4となるため、これらのサブフレームのうち、SF2とSF31〜SF33に重ね合わせ時間階調方式を適用する。つまり、SP1は、階調4以上の階調を表現する場合は常にSF2で点灯し、階調8以上の階調を表現する場合は常にSF31で点灯し、階調12以上の階調を表現する場合は常にSF32で点灯し、階調16以上の階調を表現する場合は常にSF33で点灯する。同様に、SP2は、SF2、SF31〜SF34での発光強度が8となるため、SF2とSF31〜SF34に重ね合わせ時間階調方式を適用する。

なお、図3で示したように、各サブ画素において、発光強度が等しくなるサブフレームに対して重ね合わせ時間階調方式を適用する場合、該当するサブフレームのうち、少なくとも1個のサブフレームに対して重ね合わせ時間階調方式を適用すればよい。従って、該当するサブフレームの中の複数のサブフレームに重ね合わせ時間階調方式を適用してもよいし、該当する全てのサブフレームに重ね合わせ時間階調方式を適用してもよい。

なお、図3に示した駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。例えば、図3に示したサブ画素及びサブフレームの選択方法を用いて、画素Aでは、階調31を表示し、画素Bでは、階調32で表示しているとする。その場合の、各サブフレームにおける各サブ画素の点灯・非点灯の状態を、図4に示す。例えば、視線が動いたとすると、視線の追い方によって、あるときは階調が21(=1+4+8+4+4)と感じ、あるときは、階調が28(=8+8+4+4+4)と感じる。本来は、階調が31と32に見えるべきであるのに、階調が21や28に見えてしまい、擬似輪郭が発生してしまう。しかし、階調のずれが従来の駆動方法よりも小さくなるため、擬似輪郭が低減される。

なお、図3に示した例のように、SF3の分割数を多くすると、最長の点灯期間を有するサブフレームの個数が多くなり、消去動作を行う必要のないサブフレームの個数が多くなる。これにより、消去動作を行うために消費される電力を低減させることができる。また、デューティー比を向上させることができ、輝度を上げることができる。また、デューティー比の向上により、発光素子にかかる電圧を小さくすることができる。従って、消費電力を低減でき、発光素子の劣化も少なくすることができる。

なお、図1や図3に示した例では、SF3を、同じ点灯期間を有する複数のサブフレームに分割したが、これに限定されない。SF3を、それぞれ異なる点灯期間を有する複数のサブフレームに分割してもよい。例えば、図1において、SF3を、それぞれ異なる点灯期間を有する2個のサブフレームに分割した場合のサブ画素及びサブフレームの選択方法を、図5に示す。

図5に示した例では、点灯期間の比率が1:4:16となるように、3個に分割されたサブフレーム(SF1〜SF3)の中で、点灯期間16を有するSF3を、点灯期間4を有するサブフレームSF31と点灯期間12を有するサブフレームSF32に分割する。

これにより、1フレームは4個のサブフレームに分割され、各サブフレームの点灯期間は、SF1=1、SF2=4、SF31=4、SF32=12となる。

なお、各サブ画素において、発光強度が等しくなるサブフレームに対して、重ね合わせ時間階調方式を適用する。つまり、階調が大きくなるに従って、点灯するサブフレームが連続的に増えていくようにし、小さい階調において点灯しているサブフレームを、大きい階調においても点灯したままにする。

図5に示した例の場合、SP1は、SF2とSF31での発光強度が4となるため、これらのサブフレームのうち、SF2に重ね合わせ時間階調方式を適用する。つまり、SP1は、階調4以上の階調を表現する場合は常にSF2で点灯する。同様に、SP2は、SF2とSF31での発光強度が8となるため、これらのサブフレームのうち、SF2に重ね合わせ時間階調方式を適用する。

図5に示した駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。例えば、図5に示したサブ画素及びサブフレームの選択方法を用いて、画素Aでは、階調31を表示し、画素Bでは、階調32で表示しているとする。その場合の、各サブフレームにおける各サブ画素の点灯・非点灯の状態を、図6に示す。例えば、視線が動いたとすると、視線の追い方によって、あるときは階調が25(=1+4+8+12)と感じ、あるときは、階調が28(=8+8+12)と感じる。本来は、階調が31と32に見えるべきであるのに、階調が25や28に見えてしまい、擬似輪郭が発生してしまう。しかし、階調のずれが従来の駆動方法よりも小さくなるため、擬似輪郭が低減される。

なお、図1において、SF3を、それぞれ異なる点灯期間を有する3個のサブフレームに分割した場合のサブ画素及びサブフレームの選択方法を、図7、図9に示す。

図7に示した例では、点灯期間の比率が1:4:16となるように、3個に分割されたサブフレーム(SF1〜SF3)の中で、点灯期間16を有するSF3を、点灯期間4を有するサブフレームSF31、SF32と点灯期間8を有するサブフレームSF33に分割する。

これにより、1フレームは5個のサブフレームに分割され、各サブフレームの点灯期間は、SF1=1、SF2=4、SF31=4、SF32=4、SF33=8となる。

なお、各サブ画素において、発光強度が等しくなるサブフレームに対して、重ね合わせ時間階調方式を適用する。つまり、階調が大きくなるに従って、点灯するサブフレームが連続的に増えていくようにし、小さい階調において点灯しているサブフレームを、大きい階調においても点灯したままにする。

図7に示した例の場合、SP1は、SF2、SF31、SF32での発光強度が4となるため、これらのサブフレームのうち、SF2とSF31に重ね合わせ時間階調方式を適用する。つまり、SP1は、階調4以上の階調を表現する場合は常にSF2で点灯し、階調8以上の階調を表現する場合は常にSF31で点灯する。同様に、SP2は、SF2、SF31、SF32での発光強度が8となるため、SF2、SF31、SF32に重ね合わせ時間階調方式を適用する。

図7に示した駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。例えば、図7に示したサブ画素及びサブフレームの選択方法を用いて、画素Aでは、階調31を表示し、画素Bでは、階調32で表示しているとする。その場合の、各サブフレームにおける各サブ画素の点灯・非点灯の状態を、図8に示す。例えば、視線が動いたとすると、視線の追い方によって、あるときは階調が20(=8+8+4)と感じ、あるときは、階調が29(=1+4+8+8+8)と感じる。本来は、階調が31と32に見えるべきであるのに、階調が20や29に見えてしまい、擬似輪郭が発生してしまう。しかし、階調のずれが従来の駆動方法よりも小さくなるため、擬似輪郭が低減される。

図9に示した例では、点灯期間の比率が1:4:16となるように、3個に分割されたサブフレーム(SF1〜SF3)の中で、点灯期間16を有するSF3を、点灯期間4を有するサブフレームSF31と点灯期間6を有するサブフレームSF32、SF33に分割する。

これにより、1フレームは5個のサブフレームに分割され、各サブフレームの点灯期間は、SF1=1、SF2=4、SF31=4、SF32=6、SF33=6となる。

なお、各サブ画素において、発光強度が等しくなるサブフレームに対して、重ね合わせ時間階調方式を適用する。つまり、階調が大きくなるに従って、点灯するサブフレームが連続的に増えていくようにし、小さい階調において点灯しているサブフレームを、大きい階調においても点灯したままにする。

図9に示した例の場合、SP1は、SF2、SF31での発光強度が4となるため、これらのサブフレームのうち、SF2に重ね合わせ時間階調方式を適用する。また、SF32、SF33での発光強度が6となるため、SF32、SF33に重ね合わせ時間階調方式を適用する。つまり、SP1は、階調4以上の階調を表現する場合は常にSF2で点灯し、階調12以上の階調を表現する場合は常にSF32で点灯し、階調18以上の階調を表現する場合は常にSF33で点灯する。同様に、SP2は、SF2、SF31での発光強度が8となるため、これらのサブフレームのうち、SF2に重ね合わせ時間階調方式を適用する。また、SF32、SF33での発光強度が12となるため、SF32、SF33に重ね合わせ時間階調方式を適用する。

図9に示した駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。例えば、図9に示したサブ画素及びサブフレームの選択方法を用いて、画素Aでは、階調31を表示し、画素Bでは、階調32で表示しているとする。その場合の、各サブフレームにおける各サブ画素の点灯・非点灯の状態を、図10に示す。例えば、視線が動いたとすると、視線の追い方によって、あるときは階調が25(=1+4+8+6+6)と感じ、あるときは、階調が28(=8+8+6+6)と感じる。本来は、階調が31と32に見えるべきであるのに、階調が25や28に見えてしまい、擬似輪郭が発生してしまう。しかし、階調のずれが従来の駆動方法よりも小さくなるため、擬似輪郭が低減される。

なお、図9に示した例では、SF1〜SF3の中の1個のサブフレーム(SF3)を、さらに複数のサブフレームに分割したが、複数のサブフレームに分割するサブフレームの個数は、これに限定されない。SF1〜SF3の中の複数のサブフレームを、それぞれ複数のサブフレームに分割してもよい。

例えば、図1において、点灯期間の比率が1:4:16となるように、3個に分割されたサブフレーム(SF1〜SF3)の中の2個のサブフレームを、さらに複数のサブフレームに分割した場合の例を図11、図13に示す。なお、図11、図13に示した例では、複数のサブフレームに分割するサブフレームをSF2、SF3としている。

図11に示した例は、SF2、SF3を、それぞれ2個のサブフレームに分割する場合を示している。例えば、点灯期間4を有するSF2を、点灯期間2を有する2個のサブフレームSF21、SF22に分割する。また、点灯期間16を有するSF3を、点灯期間8を有する2個のサブフレームSF31、SF32に分割する。

これにより、1フレームは5個のサブフレームに分割され、各サブフレームの点灯期間は、SF1=1、SF21=2、SF22=2、SF31=8、SF32=8となる。

なお、各サブ画素において、発光強度が等しくなるサブフレームに対して、重ね合わせ時間階調方式を適用する。つまり、階調が大きくなるに従って、点灯するサブフレームが連続的に増えていくようにし、小さい階調において点灯しているサブフレームを、大きい階調においても点灯したままにする。

図11に示した例の場合、SP1は、SF21、SF22での発光強度が2となるため、SF21、SF22に重ね合わせ時間階調方式を適用する。また、SF31、SF32での発光強度が8となるため、これらのサブフレームのうち、SF32に重ね合わせ時間階調方式を適用する。つまり、SP1は、階調2以上の階調を表現する場合は常にSF21で点灯し、階調4以上の階調を表現する場合は常にSF22で点灯し、階調16以上の階調を表現する場合は常にSF31で点灯する。同様に、SP2は、SF21、SF22での発光強度が4となるため、これらのサブフレームのうち、SF21に重ね合わせ時間階調方式を適用する。また、SF31、SF32での発光強度が16となるため、SF31、SF32に重ね合わせ時間階調方式を適用する。

図11に示した駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。例えば、図11に示したサブ画素及びサブフレームの選択方法を用いて、画素Aでは、階調31を表示し、画素Bでは、階調32で表示しているとする。その場合の、各サブフレームにおける各サブ画素の点灯・非点灯の状態を、図12に示す。例えば、視線が動いたとすると、視線の追い方によって、あるときは階調が19(=1+2+4+4+8)と感じ、あるときは、階調が28(=4+16+8)と感じる。本来は、階調が31と32に見えるべきであるのに、階調が19や28に見えてしまい、擬似輪郭が発生してしまう。しかし、階調のずれが従来の駆動方法よりも小さくなるため、擬似輪郭が低減される。

図13に示した例は、SF2を2個のサブフレームに分割し、SF3を4個のサブフレームに分割する場合を示している。例えば、点灯期間4を有するSF2を、点灯期間2を有する2個のサブフレームSF21、SF22に分割する。また、点灯期間16を有するSF3を、点灯期間4を有する4個のサブフレームSF31、SF32、SF33、SF34に分割する。

これにより、1フレームは7個のサブフレームに分割され、各サブフレームの点灯期間は、SF1=1、SF21=2、SF22=2、SF31=4、SF32=4、SF33=4、SF34=4となる。

なお、各サブ画素において、発光強度が等しくなるサブフレームに対して、重ね合わせ時間階調方式を適用する。つまり、階調が大きくなるに従って、点灯するサブフレームが連続的に増えていくようにし、小さい階調において点灯しているサブフレームを、大きい階調においても点灯したままにする。

図13に示した例の場合、SP1は、SF21、SF22での発光強度が2となるため、SF21、SF22に重ね合わせ時間階調方式を適用する。また、SF31〜SF34での発光強度が4となるため、SF31〜SF34に重ね合わせ時間階調方式を適用する。つまり、SP1は、階調2以上の階調を表現する場合は常にSF21で点灯し、階調4以上の階調を表現する場合は常にSF22で点灯し、階調8以上の階調を表現する場合は常にSF31で点灯し、階調12以上の階調を表現する場合は常にSF32で点灯し、階調16以上の階調を表現する場合は常にSF33で点灯し、階調20以上の階調を表現する場合は常にSF34で点灯する。同様に、SP2は、SF21、SF22での発光強度が4となるため、これらのサブフレームのうち、SF21に重ね合わせ時間階調方式を適用する。また、SF31〜SF34での発光強度が8となるため、SF31〜SF34に重ね合わせ時間階調方式を適用する。

図13に示した駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。例えば、図13に示したサブ画素及びサブフレームの選択方法を用いて、画素Aでは、階調31を表示し、画素Bでは、階調32で表示しているとする。その場合の、各サブフレームにおける各サブ画素の点灯・非点灯の状態を、図14に示す。例えば、視線が動いたとすると、視線の追い方によって、あるときは階調が19(=1+2+4+4+4+4)と感じ、あるときは、階調が24(=4+8+4+4+4)と感じる。本来は、階調が31と32に見えるべきであるのに、階調が19や24に見えてしまい、擬似輪郭が発生してしまう。しかし、階調のずれが従来の駆動方法よりも小さくなるため、擬似輪郭が低減される。

なお、これまでに示した例では、複数のサブフレームに分割するサブフレームとして、SF3を必ず含むように選んだが、複数のサブフレームに分割するサブフレームの選び方は、これに限定されない。複数のサブフレームに分割するサブフレームとして、SF1及びSF2の中から選んでもよい。

なお、本実施形態において、複数のサブフレームに分割するサブフレームとして、n個のサブフレームの中の最長の点灯期間を有するサブフレームを含むように選ぶのが望ましい。なぜなら、最長の点灯期間を有するサブフレームを分割することにより、擬似輪郭をより低減させることができるからである。また、最長の点灯期間を有するサブフレームを分割することにより、分割後において最長の点灯期間を有するサブフレームの個数が多くなり、消去動作を行う必要のないサブフレームの個数が多くなることにより、消去動作を行うために消費される電力を低減させることができるからである。また、デューティー比を向上させることができ、輝度を上げることができる。また、デューティー比の向上により、発光素子にかかる電圧を小さくすることができる。従って、消費電力を低減でき、発光素子の劣化も少なくすることができる。

なお、サブフレームを複数に分割することにより、同じ階調を表現するためのサブ画素及びサブフレームの選択方法が増える。従って、サブ画素及びサブフレームの選択方法は、これまでに示した例に限定されない。例えば、図1において、階調31及び階調32を表現するためのサブ画素及びサブフレームの選択方法を変えた場合の例を、図15に示す。

図1及び図15に示したそれぞれのサブ画素及びサブフレームの選択方法で異なる箇所について説明する。まず、階調31を表現する場合、図1に示した例では、SF31とSF32でSP1を点灯させるが、図15に示した例では、SF31とSF32でSP1を点灯させずに、SF31でSP2を点灯させる。次に、階調32を表現する場合、図1に示した例では、SF31でSP1を点灯させるが、図15に示した例では、SF31でSP1を点灯させずに、SF2でSP2を点灯させる。

なお、図1に示した例では、SP1、SP2ともに、SF31とSF32に重ね合わせ時間階調方式を適用していたが、図15に示した例では、SP2のSF31とSF32に重ね合わせ時間階調方式を適用する。

図15に示した駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。例えば、図15に示したサブ画素及びサブフレームの選択方法を用いて、画素Aでは、階調31を表示し、画素Bでは、階調32で表示しているとする。その場合の、各サブフレームにおける各サブ画素の点灯・非点灯の状態を、図16に示す。例えば、視線が動いたとすると、視線の追い方によって、あるときは階調が37(=1+4+8+16+8)と感じ、あるときは、階調が40(=8+16+16)と感じる。本来は、階調が31と32に見えるべきであるのに、階調が37や40のように見えてしまい、擬似輪郭が発生してしまう。しかし、階調のずれが従来の駆動方法よりも小さくなるため、擬似輪郭が低減される。

なお、サブ画素及びサブフレームの選択方法を変える階調は、階調31と階調32に限定されない。他の階調に対して、サブ画素及びサブフレームの選択方法を変えてもよい。なお、階調31と階調32のように、擬似輪郭が特に出やすい階調に対して、選択的に各サブフレームにおけるサブ画素の選択方法を変えることにより、擬似輪郭を低減させる効果を大きくすることができる。

なお、本実施形態では、各サブフレームを点灯期間の昇順に配置したが、サブフレームの配置の順序は、これに限定されない。例えば、図1において、サブフレームの配置の順序を変えた場合の例を、図17に示す。

図17に示した例では、図1において、点灯期間4を有するSF2と点灯期間8を有するSF32の配置を入れ換えている。

図17に示した駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。例えば、図17に示したサブ画素及びサブフレームの選択方法を用いて、画素Aでは、階調31を表示し、画素Bでは、階調32で表示しているとする。その場合の、各サブフレームにおける各サブ画素の点灯・非点灯の状態を、図18に示す。例えば、視線が動いたとすると、視線の追い方によって、あるときは階調が28(=8+8+8+4)と感じ、あるときは、階調が33(=1+8+8+16)と感じる。本来は、階調が31と32に見えるべきであるのに、階調が28や33に見えてしまい、擬似輪郭が発生してしまう。しかし、階調のずれが従来の駆動方法よりも小さくなるため、擬似輪郭が低減される。

このように、各サブフレームの配置の順序を変えることにより、目が誤魔化され、視線が動いたときの階調のずれを従来の駆動方法よりも小さくすることができる。よって、従来の駆動方法よりも擬似輪郭を低減させることができる。

なお、図17に示した例では、SF2とSF32の配置を入れ換えたが、配置を入れ換えるサブフレームは、これらに限定されない。任意の複数のサブフレームを選択し、配置を入れ換えてもよい。なお、配置を入れ換えるサブフレームとして、点灯期間が最長となるサブフレームを選択するのが望ましい。なぜならば、点灯期間が最長となるサブフレームの配置を入れ換えることによって、目が誤魔化され、視線が動いたときの階調のずれを従来の駆動方法よりも小さくすることができ、従来の駆動方法よりも擬似輪郭を低減させることができるためである。

なお、サブフレームの配置の順序として、点灯期間の昇順もしくは降順に配置するのがより望ましい。なぜならば、点灯期間の昇順もしくは降順に配置した方が、従来の駆動方法よりも階調のずれをより小さくすることができ、従来の駆動方法よりも擬似輪郭をより低減させることができるためである。

なお、本実施形態では、各サブ画素の面積比を1:2としていたが、これに限定されない。例えば、1:4に分割してもよいし、1:8に分割してもよい。

例えば、各サブ画素の面積比を1:1とすると、同じサブフレームでどちらのサブ画素を発光させても発光強度は等しくなる。従って、同じ階調を表現する際に、どちらのサブ画素を発光させるかを切り換えてもよい。これにより、特定のサブ画素のみ集中して発光することを防ぐことができ、焼き付きを防ぐことができる。

なお、m個(mはm≧2の整数)のサブ画素において、(s+1)番目(1≦s≦m−1)のサブ画素の面積は、s番目のサブ画素の面積の2倍である。すなわち、s番目のサブ画素の面積と(s+1)番目のサブ画素の面積の比は、1:2である。また、n個(nはn≧2の整数)のサブフレームにおいて、(p+1)番目(1≦p≦n−1)のサブフレームの点灯期間の長さは、p番目のサブフレームの点灯期間の長さの2m倍である。すなわち、p番目のサブフレームの点灯期間の長さと(p+1)番目のサブフレームの点灯期間の長さの比は、1:2mである。これにより、より少ないサブ画素数及びより少ないサブフレーム数で、より多くの階調を表現することが可能となる。また、この方法で表現できる階調は、階調の変化率が一定となるため、よりなめらかな階調表示が可能となり、画質を向上させることができる。

なお、本実施形態では、サブ画素の個数は2個としていたが、これに限定されない。

例えば、1つの画素を、各サブ画素の面積比が1:2:4となるように、3個のサブ画素(SP1、SP2、SP3)に分割するとともに、1フレームを、各サブフレームの点灯期間の比率が1:8となるように、2個のサブフレーム(SF1、SF2)に分割し、さらに、2個のサブフレーム(SF1、SF2)の中の1個のサブフレームを、2個のサブフレームに分割した場合を例に挙げて説明する。この場合のサブ画素及びサブフレームの選択方法を、図19に示す。なお、この例は、m=3、n=2に対応する。

ここで、各サブ画素の面積を、SP1=1、SP2=2、SP3=4、各サブフレームの点灯期間を、SF1=1、SF2=8とする。

図19では、点灯期間の比率が1:8となるように、2個に分割されたサブフレーム(SF1、SF2)の中の1個のサブフレームを、さらに2個のサブフレームに分割する。例えば、2個のサブフレームに分割するサブフレームをSF2とした場合、点灯期間8を有するSF2を、点灯期間4を有する2個のサブフレームSF21、SF22に分割する。

これにより、1フレームは3個のサブフレームに分割され、各サブフレームの点灯期間は、SF1=1、SF21=4、SF22=4となる。

なお、各サブ画素において、発光強度が等しくなるサブフレームに対して、重ね合わせ時間階調方式を適用する。つまり、階調が大きくなるに従って、点灯するサブフレームが連続的に増えていくようにし、小さい階調において点灯しているサブフレームを、大きい階調においても点灯したままにする。

図19に示した例の場合、SP1は、SF21とSF22での発光強度が4となるため、SF21とSF22に重ね合わせ時間階調方式を適用する。つまり、SP1は、階調4以上の階調を表現する場合は常にSF21で点灯し、階調8以上の階調を表現する場合は常にSF22で点灯する。同様に、SP2は、SF21とSF22での発光強度が8となるため、これらのサブフレームのうち、SF21に重ね合わせ時間階調方式を適用する。同様に、SP3は、SF21とSF22での発光強度が16となるため、SF21とSF22に重ね合わせ時間階調方式を適用する。

図19に示した駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。例えば、図19に示したサブ画素及びサブフレームの選択方法を用いて、画素Aでは、階調31を表示し、画素Bでは、階調32で表示しているとする。その場合の、各サブフレームにおける各サブ画素の点灯・非点灯の状態を、図20に示す。例えば、視線が動いたとすると、視線の追い方によって、あるときは階調が19(=1+2+8+4+4)と感じ、あるときは、階調が36(=16+8+4+8)と感じる。本来は、階調が31と32に見えるべきであるのに、階調が19や36に見えてしまい、擬似輪郭が発生してしまう。しかし、階調のずれが従来の駆動方法よりも小さくなるため、擬似輪郭が低減される。

なお、図19に示した例では、SF2を2個のサブフレームに分割したが、SF2を3個以上のサブフレームに分割してもよい。例えば、図19において、SF2を4個のサブフレームに分割した場合のサブ画素及びサブフレームの選択方法を、図21に示す。

図21に示した例では、点灯期間の比率が1:8となるように、2個に分割されたサブフレーム(SF1、SF2)の中で、点灯期間8を有するSF2を、点灯期間2を有する4個のサブフレームSF21、SF22、SF23、SF24に分割する。

これにより、1フレームは5個のサブフレームに分割され、各サブフレームの点灯期間は、SF1=1、SF21=2、SF22=2、SF23=2、SF24=2となる。

なお、各サブ画素において、発光強度が等しくなるサブフレームに対して、重ね合わせ時間階調方式を適用する。つまり、階調が大きくなるに従って、点灯するサブフレームが連続的に増えていくようにし、小さい階調において点灯しているサブフレームを、大きい階調においても点灯したままにする。

図21に示した例の場合、SP1は、SF21〜SF24での発光強度が2となるため、SF21〜SF24に重ね合わせ時間階調方式を適用する。つまり、SP1は、階調2以上の階調を表現する場合は常にSF21で点灯し、階調4以上の階調を表現する場合は常にSF22で点灯し、階調6以上の階調を表現する場合は常にSF23で点灯し、階調8以上の階調を表現する場合は常にSF24で点灯する。同様に、SP2は、SF21〜SF24での発光強度が4となるため、SF21〜SF24に重ね合わせ時間階調方式を適用する。同様に、SP3は、SF21〜SF24での発光強度が8となるため、SF21〜SF24に重ね合わせ時間階調方式を適用する。

図21に示した駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。例えば、図21に示したサブ画素及びサブフレームの選択方法を用いて、画素Aでは、階調31を表示し、画素Bでは、階調32で表示しているとする。その場合の、各サブフレームにおける各サブ画素の点灯・非点灯の状態を、図22に示す。例えば、視線が動いたとすると、視線の追い方によって、あるときは階調が17(=1+2+4+2+4+4)と感じ、あるときは、階調が24(=8+4+4+2+4+2)と感じる。本来は、階調が31と32に見えるべきであるのに、階調が17や24に見えてしまい、擬似輪郭が発生してしまう。しかし、階調のずれが従来の駆動方法よりも小さくなるため、擬似輪郭が低減される。

なお、図21に示した例のように、SF2の分割数を多くすると、最長の点灯期間を有するサブフレームの個数が多くなり、消去動作を行う必要のないサブフレームの個数が多くなる。これにより、消去動作を行うために消費される電力を低減させることができる。また、デューティー比を向上させることができ、輝度を上げることができる。また、デューティー比の向上により、発光素子にかかる電圧を小さくすることができる。従って、消費電力を低減でき、発光素子の劣化も少なくすることができる。

なお、ある階調において、サブ画素及びサブフレームの選択方法を時間的に、または、場所的に変えてもよい。つまり、時刻によって、サブ画素及びサブフレームの選択方法を変えてもよいし、画素によって、サブ画素及びサブフレームの選択方法を変えてもよい。さらに、時刻によって変えて、かつ、画素によっても変えてもよい。

例えば、ある階調を表現するとき、フレーム数が奇数番目のときと、偶数番目のときとで、各サブフレームにおけるサブ画素の選択方法を変えてもよい。例えば、フレーム数が奇数番目のときは、図1に示したサブ画素及びサブフレームの選択方法で階調を表現し、フレーム数が偶数番目のときは、図15に示したサブ画素及びサブフレームの選択方法で階調を表現してもよい。

このように、擬似輪郭が特に出やすい階調に対するサブ画素及びサブフレームの選択方法を、フレーム数が奇数番目のときと、偶数番目のときとで変えることにより、擬似輪郭を低減することができる。

また、ある階調を表現するとき、奇数行目の画素を表示するときと、偶数行目の画素を表示するときとで、サブ画素及びサブフレームの選択方法を変えてもよい。また、ある階調を表現するとき、奇数列目の画素を表示するときと、偶数列目の画素を表示するときとで、サブ画素及びサブフレームの選択方法を変えてもよい。

また、ある階調を表現するとき、フレーム数が奇数番目のときと、偶数番目のときとで、サブフレームの個数や点灯期間の比率を変えてもよい。例えば、フレーム数が奇数番目のときは、図1で示したサブ画素の選択方法で階調を表現し、フレーム数が偶数番目のときは、図3で示したサブ画素の選択方法で階調を表現してもよい。

また、ある階調を表現するとき、奇数行目の画素を表示するときと、偶数行目の画素を表示するときとで、サブフレームの個数や点灯期間の比率を変えてもよい。また、ある階調を表現するとき、奇数列目の画素を表示するときと、偶数列目の画素を表示するときとで、サブフレームの個数や点灯期間の比率を変えてもよい。

また、ある階調を表現するとき、フレーム数が奇数番目のときと、偶数番目のときとで、サブフレームの配置の順序を変えてもよい。例えば、フレーム数が奇数番目のときは、図1で示したサブ画素及びサブフレームの選択方法で階調を表現し、フレーム数が偶数番目のときは、図17で示したサブ画素及びサブフレームの選択方法で階調を表現してもよい。

また、ある階調を表現するとき、奇数行目の画素を表示するときと、偶数行目の画素を表示するときとで、サブフレームの配置の順序を変えてもよい。また、ある階調を表現するとき、奇数列目の画素を表示するときと、偶数列目の画素を表示するときとで、サブフレームの配置と順序を変えてもよい。

このように、ある階調において、サブ画素及びサブフレームの選択方法やサブフレームの個数や点灯期間の比率、サブフレームの配置の順序を時間的に、または、場所的に変えることにより、より目を誤魔化して、階調のずれをより小さくすることができるため、従来の駆動方法よりも擬似輪郭を低減させることができる。

なお、本実施形態では、6ビット階調(64階調)の場合を例に挙げたが、表示する階調数はこれに限定されない。例えば、本発明の駆動方法を用いて、8ビット階調(256階調)を表現することができる。この場合の例を図23〜図26に示す。なお、図23は階調0〜63、図24は階調64〜127、図25は階調128〜191、図26は階調192〜255におけるサブ画素の選択方法を示す。

図23〜図26では、1つの画素を、各サブ画素の面積比が1:2となるように、2個のサブ画素(SP1、SP2)に分割するとともに、1フレームを、各サブフレームの点灯期間の比率が1:4:16:64となるように、4個のサブフレーム(SF1〜SF4)に分割し、さらに、4個のサブフレーム(SF1〜SF4)の中の1個のサブフレームを、2個のサブフレームに分割している。なお、この例は、m=2、n=4に対応する。

ここで、各サブ画素の面積を、SP1=1、SP2=2、各サブフレームの点灯期間を、SF1=1、SF2=4、SF3=16、SF4=64とする。

なお、図23〜図26では、2個のサブフレームに分割するサブフレームをSF4とし、点灯期間64を有するSF4を、点灯期間32を有する2個のサブフレームSF41、SF42に分割している。

これにより、1フレームは5個のサブフレームに分割され、各サブフレームの点灯期間は、SF1=1、SF2=4、SF3=16、SF41=32、SF42=32となる。

なお、各サブ画素において、発光強度が等しくなるサブフレームに対して、重ね合わせ時間階調方式を適用する。つまり、階調が大きくなるに従って、点灯するサブフレームが連続的に増えていくようにし、小さい階調において点灯しているサブフレームを、大きい階調においても点灯したままにする。

図23〜図26に示した例の場合、SP1は、SF41とSF42での発光強度が32となるため、SF41とSF42に重ね合わせ時間階調方式を適用する。つまり、SP1は、階調32以上の階調を表現する場合は常にSF41で点灯し、階調64以上の階調を表現する場合は常にSF42で点灯する。同様に、SP2は、SF41とSF42での発光強度が64となるため、SF41とSF42に重ね合わせ時間階調方式を適用する。

以上のように、各サブフレームで点灯させるサブ画素を選択することにより、8ビット階調(256階調)を表現することができる。

図23〜図26に示した駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。例えば、図23〜図26に示したサブ画素及びサブフレームの選択方法を用いて、画素Aでは、階調127を表示し、画素Bでは、階調128で表示しているとする。その場合の、各サブフレームにおける各サブ画素の点灯・非点灯の状態を、図27に示す。例えば、視線が動いたとすると、視線の追い方によって、あるときは階調が109(=1+4+8+32+32+32)と感じ、あるときは、階調が128(=64+32+32)と感じる。本来は、階調が127と128に見えるべきであるのに、階調が109や128に見えてしまい、擬似輪郭が発生してしまう。しかし、階調のずれが従来の駆動方法よりも小さくなるため、擬似輪郭が低減される。

このように、本実施形態の駆動方法を用いることにより、従来の駆動方法よりも擬似輪郭を低減させることができる。また、デューティー比を向上させることができるため、輝度を上げることができる。また、デューティー比の向上により、消費電力を削減できるとともに、発光素子の劣化を少なくすることができる。

なお、これまでに説明した、表示する階調数、サブフレームの点灯期間の比率及び分割の仕方、サブフレームの配置の順序、サブ画素の面積比と個数、階調によってサブ画素及びサブフレームの選択方法を変えるなどの内容を、互いに組み合わせて用いてもよい。

(実施の形態2)

実施の形態1では、階調が増えると、それに線形に比例して点灯期間が増えている場合について述べた。そこで本実施形態では、ガンマ補正を行った場合について説明する。

ガンマ補正とは、階調が増えると、非線形で点灯期間が増えていくようにしたものを指す。人間の目は、輝度が線形に比例して大きくなっても、比例して明るくなっているとは感じない。輝度が高くなるほど、明るさの差を感じにくくなっている。よって、人間の目で、明るさの差を感じるようにするためには、階調が増えていくに従って、点灯期間をより長くとる、つまり、ガンマ補正を行う必要がある。なお、階調をx、輝度をyとすると、ガンマ補正における輝度と階調の関係は、以下の(数1)で表される。

y = Axγ ・ ・ ・ (数1)

ただし、(1)式において、Aは、輝度yを0≦y≦1に規格化するための定数である。ここで、階調xの指数であるγがガンマ補正の程度を示すパラメータとなっている。

最も単純な方法は、実際に表示するビット数(階調数)よりも、多くのビット数(階調数)で表示できるようにしておく、というものである。例えば、6ビット階調(64階調)で表示を行うとき、実際には、8ビット階調(256階調)を表示できるようにしておく。そして、実際に表示するときには、階調の輝度が非線形になるようにして、6ビット階調(64階調)で表示する。これによりガンマ補正を実現できる。

一例として、6ビット階調(64階調)を表示できるようにしておいて、ガンマ補正を行った5ビット階調(32階調)を表示する場合のサブ画素及びサブフレームの選択方法を図28に示す。

なお、本実施形態では、1つの画素を、各サブ画素の面積比が1:2となるように、2個のサブ画素(SP1、SP2)に分割するとともに、1フレームを、各サブフレームの点灯期間の比率が1:4:16となるように、3個のサブフレーム(SF1、SF2、SF3)に分割し、さらに、3個のサブフレーム(SF1〜SF3)の中の1個のサブフレームを、2個のサブフレームに分割した場合を例に挙げて説明する。具体例として、図1に示したサブ画素及びサブフレームの選択方法を用いた場合を例に挙げて説明する。

図28は、全階調にわたってγ=2.2となるようなガンマ補正を行って5ビット階調(32階調)を表示する場合のサブ画素及びサブフレームの選択方法を示している。なお、γ=2.2という値は人間の視覚特性を最もよく補うような値となっており、輝度が高くなっても、最も適切な明るさの差を感じることができるようになる。図28では、ガンマ補正済みの5ビットでの階調が3までは、実際には6ビットの階調0のサブ画素及びサブフレームの選択方法で点灯させる。同様に、ガンマ補正済みの5ビットでの階調が4のときは、実際には6ビットの階調1で表示させ、ガンマ補正済みの5ビットでの階調が6のときは、実際には6ビットの階調2で表示させる。ここで、階調xと輝度yのグラフを図29に示す。図29(A)は、全階調での階調xと輝度yの関係を示し、図29(B)は、低階調領域での階調xと輝度yのグラフを示す。このように、ガンマ補正済みの5ビットでの階調と、6ビットでの階調との対応表を作成し、それに応じて、サブ画素及びサブフレームを選択し、階調を表示させればよい。これにより、γ=2.2となるようなガンマ補正を実現することができる。

ただし、図29(B)から分かるように、図28の場合、階調0〜階調3や、階調4〜階調5、階調6〜階調7までは、同じ輝度で表示させることになる。なぜなら、6ビット表示では階調数が十分でないため、輝度の違いを表現できないからである。これを対策する方法として、次の2つが考えられる。

1つ目の方法は、表示できるビット数をさらに増やすことである。6ビットではなく、7ビット以上、好ましくは8ビット以上で表示できるようにする。その結果、低階調領域においてもなめらかな表示を行うことができる。

2つ目の方法は、低階調領域ではγ=2.2の関係を満足しないが、輝度が線形で変化するようにして、なめらかに表示させる方法である。この場合のサブ画素及びサブフレームの選択方法を図30に示す。図30では、5ビットでの階調が17までは、6ビットでの階調と同じである。しかし、ガンマ補正済みの5ビットでの階調が18のときは、実際には6ビットの階調19のサブ画素及びサブフレームの選択方法で点灯させる。同様に、ガンマ補正済みの5ビットでの階調が19のときは、実際には6ビットの階調21で表示させ、ガンマ補正済みの5ビットでの階調が20のときは、実際には6ビットの階調24で表示させる。ここで、階調xと輝度yのグラフを図31に示す。図31(A)は、全階調での階調xと輝度yの関係を示し、図31(B)は、低階調領域での階調xと輝度yのグラフを示す。低階調領域では、輝度が線形に変化している。このようなガンマ補正を行うことにより、低階調領域がよりなめらかに表示できるようになる。

つまり、低階調領域については、輝度を線形に比例するように変化させ、それ以外の階調領域については、輝度を非線形に変化させることにより、低階調領域がよりなめらかに表示できるようになる。

なお、ガンマ補正済みの5ビットでの階調と、6ビットでの階調との対応表は、適宜変更することが可能である。よって、対応表を変更することにより、ガンマ補正の程度(すなわち、γの値)を容易に変更することが可能である。よって、γ=2.2に限定されない。

また、何ビット(例えばpビット、ここでpは整数)を表示できるようにしておいて、ガンマ補正済みで何ビット(例えばqビット、ここでqは整数)で表示するのかについても、これに限定されない。ガンマ補正済みで表示する場合、階調をなめらかに表現するためには、ビット数pをできるだけ大きくしておくことが望ましい。ただし、あまり大きくしすぎると、サブフレーム数が多くなってしまうなど、弊害も出てきてしまう。よって、ビット数qとビット数pとの関係は、q+2≦p≦q+5、とすることが望ましい。これにより、階調をなめらかに表現しつつ、サブフレーム数も増えすぎない、ということを実現できる。

このように、本実施形態で述べた方法でガンマ補正を行うことにより、より高画質の映像を表示することができる。

なお、本実施形態で述べた内容は、実施の形態1で述べた内容と自由に組み合わせて実施することができる。

(実施の形態3)

実施の形態1では、各サブ画素において、発光強度が等しくなるサブフレームに対して、重ね合わせ時間階調方式を適用したが、各サブ画素において、重ね合わせ時間階調方式を適用するサブフレームは、これに限定されない。本実施形態では、各サブ画素において、全てのサブフレームに対して、重ね合わせ時間階調方式を適用した場合について説明する。

本実施形態では、1つの画素を、各サブ画素の面積が全て等しい2個のサブ画素(SP1、SP2)に分割するとともに、1フレームを、各サブフレームの点灯期間の長さが全て等しい8個のサブフレーム(SF1〜SF8)に分割した場合について説明する。この場合のサブ画素及びサブフレームの選択方法を、図32に示す。

ここで、各サブ画素の面積を、SP1=SP2=1、各サブフレームの点灯期間を、SF1=SF2=SF3=SF4=SF5=SF6=SF7=SF8=1とする。

図32に示した例では、各サブ画素の面積が全て等しく、かつ、各サブフレームの点灯期間の長さが全て等しいため、全サブ画素及び全サブフレームにおいて、発光強度が等しくなる。具体的には、各サブ画素の面積が1で、各サブフレームの点灯期間が1なので、発光強度は1×1=1となる。

なお、各サブ画素において、全てのサブフレームに対して、重ね合わせ時間階調方式を適用する。つまり、階調が大きくなるに従って、点灯するサブフレームが連続的に増えていくようにし、小さい階調において点灯しているサブフレームを、大きい階調においても点灯したままにする。

図32に示した例の場合、SP1は、階調1以上の階調を表現する場合は常にSF1で点灯し、階調3以上の階調を表現する場合は常にSF2で点灯し、階調5以上の階調を表現する場合は常にSF3で点灯し、階調7以上の階調を表現する場合は常にSF4で点灯し、階調9以上の階調を表現する場合は常にSF5で点灯し、階調11以上の階調を表現する場合は常にSF6で点灯し、階調13以上の階調を表現する場合は常にSF7で点灯し、階調15以上の階調を表現する場合は常にSF8で点灯する。SP2についても同様である。

以上のように、各サブフレームで点灯させるサブ画素を選択することにより、17階調を表現することができる。

図32に示した駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。例えば、図32に示したサブ画素及びサブフレームの選択方法を用いて、画素Aでは、階調7を表示し、画素Bでは、階調8で表示しているとする。その場合の、各サブフレームにおける各サブ画素の点灯・非点灯の状態を、図33に示す。例えば、視線が動いたとすると、視線の追い方によって、あるときは階調が4(=1+1+1+1)と感じ、あるときは、階調が5(=1+1+1+1+1)と感じる。本来は、階調が7と8に見えるべきであるのに、階調が4や5に見えてしまい、擬似輪郭が発生してしまう。しかし、階調のずれが従来の駆動方法よりも小さくなるため、擬似輪郭が低減される。

なお、誤差拡散やディザ拡散などの画像処理技術を用いて、より多くの階調を表現してもよい。

なお、図32に示した例では、各サブ画素の面積を全て等しくし、かつ、各サブフレームの点灯期間の長さを全て等しくしたが、これに限定されない。

例えば、1つの画素を、各サブ画素の面積比が1:2となるように、2個のサブ画素(SP1、SP2)に分割するとともに、1フレームを、各サブフレームの点灯期間の長さが全て等しい8個のサブフレーム(SF1〜SF8)に分割した場合について説明する。この場合のサブ画素及びサブフレームの選択方法を、図34に示す。

ここで、各サブ画素の面積を、SP1=1、SP2=2、各サブフレームの点灯期間を、SF1=SF2=SF3=SF4=SF5=SF6=SF7=SF8=1とする。

なお、各サブ画素において、全てのサブフレームに対して、重ね合わせ時間階調方式を適用する。つまり、階調が大きくなるに従って、点灯するサブフレームが連続的に増えていくようにし、小さい階調において点灯しているサブフレームを、大きい階調においても点灯したままにする。

図34に示した例の場合、SP1は、階調1以上の階調を表現する場合は常にSF1で点灯し、階調4以上の階調を表現する場合は常にSF2で点灯し、階調7以上の階調を表現する場合は常にSF3で点灯し、階調10以上の階調を表現する場合は常にSF4で点灯し、階調13以上の階調を表現する場合は常にSF5で点灯し、階調16以上の階調を表現する場合は常にSF6で点灯し、階調19以上の階調を表現する場合は常にSF7で点灯し、階調22以上の階調を表現する場合は常にSF8で点灯する。SP2についても同様である。

以上のように、各サブフレームで点灯させるサブ画素を選択することにより、階調0から階調24のうち17個の階調を表現することができる。なお、階調0から階調24の中で表現できなかった残りの階調は、誤差拡散やディザ拡散などの画像処理技術を用いて表現する。これにより、階調0から階調24の25階調を表現することができる。

図34に示した駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。例えば、図34に示したサブ画素及びサブフレームの選択方法を用いて、画素Aでは、階調15を表示し、画素Bでは、階調16で表示しているとする。その場合の、各サブフレームにおける各サブ画素の点灯・非点灯の状態を、図35に示す。例えば、視線が動いたとすると、視線の追い方によって、あるときは階調が10(=2+2+2+1+1+2)と感じ、あるときは、階調が11(=1+2+2+2+2+1+1)と感じる。本来は、階調が15と16に見えるべきであるのに、階調が10や11に見えてしまい、擬似輪郭が発生してしまう。しかし、階調のずれが従来の駆動方法よりも小さくなるため、擬似輪郭が低減される。

なお、誤差拡散やディザ拡散などの画像処理技術を用いて、より多くの階調を表現してもよい。

また、別の例として、1つの画素を、各サブ画素の面積比が1:2となるように、2個のサブ画素(SP1、SP2)に分割するとともに、1フレームを、各サブフレームの点灯期間の比率が1:4:16となるように、3個のサブフレーム(SF1〜SF3)に分割し、さらに、3個のサブフレーム(SF1〜SF3)の中の2個のサブフレームを、さらに複数のサブフレームに分割した場合について説明する。この場合のサブ画素及びサブフレームの選択方法を図36に示す。なお、図36に示した例では、複数のサブフレームに分割するサブフレームをSF2、SF3としている。

ここで、各サブ画素の面積を、SP1=1、SP2=2、各サブフレームの点灯期間を、SF1=1、SF2=4、SF3=16とする。

図36に示した例は、SF2を2個のサブフレームに分割し、SF3を4個のサブフレームに分割する場合を示している。例えば、点灯期間4を有するSF2を、点灯期間2を有する2個のサブフレームSF21、SF22に分割する。また、点灯期間16を有するSF3を、点灯期間4を有する4個のサブフレームSF31、SF32、SF33、SF34に分割する。

これにより、1フレームは7個のサブフレームに分割され、各サブフレームの点灯期間は、SF1=1、SF21=2、SF22=2、SF31=4、SF32=4、SF33=4、SF34=4となる。

なお、各サブ画素において、全てのサブフレームに対して、重ね合わせ時間階調方式を適用する。つまり、階調が大きくなるに従って、点灯するサブフレームが連続的に増えていくようにし、小さい階調において点灯しているサブフレームを、大きい階調においても点灯したままにする。

図36に示した例の場合、SP1は、階調1以上の階調を表現する場合は常にSF1で点灯し、階調5以上の階調を表現する場合は常にSF21で点灯し、階調11以上の階調を表現する場合は常にSF22で点灯し、階調19以上の階調を表現する場合は常にSF31で点灯し、階調31以上の階調を表現する場合は常にSF32で点灯し、階調43以上の階調を表現する場合は常にSF33で点灯し、階調55以上の階調を表現する場合は常にSF34で点灯する。SP2についても同様である。

以上のように、各サブフレームで点灯させるサブ画素を選択することにより、階調0から階調63のうち17個の階調を表現することができる。なお、階調0から階調63の中で表現できなかった残りの階調は、誤差拡散やディザ拡散などの画像処理技術を用いて表現する。これにより、階調0から階調63の64階調を表現することができる。

なお、誤差拡散やディザ拡散などの画像処理技術を用いて、より多くの階調を表現してもよい。

このように、本実施形態の駆動方法を用いると、従来の駆動方法よりも擬似輪郭を低減させることができる。

なお、図32や図34に示した例のように、全てのサブフレームの点灯期間の長さを等しくすると、全てのサブフレームで消去動作を行う必要がなくなるため、消去動作を行うために消費される電力をなくすことができる。また、デューティー比を向上させることができ、輝度を上げることができる。また、デューティー比の向上により、発光素子にかかる電圧を小さくすることができる。従って、消費電力を低減でき、発光素子の劣化も少なくすることができる。

なお、本実施形態で述べた内容は、実施の形態1〜実施の形態2で述べた内容と自由に組み合わせて実施することができる。

(実施の形態4)

本実施形態では、本発明の表示装置の動作について、タイミングチャートを用いて説明する。

なお、本実施形態では、1つの画素を、各サブ画素の面積比が1:2となるように、2個のサブ画素(SP1、SP2)に分割するとともに、1フレームを、各サブフレームの点灯期間の比率が1:4:16となるように、3個のサブフレーム(SF1、SF2、SF3)に分割し、さらに、3個のサブフレーム(SF1〜SF3)の中の1個のサブフレームを、2個のサブフレームに分割した場合を例に挙げて説明する。具体例として、図1に示したサブ画素及びサブフレームの選択方法を用いた場合を例に挙げて説明する。

まず、画素に信号を書き込む期間と点灯する期間とが分離されている場合のタイミングチャートを図37に示す。

なお、タイミングチャートとは、1フレームでの画素の発光のタイミングを示す図であり、横方向は時間、縦方向は画素が配置されている行を示している。

まず、信号書き込み期間において、1画面分の信号を全画素に入力する。この間は、画素は点灯しない。信号書き込み期間が終了したのち、点灯期間が始まり、画素が点灯する。そのときの点灯期間の長さは、1である。次に、次のサブフレームが始まり、信号書き込み期間において、1画面分の信号を全画素に入力する。この間は、画素は点灯しない。信号書き込み期間が終了したのち、点灯期間が始まり、画素が点灯する。そのときの点灯期間の長さは、4である。

同様のことを繰り返すことにより、点灯期間の長さが、1、4、8、8という順序で配置される。

このように、画素に信号を書き込む期間と点灯する期間とが分離されている駆動方法は、プラズマディスプレイに適用することが好適である。なお、プラズマディスプレイに用いる場合は、初期化の動作などが必要になる。しかしながら、図37では、簡単のため、省略している。

また、この駆動方法は、ELディスプレイ(有機ELディスプレイ、無機ELディスプレイ又は無機と有機とを含む素子からなるディスプレイなど)やフィールドエミッションディスプレイやデジタル・マイクロミラー・デバイス(DMD)を用いたディスプレイなどに適用することも好適である。

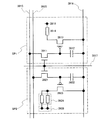

ここで、画素に信号を書き込む期間と点灯する期間とが分離されている駆動方法を実現するための画素構成を図38に示す。なお、図38では、各サブ画素の面積を発光素子の個数で表現している。従って、サブ画素1(SP1)には発光素子を1個、サブ画素2(SP2)には発光素子を2個記載している。

まず、図38に示した画素の構成について説明する。SP1は、第1の選択トランジスタ3811、第1の駆動トランジスタ3813、第1の保持容量3812、信号線3815、第1の電源線3816、第1の走査線3817、第1の発光素子3814、第2の電源線3818を有する。

第1の選択トランジスタ3811は、ゲート電極が、第1の走査線3817に接続され、第1の電極が、信号線3815に接続され、第2の電極が、第1の保持容量3812の第2の電極、及び第1の駆動トランジスタ3813のゲート電極と接続される。第1の保持容量3812は、第1の電極が、第1の電源線3816に接続される。第1の駆動トランジスタ3813は、第1の電極が、第1の電源線3816に接続され、第2の電極が、第1の発光素子3814の第1の電極に接続される。第1の発光素子3814は、第2の電極が、第2の電源線3818に接続される。

SP2は、第2の選択トランジスタ3821、第2の駆動トランジスタ3823、第2の保持容量3822、信号線3815、第1の電源線3816、第2の走査線3827、第2の発光素子3824、第3の電源線3828を有する。なお、SP2の各素子及び配線の接続は、SP1と同様であるため、説明を割愛する。

次に、図38に示した画素の動作について説明する。ここでは、SP1の動作について説明する。第1の走査線3817の電位を高くすることにより、第1の走査線3817を選択し、第1の選択トランジスタ3811をオン状態にして、信号線3815から信号を第1の保持容量3812に入力する。すると、その信号に応じて、第1の駆動トランジスタ3813の電流が制御され、第1の電源線3816から、第1の発光素子3814に電流が流れる。なお、SP2の動作については、SP1の動作と同様であるため、説明を割愛する。

このとき、第1及び第2の走査線のうち、どの走査線を選択するかによって、発光する発光素子の個数が変化する。例えば、第1の走査線3817のみを選択した場合は、第1の選択トランジスタ3811のみがオン状態となり、第1の駆動トランジスタ3813のみの電流が制御されるため、第1の発光素子3814のみが発光する。つまり、SP1のみが発光する。一方、第2の走査線3827のみを選択した場合は、第2の選択トランジスタ3821のみがオン状態となり、第2の駆動トランジスタ3823のみの電流が制御されるため、第2の発光素子3824のみが発光する。つまり、SP2のみが発光する。また、第1及び第2の走査線3817、3827の両方を選択すると、第1及び第2の選択トランジスタ3811、3821がオン状態となり、第1及び第2の駆動トランジスタ3813、3823の電流が制御されるため、第1及び第2の発光素子3814、3824の両方が発光する。つまり、SP1とSP2の両方が発光する。

なお、信号書き込み期間においては、第2及び第3の電源線3818、3828の電位を制御することにより、発光素子3814、3824に電圧が加わらないようにしておく。例えば、SP1の場合、第2の電源線3818をフローティングにすればよい。もしくは、第2の電源線3818の電位を信号線3815の電位よりも、第1の駆動トランジスタ3813の閾値電圧分だけ低くすればよい。また、第2の電源線3818の電位を信号線3815の電位と同程度、もしくはそれよりも高くしてもよい。その結果、信号書き込み期間において、発光素子3814が点灯することを避けることができる。なお、SP2についても同様である。

なお、第2の電源線3818と第3の電源線3828は、それぞれ別の配線でもよいし、共通の配線でもよい。

なお、1つの画素をm個(mはm≧2の整数)のサブ画素に分割する場合、図38に示した画素構成を実現するためには、1つの画素が有する走査線の本数を2本以上m本以下とし、m個のサブ画素のうち少なくとも1個のサブ画素が有する選択トランジスタを、他のサブ画素が有する選択トランジスタと異なる走査線と接続すればよい。

なお、図38は、走査線を複数設け、どの走査線を選択するかを制御して、発光させる発光素子の個数を変えることにより、階調を表現する場合の構成例であったが、信号線を複数設け、どの信号線にどのような信号を入力するかを制御して、発光させる発光素子の個数を変えることにより、階調を表現することも可能である。この場合の構成例を図39に示す。

まず、図39に示した画素の構成について説明する。SP1は、第1の選択トランジスタ3911、第1の駆動トランジスタ3913、第1の保持容量3912、第1の信号線3915、第1の電源線3916、走査線3917、第1の発光素子3914、第2の電源線3918を有する。

第1の選択トランジスタ3911は、ゲート電極が、走査線3917に接続され、第1の電極が、第1の信号線3915に接続され、第2の電極が、第1の保持容量3912の第2の電極、及び第1の駆動トランジスタ3913のゲート電極と接続される。第1の保持容量3912は、第1の電極が、第1の電源線3916に接続される。第1の駆動トランジスタ3913は、第1の電極が、第1の電源線3916に接続され、第2の電極が、第1の発光素子3914の第1の電極に接続される。第1の発光素子3914は、第2の電極が、第2の電源線3918に接続される。

SP2は、第2の選択トランジスタ3921、第2の駆動トランジスタ3923、第2の保持容量3922、第2の信号線3925、第1の電源線3916、走査線3917、第2の発光素子3924、第3の電源線3928を有する。SP2の各素子及び配線の接続は、SP1と同様であるため、説明を割愛する。

次に、図39に示した画素の動作について説明する。ここでは、SP1の動作について説明する。走査線3917の電位を高くすることにより、走査線3917を選択し、第1の選択トランジスタ3911をオン状態にして、第1の信号線3915からビデオ信号を第1の保持容量3912に入力する。すると、そのビデオ信号に応じて、第1の駆動トランジスタ3913の電流が制御され、第1の電源線3916から第1の発光素子3914に電流が流れる。なお、SP2の動作については、SP1の動作と同様であるため、説明を割愛する。

このとき、第1及び第2の信号線に入力するビデオ信号によって、発光する発光素子の個数が変化する。例えば、第1の信号線3915にLowの信号を入力し、第2の信号線3925にHighの信号を入力すると、第1の駆動トランジスタ3913のみがオン状態となるため、第1の発光素子3914のみが発光する。つまり、SP1のみが発光する。一方、第1の信号線3915にHighの信号を入力し、第2の信号線3925にLowの信号を入力すると、第2の駆動トランジスタ3923のみがオン状態となるため、第2の発光素子3924のみが発光する。つまり、SP2のみが発光する。また、第1及び第2の信号線3915、3925にLowの信号を入力すると、第1及び第2の駆動トランジスタ3913、3923が共にオン状態となるため、第1及び第2の発光素子3914、3924が発光する。つまり、SP1とSP2の両方が発光する。

ここで、第1及び第2の信号線3915、3925に入力するビデオ信号の電圧を制御することにより、第1及び第2の発光素子3914、3924に流れる電流を制御することができる。その結果、各サブ画素の輝度を変えることができ、階調を表現することができる。例えば、点灯期間1を有するSF1で、面積1を有するSP1が点灯した場合、発光強度は1であるが、第1の信号線3915に入力するビデオ信号の電圧の大きさを変えることにより、第1の発光素子3914の輝度を変えることができる。これにより、サブ画素の面積及びサブフレームの点灯期間の長さを用いて表現できる階調数よりも、さらに多くの階調を表現することができる。また、サブ画素の面積及びサブフレームの点灯期間の長さに加えて、各サブ画素が有する発光素子に印加する電圧によって階調を表現することにより、同じ階調数を表現するのに必要なサブ画素の個数及びサブフレーム数をより少なくすることができる。これにより、画素部の開口率を上げることができる。また、デューティー比を向上させることができ、輝度を上げることができる。また、デューティー比の向上により、発光素子にかかる電圧を小さくすることができる。従って、消費電力を低減でき、発光素子の劣化も少なくすることができる。

なお、1つの画素をm個(mはm≧2の整数)のサブ画素に分割する場合、図39に示した画素構成を実現するためには、1つの画素が有する信号線の本数を2本以上m本以下とし、m個のサブ画素のうち少なくとも1個のサブ画素が有する選択トランジスタを、他のサブ画素が有する選択トランジスタと異なる信号線と接続すればよい。

なお、図38、図39では、各サブ画素には共通の電源線(第1の電源線3816、3916)が接続されていたが、図38、図39における第1の電源線に相当する電源線を複数設け、サブ画素に加える電源電圧を変えてもよい。例えば、図38において、第1の電源線に相当する電源線を2本にした場合の構成例を図40に示す。

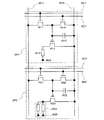

まず、図40に示した画素の構成について説明する。SP1は、第1の選択トランジスタ4011、第1の駆動トランジスタ4013、第1の保持容量4012、信号線4015、第1の電源線4016、第1の走査線4017、第1の発光素子4014、第2の電源線4018を有する。

第1の選択トランジスタ4011は、ゲート電極が、第1の走査線4017に接続され、第1の電極が、信号線4015に接続され、第2の電極が、第1の保持容量4012の第2の電極、及び第1の駆動トランジスタ4013のゲート電極と接続される。第1の保持容量4012は、第1の電極が、第1の電源線4016に接続される。第1の駆動トランジスタ4013は、第1の電極が、第1の電源線4016に接続され、第2の電極が、第1の発光素子4014の第1の電極に接続される。第1の発光素子4014は、第2の電極が、第2の電源線4018に接続される。

SP2は、第2の選択トランジスタ4021、第2の駆動トランジスタ4023、第2の保持容量4022、信号線4015、第2の走査線4027、第2の発光素子4024、第3の電源線4028、第4の電源線4026を有する。なお、SP2の各素子及び配線の接続は、SP1と同様であるため、説明を割愛する。

ここで、第1及び第4の電源線4016、4026に印加する電圧を制御することにより、第1及び第2の発光素子4014、4024に流れる電流を制御することができる。その結果、各サブ画素の輝度を変えることができ、階調を表現することができる。例えば、点灯期間1を有するSF1で、面積1を有するSP1が点灯した場合、発光強度は1であるが、第1の電源線4016に印加する電圧の大きさを変えることにより、第1の発光素子4014の輝度を変えることができる。これにより、サブ画素の面積及びサブフレームの点灯期間の長さを用いて表現できる階調数よりも、さらに多くの階調を表現することができる。また、サブ画素の面積及びサブフレームの点灯期間の長さに加えて、各サブ画素が有する発光素子に印加する電圧によって階調を表現することにより、同じ階調数を表現するのに必要なサブ画素の個数及びサブフレーム数をより少なくすることができる。これにより、画素部の開口率を上げることができる。また、デューティー比を向上させることができ、輝度を上げることができる。また、デューティー比の向上により、発光素子にかかる電圧を小さくすることができる。従って、消費電力を低減でき、発光素子の劣化も少なくすることができる。

なお、1つの画素をm個(mはm≧2の整数)のサブ画素に分割する場合、図40に示した画素構成を実現するためには、1つの画素が有する図38、図39における第1の電源線に相当する電源線の本数を2本以上m本以下とし、m個のサブ画素のうち少なくとも1個のサブ画素が有する駆動トランジスタを、他のサブ画素が有する駆動トランジスタと異なる前記電源線と接続すればよい。

次に、画素に信号を書き込む期間と点灯する期間とが分離されていない場合のタイミングチャートを図41に示す。各行において、信号書き込み動作を行うと、すぐに点灯期間が開始する。

ある行において、信号を書き込み、所定の点灯期間が終了したのち、次のサブフレームにおける信号の書き込み動作を開始する。これを繰り返すことにより、点灯期間の長さが、1、4、8、8という順序で配置される。

このようにすることにより、信号の書き込み動作が遅くても、1フレーム内に複数のサブフレームを配置することが可能となる。

このような駆動方法は、プラズマディスプレイに適用することが好適である。なお、プラズマディスプレイに用いる場合は、初期化の動作などが必要になるが、図41では、簡単のため、省略している。

また、この駆動方法は、ELディスプレイやフィールドエミッションディスプレイやデジタル・マイクロミラー・デバイス(DMD)を用いたディスプレイなどに適用することも好適である。

ここで、画素に信号を書き込む期間と点灯する期間とが分離されていない駆動方法を実現するための画素構成を図42に示す。なお、このような駆動方法を実現するためには、同時に複数の行を選択することが可能でなければならない。

まず、図42に示した画素の構成について説明する。SP1は、第1の選択トランジスタ4211、第2の選択トランジスタ4221、第1の駆動トランジスタ4213、第1の保持容量4212、第1の信号線4215、第2の信号線4225、第1の電源線4216、第1の走査線4217、第2の走査線4227、第1の発光素子4214、第2の電源線4218を有する。

第1の選択トランジスタ4211は、ゲート電極が、第1の走査線4217に接続され、第1の電極が、第1の信号線4215に接続され、第2の電極が、第2の選択トランジスタ4221の第2の電極、及び第1の保持容量4212の第2の電極、及び第1の駆動トランジスタ4213のゲート電極と接続される。第2の選択トランジスタ4221は、ゲート電極が、第2の走査線4227に接続され、第1の電極が、第2の信号線4225に接続される。第1の保持容量4212は、第1の電極が、第1の電源線4216に接続される。第1の駆動トランジスタ4213は、第1の電極が、第1の電源線4216に接続され、第2の電極が、第1の発光素子4214の第1の電極に接続される。第1の発光素子4214は、第2の電極が、第2の電源線4218に接続される。

SP2は、第3の選択トランジスタ4231、第4の選択トランジスタ4241、第2の駆動トランジスタ4223、第2の保持容量4222、第1の信号線4215、第2の信号線4225、第1の電源線4216、第3の走査線4237、第4の走査線4247、第2の発光素子4224、第3の電源線4228を有する。SP2の各素子及び配線の接続は、SP1と同様であるため、説明を割愛する。

次に、図42に示した画素の動作について説明する。ここでは、SP1の動作について説明する。第1の走査線4217の電位を高くすることにより、第1の走査線4217を選択し、第1の選択トランジスタ4211をオン状態にして、第1の信号線4215から信号を第1の保持容量4212に入力する。すると、その信号に応じて、第1の駆動トランジスタ4213の電流が制御され、第1の電源線4216から、第1の発光素子4214に電流が流れる。同様に、第2の走査線4227の電位を高くすることにより、第2の走査線4227を選択し、第2の選択トランジスタ4221をオン状態にして、第2の信号線4225から信号を第1の保持容量4212に入力する。すると、その信号に応じて、第1の駆動トランジスタ4213の電流が制御され、第1の電源線4216から、第1の発光素子4214に電流が流れる。なお、SP2の動作については、SP1の動作と同様であるため、説明を割愛する。

第1の走査線4217と第2の走査線4227とは、別々に制御できる。同様に、第3の走査線4237と第4の走査線4247とは、別々に制御できる。また、第1の信号線4215と第2の信号線4225とは、別々に制御できる。よって、同時に2行分の画素に信号を入力することが可能であるため、図41のような駆動方法が実現できる。

なお、図38の画素構成を用いて、図41のような駆動方法を実現することも可能である。このとき、1ゲート選択期間を複数のサブゲート選択期間に分割するという方法を用いる。まず、図43に示すように、1ゲート選択期間を複数(図43では2つ)のサブゲート選択期間に分割する。そして、各サブゲート選択期間内で、各々の走査線の電位を高くすることにより、各々の走査線を選択し、その時に対応する信号を信号線3815に入力する。例えば、ある1ゲート選択期間において、前半のサブゲート選択期間ではi行目を選択し、後半のサブゲート選択期間ではj行目を選択する。すると、1ゲート選択期間において、あたかも同時に2行分を選択したかのように動作させることが可能となる。

なお、このような駆動方法の詳細については、例えば、特開2001−324958号公報等に記載されており、その内容を本願と組み合わせて適用することができる。

なお、図42では、走査線を複数設けた例を示したが、信号線を1本にし、第1〜第4の選択トランジスタの第1の電極を信号線に接続してもよい。また、図42における第1の電源線に相当する電源線を複数設けてもよい。

次に、画素の信号を消去する動作を行う場合のタイミングチャートを図44に示す。各行において、信号書き込み動作を行い、次の信号書き込み動作が来る前に、画素の信号を消去する。このようにすることにより、点灯期間の長さを容易に制御できるようになる。

ある行において、信号を書き込み、所定の点灯期間が終了したのち、次のサブフレームにおける信号の書き込み動作を開始する。もし、点灯期間が短い場合は、信号消去動作を行い、強制的に非点灯状態にする。このようなことを繰り返すことにより、点灯期間の長さが、1、4、8、8という順序で配置される。

なお、図44では、点灯期間が1と4の場合において、信号消去動作を行っているが、これに限定されない。他の点灯期間においても、消去動作を行ってもよい。

このようにすることにより、信号の書き込み動作が遅くても、1フレーム内に複数のサブフレームを配置することが可能となる。また、消去動作を行う場合は、消去用のデータをビデオ信号と同様に取得する必要がないため、信号線駆動回路の駆動周波数も低減できる。

このような駆動方法は、プラズマディスプレイに適用することが好適である。なお、プラズマディスプレイに用いる場合は、初期化の動作などが必要になるが、図44では、簡単のため、省略している。

また、この駆動方法は、ELディスプレイやフィールドエミッションディスプレイやデジタル・マイクロミラー・デバイス(DMD)を用いたディスプレイなどに適用することも好適である。

ここで、消去動作を行う場合の画素構成を図45に示す。図45に示す画素は、消去トランジスタを用いて消去動作を行う場合の構成例である。

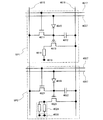

まず、図45に示した画素の構成について説明する。SP1は、第1の選択トランジスタ4511、第1の駆動トランジスタ4513、第1の消去トランジスタ4519、第1の保持容量4512、信号線4515、第1の電源線4516、第1の走査線4517、第2の走査線4527、第1の発光素子4514、第2の電源線4518を有する。

第1の選択トランジスタ4511は、ゲート電極が、第1の走査線4517に接続され、第1の電極が、信号線4515に接続され、第2の電極が、第1の消去トランジスタ4519の第2の電極、及び第1の保持容量4512の第2の電極、及び第1の駆動トランジスタ4513のゲート電極と接続される。第1の消去トランジスタ4519は、ゲート電極が、第2の走査線4527に接続され、第1の電極が、第1の電源線4516に接続される。第1の保持容量4512は、第1の電極が、第1の電源線4516に接続される。第1の駆動トランジスタ4513は、第1の電極が、第1の電源線4516に接続され、第2の電極が、第1の発光素子4514の第1の電極に接続される。第1の発光素子4514は、第2の電極が、第2の電源線4518に接続される。

SP2は、第2の選択トランジスタ4521、第2の駆動トランジスタ4523、第2の消去トランジスタ4529、第2の保持容量4522、信号線4515、第1の電源線4516、第3の走査線4537、第4の走査線4547、第2の発光素子4524、第3の電源線4528を有する。SP2の各素子及び配線の接続は、SP1と同様であるため、説明を割愛する。

次に、図45に示した画素の動作について説明する。ここでは、SP1の動作について説明する。第1の走査線4517の電位を高くすることにより、第1の走査線4517を選択し、第1の選択トランジスタ4511をオン状態にして、信号線4515から信号を第1の保持容量4512に入力する。すると、その信号に応じて、第1の駆動トランジスタ4513の電流が制御され、第1の電源線4516から第1の発光素子4514に電流が流れる。

信号を消去したい場合は、第2の走査線4527の電位を高くすることにより、第2の走査線4527を選択し、第1の消去トランジスタ4519をオン状態にして、第1の駆動トランジスタ4513がオフ状態になるようにする。すると、第1の発光素子4514には、電流が流れないようになる。その結果、非点灯期間を作ることができ、点灯期間の長さを自由に制御できるようになる。

なお、SP2の動作は、SP1の動作と同様であるため、説明を割愛する。

図45では、消去トランジスタ4519、4529を用いて消去動作を行ったが、別の方法を用いることもできる。なぜなら、強制的に非点灯期間をつくればよいので、発光素子4514、4524に電流が供給されないようにすればよいからである。よって、第1の電源線4516から、発光素子4514、4524を通って、第2及び第3の電源線4518、4528に電流が流れる経路中に、スイッチを配置して、そのスイッチのオン・オフを制御して、非点灯期間を作ればよい。あるいは、駆動トランジスタ4513、4523のゲート・ソース間電圧を制御して、駆動トランジスタが強制的にオフになるようにすればよい。

ここで、駆動トランジスタを強制的にオフにする場合の画素構成の例を図46に示す。図46に示した画素は、消去ダイオードを用いて駆動トランジスタを強制的にオフにする場合の構成例である。

まず、図46に示した画素の構成について説明する。SP1は、第1の選択トランジスタ4611、第1の駆動トランジスタ4613、第1の保持容量4612、信号線4615、第1の電源線4616、第1の走査線4617、第2の走査線4627、第1の発光素子4614、第2の電源線4618、第1の消去ダイオード4619を有する。

第1の選択トランジスタ4611は、ゲート電極が、第1の走査線4617に接続され、第1の電極が、信号線4615に接続され、第2の電極が、第1の消去ダイオード4619の第2の電極、及び第1の保持容量4612の第2の電極、及び第1の駆動トランジスタ4613のゲート電極と接続される。第1の消去ダイオード4619は、第1の電極が、第2の走査線4627に接続される。第1の保持容量4612は、第1の電極が、第1の電源線4616に接続される。第1の駆動トランジスタ4613は、第1の電極が、第1の電源線4616に接続され、第2の電極が、第1の発光素子4614の第1の電極に接続される。第1の発光素子4614は、第2の電極が、第2の電源線4618に接続される。

SP2は、第2の選択トランジスタ4621、第2の駆動トランジスタ4623、第2の保持容量4622、信号線4615、第1の電源線4616、第3の走査線4637、第4の走査線4647、第2の発光素子4624、第3の電源線4628、第2の消去ダイオード4629を有する。SP2の各素子及び配線の接続は、SP1と同様であるため、説明を割愛する。

次に、図46に示した画素の動作について説明する。ここでは、SP1の動作について説明する。第1の走査線4617の電位を高くすることにより、第1の走査線4617を選択し、第1の選択トランジスタ4611をオン状態にして、信号線4615から信号を第1の保持容量4612に入力する。すると、その信号に応じて、第1の駆動トランジスタ4613の電流が制御され、第1の電源線4616から第1の発光素子4614に電流が流れる。

信号を消去したい場合は、第2の走査線4627の電位を高くすることにより、第2の走査線4627を選択し、第1の消去ダイオード4619がオンして、第2の走査線4627から第1の駆動トランジスタ4613のゲート電極へ電流が流れるようにする。その結果、第1の駆動トランジスタ4613がオフ状態になる。すると、第1の電源線4616から第1の発光素子4614に電流が流れないようになる。その結果、非点灯期間を作ることができ、点灯期間の長さを自由に制御できるようになる。

信号を保持しておきたい場合は、第2の走査線4627の電位を低くすることにより、第2の走査線4627を非選択しておく。すると、第1の消去ダイオード4619がオフするので、第1の駆動トランジスタ4613のゲート電位は保持される。

なお、SP2の動作は、SP1の動作と同様であるため、説明を割愛する。

なお、消去ダイオード4619、4629は、整流性がある素子であれば、なんでもよい。PN型ダイオードでもよいし、PIN型ダイオードでもよいし、ショットキー型ダイオードでもよいし、ツェナー型ダイオードでもよい。

また、ダイオード接続(ゲートとドレインを接続)されたトランジスタを用いてもよい。その場合の回路図を図47に示す。第1及び第2の消去ダイオード4619、4629として、ダイオード接続されたトランジスタ4719、4729を用いている。なお、図47では、ダイオード接続されたトランジスタとしてNチャネル型を用いているが、これに限定されない。Pチャネル型を用いてもよい。

なお、さらに別の方法として、図38の画素構成を用いて、図44のような駆動方法を実現することも可能である。この場合、1ゲート選択期間を複数のサブゲート選択期間に分割するという方法を用いる。まず、図43に示すように、1ゲート選択期間を複数(図43では2つ)のサブゲート選択期間に分割する。そして、各サブゲート選択期間内で、各々の走査線の電位を高くすることにより、各々の走査線を選択し、その時に対応する信号(ビデオ信号と消去するための信号)を信号線3815に入力する。例えば、i行目の画素には信号を書き込み、j行目の画素では信号を消去する場合、ある1ゲート選択期間において、前半のサブゲート選択期間ではi行目を選択し、後半のサブゲート選択期間ではj行目を選択する。そして、i行目が選択されているときは、i行目の画素に入力すべきビデオ信号を信号線3815に入力する。一方、j行目が選択されているときは、j行目の画素の駆動トランジスタがオフするような信号を信号線3815に入力する。すると、1ゲート選択期間において、あたかも同時に2行分を選択し、信号書き込み動作と信号消去動作を行ったかのように動作させることが可能となる。

なお、このような駆動方法の詳細については、例えば、特開2001−324958号公報等に記載されており、その内容を本願と組み合わせて適用することができる。

なお、図45〜図47では、走査線を複数設けた例を示したが、信号線を複数設けてもよいし、図45〜図47における第1の電源線に相当する電源線を複数設けてもよい。

なお、本実施形態で示したタイミングチャートや画素構成や駆動方法は、一例であり、これに限定されない。様々なタイミングチャートや画素構成や駆動方法に適用することが可能である。また、本実施形態で示した画素構成において、トランジスタの極性は、これに限定されない。

なお、本実施形態において、1フレーム内に、点灯期間や信号書き込み期間や非点灯期間が配置されていたが、これに限定されない。それ以外の動作期間が配置されていてもよい。例えば、発光素子に加える電圧を、通常とは逆の極性のものにするような期間、いわゆる、逆バイアス期間を設けてもよい。逆バイアス期間を設けることにより、発光素子の信頼性が向上する場合がある。

なお、本実施形態で示した画素構成において、保持容量は、トランジスタの寄生容量で代用することにより省略することができる。

なお、本実施形態で述べた内容は、実施の形態1〜実施の形態3で述べた内容と自由に組み合わせて実施することができる。

(実施の形態5)

本実施形態では、本発明の表示装置における画素のレイアウトについて述べる。例として、図38に示した画素構成について、そのレイアウト図を図48に示す。なお、図48中に付した符号は、図38に付した符号に対応している。なお、レイアウトの仕方は、図48に限定されない。

図48に示したレイアウト図では、第1及び第2の選択トランジスタ3811、3821、第1及び第2の駆動トランジスタ3813、3823、第1及び第2の保持容量3812、3822、第1の発光素子3814の電極3819及び第2の発光素子3824の電極3829、信号線3815、第1の電源線3816、第1及び第2の走査線3817、3827が配置されている。そして、第1の発光素子3814の電極3819と第2の発光素子3824の電極3829の面積比は1:2となっている。

信号線3815、第1の電源線3816は、第2の配線によって形成され、第1及び第2の走査線3817、3827は、第1の配線によって形成されている。

トランジスタがトップゲート構造の場合は、基板、半導体層、ゲート絶縁膜、第1の配線、層間絶縁膜、第2の配線、の順で膜が構成される。また、トランジスタがボトムゲート構造の場合は、基板、第1の配線、ゲート絶縁膜、半導体層、層間絶縁膜、第2の配線、の順で膜が構成される。

なお、第1及び第2の選択トランジスタ3811、3821、第1及び第2の駆動トランジスタ3813、3823の構造は、様々な形態をとることができる。例えば、ゲート電極が2個以上になっているマルチゲート構造を用いてもよい。マルチゲート構造にすると、チャネル領域が直列に接続されるような構成となるため、複数のトランジスタが直列に接続されたような構成となる。第1及び第2の駆動トランジスタ3813、3823をマルチゲート構造にした場合のレイアウト図を、図49に示す。マルチゲート構造にすることにより、オフ電流を低減することや、トランジスタの耐圧を向上させて信頼性を良くすることや、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。また、チャネルの上下にゲート電極が配置されている構造でもよい。チャネルの上下にゲート電極が配置されている構造にすることにより、チャネル領域が増えるため、電流値を大きくすることや、空乏層ができやすくなってS値を小さくすることができる。チャネルの上下にゲート電極が配置されると、複数のトランジスタが並列に接続されたような構成となる。また、チャネルの上にゲート電極が配置されている構造でもよいし、チャネルの下にゲート電極が配置されている構造でもよいし、正スタガ構造であってもよいし、逆スタガ構造でもよいし、チャネル領域が複数の領域に分かれていてもよいし、並列に接続されていてもよいし、直列に接続されていてもよい。また、チャネル(もしくはその一部)にソース電極やドレイン電極が重なっていてもよい。チャネル(もしくはその一部)にソース電極やドレイン電極が重なっている構造にすることにより、チャネルの一部に電荷がたまって、動作が不安定になることを防ぐことができる。また、LDD領域があってもよい。LDD領域を設けることにより、オフ電流を低減することや、トランジスタの耐圧を向上させて信頼性を良くすることや、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。

なお、配線や電極は、アルミニウム(Al)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)、ネオジウム(Nd)、クロム(Cr)、ニッケル(Ni)、白金(Pt)、金(Au)、銀(Ag)、銅(Cu)、マグネシウム(Mg)、スカンジウム(Sc)、コバルト(Co)、亜鉛(Zn)、ニオブ(Nb)、シリコン(Si)、リン(P)、ボロン(B)、ヒ素(As)、ガリウム(Ga)、インジウム(In)、錫(Sn)、酸素(O)で構成された群から選ばれた一つ又は複数の元素、もしくは、前記群から選ばれた一つ又は複数の元素を成分とする化合物や合金材料(例えば、インジウム錫酸化物(Indium Tin Oxide(ITO))、インジウム亜鉛酸化物(酸化インジウム酸化亜鉛ともいう(Indium Zinc Oxide(IZO)))、酸化珪素を添加したインジウム錫酸化物(本明細書では「ITSO」と呼ぶ)、酸化亜鉛(ZnO)、アルミネオジウム(Al−Nd)、マグネシウム銀(Mg−Ag)など)、もしくは、これらの化合物を組み合わせた物質などを有して形成される。もしくは、それらとシリコンの化合物(シリサイド)(例えば、アルミシリコン、モリブデンシリコン、ニッケルシリサイドなど)や、それらと窒素の化合物(例えば、窒化チタン、窒化タンタル、窒化モリブデン等)を有して形成される。なお、シリコン(Si)には、N型不純物(リンなど)やP型不純物(ボロンなど)を多く含んでいてもよい。これらの不純物を含むことにより、導電率が向上することや、通常の導体と同様な振る舞いをするので、配線や電極として利用しやすくなったりする。なお、シリコンは、単結晶でもよいし、多結晶(ポリシリコン)でもよいし、非晶質(アモルファスシリコン)でもよい。単結晶シリコンや多結晶シリコンを用いることにより、抵抗を小さくすることができる。非晶質シリコンを用いることにより、簡単な製造工程で作ることができる。なお、アルミニウムや銀は、導電率が高いため、信号遅延を低減することができ、エッチングしやすいので、微細加工を行うことができる。なお、銅は、導電率が高いため、信号遅延を低減することができる。なお、モリブデンは、ITOやIZOなどの酸化物半導体や、シリコンと接触しても、材料が不良を起こすなどの問題が生じることなく製造できたり、エッチングがしやすかったり、耐熱性が高いため、望ましい。なお、チタンは、ITOやIZOなどの酸化物半導体や、シリコンと接触しても、材料が不良を起こすなどの問題が生じることなく製造できたり、耐熱性が高いため、望ましい。なお、タングステンは、耐熱性が高いため、望ましい。なお、ネオジウムは、耐熱性が高いため、望ましい。特に、ネオジウムとアルミニウムとの合金にすると、耐熱性が向上し、アルミニウムがヒロックをおこしにくくなるため、望ましい。なお、シリコンは、トランジスタが有する半導体層と同時に形成できたり、耐熱性が高いため、望ましい。なお、インジウム錫酸化物(ITO)、インジウム亜鉛酸化物(IZO)、酸化珪素を添加したインジウム錫酸化物(ITSO)、酸化亜鉛(ZnO)、シリコン(Si)は、透光性を有しているため、光を透過させるような部分に用いることができるため、望ましい。たとえば、画素電極や共通電極として用いることができる。

なお、これらが単層で配線や電極を形成していてもよいし、多層構造になっていてもよい。単層構造で形成することにより、製造工程を簡略化することができ、工程日数を少なくでき、コストを低減することができる。また、多層構造にすることにより、それぞれの材料のメリットを生かし、デメリットを低減させ、性能の良い配線や電極を形成することができる。たとえば、抵抗の低い材料(アルミニウムなど)を多層構造の中に含むようにすることにより、配線の低抵抗化を図ることができる。また、耐熱性が高い材料を含むようにすれば、例えば、耐熱性が弱いが、別のメリットを有する材料を、耐熱性が高い材料で挟むような積層構造にすることにより、配線や電極全体として、耐熱性を高くすることができる。例えば、アルミニウムを含む層を、モリブデンやチタンを含む層で挟んだような形にした積層構造にすると望ましい。また、別の材料の配線や電極などと直接接するような部分がある場合、お互いに悪影響を及ぼすことがある。例えば、一方の材料が他方の材料の中に入っていって、性質を変えてしまい、本来の目的を果たせなくなったり、製造するときに、問題が生じて、正常に製造できなくなったりすることがある。そのような場合、ある層を別の層で挟んだり、覆ったりすることにより、問題を解決することができる。例えば、インジウム錫酸化物(ITO)と、アルミニウムを接触させたい場合は、間に、チタンやモリブデンを挟むことが望ましい。また、シリコンとアルミニウムを接触させたい場合は、間に、チタンやモリブデンを挟むことが望ましい。

なお、R(赤)、G(緑)、B(青)の各画素において、画素の総発光面積を変えてもよい。この場合の実施例を図50に示す。

図50に示した例では、各画素が2個のサブ画素から構成されている。また、信号線5015、第1の電源線5016、第1及び第2の走査線5017、5027が配置されている。また、図50において、各サブ画素の面積の大きさが、各サブ画素の発光面積に対応している。

図50では、画素の総発光面積が大きい順にG、R、Bとなっている。これにより、R、G、Bの適切な色バランスを実現でき、より高精細なカラー表示が可能となる。また、消費電力を低減させたり、発光素子の寿命を伸ばすことができる。

また、R、G、B、W(白)構成において、RGB部のサブ画素の個数とW部のサブ画素の個数とが異なってもよい。この場合の実施例を図51に示す。

図51に示した例では、RGB部は2個のサブ画素に分割されており、W部は3個のサブ画素に分割されている。また、信号線5115、第1の電源線5116、第1の走査線5117、第2の走査線5127、第3の走査線5137が配置されている。

図51に示したように、RGB部のサブ画素とW部のサブ画素とをそれぞれ異なる個数にすることにより、より高精細な白表示が可能となる。

なお、本実施形態で述べた内容は、実施の形態1〜実施の形態4で述べた内容と自由に組み合わせて実施することができる。

(実施の形態6)

本実施形態では、表示装置における信号線駆動回路や走査線駆動回路などの構成とその動作について説明する。本実施形態では、1つの画素を2個のサブ画素(SP1、SP2)に分割した場合を例に説明する。

まず、画素に信号を書き込む期間と点灯する期間とが分離されている場合について説明する。ここでは、画素構成として、図38に示した画素構成を用いた場合を例に挙げて説明する。この場合の表示装置の構成例を図52に示す。

図52に示した表示装置は、画素部5201、第1及び第2の走査線駆動回路5202、5203、信号線駆動回路5204を有しており、第1の走査線駆動回路5202と第1の走査線3817とが接続され、第2の走査線駆動回路5203と第2の走査線3827とが接続され、信号線駆動回路5204と信号線3815とが接続される。なお、第1及び第2の走査線、及び信号線に付した符号は、図38に付した符号に対応している。

まずは、走査線駆動回路について説明する。第1の走査線駆動回路5202は、サブ画素1(SP1)に接続された第1の走査線3817に順次選択信号を出力するための回路である。また、第2の走査線駆動回路5203は、サブ画素2(SP2)に接続された第2の走査線3827に順次選択信号を出力するための回路である。これにより、SP1、SP2に選択信号が書き込まれる。なお、一般に、1つの画素をm個(mはm≧2の整数)のサブ画素に分割した場合、m個の走査線駆動回路を設ければよい。

ここで、第1及び第2の走査線駆動回路5202、5203の構成例を図53に示す。第1及び第2の走査線駆動回路5202、5203は、主に、シフトレジスタ5301や増幅回路5302などを有している。

次に、図53に示した第1及び第2の走査線駆動回路5202、5203の動作を簡単に説明する。シフトレジスタ5301には、クロック信号(G−CLK)、スタートパルス(G−SP)、クロック反転信号(G−CLKB)が入力され、これらの信号のタイミングに従って、順次サンプリングパルスが出力される。出力されたサンプリングパルスは、増幅回路5302で増幅され、各走査線から画素部5201へ入力される。

なお、増幅回路5302の構成として、バッファ回路を有してもよいし、レベルシフタ回路を有してもよい。また、走査線駆動回路には、シフトレジスタ5301や増幅回路5302の他に、パルス幅制御回路などが配置されてもよい。

次に、信号線駆動回路について説明する。信号線駆動回路5204は、SP1、SP2に接続された信号線3815にビデオ信号を順次出力するための回路である。信号線駆動回路5204から出力されたビデオ信号は、画素部5201に入力される。画素部5201では、ビデオ信号に従って、画素の発光状態を制御することにより、画像を表示する。

ここで、信号線駆動回路5204の構成例を図54に示す。図54(A)は、線順次駆動で画素に信号を供給する場合の信号線駆動回路5204の一例を示している。この場合の信号線駆動回路5204は、主に、シフトレジスタ5401、第1のラッチ回路5402、第2のラッチ回路5403、増幅回路5404などを有している。なお、増幅回路5404の構成として、バッファ回路を有してもよいし、レベルシフタ回路を有してもよいし、デジタル信号をアナログに変換する機能を有する回路を有してもよいし、ガンマ補正を行う機能を有する回路を有してもよい。

また、画素が有している発光素子に電流(ビデオ信号)を出力する回路、すなわち、電流源回路を有してもよい。

次に、図54(A)に示した信号線駆動回路5204の動作を簡単に説明する。シフトレジスタ5401には、クロック信号(S−CLK)、スタートパルス(S−SP)、クロック反転信号(S−CLKB)が入力され、これらの信号のタイミングに従って、順次サンプリングパルスが出力される。

シフトレジスタ5401より出力されたサンプリングパルスは、第1のラッチ回路5402に入力される。第1のラッチ回路5402には、ビデオ信号線より、ビデオ信号が電圧Vdataで入力されており、サンプリングパルスが入力されるタイミングに従って、各列でビデオ信号を保持していく。

第1のラッチ回路5402において、最終列までビデオ信号の保持が完了すると、水平帰線期間中に、ラッチ制御線よりラッチ信号が入力され、第1のラッチ回路5402に保持されていたビデオ信号は、一斉に第2のラッチ回路5403に転送される。その後、第2のラッチ回路5403に保持されたビデオ信号は、1行分が同時に増幅回路5404へと入力される。そして、増幅回路5404にて、ビデオ信号電圧Vdataの振幅が増幅され、ビデオ信号が各信号線から画素部5201へ入力される。

第2のラッチ回路5403に保持されたビデオ信号が増幅回路5404に入力され、そして、画素部5201に入力されている間、シフトレジスタ5401においては再びサンプリングパルスが出力される。つまり、同時に2つの動作が行われる。これにより、線順次駆動が可能となる。以後、この動作を繰り返す。

なお、点順次駆動で画素に信号を供給する場合もある。その場合の信号線駆動回路5204の一例を図54(B)に示す。この場合の信号線駆動回路5204は、シフトレジスタ5401とサンプリング回路5405などを有している。シフトレジスタ5401から、サンプリングパルスがサンプリング回路5405に出力される。また、サンプリング回路5405には、ビデオ信号線より、ビデオ信号が電圧Vdataで入力され、サンプリングパルスに応じて、順次画素部5201へビデオ信号が出力される。これにより、点順次駆動が可能となる。

なお、信号線駆動回路やその一部(電流源回路や増幅回路など)は、画素部5201と同一基板上に存在せず、例えば、外付けのICチップを用いて構成されることもある。

以上のような走査線駆動回路及び信号線駆動回路を用いることにより、画素に信号を書き込む期間と点灯する期間とが分離されている場合の駆動を実現できる。

なお、図52に示した表示装置は、走査線駆動回路が複数設けられていたが、画素構成によっては、信号線駆動回路が複数設けられる場合もある。例えば、画素構成として、図39に示した画素構成を用いた場合の表示装置の構成例を、図55に示す。

図55に示した表示装置は、画素部5501、走査線駆動回路5502、第1及び第2の信号線駆動回路5503、5504を有しており、走査線駆動回路5502と走査線3917とが接続され、第1の信号線駆動回路5503と第1の信号線3915とが接続され、第2の信号線駆動回路5504と第2の信号線3925とが接続される。なお、第1及び第2の信号線、及び走査線に付した符号は、図39に付した符号に対応している。なお、第1及び第2の信号線駆動回路5503、5504、及び走査線駆動回路5502の構成は、図53、図54で説明したものと同様であるため、ここでは説明を割愛する。

ここで、走査線駆動回路5502は、SP1、SP2に接続された走査線3917に順次選択信号を出力するための回路である。これにより、SP1、SP2に選択信号が書き込まれる。

第1の信号線駆動回路5503は、SP1に接続された第1の信号線3915にビデオ信号を順次出力するための回路である。第1の信号線駆動回路5503から出力されたビデオ信号は、SP1に入力される。また、第2の信号線駆動回路5504は、SP2に接続された第2の信号線3925にビデオ信号を順次出力するための回路である。第2の信号線駆動回路5504から出力されたビデオ信号は、SP2に入力される。画素部5501では、ビデオ信号に従って、画素の発光状態を制御することにより、画像を表示する。なお、一般に、1つの画素をm個(mはm≧2の整数)のサブ画素に分割した場合、m個の信号線駆動回路を設ければよい。

以上のような走査線駆動回路及び信号線駆動回路を用いることにより、画素に信号を書き込む期間と点灯する期間とが分離されている場合の駆動を実現できる。

次に、画素の信号を消去する動作を行う場合について説明する。ここでは、画素構成として、図45に示した画素構成を用いた場合を例に挙げて説明する。この場合の表示装置の構成例を図56に示す。

図56に示した表示装置は、画素部5601、第1〜第4の走査線駆動回路5602〜5605、信号線駆動回路5606を有しており、第1の走査線駆動回路5602と第1の走査線4517とが接続され、第2の走査線駆動回路5603と第2の走査線4527とが接続され、第3の走査線駆動回路5604と第3の走査線4537とが接続され、第4の走査線駆動回路5605と第4の走査線4547とが接続され、信号線駆動回路5606と信号線4515とが接続される。なお、第1〜第4の走査線、及び信号線に付した符号は、図45に付した符号に対応している。なお、第1〜第4の走査線駆動回路5602〜5605及び信号線駆動回路5606の構成は、図53、図54で説明したものと同様であるため、ここでは説明を割愛する。

ここで、第1及び第2の走査線駆動回路5602、5603は、SP1に接続された第1及び第2の走査線4517、4527を駆動させるための回路である。ここで、第1の走査線駆動回路5602は、SP1に接続された第1の走査線4517に順次選択信号を出力する。一方、第2の走査線駆動回路5603は、SP1に接続された第2の走査線4527に順次消去信号を出力する。これにより、SP1に選択信号や消去信号が書き込まれる。

同様に、第3及び第4の走査線駆動回路5604、5605は、SP2に接続された第3及び第4の走査線4537、4547を駆動させるための回路である。ここで、第3の走査線駆動回路5604は、SP2に接続された第3の走査線4537に順次選択信号を出力する。一方、第4の走査線駆動回路5605は、SP2に接続された第4の走査線4547に順次消去信号を出力する。これにより、SP2に選択信号や消去信号が書き込まれる。

信号線駆動回路5606は、SP1、SP2に接続された信号線4515にビデオ信号を順次出力するための回路である。信号線駆動回路5606から出力されたビデオ信号は、画素部5601に入力される。

以上のような走査線駆動回路及び信号線駆動回路を用いることにより、画素の信号を消去する動作を行う場合の駆動を実現できる。

なお、表示装置、信号線駆動回路、走査線駆動回路などの構成は、図52〜図56に限定されない。

なお、本発明におけるトランジスタは、どのようなタイプのトランジスタでもよいし、どのような基板上に形成されていてもよい。従って、図52〜図56で示したような回路が、全てガラス基板上に形成されていてもよいし、プラスチック基板に形成されていてもよいし、単結晶基板に形成されていてもよいし、SOI基板に形成されていてもよいし、どのような基板上に形成されていてもよい。あるいは、図52〜図56における回路の一部が、ある基板に形成されており、図52〜図56における回路の別の一部が、別の基板に形成されていてもよい。つまり、図52〜図56における回路の全てが同じ基板上に形成されていなくてもよい。例えば、図52〜図56において、画素部と走査線駆動回路とは、ガラス基板上にトランジスタを用いて形成し、信号線駆動回路(もしくはその一部)は、単結晶基板に形成し、そのICチップをCOG(Chip On Glass)で接続してガラス基板上に配置してもよい。あるいは、そのICチップをTAB(Tape Automated Bonding)やプリント基板を用いてガラス基板と接続してもよい。このように、回路の一部が同じ基板に形成されていることにより、部品点数を減らしてコストを低減することや、回路部品との接続点数を減らして信頼性を向上させたりすることができる。また、駆動電圧が高い部分や駆動周波数が高い部分は、消費電力が大きくなってしまうので、そのような部分は同じ基板に形成しないようにすれば、消費電力の向上を防ぐことができる。

なお、本実施形態で述べた内容は、実施の形態1〜実施の形態5で述べた内容と自由に組み合わせて実施することができる。

(実施の形態7)

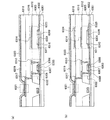

本実施形態では、本発明の表示装置に用いる表示パネルについて図57などを用いて説明する。なお、図57(a)は、表示パネルを示す上面図、図57(b)は図57(a)をA−A’で切断した断面図である。点線で示された信号線駆動回路5701、画素部5702、第1の走査線駆動回路5703、第2の走査線駆動回路5706を有する。また、封止基板5704、シール材5705を有し、シール材5705で囲まれた内側は、空間5707になっている。

なお、配線5708は第1の走査線駆動回路5703、第2の走査線駆動回路5706及び信号線駆動回路5701に入力される信号を伝送するための配線であり、外部入力端子となるFPC5709からビデオ信号、クロック信号、スタート信号等を受け取る。FPC5709と表示パネルとの接合部上にはICチップ(メモリ回路や、バッファ回路などが形成された半導体チップ)5719がCOG(Chip On Glass)等で実装されている。なお、ここではFPCしか図示されていないが、このFPCにはプリント配線基板(PWB)が取り付けられていてもよい。

次に、断面構造について図57(b)を用いて説明する。基板5710上には画素部5702とその周辺駆動回路(第1の走査線駆動回路5703、第2の走査線駆動回路5706及び信号線駆動回路5701)が形成されているが、ここでは、信号線駆動回路5701と、画素部5702が示されている。

なお、信号線駆動回路5701は、トランジスタ5720やトランジスタ5721など複数のトランジスタで構成されている。また、本実施形態では、基板上に周辺駆動回路を一体形成した表示パネルを示すが、必ずしもその必要はなく、周辺駆動回路の全部もしくは一部をICチップなどに形成し、COGなどで実装してもよい。

また、画素部5702は、選択トランジスタ5711と、駆動トランジスタ5712とを含む画素を構成する複数の回路を有している。なお、駆動トランジスタ5712のソース電極は第1の電極5713と接続されている。また、第1の電極5713の端部を覆って絶縁物5714が形成されている。ここでは、ポジ型の感光性アクリル樹脂膜を用いることにより形成する。

また、カバレッジを良好なものとするため、絶縁物5714の上端部または下端部に曲率を有する曲面が形成されるようにする。例えば、絶縁物5714の材料としてポジ型の感光性アクリルを用いた場合、絶縁物5714の上端部のみに曲率半径(0.2μm〜3μm)を有する曲面を持たせることが好ましい。また、絶縁物5714として、感光性の光によってエッチャントに不溶解性となるネガ型、あるいは光によってエッチャントに溶解性となるポジ型のいずれも使用することができる。

第1の電極5713上には、有機化合物を含む層5716、及び第2の電極5717がそれぞれ形成されている。ここで、陽極として機能する第1の電極5713に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、ITO(インジウム錫酸化物)膜、インジウム亜鉛酸化物(IZO)膜、窒化チタン膜、クロム膜、タングステン膜、Zn膜、Pt膜などの単層膜の他、窒化チタンとアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜と窒化チタン膜との3層構造等を用いることができる。なお、積層構造とすると、配線としての抵抗も低く、良好なオーミックコンタクトがとれ、さらに陽極として機能させることができる。

また、有機化合物を含む層5716は、蒸着マスクを用いた蒸着法、またはインクジェット法によって形成される。有機化合物を含む層5716には、元素周期表第4族金属錯体をその一部に用いることとし、その他、組み合わせて用いることのできる材料としては、低分子系材料であっても高分子系材料であってもよい。また、有機化合物を含む層に用いる材料としては、通常、有機化合物を単層もしくは積層で用いる場合が多いが、本実施形態においては、有機化合物からなる膜の一部に無機化合物を用いる構成も含めることとする。さらに、公知の三重項材料を用いることも可能である。

さらに、有機化合物を含む層5716上に形成される、陰極である第2の電極5717に用いる材料としては、仕事関数の小さい材料(Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF2、または窒化カルシウム)を用いればよい。なお、有機化合物を含む層5716で生じた光が第2の電極5717を透過させる場合には、第2の電極5717として、膜厚を薄くした金属薄膜と、透明導電膜(ITO(インジウム錫酸化物))、酸化インジウム酸化亜鉛合金(In2O3―ZnO)、酸化亜鉛(ZnO)等)との積層を用いるのがよい。

さらに、シール材5705で封止基板5704を基板5710と貼り合わせることにより、基板5710、封止基板5704、及びシール材5705で囲まれた空間5707に発光素子5718が備えられた構造になっている。なお、空間5707には、不活性気体(窒素やアルゴン等)が充填される場合の他、シール材5705で充填される構成も含むものとする。

なお、シール材5705にはエポキシ系樹脂を用いるのが好ましい。また、これらの材料はできるだけ水分や酸素を透過しない材料であることが望ましい。また、封止基板5704に用いる材料としてガラス基板や石英基板の他、FRP(Fiberglass−Reinforced Plastics)、PVF(ポリビニルフロライド)、マイラー(登録商標)、ポリエステルまたはアクリル等からなるプラスチック基板を用いることができる。

以上のようにして、本発明の画素構成を有する表示パネルを得ることができる。

図57に示すように、信号線駆動回路5701、画素部5702、第1の走査線駆動回路5703及び第2の走査線駆動回路5706を一体形成することで、表示装置の低コスト化が図れる。なお、信号線駆動回路5701、画素部5702、第1の走査線駆動回路5703及び第2の走査線駆動回路5706に用いられるトランジスタを単極性とすることで作製工程の簡略化が図れるためさらなる低コスト化が図れる。また、信号線駆動回路5701、画素部5702、第1の走査線駆動回路5703及び第2の走査線駆動回路5706に用いられるトランジスタの半導体層にアモルファスシリコンを適用することでさらなる低コスト化を図ることができる。

なお、表示パネルの構成としては、図57(a)に示したように信号線駆動回路5701、画素部5702、第1の走査線駆動回路5703及び第2の走査線駆動回路5706を一体形成した構成に限定されず、信号線駆動回路5701に相当する信号線駆動回路をICチップ上に形成して、COG等で表示パネルに実装した構成としてもよい。

つまり、駆動回路の高速動作が要求される信号線駆動回路のみを、CMOS等を用いてICチップに形成し、低消費電力化を図る。また、ICチップはシリコンウエハ等の半導体チップとすることで、より高速動作かつ低消費電力化を図れる。

そして、走査線駆動回路を画素部と一体形成することで、低コスト化が図れる。なお、この走査線駆動回路及び画素部は単極性のトランジスタで構成することでさらなる低コスト化が図れる。画素部の有する画素の構成としては実施の形態4で示した構成を適用することができる。また、トランジスタの半導体層にアモルファスシリコンを用いることで、作製工程が簡略化し、さらなる低コスト化が図れる。

こうして、高精細な表示装置の低コスト化が図れる。また、FPC5709と基板5710との接続部において機能回路(メモリやバッファ)が形成されたICチップを実装することで基板面積を有効利用することができる。

また、図57(a)の信号線駆動回路5701、第1の走査線駆動回路5703及び第2の走査線駆動回路5706に相当する信号線駆動回路、第1の走査線駆動回路及び第2の走査線駆動回路をICチップ上に形成して、COG等で表示パネルに実装した構成としてもよい。この場合には高精細な表示装置をより低消費電力にすることが可能である。よって、より消費電力が少ない表示装置とするため、画素部に用いられるトランジスタの半導体層にはポリシリコンを用いることが望ましい。

また、画素部5702のトランジスタの半導体層にアモルファスシリコンを用いることにより低コスト化を図ることができる。さらに、大型の表示パネルを作製することも可能となる。

なお、走査線駆動回路及び信号線駆動回路は、画素の行方向及び列方向に設けることに限定されない。

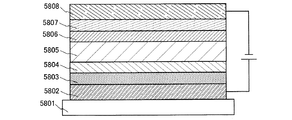

次に、発光素子5718に適用可能な発光素子の例を図58に示す。

基板5801の上に陽極5802、正孔注入材料からなる正孔注入層5803、その上に正孔輸送材料からなる正孔輸送層5804、発光層5805、電子輸送材料からなる電子輸送層5806、電子注入材料からなる電子注入層5807、そして陰極5808を積層させた素子構造である。ここで、発光層5805は、一種類の発光材料のみから形成されることもあるが、2種類以上の材料から形成されてもよい。また本発明の素子の構造は、この構造に限定されない。

また、図58で示した各機能層を積層した積層構造の他、高分子化合物を用いた素子、発光層に三重項励起状態から発光する三重項発光材料を利用した高効率素子など、バリエーションは多岐にわたる。ホールブロック層によってキャリヤの再結合領域を制御し、発光領域を2つの領域に分けることによって得られる白色発光素子などにも応用可能である。

次に、図58に示す本発明の素子作製方法について説明する。まず、陽極5802(ITO(インジウム錫酸化物))を有する基板5801に正孔注入材料、正孔輸送材料、発光材料を順に蒸着する。次に電子輸送材料、電子注入材料を蒸着し、最後に陰極5808を蒸着で形成する。

次に、正孔注入材料、正孔輸送材料、電子輸送材料、電子注入材料、発光材料の材料に好適な材料を以下に列挙する。

正孔注入材料としては、有機化合物であればポルフィリン系の化合物や、フタロシアニン(以下「H2Pc」と記す)、銅フタロシアニン(以下「CuPc」と記す)などが有効である。また、使用する正孔輸送材料よりもイオン化ポテンシャルの値が小さく、かつ、正孔輸送機能をもつ材料であれば、これも正孔注入材料として使用できる。導電性高分子化合物に化学ドーピングを施した材料もあり、ポリスチレンスルホン酸(以下「PSS」と記す)をドープしたポリエチレンジオキシチオフェン(以下「PEDOT」と記す)や、ポリアニリンなどが挙げられる。また、絶縁体の高分子化合物も陽極の平坦化の点で有効であり、ポリイミド(以下「PI」と記す)がよく用いられる。さらに、無機化合物も用いられ、金や白金などの金属薄膜の他、酸化アルミニウム(以下「アルミナ」と記す)の超薄膜などがある。

正孔輸送材料として最も広く用いられているのは、芳香族アミン系(すなわち、ベンゼン環−窒素の結合を有するもの)の化合物である。広く用いられている材料として、4,4’−ビス(ジフェニルアミノ)−ビフェニル(以下、「TAD」と記す)や、その誘導体である4,4’−ビス[N−(3−メチルフェニル)−N−フェニル−アミノ]−ビフェニル(以下、「TPD」と記す)、4,4’−ビス[N−(1−ナフチル)−N−フェニル−アミノ]−ビフェニル(以下、「α−NPD」と記す)がある。4,4’,4”−トリス(N,N− ジフェニル−アミノ)−トリフェニルアミン(以下、「TDATA」と記す)、4,4’,4”−トリス[N−(3−メチルフェニル)−N− フェニル−アミノ]−トリフェニルアミン(以下、「MTDATA」と記す)などのスターバースト型芳香族アミン化合物が挙げられる。

電子輸送材料としては、金属錯体がよく用いられ、トリス(8−キノリノラト)アルミニウム(以下、「Alq3」と記す)、BAlq、トリス(4−メチル−8−キノリノラト)アルミニウム(以下、「Almq」と記す)、ビス(10−ヒドロキシベンゾ[h]−キノリナト)ベリリウム(以下、「Bebq」と記す)などのキノリン骨格またはベンゾキノリン骨格を有する金属錯体などがある。また、ビス[2−(2−ヒドロキシフェニル)−ベンゾオキサゾラト]亜鉛(以下、「Zn(BOX)2」と記す)、ビス[2−(2−ヒドロキシフェニル)−ベンゾチアゾラト]亜鉛(以下、「Zn(BTZ)2」と記す)などのオキサゾール系、チアゾール系配位子を有する金属錯体もある。さらに、金属錯体以外にも、2−(4−ビフェニリル)−5−(4−tert−ブチルフェニル)−1,3,4−オキサジアゾール(以下、「PBD」と記す)、OXD−7などのオキサジアゾール誘導体、TAZ、3−(4−tert−ブチルフェニル)−4−(4−エチルフェニル)−5−(4−ビフェニリル)−1、2、4−トリアゾール(以下、「p−EtTAZ」と記す)などのトリアゾール誘導体、バソフェナントロリン(以下、「BPhen」と記す)、BCPなどのフェナントロリン誘導体が電子輸送性を有する。

電子注入材料としては、上で述べた電子輸送材料を用いることができる。その他に、フッ化カルシウム、フッ化リチウム、フッ化セシウムなどの金属ハロゲン化物や、酸化リチウムなどのアルカリ金属酸化物のような絶縁体の、超薄膜がよく用いられる。また、リチウムアセチルアセトネート(以下、「Li(acac)」と記す)や8−キノリノラト−リチウム(以下、「Liq」と記す)などのアルカリ金属錯体も有効である。

発光材料としては、先に述べたAlq3、Almq、BeBq、BAlq、Zn(BOX)2、Zn(BTZ)2などの金属錯体の他、各種蛍光色素が有効である。蛍光色素としては、青色の4,4’−ビス(2,2 − ジフェニル−ビニル)−ビフェニルや、赤橙色の4−(ジシアノメチレン)−2−メチル−6−(p−ジメチルアミノスチリル)−4H−ピランなどがある。また、三重項発光材料も可能であり、白金ないしはイリジウムを中心金属とする錯体が主体である。三重項発光材料として、トリス(2−フェニルピリジン)イリジウム、ビス(2−(4’−トリル)ピリジナト−N,C2’)アセチルアセトナトイリジウム(以下「acacIr(tpy)2」と記す)、 2,3,7,8,12,13,17,18−オクタエチル−21H,23Hポルフィリン−白金などが知られている。

以上で述べたような各機能を有する材料を、各々組み合わせ、高信頼性の発光素子を作製することができる。

また、図58とは逆の順番に層を形成した発光素子を用いることもできる。つまり、基板5801の上に陰極5808、電子注入材料からなる電子注入層5807、その上に電子輸送材料からなる電子輸送層5806、発光層5805、正孔輸送材料からなる正孔輸送層5804、正孔注入材料からなる正孔注入層5803、そして陽極5802を積層させた素子構造である。

また、発光素子は発光を取り出すために少なくとも陽極又は陰極の一方が透明であればよい。そして、基板上にトランジスタ及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、本発明の画素構成はどの射出構造の発光素子にも適用することができる。

まず、上面射出構造の発光素子について、図59(a)を用いて説明する。

基板5900上に駆動トランジスタ5901が形成され、駆動トランジスタ5901のソース電極に接して第1の電極5902が形成され、その上に有機化合物を含む層5903と第2の電極5904が形成されている。

また、第1の電極5902は発光素子の陽極である。そして、第2の電極5904は発光素子の陰極である。つまり、第1の電極5902と第2の電極5904とで有機化合物を含む層5903が挟まれているところが発光素子となる。

また、ここで、陽極として機能する第1の電極5902に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、窒化チタン膜、クロム膜、タングステン膜、Zn膜、Pt膜などの単層膜の他、窒化チタンとアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜と窒化チタン膜との3層構造等を用いることができる。なお、積層構造とすると、配線としての抵抗も低く、良好なオーミックコンタクトがとれ、さらに陽極として機能させることができる。光を反射する金属膜を用いることで光を透過させない陽極を形成することができる。

また、陰極として機能する第2の電極5904に用いる材料としては、仕事関数の小さい材料(Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF2、または窒化カルシウム)からなる金属薄膜と、透明導電膜(ITO(インジウム錫酸化物)、インジウム亜鉛酸化物(IZO)、酸化亜鉛(ZnO)等)との積層を用いるのがよい。こうして薄い金属薄膜と、透明性を有する透明導電膜を用いることで光を透過させることが可能な陰極を形成することができる。

こうして、図59(a)の矢印に示すように発光素子からの光を上面に取り出すことが可能になる。つまり、図57の表示パネルに適用した場合には、封止基板5704側に光が射出することになる。従って、上面射出構造の発光素子を表示装置に用いる場合には、封止基板5704は光透過性を有する基板を用いる。

また、光学フィルムを設ける場合には、封止基板5704に光学フィルムを設ければよい。

なお、第1の電極5902を、陰極として機能するMgAg、MgIn、AlLi等の仕事関数の小さい材料からなる金属膜を用いて形成することもできる。この場合には、第2の電極5904にはITO(インジウム錫酸化物)膜、インジウム亜鉛酸化物(IZO)などの透明導電膜を用いることができる。よって、この構成によれば、上面射出の透過率を高くすることができる。

次に、下面射出構造の発光素子について、図59(b)を用いて説明する。射出構造以外は図59(a)と同じ構造の発光素子であるため同じ符号を用いて説明する。

ここで、陽極として機能する第1の電極5902に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、ITO(インジウム錫酸化物)膜、インジウム亜鉛酸化物(IZO)膜などの透明導電膜を用いることができる。透明性を有する透明導電膜を用いることで光を透過させることが可能な陽極を形成することができる。

また、陰極として機能する第2の電極5904に用いる材料としては、仕事関数の小さい材料(Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF2、または窒化カルシウム)からなる金属膜を用いることができる。こうして、光を反射する金属膜を用いることで光が透過しない陰極を形成することができる。

こうして、図59(b)の矢印に示すように発光素子からの光を下面に取り出すことが可能になる。つまり、図57の表示パネルに適用した場合には、基板5710側に光が射出することになる。従って、下面射出構造の発光素子を表示装置に用いる場合には、基板5710は光透過性を有する基板を用いる。

また、光学フィルムを設ける場合には、基板5710に光学フィルムを設ければよい。

次に、両面射出構造の発光素子について、図59(c)を用いて説明する。射出構造以外は図59(a)と同じ構造の発光素子であるため同じ符号を用いて説明する。

ここで、陽極として機能する第1の電極5902に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、ITO(インジウム錫酸化物)膜、インジウム亜鉛酸化物(IZO)膜などの透明導電膜を用いることができる。透明性を有する透明導電膜を用いることで光を透過させることが可能な陽極を形成することができる。

また、陰極として機能する第2の電極5904に用いる材料としては、仕事関数の小さい材料(Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF2、または窒化カルシウム)からなる金属薄膜と、透明導電膜(ITO(インジウム錫酸化物)、酸化インジウム酸化亜鉛合金(In2O3―ZnO)、酸化亜鉛(ZnO)等)との積層を用いるのがよい。こうして薄い金属薄膜と、透明性を有する透明導電膜を用いることで光を透過させることが可能な陰極を形成することができる。

こうして、図59(c)の矢印に示すように発光素子からの光を両面に取り出すことが可能になる。つまり、図57の表示パネルに適用した場合には、基板5710側と封止基板5704側に光が射出することになる。従って、両面射出構造の発光素子を表示装置に用いる場合には、基板5710及び封止基板5704は、ともに光透過性を有する基板を用いる。

また、光学フィルムを設ける場合には、基板5710及び封止基板5704の両方に光学フィルムを設ければよい。

また、白色の発光素子とカラーフィルターを用いてフルカラー表示を実現する表示装置にも本発明を適用することが可能である。

図60に示すように、基板6000上に下地膜6002が形成され、下地膜6002の上に駆動トランジスタ6001が形成され、駆動トランジスタ6001のソース電極に接して第1の電極6003が形成され、その上に有機化合物を含む層6004と第2の電極6005が形成されている。

また、第1の電極6003は発光素子の陽極である。そして、第2の電極6005は発光素子の陰極である。つまり、第1の電極6003と第2の電極6005とで有機化合物を含む層6004が挟まれているところが発光素子となる。図60の構成では白色光を発光する。そして、発光素子の上部に赤色のカラーフィルター6006R、緑色のカラーフィルター6006G、青色のカラーフィルター6006Bを設けられており、フルカラー表示を行うことができる。また、これらのカラーフィルターを隔離するブラックマトリクス(BMともいう)6007が設けられている。

上述した発光素子の構成は組み合わせて用いることができ、本発明の表示装置に適宜用いることができる。また、上述した表示パネルの構成や、発光素子は例示であり、上述した構成と異なる他の構成を有する表示装置に適用することもできる。

次に、表示パネルの画素部の部分断面図を示す。

まず、トランジスタの半導体層にポリシリコン(p−Si:H)膜を用いた場合について、図61、図62及び図63を用いて説明する。

ここで、半導体層は、例えば基板上にアモルファスシリコン(a−Si)膜を公知の成膜法で形成する。なお、アモルファスシリコン膜に限定する必要はなく、非晶質構造を含む半導体膜(微結晶半導体膜を含む)であればよい。さらに非晶質シリコンゲルマニウム膜などの非晶質構造を含む化合物半導体膜でもよい。

そして、アモルファスシリコン膜をレーザー結晶化法や、RTAやファーネスアニール炉を用いた熱結晶化法や、結晶化を助長する金属元素を用いた熱結晶化法などにより結晶化させる。もちろん、これらを組み合わせて行ってもよい。

上述した結晶化によって、非晶質半導体膜に部分的に結晶化された領域が形成される。

さらに、部分的に結晶性が高められた結晶性半導体膜を所望の形状にパターンを形成して、結晶化された領域から島状の半導体膜を形成する。この半導体膜をトランジスタの半導体層に用いる。

図61(a)に示すように、基板6101上に下地膜6102が形成され、その上に半導体層が形成されている。半導体層は、駆動トランジスタ6118のチャネル形成領域6103、LDD領域6104及びソース領域またはドレイン領域となる不純物領域6105、並びに容量素子6119の下部電極となるチャネル形成領域6106、LDD領域6107及び不純物領域6108を有する。なお、チャネル形成領域6103及びチャネル形成領域6106はチャネルドープが行われていてもよい。

基板はガラス基板、石英基板、セラミック基板などを用いることができる。また、下地膜6102としては、窒化アルミニウム(AlN)や酸化珪素(SiO2)、酸化窒化珪素(SiOxNy)などの単層やこれらの積層を用いることができる。

半導体層上には、ゲート絶縁膜6109を介してゲート電極6110及び容量素子6119の上部電極6111が形成されている。

容量素子6119及び駆動トランジスタ6118を覆って層間絶縁膜6112が形成され、層間絶縁膜6112上に、コンタクトホールを介して配線6113が不純物領域6105と接している。配線6113に接して画素電極6114が形成され、画素電極6114の端部及び配線6113を覆って絶縁物6115が形成されている。ここでは、ポジ型の感光性アクリル樹脂膜を用いることにより形成する。そして、画素電極6114上に有機化合物を含む層6116及び対向電極6117が形成され、画素電極6114と対向電極6117とで有機化合物を含む層6116が挟まれた領域に、発光素子6120が形成されている。

また、図61(b)に示すように、容量素子6119の下部電極の一部を構成するLDD領域が、容量素子6119の上部電極6111と重なるような領域6121を設けてもよい。なお、図61(a)と共通する箇所は共通の符号を用い、説明は省略する。

また、図62(a)に示すように、容量素子6123は、駆動トランジスタ6118の不純物領域6105と接する配線6113と同じ層に形成された第2の上部電極6122を有していてもよい。なお、図61(a)と共通する箇所は共通の符号を用い、説明は省略する。第2の上部電極6122は不純物領域6108と接しているため、上部電極6111とチャネル形成領域6106とでゲート絶縁膜6109を挟みこんで構成される第1の容量素子と、上部電極6111と第2の上部電極6122とで層間絶縁膜6112を挟みこんで構成される第2の容量素子と、が並列に接続され、第1の容量素子と第2の容量素子からなる容量素子6123が形成される。この容量素子6123の容量は、第1の容量素子と第2の容量素子の容量を加算した合成容量であるため、小さい面積で大きな容量の容量素子を形成することができる。つまり、本発明の画素構成の容量素子として用いるとより開口率の向上が図れる。

また、図62(b)に示すような容量素子の構成としてもよい。基板6201上に下地膜6202が形成され、その上に半導体層が形成されている。半導体層は、駆動トランジスタ6218のチャネル形成領域6203、LDD領域6204及びソース領域又はドレイン領域となる不純物領域6205を有する。なお、チャネル形成領域6203はチャネルドープが行われていてもよい。

基板はガラス基板、石英基板、セラミック基板などを用いることができる。また、下地膜6202としては、窒化アルミニウム(AlN)や酸化珪素(SiO2)、酸化窒化珪素(SiOxNy)などの単層やこれらの積層を用いることができる。

半導体層上には、ゲート絶縁膜6206を介してゲート電極6207及び第1の電極6208が形成されている。

駆動トランジスタ6218及び第1の電極6208を覆って第1の層間絶縁膜6209が形成され、第1の層間絶縁膜6209上に、コンタクトホールを介して配線6210が不純物領域6205と接している。また、配線6210と同層に、配線6210と同じ材料からなる第2の電極6211が形成される。

さらに、配線6210及び第2の電極6211を覆うように第2の層間絶縁膜6212が形成され、第2の層間絶縁膜6212上に、コンタクトホールを介して配線6210と接して画素電極6213が形成されている。また、画素電極6213と同層に、画素電極6213と同じ材料からなる第3の電極6214が形成されている。また、画素電極6213の端部及び第3の電極6214を覆って絶縁物6215が形成されている。絶縁物6215は、例えば、ポジ型の感光性アクリル樹脂膜を用いることができる。ここで、第1の電極6208、第2の電極6211及び第3の電極6214からなる容量素子6219が形成される。

画素電極6213上に有機化合物を含む層6216及び対向電極6217が形成され、画素電極6213と対向電極6217とで有機化合物を含む層6216が挟まれた領域に、発光素子6220が形成されている。

上述したように、結晶性半導体膜を半導体層に用いたトランジスタの構成は図61及び図62に示したような構成が挙げられる。なお、図61及び図62に示したトランジスタの構造は、トップゲート構造のトランジスタの一例である。つまり、LDD領域はゲート電極と重なっていてもよいし、ゲート電極と重ならなくてもよいし、またはLDD領域の一部の領域が重なっていてもよい。さらに、ゲート電極はテーパー形状でもよく、ゲート電極のテーパー部の下部にLDD領域が自己整合的に設けられていてもよい。また、ゲート電極は2つに限定されず、3つ以上のマルチゲート構造でもよいし、1つのゲート電極でもよい。

本発明の画素を構成するトランジスタの半導体層(チャネル形成領域やソース領域やドレイン領域など)に結晶性半導体膜を用いることで、走査線駆動回路及び信号線駆動回路を画素部と一体形成することが容易になる。また、信号線駆動回路の一部を画素部と一体形成し、一部はICチップ上に形成して図57の表示パネルに示すようにCOG等で実装してもよい。このような構成とすることで、製造コストの削減を図ることができる。

また、半導体層にポリシリコン(p−Si:H)を用いたトランジスタの構成として、基板と半導体層の間にゲート電極が挟まれた構造、つまり、半導体層の下にゲート電極が位置するボトムゲート構造のトランジスタを適用してもよい。ここで、ボトムゲート構造のトランジスタを適用した表示パネルの画素部の部分断面図を図63に示す。

図63(a)に示すように、基板6301上に下地膜6302が形成されている。さらに下地膜6302上にゲート電極6303が形成されている。また、ゲート電極6303と同層に、ゲート電極6303と同じ材料からなる第1の電極6304が形成されている。ゲート電極6303の材料には、リンが添加された多結晶シリコンを用いることができる。多結晶シリコンの他に、金属とシリコンの化合物であるシリサイドでもよい。

ゲート電極6303及び第1の電極6304を覆うように、ゲート絶縁膜6305が形成されている。ゲート絶縁膜6305としては、酸化珪素膜や窒化珪素膜などが用いられる。

ゲート絶縁膜6305上に、半導体層が形成されている。半導体層は駆動トランジスタ6322のチャネル形成領域6306、LDD領域6307及びソース領域又はドレイン領域となる不純物領域6308、並びに容量素子6323の第2の電極となるチャネル形成領域6309、LDD領域6310及び不純物領域6311を有する。なお、チャネル形成領域6306及びチャネル形成領域6309はチャネルドープが行われていてもよい。

基板はガラス基板、石英基板、セラミック基板などを用いることができる。また、下地膜6302としては、窒化アルミニウム(AlN)や酸化珪素(SiO2)、酸化窒化珪素(SiOxNy)などの単層やこれらの積層を用いることができる。

半導体層を覆って第1の層間絶縁膜6312が形成され、第1の層間絶縁膜6312上に、コンタクトホールを介して配線6313が不純物領域6308と接している。また、配線6313と同層に、配線6313と同じ材料で第3の電極6314が形成されている。第1の電極6304、第2の電極、第3の電極6314によって容量素子6323が構成されている。

また、第1の層間絶縁膜6312には開口部6315が形成されている。駆動トランジスタ6322、容量素子6323及び開口部6315を覆うように第2の層間絶縁膜6316が形成され、第2の層間絶縁膜6316上に、コンタクトホールを介して画素電極6317が形成されている。また、画素電極6317の端部を覆って絶縁物6318が形成されている。例えば、ポジ型の感光性アクリル樹脂膜を用いることができる。そして、画素電極6317上に有機化合物を含む層6319及び対向電極6320が形成され、画素電極6317と対向電極6320とで有機化合物を含む層6319が挟まれた領域に、発光素子6321が形成されている。そして、発光素子6321の下部に開口部6315が位置している。つまり、発光素子6321からの発光を基板側から取り出すときには、開口部6315を有するため、透過率を高めることができる。

また、図63(a)において、画素電極6317と同層に、同じ材料を用いて第4の電極6324を形成して、図63(b)のような構成としてもよい。すると、第1の電極6304、第2の電極、第3の電極6314及び第4の電極6324によって構成される容量素子6325を形成することができる。

次に、トランジスタの半導体層にアモルファスシリコン(a−Si:H)膜を用いた場合について、図64、図65及び図66を用いて説明する。

アモルファスシリコンを半導体層に用いたトップゲート構造のトランジスタを適用した表示パネルの画素部の部分断面図を図64に示す。図64(a)に示すように、基板6401上に下地膜6402が形成されている。さらに、下地膜6402上に画素電極6403が形成されている。また、画素電極6403と同層に、画素電極6403と同じ材料からなる第1の電極6404が形成されている。

基板はガラス基板、石英基板、セラミック基板などを用いることができる。また、下地膜6402としては、窒化アルミニウム(AlN)や酸化珪素(SiO2)、酸化窒化珪素(SiOxNy)などの単層やこれらの積層を用いることができる。

下地膜6402上に配線6405及び配線6406が形成され、画素電極6403の端部が配線6405で覆われている。配線6405及び配線6406の上部に、N型の導電型を有するN型半導体層6407及びN型半導体層6408が形成されている。また、配線6405と配線6406の間であって、下地膜6402上に半導体層6409が形成されている。そして、半導体層6409の一部は、N型半導体層6407及びN型半導体層6408上にまで延長されている。なお、この半導体層6409はアモルファスシリコン(a−Si:H)、微結晶半導体(μc−Si:H)等の非結晶性を有する半導体膜で形成されている。

半導体層6409上に、ゲート絶縁膜6410が形成されている。また、ゲート絶縁膜6410と同層に、ゲート絶縁膜6410と同じ材料からなる絶縁膜6411が第1の電極6404上にも形成されている。なお、ゲート絶縁膜6410としては、酸化珪素膜や窒化珪素膜などが用いられる。

ゲート絶縁膜6410上に、ゲート電極6412が形成されている。また、ゲート電極6412と同層に、ゲート電極6412と同じ材料からなる第2の電極6413が、第1の電極6404上に絶縁膜6411を介して形成されている。これにより、第1の電極6404及び第2の電極6413で絶縁膜6411を挟み込んだ構造の容量素子6419が形成されている。また、画素電極6403の端部、駆動トランジスタ6418及び容量素子6419を覆い、層間絶縁膜6414が形成されている。

層間絶縁膜6414及びその開口部に位置する画素電極6403上に、有機化合物を含む層6415及び対向電極6416が形成され、画素電極6403と対向電極6416とで有機化合物を含む層6415が挟まれた領域に、発光素子6417が形成されている。

また、図64(a)に示す第1の電極6404を、図64(b)に示すように第1の電極6420で形成してもよい。なお、図64(b)に示した第1の電極6420は、配線6405、6406と同層に、配線6405、6406と同一材料で形成されている。

次に、アモルファスシリコンを半導体層に用いたボトムゲート構造のトランジスタを適用した表示パネルの画素部の部分断面図を図65、図66に示す。

図65(a)に示すように、基板6501上に下地膜6502が形成されている。さらに、下地膜6502上にゲート電極6503が形成されている。また、ゲート電極6503と同層に、ゲート電極6503と同じ材料からなる第1の電極6504が形成されている。ゲート電極6503の材料には、リンが添加された多結晶シリコンを用いることができる。多結晶シリコンの他に、金属とシリコンの化合物であるシリサイドでもよい。

ゲート電極6503及び第1の電極6504を覆うように、ゲート絶縁膜6505が形成されている。ゲート絶縁膜6505としては、酸化珪素膜や窒化珪素膜などが用いられる。

ゲート絶縁膜6505上に、半導体層6506が形成されている。また、半導体層6506と同層に、半導体層6506と同じ材料からなる半導体層6507が形成されている。

基板はガラス基板、石英基板、セラミック基板などを用いることができる。また、下地膜6502としては、窒化アルミニウム(AlN)や酸化珪素(SiO2)、酸化窒化珪素(SiOxNy)などの単層やこれらの積層を用いることができる。

半導体層6506上には、N型の導電性を有するN型半導体層6508、6509が形成され、半導体層6507上には、N型半導体層6510が形成されている。

N型半導体層6508、6509上にはそれぞれ配線6511、6512が形成される。また、配線6511、6512と同層に、配線6511、6512と同一材料からなる導電層6513が、N型半導体層6510上に形成されている。

これにより、半導体層6507、N型半導体層6510及び導電層6513からなる第2の電極が構成される。なお、この第2の電極と第1の電極6504でゲート絶縁膜6505を挟み込んだ構造の容量素子6520が形成されている。

また、配線6511の一方の端部は延在し、その延在した配線6511上部に接して画素電極6514が形成されている。

また、画素電極6514の端部、駆動トランジスタ6519及び容量素子6520を覆うように絶縁物6515が形成されている。

画素電極6514及び絶縁物6515上には、有機化合物を含む層6516及び対向電極6517が形成され、画素電極6514と対向電極6517とで有機化合物を含む層6516が挟まれた領域に、発光素子6518が形成されている。

なお、容量素子6520の第2の電極の一部となる半導体層6507及びN型半導体層6510は設けなくてもよい。つまり、容量素子6520の第2の電極は導電層6513とし、容量素子6520の構造を、第1の電極6504と導電層6513でゲート絶縁膜を挟み込んだ構造としてもよい。

なお、図65(a)において、配線6511を形成する前に画素電極6514を形成することで、図65(b)に示すような、画素電極6514と同層に、画素電極6514と同じ材料からなる第2の電極6521を形成することができる。これにより、第2の電極6521と第1の電極6504でゲート絶縁膜6505を挟み込んだ構造の容量素子6522を形成することができる。

なお、図65では、逆スタガ型のチャネルエッチ構造のトランジスタを適用した例について示したが、もちろんチャネル保護構造のトランジスタを適用してもよい。チャネル保護構造のトランジスタを適用した場合について、図66(a)、(b)を用いて説明する。

図66(a)に示すチャネル保護型構造のトランジスタは、図65(a)に示したチャネルエッチ構造の駆動トランジスタ6519の半導体層6506のチャネルが形成される領域上に、エッチングのマスクとなる絶縁物6601が設けられている点が異なり、他の共通しているところは共通の符号を用いている。

また、同様に、図66(b)に示すチャネル保護型構造のトランジスタは、図65(b)に示したチャネルエッチ構造の駆動トランジスタ6519の半導体層6506のチャネルが形成される領域上に、エッチングのマスクとなる絶縁物6601が設けられている点が異なり、他の共通しているところは共通の符号を用いている。

本発明の画素を構成するトランジスタの半導体層(チャネル形成領域やソース領域やドレイン領域など)に非晶質半導体膜を用いることで、製造コストを削減することができる。

なお、本発明の表示装置の画素部に適用することができるトランジスタの構造や、容量素子の構造は上述した構成に限られず、さまざまな構成のトランジスタの構造や、容量素子の構造を用いることができる。

なお、本実施形態で述べた内容は、実施の形態1〜実施の形態6で述べた内容と自由に組み合わせて実施することができる。

(実施の形態8)

本実施形態では、トランジスタを始めとする半導体装置を作製する方法として、プラズマ処理を用いて半導体装置を作製する方法について説明する。

図67は、トランジスタを含む半導体装置の構造例を示した図である。なお、図67において、図67(B)は図67(A)のa−b間の断面図に相当し、図67(C)は図67(A)のc−d間の断面図に相当する。

図67に示す半導体装置は、基板6701上に絶縁膜6702を介して設けられた半導体膜6703a、6703bと、当該半導体膜6703a、6703b上にゲート絶縁膜6704を介して設けられたゲート電極6705と、ゲート電極を覆って設けられた絶縁膜6706、6707と、半導体膜6703a、6703bのソース領域またはドレイン領域と接続しかつ絶縁膜6707上に設けられた導電膜6708とを有している。なお、図67においては、半導体膜6703aの一部をチャネル領域として用いたNチャネル型トランジスタ6710aと半導体膜6703bの一部をチャネル領域として用いたPチャネル型トランジスタ6710bとを設けた場合を示しているが、この構成に限られない。例えば、図67では、Nチャネル型トランジスタ6710aにLDD領域を設け、Pチャネル型トランジスタ6710bにはLDD領域を設けていないが、両方に設けた構成としてもよいし両方に設けない構成とすることも可能である。

なお、本実施形態では、上記基板6701、絶縁膜6702、半導体膜6703a及び6703b、ゲート絶縁膜6704、絶縁膜6706または絶縁膜6707のうち少なくともいずれか一層に、プラズマ処理を用いて酸化または窒化を行うことにより半導体膜または絶縁膜を酸化または窒化することによって、図67に示した半導体装置を作製する。このように、プラズマ処理を用いて半導体膜または絶縁膜を酸化または窒化することによって、当該半導体膜または絶縁膜の表面を改質し、CVD法やスパッタ法により形成した絶縁膜と比較してより緻密な絶縁膜を形成することができるため、ピンホール等の欠陥を抑制し半導体装置の特性等を向上させることが可能となる。

なお、本実施形態では、上記図67における半導体膜6703a及び6703bまたはゲート絶縁膜6704にプラズマ処理を行い、当該半導体膜6703a及び6703bまたはゲート絶縁膜6704を酸化または窒化することによって半導体装置を作製する方法について図面を参照して説明する。

はじめに、基板上に設けられた島状の半導体膜において、当該島状の半導体膜の端部を直角に近い形状で設ける場合について示す。

まず、基板6701上に島状の半導体膜6703a、6703bを形成する(図68(A))。島状の半導体膜6703a、6703bは、基板6701上にあらかじめ形成された絶縁膜6702上に公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)を用いてシリコン(Si)を主成分とする材料(例えばSixGe1−x等)等を用いて非晶質半導体膜を形成し、当該非晶質半導体膜を結晶化させ、半導体膜を選択的にエッチングすることにより設けることができる。なお、非晶質半導体膜の結晶化は、レーザー結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法またはこれら方法を組み合わせた方法等の公知の結晶化法により行うことができる。なお、図68では、島状の半導体膜6703a、6703bの端部を直角に近い形状(θ=85〜100°)で設ける。

次に、プラズマ処理を行い半導体膜6703a、6703bを酸化または窒化することによって、当該半導体膜6703a、6703bの表面にそれぞれ酸化半導体膜または窒化半導体膜である絶縁膜6721a、6721bを形成する(図68(B))。例えば、半導体膜6703a、6703bとしてSiを用いた場合、絶縁膜6721a及び絶縁膜6721bとして、酸化珪素(SiOx)または窒化珪素(SiNx)が形成される。また、プラズマ処理により半導体膜6703a、6703bを酸化させた後に、再度プラズマ処理を行うことによって窒化させてもよい。この場合、半導体膜6703a、6703bに接して酸化珪素(SiOx)が形成され、当該酸化珪素の表面に窒化酸化珪素(SiNxOy)(x>y)が形成される。なお、プラズマ処理により半導体膜を酸化する場合には、酸素雰囲気下(例えば、酸素(O2)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下または酸素と水素(H2)と希ガス雰囲気下または一酸化二窒素と希ガス雰囲気下)でプラズマ処理を行う。一方、プラズマ処理により半導体膜を窒化する場合には、窒素雰囲気下(例えば、窒素(N2)と希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)雰囲気下または窒素と水素と希ガス雰囲気下またはNH3と希ガス雰囲気下)でプラズマ処理を行う。希ガスとしては、例えばArを用いることができる。また、ArとKrを混合したガスを用いてもよい。そのため、絶縁膜6721a、6721bは、プラズマ処理に用いた希ガス(He、Ne、Ar、Kr、Xeの少なくとも一つを含む)を含んでおり、Arを用いた場合には絶縁膜6721a、6721bにArが含まれている。

また、プラズマ処理は、上記ガスの雰囲気中において、電子密度が1×1011cm−3以上1×1013cm−3以下であり、プラズマの電子温度が0.5eV以上1.5eV以下で行う。プラズマの電子密度が高密度であり、基板6701上に形成された被処理物(ここでは、半導体膜6703a、6703b)付近での電子温度が低いため、被処理物に対するプラズマによる損傷を防止することができる。また、プラズマの電子密度が1×1011cm−3以上と高密度であるため、プラズマ処理を用いて、被照射物を酸化または窒化することよって形成される酸化物または窒化膜は、CVD法やスパッタ法等により形成された膜と比較して膜厚等が均一性に優れ、かつ緻密な膜を形成することができる。また、プラズマの電子温度が1eV以下と低いため、従来のプラズマ処理や熱酸化法と比較して低温度で酸化または窒化処理を行うことができる。たとえば、ガラス基板の歪点温度よりも100度以上低い温度でプラズマ処理を行っても十分に酸化または窒化処理を行うことができる。なお、プラズマを形成するための周波数としては、マイクロ波(2.45GHz)等の高周波を用いることができる。なお、以下に特に断らない場合は、プラズマ処理として上記条件を用いて行うものとする。

次に、絶縁膜6721a、6721bを覆うようにゲート絶縁膜6704を形成する(図68(C))。ゲート絶縁膜6704は、公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)を用いて、酸化珪素(SiOx)、窒化珪素(SiNx)、酸化窒化珪素(SiOxNy)(x>y)、窒化酸化珪素(SiNxOy)(x>y)等の酸素または窒素を有する絶縁膜の単層構造、またはこれらの積層構造で設けることができる。例えば、半導体膜6703a、6703bとしてSiを用い、プラズマ処理により当該Siを酸化させることによって当該半導体膜6703a、6703b表面に絶縁膜6721a、6721bとして酸化珪素を形成した場合、当該絶縁膜6721a、6721b上にゲート絶縁膜として酸化珪素(SiOx)を形成する。また、上記図68(B)において、プラズマ処理により半導体膜6703a、6703bを酸化または窒化することによって形成された絶縁膜6721a、6721bの膜厚が十分である場合には、当該絶縁膜6721a、6721bをゲート絶縁膜として用いることも可能である。

次に、ゲート絶縁膜6704上にゲート電極6705等を形成することによって、島状の半導体膜6703a、6703bをチャネル領域として用いたNチャネル型トランジスタ6710a、Pチャネル型トランジスタ6710bを有する半導体装置を作製することができる(図68(D))。

このように、半導体膜6703a、6703b上にゲート絶縁膜6704を設ける前に、プラズマ処理により半導体膜6703a、6703bの表面を酸化または窒化することによって、チャネル領域の端部6751a、6751b等におけるゲート絶縁膜6704の被覆不良に起因するゲート電極と半導体膜のショート等を防止することができる。つまり、島状の半導体膜の端部が直角に近い形状(θ=85〜100°)を有する場合には、CVD法やスパッタ法等により半導体膜を覆うようにゲート絶縁膜を形成した際に、半導体膜の端部においてゲート絶縁膜の段切れ等による被覆不良の問題が生じる恐れがあるが、あらかじめ半導体膜の表面にプラズマ処理を用いて酸化または窒化しておくことによって、半導体膜の端部におけるゲート絶縁膜の被覆不良等を防止することが可能となる。

また、上記図68において、ゲート絶縁膜6704を形成した後にプラズマ処理を行うことによって、ゲート絶縁膜6704を酸化または窒化させてもよい。この場合、半導体膜6703a、6703bを覆うように形成されたゲート絶縁膜6704(図69(A))にプラズマ処理を行い、ゲート絶縁膜6704を酸化または窒化することによって、ゲート絶縁膜6704の表面に酸化絶縁膜または窒化絶縁膜である絶縁膜6723を形成する(図69(B))。プラズマ処理の条件は、上記図68(B)と同様に行うことができる。また、絶縁膜6723は、プラズマ処理に用いた希ガスを含んでおり、例えばArを用いた場合には絶縁膜6723にArが含まれている。

また、図69(B)において、一旦酸素雰囲気下でプラズマ処理を行うことによりゲート絶縁膜6704を酸化させた後に、再度窒素雰囲気下でプラズマ処理を行うことにより窒化させてもよい。この場合、半導体膜6703a、6703b側に酸化珪素(SiOx)または酸化窒化珪素(SiOxNy)(x>y)が形成され、ゲート電極6705に接して窒化酸化珪素(SiNxOy)(x>y)が形成される。その後、ゲート絶縁膜6704上にゲート電極6705等を形成することによって、島状の半導体膜6703a、6703bをチャネル領域として用いたNチャネル型トランジスタ6710a、Pチャネル型トランジスタ6710bを有する半導体装置を作製することができる(図69(C))。このように、ゲート絶縁膜にプラズマ処理を行うことにより、当該ゲート絶縁膜の表面を酸化または窒化することによって、ゲート絶縁膜の表面を改質し緻密な膜を形成することができる。プラズマ処理を行うことによって得られた絶縁膜は、CVD法やスパッタ法で形成された絶縁膜と比較して緻密でピンホール等の欠陥も少ないため、トランジスタの特性を向上させることができる。

なお、図69においては、あらかじめ半導体膜6703a、6703bにプラズマ処理を行うことによって、当該半導体膜6703a、6703bの表面を酸化または窒化させた場合を示したが、半導体膜6703a、6703bにプラズマ処理を行わずにゲート絶縁膜6704を形成した後にプラズマ処理を行う方法を用いてもよい。このように、ゲート電極を形成する前にプラズマ処理を行うことによって、半導体膜の端部においてゲート絶縁膜の段切れ等による被覆不良が生じた場合であっても、被覆不良により露出した半導体膜を酸化または窒化することができるため、半導体膜の端部におけるゲート絶縁膜の被覆不良に起因するゲート電極と半導体膜のショート等を防止することができる。

このように、島状の半導体膜の端部を直角に近い形状で設けた場合であっても、半導体膜またはゲート絶縁膜にプラズマ処理を行い、当該半導体膜またはゲート絶縁膜を酸化または窒化することによって、半導体膜の端部におけるゲート絶縁膜の被覆不良に起因するゲート電極と半導体膜のショート等を防止することができる。

次に、基板上に設けられた島状の半導体膜において、当該島状の半導体膜の端部をテーパー形状(θ=30〜85°)で設ける場合について示す。

まず、基板6701上に島状の半導体膜6703a、6703bを形成する(図70(A))。島状の半導体膜6703a、6703bは、基板6701上にあらかじめ形成された絶縁膜6702上に公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)を用いてシリコン(Si)を主成分とする材料(例えばSixGe1−x等)等を用いて非晶質半導体膜を形成し、当該非晶質半導体膜をレーザー結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法などの公知の結晶化法により結晶化させ、選択的に半導体膜をエッチングして除去することにより設けることができる。なお、図70では、島状の半導体膜の端部をテーパー形状(θ=30〜85°)で設ける。

次に、半導体膜6703a、6703bを覆うようにゲート絶縁膜6704を形成する(図70(B))。ゲート絶縁膜6704は、公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)を用いて、酸化珪素(SiOx)、窒化珪素(SiNx)、酸化窒化珪素(SiOxNy)(x>y)、窒化酸化珪素(SiNxOy)(x>y)等の酸素または窒素を有する絶縁膜の単層構造、またはこれらの積層構造で設けることができる。

次に、プラズマ処理を行い、ゲート絶縁膜6704を酸化または窒化することによって、当該ゲート絶縁膜6704の表面にそれぞれ酸化絶縁膜または窒化絶縁膜である絶縁膜6724を形成する(図70(C))。なお、プラズマ処理の条件は上記と同様に行うことができる。例えば、ゲート絶縁膜6704として酸化珪素(SiOx)または酸化窒化珪素(SiOxNy)(x>y)を用いた場合、酸素雰囲気下でプラズマ処理を行い、ゲート絶縁膜6704を酸化することによって、ゲート絶縁膜の表面にはCVD法やスパッタ法等により形成されたゲート絶縁膜と比較してピンホール等の欠陥の少ない緻密な膜を形成することができる。一方、窒素雰囲気下でプラズマ処理を行いゲート絶縁膜6704を窒化することによって、ゲート絶縁膜6704の表面に絶縁膜6724として窒化酸化珪素(SiNxOy)(x>y)を設けることができる。また、一旦酸素雰囲気下でプラズマ処理を行うことによりゲート絶縁膜6704を酸化させた後に、再度窒素雰囲気下でプラズマ処理を行うことにより窒化させてもよい。また、絶縁膜6724は、プラズマ処理に用いた希ガスを含んでおり、例えばArを用いた場合には絶縁膜6724中にArが含まれている。

次に、ゲート絶縁膜6704上にゲート電極6705等を形成することによって、島状の半導体膜6703a、6703bをチャネル領域として用いたNチャネル型トランジスタ6710a、Pチャネル型トランジスタ6710bを有する半導体装置を作製することができる(図70(D))。

このように、ゲート絶縁膜にプラズマ処理を行うことにより、ゲート絶縁膜の表面に酸化膜または窒化膜からなる絶縁膜を設け、ゲート絶縁膜の表面の改質をすることができる。プラズマ処理を行うことによって酸化または窒化された絶縁膜は、CVD法やスパッタ法で形成されたゲート絶縁膜と比較して緻密でピンホール等の欠陥も少ないため、トランジスタの特性を向上させることができる。また、半導体膜の端部をテーパー形状とすることによって、半導体膜の端部におけるゲート絶縁膜の被覆不良に起因するゲート電極と半導体膜のショート等を抑制することができるが、ゲート絶縁膜を形成した後にプラズマ処理を行うことによって、より一層ゲート電極と半導体膜のショート等を防止することができる。

次に、図70とは、異なる半導体装置の作製方法に関して図面を参照して説明する。具体的には、テーパー形状を有する半導体膜の端部に選択的にプラズマ処理を行う場合に関して示す。

まず、基板6701上に島状の半導体膜6703a、6703bを形成する(図71(A))。島状の半導体膜6703a、6703bは、基板6701上にあらかじめ形成された絶縁膜6702上に公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)を用いてシリコン(Si)を主成分とする材料(例えばSixGe1−x等)等を用いて非晶質半導体膜を形成し、当該非晶質半導体膜を結晶化させ、レジスト6725a、6725bをマスクとして半導体膜を選択的にエッチングすることにより設けることができる。なお、非晶質半導体膜の結晶化は、レーザー結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法またはこれら方法を組み合わせた方法等の公知の結晶化法により行うことができる。

次に、半導体膜のエッチングのために使用したレジスト6725a、6725bを除去する前に、プラズマ処理を行い島状の半導体膜6703a、6703bの端部を選択的に酸化または窒化することによって、当該半導体膜6703a、6703bの端部にそれぞれ酸化半導体膜または窒化半導体膜である絶縁膜6726を形成する(図71(B))。プラズマ処理は、上述した条件下で行う。また、絶縁膜6726は、プラズマ処理に用いた希ガスを含んでいる。

次に、半導体膜6703a、6703bを覆うようにゲート絶縁膜6704を形成する(図71(C))。ゲート絶縁膜6704は、上記と同様に設けることができる。

次に、ゲート絶縁膜6704上にゲート電極6705等を形成することによって、島状の半導体膜6703a、6703bをチャネル領域として用いたNチャネル型トランジスタ6710a、Pチャネル型トランジスタ6710bを有する半導体装置を作製することができる(図71(D))。

半導体膜6703a、6703bの端部をテーパー形状に設けた場合、半導体膜6703a、6703bの一部に形成されるチャネル領域の端部6752a、6752bもテーパー形状となり半導体膜の膜厚やゲート絶縁膜の膜厚が中央部分と比較して変化するため、トランジスタの特性に影響を及ぼす場合がある。そのため、ここではプラズマ処理によりチャネル領域の端部を選択的に酸化または窒化して、当該チャネル領域の端部となる半導体膜に絶縁膜を形成することによって、チャネル領域の端部に起因するトランジスタへの影響を低減することができる。

なお、図71では、半導体膜6703a、6703bの端部に限ってプラズマ処理により酸化または窒化を行った例を示したが、もちろん上記図70で示したようにゲート絶縁膜6704にもプラズマ処理を行って酸化または窒化させることも可能である(図73(A))。

次に、上記とは異なる半導体装置の作製方法に関して図面を参照して説明する。具体的には、テーパー形状を有する半導体膜にプラズマ処理を行う場合に関して示す。

まず、基板6701上に上記と同様に島状の半導体膜6703a、6703bを形成する(図72(A))。

次に、プラズマ処理を行い半導体膜6703a、6703bを酸化または窒化することによって、当該半導体膜6703a、6703bの表面にそれぞれ酸化半導体膜または窒化半導体膜である絶縁膜6727a、6727bを形成する(図72(B)。プラズマ処理は上述した条件下で同様に行うことができる。例えば、半導体膜6703a、6703bとしてSiを用いた場合、絶縁膜6727a及び絶縁膜6727bとして、酸化珪素(SiOx)または窒化珪素(SiNx)が形成される。また、プラズマ処理により半導体膜6703a、6703bを酸化させた後に、再度プラズマ処理を行うことによって窒化させてもよい。この場合、半導体膜6703a、6703bに接して酸化珪素(SiOx)または酸化窒化珪素(SiOxNy)(x>y)が形成され、当該酸化珪素の表面に窒化酸化珪素(SiNxOy)(x>y)が形成される。そのため、絶縁膜6727a、6727bは、プラズマ処理に用いた希ガスを含んでいる。なお、プラズマ処理を行うことにより半導体膜6703a、6703bの端部も同時に酸化または窒化される。

次に、絶縁膜6727a、6727bを覆うようにゲート絶縁膜6704を形成する(図72(C))。ゲート絶縁膜6704は、公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)を用いて、酸化珪素(SiOx)、窒化珪素(SiNx)、酸化窒化珪素(SiOxNy)(x>y)、窒化酸化珪素(SiNxOy)(x>y)等の酸素または窒素を有する絶縁膜の単層構造、またはこれらの積層構造で設けることができる。例えば、半導体膜6703a、6703bとしてSiを用いてプラズマ処理により酸化させることによって、当該半導体膜6703a、6703b表面に絶縁膜6727a、6727bとして酸化珪素を形成した場合、当該絶縁膜6727a、6727b上にゲート絶縁膜として酸化珪素(SiOx)を形成する。

次に、ゲート絶縁膜6704上にゲート電極6705等を形成することによって、島状の半導体膜6703a、6703bをチャネル領域として用いたNチャネル型トランジスタ6710a、Pチャネル型トランジスタ6710bを有する半導体装置を作製することができる(図72(D))。

半導体膜の端部をテーパー形状に設けた場合、半導体膜の一部に形成されるチャネル領域の端部6753a、6753bもテーパー形状となるため、半導体素子の特性に影響を及ぼす場合がある。そのため、プラズマ処理により半導体膜を酸化または窒化することによって、結果的にチャネル領域の端部も酸化または窒化されるため半導体素子への影響を低減することができる。

なお、図72では、半導体膜6703a、6703bに限ってプラズマ処理により酸化または窒化を行った例を示したが、もちろん上記図70で示したようにゲート絶縁膜6704にプラズマ処理を行って酸化または窒化させることも可能である(図73(B))。この場合、一旦酸素雰囲気下でプラズマ処理を行うことによりゲート絶縁膜6704を酸化させた後に、再度窒素雰囲気下でプラズマ処理を行うことにより窒化させてもよい。この場合、半導体膜6703a、6703b側に酸化珪素(SiOx)または酸化窒化珪素(SiOxNy)(x>y)が形成され、ゲート電極6705に接して窒化酸化珪素(SiNxOy)(x>y)が形成される。

このように、プラズマ処理を行い半導体膜またはゲート絶縁膜を酸化または窒化して表面を改質することにより、緻密で膜質のよい絶縁膜を形成することができる。その結果、絶縁膜を薄く形成する場合であってもピンホール等の欠陥を防止し、トランジスタ等の半導体素子の微細化及び高性能化を実現することが達成できる。

なお、本実施形態では、上記図67における半導体膜6703a及び6703bまたはゲート絶縁膜6704にプラズマ処理を行い、当該半導体膜6703a及び6703bまたはゲート絶縁膜6704を酸化または窒化を行ったが、プラズマ処理を用いて酸化または窒化を行う層は、これに限定されない。例えば、基板6701または絶縁膜6702にプラズマ処理を行ってもよいし、絶縁膜6706または絶縁膜6707にプラズマ処理を行ってもよい。

なお、本実施形態で述べた内容は、実施の形態1〜実施の形態7で述べた内容と自由に組み合わせて実施することができる。

(実施の形態9)

本実施形態では、実施の形態1から実施の形態6までで述べた駆動方法を制御するハードウェアについて述べる。

大まかな構成図を図74に示す。基板7401の上に、画素部7404、信号線駆動回路7406、走査線駆動回路7405が配置されている。それ以外にも、電源回路やプリチャージ回路やタイミング生成回路などが配置されてもよい。なお、信号線駆動回路7406や走査線駆動回路7405が配置されていなくてもよい。その場合、基板7401に配置されていないものをICに形成してもよい。そのICは、基板7401の上に、COG(Chip On Glass)によって配置されてもよい。あるいは、周辺回路基板7402と基板7401とを接続する接続基板7407の上に、ICが配置されてもよい。

周辺回路基板7402には、信号7403が入力される。そして、コントローラ7408が制御して、メモリ7409、7410などに信号が保存される。信号7403がアナログ信号の場合は、アナログ・デジタル変換を行った後、メモリ7409、7410などに保存されることが多い。そして、コントローラ7408がメモリ7409、7410などに保存された信号を用いて、基板7401に信号を出力する。

実施の形態1〜実施の形態6で述べた駆動方法を実現するために、コントローラ7408が、サブフレームの出現順序などを制御して、基板7401に信号を出力する。

なお、本実施形態で述べた内容は、実施の形態1〜実施の形態8で述べた内容と自由に組み合わせて実施することができる。

(実施の形態10)

本実施形態では、本発明の表示装置を用いたELモジュール及びELテレビ受像機の構成例について説明する。

図75は表示パネル7501と、回路基板7502を組み合わせたELモジュールを示している。表示パネル7501は画素部7503、走査線駆動回路7504及び信号線駆動回路7505を有している。回路基板7502には、例えば、コントロール回路7506や信号分割回路7507などが形成されている。表示パネル7501と回路基板7502は接続配線7508によって接続されている。接続配線にはFPC等を用いることができる。

コントロール回路7506が、実施の形態9における、コントローラ7408やメモリ7409、7410などに相当する。主に、コントロール回路7506において、サブフレームの出現順序などを制御している。

表示パネル7501は、画素部と一部の周辺駆動回路(複数の駆動回路のうち動作周波数の低い駆動回路)を基板上にトランジスタを用いて一体形成し、一部の周辺駆動回路(複数の駆動回路のうち動作周波数の高い駆動回路)をICチップ上に形成し、そのICチップをCOG(Chip On Glass)などで表示パネル7501に実装するとよい。あるいは、そのICチップをTAB(Tape Automated Bonding)やプリント基板を用いて表示パネル7501に実装してもよい。

また、走査線や信号線に設定する信号をバッファ回路によりインピーダンス変換することで、1行毎の画素の書き込み時間を短くすることができる。よって高精細な表示装置を提供することができる。

また、さらに消費電力の低減を図るため、ガラス基板上にトランジスタを用いて画素部を形成し、全ての信号線駆動回路をICチップ上に形成し、そのICチップをCOG(Chip On Glass)により表示パネルに実装してもよい。

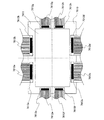

例えば、表示パネルの画面全体をいくつかの領域に分割し、各々の領域に一部もしくは全ての周辺駆動回路(信号線駆動回路、走査線駆動回路など)を形成したICチップを配置し、COG(Chip On Glass)などで表示パネルに実装してもよい。この場合の表示パネルの構成を図76に示す。

図76では、画面全体を4つの領域に分割し、8個のICチップを用いて駆動させる例である。表示パネルの構成は、基板7610、画素部7611、FPC7612a〜7612h、ICチップ7613a〜7613hを有する。8個のICチップのうち、7613a〜7613dには信号線駆動回路を形成しており、7613e〜7613hには走査線駆動回路を形成している。そして、任意のICチップを駆動させることにより、4つの画面領域のうち任意の画面領域のみを駆動させることが可能となる。例えば、ICチップ7613aと7613eのみを駆動させると、4つの画面領域のうち、左上の領域のみを駆動させることができる。このようにすることにより、消費電力を低減させることが可能となる。

また、別の構成を有している表示パネルの例を図77に示す。図77の表示パネルは基板7720上に、画素7730が複数配列された画素部7721、走査線7733の信号を制御する走査線駆動回路7722、信号線7731の信号を制御する信号線駆動回路7723を有している。また、画素7730に含まれる発光素子の輝度変化を補正するためのモニタ回路7724が設けられていてもよい。画素7730に含まれる発光素子とモニタ回路7724に含まれる発光素子は同じ構造を有している。発光素子の構造は一対の電極間にエレクトロルミネセンスを発現する材料を含む層を挟んだ形となっている。