JP2004362600A - 記憶制御装置及び記憶システム - Google Patents

記憶制御装置及び記憶システム Download PDFInfo

- Publication number

- JP2004362600A JP2004362600A JP2004212455A JP2004212455A JP2004362600A JP 2004362600 A JP2004362600 A JP 2004362600A JP 2004212455 A JP2004212455 A JP 2004212455A JP 2004212455 A JP2004212455 A JP 2004212455A JP 2004362600 A JP2004362600 A JP 2004362600A

- Authority

- JP

- Japan

- Prior art keywords

- storage

- level device

- frame

- port

- access

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Storage Device Security (AREA)

Abstract

【解決手段】 上位装置10、20、30を一意に識別できるN_Port_Name情報及び各上位装置がどのLUにアクセス可能であるかの情報の入力を、記憶制御装置40のマイクロプロセッサ42は受ける事ができる。この情報入力はパネル47或いは上位装置のユティリティプログラムにより行なう。そして上位装置10、20、30がLUにアクセスしてきたときに、このアクセスコマンドに含まれるN_Port_Name情報と入力した情報から上位装置を特定し、上位装置がそのLUにアクセス可能であるかの情報と比較する。

【選択図】図1

Description

例えば、特開平3−152652号公報には、TCP/IPをサポートするコンピュータシステム間のネットワークセキュリティシステムとして、ログインできるユーザIDをメモリに定義しておくことにより、定義されたユーザID以外でログインしようとすると、そのネットワークを切断する機能を持たせることが開示されている。

また、特開昭63−253450号公報には、中央処理装置のオペレーティングシステムがユーザID、パスワード、回線アドレスをチェックすることにより、ディスク装置のファイルへの不正アクセス防止を行なうことが示されている。

さらに、IBM社のESCONインタフェースでは、上位装置が当該上位装置の論理アドレスをソースアドレスとしてフレームに格納し、送信してくることを利用して、記憶制御装置が事前に記憶制御装置に設定した論理アドレスとフレーム内の論理アドレスが一致するか否かをチェックする機能を設けている。

上述した従来技術は、上位論理層に1種類のレイヤを搭載するインタフェースを対象とした不正アクセス防止手段の域を出ないものである。

しかし、ANSIX3T11で標準化されたファイバチャネルは、ネットワーク形アーキテクチャであり、上位論理層にはTCP/IP、SCSI、ESCON、IPI等の種々のレイヤを搭載可能である。すなわち、データのフォーマットや内容には無関係に一台の装置から別の装置へバッファの内容を移すため、他のインタフェースと論理的に互換性を持ち、物理的に自由にアクセス可能である。特に、このファイバチャネルと、ディスクアレイ装置等の複数の記憶領域を有する記憶装置とを備えた記憶システムにおいては、上記記憶領域は多くの上位装置に共用される。したがって、従来の不正アクセス防止策では不十分であり、ユーザが意識したセキュリティ設定により、機密保持を行なう必要がある。

不一致の場合は、受領した当該フレームを拒絶するLS_RJTフレームを上位装置に返すようにしたことである。これにより、記憶制御装置は上位装置からの不正アクセスを抑止することができる。

ディスクアレイ装置の代わりに、光ディスク装置、光磁気ディスク装置及び磁気テープ装置並びにこれらの各種ライブラリ装置の何れの場合でも、当該記憶制御装置は、アクセス可能な上位装置のN_Port_Name情報、記憶制御装置のポート、記憶装置の対応付けを行い、ライブラリ装置の場合はさらにドライブ、媒体の対応付けも行って、制御テーブルで管理、保持する手段を有し、フレーム受領の際にフレーム内の情報と制御テーブル内の情報を比較する手段を有し、

上位装置からの不正アクセスの防止を行うことができる。

Check)74及びエンドオブフレームEOF(End Of Frame

)75で構成される。

そして、 FCP コマンドデスクリプタブロックFCP_CDB(FCP Command Discriptor Block)フィールド93には、SCSIコマンドディスクリプタブロック(SCSI Command Descriptor Block)が格納され、リードコマンドRead等のコマンド種類、LUN等のアドレス、ブロック数が示される。FCPデータレングスFCP_DL(FCP Data Length)フィールド94には、当該コマンドにより転送されるデータ量がバイト数で指定される。

おけるシーケンスは、あるN_Portから別のN_Portへ、一方向に転送される関連するデータフレームの集まりのことを言い、SCSIのフェーズに相当する。シーケンスの集まりをエクスチェンジと呼ぶ。例えばコマンドを発行して、そのコマンドの終了までに、そのコマンド実行のためにやりとりされるシーケンスの集まり(コマンド発行、データ転送、終了報告)がエクスチェンジとなる。このように、エクスチェンジはSCSIのI/Oに相当する。

リードコマンドシーケンス(110)及びライトコマンドシーケンス(120)を示す。

上位装置10、20、30が立ち上がり、各々、N_Port_Name情報を格納したログイン要求フレームであるPLOGIフレームを発行する。記憶制御装置40のマイクロプロセッサ42は、当該フレームを受領すると、まずこのフレームを受領したことを示すACKフレームを各上位装置に返す。

そしてマイクロプロセッサ42は、当該フレームに格納されているN_Port_Name情報を切り出し、そのN_Port_Name情報が、既に設定され、保持されている制御テーブル内のN_Port_Nameリストに登録されているかどうか、比較を行なう。

上位装置10、20の発行した当該フレームに格納されているN_Port_Name情報は、制御テーブル内に登録されているN_Port_Name情報と一致するため、記憶制御装置40のマイクロプロセッサ42は、上位装置10、20に対してはログイン要求を受け付けた印として、ACCフレームを返し、ログイン処理を続行する。

一方、上位装置30の発行した当該フレームに格納されているN_Port_Name情報は、制御テーブル内に登録されているN_Port_Name情報と一致しないため、記憶制御装置40のマイクロプロセッサ42は、上位装置30に対しては接続を拒絶するリジェクトパラメータをいれたLS_RJTフレームを返す。

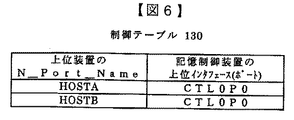

N_Port_Nameを、上位装置10はHOSTA、上位装置20はHOSTB、記憶制御装置40のファイバチャネル制御部41のポートをCTL0P0、とした場合、I/O要求制御テーブル140は、図8のようになる。

万一の電源瞬断時にも管理情報を守ることができる。

上位装置10がLU0(51)にI/O要求を出したい場合、上位装置10は記憶制御装置40に対し、SCSI CDBを格納したフレームを発行する。記憶制御装置40がこのフレームを受領した場合、まず、このフレームを受領したことを示すACKフレームを上位装置10に返す。

そしてマイクロプロセッサ42は、当該フレームに格納されているN_Port_Name情報及びCDB内のLUN番号を切り出し、そのN_Port_Name情報及びLUN番号が、当該マイクロプロセッサ42に既に設定され保持されている制御テーブル内のリストに登録されているかどうか、比較を行なう。

管理テーブル内には、「上位装置10は、LU0(51)をアクセス可能であ

る」と登録されているため、記憶制御装置40のマイクロプロセッサ42はコマンドを受領し、I/O処理を継続する。

一方、上位装置20が記憶制御装置40にLU0(51)のI/O要求フレームを発行し、記憶制御装置40がこのSCSI CDBを格納したフレームを受領した場合、マイクロプロセッサ42は、まずこのフレームを受領したことを示すACKフレームを上位装置20に返す。

そしてマイクロプロセッサ42は、当該フレームに格納されているN_Port_Name情報及びCDB内のLUN番号を切り出し、そのN_Port_Name情報及びLUN番号が、管理テーブル内にあるかどうかの検索を行なう。

検索を行なった結果、管理テーブル内に、該当するLUNおよびN_Port_Nameの組合わせが存在しないため、記憶制御装置40のマイクロプロセッサ42は、上位装置20にLS_RJTフレームを送って、I/O要求を拒絶する。

記憶制御装置は上位装置からの不正アクセスを防止可能である。

Redundancy Check)、75…エンドオブフレームEOF(End Of Frame)、80…フレームヘッダのフォーマット、81…デスティネーションアイデンティファイアD_ID(Destination ID

)、82…ソースアイデンティファイアS_ID(Source ID)、90…ファイバチャネルプロトコルコマンドFCP_CMNDペイロード(Fibre Channel Protocol for SCSI Command)、91…ファイバチャネルプロトコルロジカルユニットナンバFCP_LUN(FCP Logical Unit Number)、92…ファイバチャネルプロトコルコントロールFCP_CNTL(FCP Control)、93…ファイバチャネルプロトコルコマンドデスクリプタブロックFCP_CDB(FCP Command Descriptor Block)、94…ファイバチャネルプロトコルデータレングスFCP_DL( FCP Data Length)、100…ログイン、110…リードコマンド、120…ライトコマンド、130…ログイン要求制御テープル、140…磁気ディスクアレイI/O要求制御テープル、150…光ディスクライブラリ、160…光ディスクライブラリI/O要求制御テーブル

Claims (2)

- ファイバチャネルを介して複数の上位装置と接続される記憶システムにおけるアクセス制御方法であって、

前記記憶システムは、

記憶領域を有し前記上位装置から送信されるデータを記憶する記憶装置と、前記上位装置から前記記憶装置へのアクセスを制御する記憶制御装置を有し、さらに前記記憶制御装置は前記上位装置を識別するN_Port_Nameと、前記記憶領域を識別するLUN(Logical Unit Number)と、を有するテーブルを備え、

PLOGI時に、前記上位装置から前記記憶システムに送信されたPLOGIフレームに格納された上位装置の識別情報と前記テーブルに記載されている上位装置の識別情報が一致するか比較し、一致する場合は前記上位装置にログイン可能であることを通知する第一の工程と、

前記PLOGIの承認後の前記上位装置からのI/O要求時に、前記上位装置から前記記憶システムに送信されたI/O要求フレームに格納された上位装置の識別情報及びアクセス要求先の記憶領域の識別情報と前記テーブルに記載されている上位装置の識別情報及びアクセス要求先の記憶領域の識別情報が一致するか比較し、一致する場合は前記上位装置にI/O可能であることを通知する第二の工程とを有し、前記上位装置から前記記憶領域へのアクセスを制御することを特徴とするアクセス制御方法。 - ファイバチャネルを介して複数の上位装置と接続される記憶システムにおけるアクセス制御方法であって、

前記記憶システムは、

記憶領域を有し前記上位装置から送信されるデータを記憶する記憶装置と、前記上位装置から前記記憶装置へのアクセスを制御する記憶制御装置を有し、さらに前記記憶制御装置は前記上位装置を識別するN_Port_IDと、前記記憶領域を識別するLUN(Logical Unit Number)と、を有するテーブルを備え、

PLOGI時に、前記上位装置から前記記憶システムに送信されたPLOGIフレームに格納された上位装置の識別情報と前記テーブルに記載されている上位装置の識別情報が一致するか比較し、一致する場合は前記上位装置にログイン可能であることを通知する第一の工程と、

前記PLOGIの承認後の前記上位装置からのI/O要求時に、前記上位装置から前記記憶システムに送信されたI/O要求フレームに格納された上位装置の識別情報及びアクセス要求先の記憶領域の識別情報と前記テーブルに記載されている上位装置の識別情報及びアクセス要求先の記憶領域の識別情報が一致するか比較し、一致する場合は前記上位装置にI/O可能であることを通知する第二の工程とを有し、前記上位装置から前記記憶領域へのアクセスを制御することを特徴とするアクセス制御方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004212455A JP2004362600A (ja) | 2004-07-21 | 2004-07-21 | 記憶制御装置及び記憶システム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004212455A JP2004362600A (ja) | 2004-07-21 | 2004-07-21 | 記憶制御装置及び記憶システム |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000118493A Division JP3633436B2 (ja) | 1997-05-29 | 2000-04-14 | コンピュータシステム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004362600A true JP2004362600A (ja) | 2004-12-24 |

| JP2004362600A5 JP2004362600A5 (ja) | 2005-06-16 |

Family

ID=34056389

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004212455A Pending JP2004362600A (ja) | 2004-07-21 | 2004-07-21 | 記憶制御装置及び記憶システム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2004362600A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007140962A (ja) * | 2005-11-18 | 2007-06-07 | Hitachi Ltd | ディスクアレイシステム及びセキュリティ方法 |

| EP2477376A1 (en) | 2011-01-12 | 2012-07-18 | Fujitsu Limited | Communication control apparatus, communication system, information processing apparatus, and communication control method |

-

2004

- 2004-07-21 JP JP2004212455A patent/JP2004362600A/ja active Pending

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007140962A (ja) * | 2005-11-18 | 2007-06-07 | Hitachi Ltd | ディスクアレイシステム及びセキュリティ方法 |

| EP2477376A1 (en) | 2011-01-12 | 2012-07-18 | Fujitsu Limited | Communication control apparatus, communication system, information processing apparatus, and communication control method |

| JP2012147218A (ja) * | 2011-01-12 | 2012-08-02 | Fujitsu Ltd | 通信制御装置、通信システム、情報処理装置および通信制御方法 |

| US8984088B2 (en) | 2011-01-12 | 2015-03-17 | Fujitsu Limited | Communication control apparatus, communication system, information processing apparatus, and communication control method |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3987672B2 (ja) | 記憶制御装置及び記憶システム | |

| US8422677B2 (en) | Storage virtualization apparatus comprising encryption functions | |

| US7107421B2 (en) | Data migration method and a data migration apparatus | |

| US7363455B2 (en) | Apparatus and method for partitioning and managing subsystem logics | |

| US20020095549A1 (en) | Disk storage system | |

| JP4990442B2 (ja) | 記憶制御装置及びコンピュータシステム | |

| US20090177895A1 (en) | Controller for controlling logical volume-related settings | |

| JP4497957B2 (ja) | 記憶制御システム | |

| JP2004362600A (ja) | 記憶制御装置及び記憶システム | |

| JP2007250009A (ja) | 記憶制御装置及び記憶システム | |

| US20060101169A1 (en) | Device and method for generating a logical path between connection of control device connected to a host device and memory device provided in said control device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041117 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051128 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20051128 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20060523 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060928 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061019 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061218 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070807 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071005 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20080623 |