KR20160086320A - 나노-갭 전극 및 이를 제조하기 위한 방법들 - Google Patents

나노-갭 전극 및 이를 제조하기 위한 방법들 Download PDFInfo

- Publication number

- KR20160086320A KR20160086320A KR1020167008057A KR20167008057A KR20160086320A KR 20160086320 A KR20160086320 A KR 20160086320A KR 1020167008057 A KR1020167008057 A KR 1020167008057A KR 20167008057 A KR20167008057 A KR 20167008057A KR 20160086320 A KR20160086320 A KR 20160086320A

- Authority

- KR

- South Korea

- Prior art keywords

- electrode

- gap

- nano

- forming

- sensor

- Prior art date

Links

- 238000000034 method Methods 0.000 title claims abstract description 223

- 238000004519 manufacturing process Methods 0.000 title claims description 98

- 239000000758 substrate Substances 0.000 claims description 87

- 239000000463 material Substances 0.000 claims description 59

- 229910052751 metal Inorganic materials 0.000 claims description 31

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical group [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims description 30

- 229910021332 silicide Inorganic materials 0.000 claims description 29

- 239000002184 metal Substances 0.000 claims description 28

- 239000004065 semiconductor Substances 0.000 claims description 26

- 229910052710 silicon Inorganic materials 0.000 claims description 26

- 239000010703 silicon Substances 0.000 claims description 26

- 102000039446 nucleic acids Human genes 0.000 claims description 24

- 108020004707 nucleic acids Proteins 0.000 claims description 24

- 150000007523 nucleic acids Chemical class 0.000 claims description 24

- 238000005530 etching Methods 0.000 claims description 22

- 238000010438 heat treatment Methods 0.000 claims description 21

- 150000001875 compounds Chemical class 0.000 claims description 18

- 238000006243 chemical reaction Methods 0.000 claims description 16

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 claims description 8

- 238000007669 thermal treatment Methods 0.000 claims description 5

- 150000004767 nitrides Chemical class 0.000 claims description 3

- 238000004891 communication Methods 0.000 claims description 2

- 239000012530 fluid Substances 0.000 claims description 2

- 239000012528 membrane Substances 0.000 claims description 2

- 230000000750 progressive effect Effects 0.000 claims 1

- 239000010410 layer Substances 0.000 description 259

- 239000000470 constituent Substances 0.000 description 76

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 68

- 229910052814 silicon oxide Inorganic materials 0.000 description 64

- 230000000875 corresponding effect Effects 0.000 description 49

- 108020004414 DNA Proteins 0.000 description 36

- 102000053602 DNA Human genes 0.000 description 36

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical group [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 23

- 230000008569 process Effects 0.000 description 22

- 108020004682 Single-Stranded DNA Proteins 0.000 description 21

- 238000010586 diagram Methods 0.000 description 18

- 229910052581 Si3N4 Inorganic materials 0.000 description 16

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 16

- 239000010936 titanium Substances 0.000 description 16

- 238000012545 processing Methods 0.000 description 14

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 12

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 12

- 239000004020 conductor Substances 0.000 description 12

- 229910052719 titanium Inorganic materials 0.000 description 12

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Substances [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 11

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 10

- 238000005229 chemical vapour deposition Methods 0.000 description 10

- 206010010144 Completed suicide Diseases 0.000 description 9

- 238000001312 dry etching Methods 0.000 description 9

- 229910017052 cobalt Inorganic materials 0.000 description 8

- 239000010941 cobalt Substances 0.000 description 8

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 8

- 230000005641 tunneling Effects 0.000 description 8

- 239000011248 coating agent Substances 0.000 description 7

- 238000000576 coating method Methods 0.000 description 7

- 239000002090 nanochannel Substances 0.000 description 7

- 229920002477 rna polymer Polymers 0.000 description 7

- 239000007787 solid Substances 0.000 description 7

- 229910045601 alloy Inorganic materials 0.000 description 6

- 239000000956 alloy Substances 0.000 description 6

- 229910052758 niobium Inorganic materials 0.000 description 6

- 239000010955 niobium Substances 0.000 description 6

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 6

- 229910052763 palladium Inorganic materials 0.000 description 6

- 238000004544 sputter deposition Methods 0.000 description 6

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 5

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 5

- 239000002041 carbon nanotube Substances 0.000 description 5

- 229910021393 carbon nanotube Inorganic materials 0.000 description 5

- 238000011161 development Methods 0.000 description 5

- 239000011733 molybdenum Substances 0.000 description 5

- 229910052750 molybdenum Inorganic materials 0.000 description 5

- 229910052759 nickel Inorganic materials 0.000 description 5

- 239000012811 non-conductive material Substances 0.000 description 5

- 229910052697 platinum Inorganic materials 0.000 description 5

- 238000001039 wet etching Methods 0.000 description 5

- 238000000151 deposition Methods 0.000 description 4

- 239000007769 metal material Substances 0.000 description 4

- 229910004298 SiO 2 Inorganic materials 0.000 description 3

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 3

- 238000000231 atomic layer deposition Methods 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 230000000295 complement effect Effects 0.000 description 3

- 238000010884 ion-beam technique Methods 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 239000002071 nanotube Substances 0.000 description 3

- 239000002070 nanowire Substances 0.000 description 3

- 239000002773 nucleotide Substances 0.000 description 3

- 125000003729 nucleotide group Chemical group 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- ISAKRJDGNUQOIC-UHFFFAOYSA-N Uracil Chemical compound O=C1C=CNC(=O)N1 ISAKRJDGNUQOIC-UHFFFAOYSA-N 0.000 description 2

- OIRDTQYFTABQOQ-KQYNXXCUSA-N adenosine group Chemical group [C@@H]1([C@H](O)[C@H](O)[C@@H](CO)O1)N1C=NC=2C(N)=NC=NC12 OIRDTQYFTABQOQ-KQYNXXCUSA-N 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 229910052681 coesite Inorganic materials 0.000 description 2

- 229910052906 cristobalite Inorganic materials 0.000 description 2

- OPTASPLRGRRNAP-UHFFFAOYSA-N cytosine Chemical compound NC=1C=CNC(=O)N=1 OPTASPLRGRRNAP-UHFFFAOYSA-N 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- UYTPUPDQBNUYGX-UHFFFAOYSA-N guanine Chemical compound O=C1NC(N)=NC2=C1N=CN2 UYTPUPDQBNUYGX-UHFFFAOYSA-N 0.000 description 2

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 229920003229 poly(methyl methacrylate) Polymers 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 239000004926 polymethyl methacrylate Substances 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 239000011148 porous material Substances 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- 125000006850 spacer group Chemical group 0.000 description 2

- 229910052682 stishovite Inorganic materials 0.000 description 2

- 238000006467 substitution reaction Methods 0.000 description 2

- RWQNBRDOKXIBIV-UHFFFAOYSA-N thymine Chemical compound CC1=CNC(=O)NC1=O RWQNBRDOKXIBIV-UHFFFAOYSA-N 0.000 description 2

- 229910052905 tridymite Inorganic materials 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 235000012431 wafers Nutrition 0.000 description 2

- ZXEYZECDXFPJRJ-UHFFFAOYSA-N $l^{3}-silane;platinum Chemical compound [SiH3].[Pt] ZXEYZECDXFPJRJ-UHFFFAOYSA-N 0.000 description 1

- KXGFMDJXCMQABM-UHFFFAOYSA-N 2-methoxy-6-methylphenol Chemical compound [CH]OC1=CC=CC([CH])=C1O KXGFMDJXCMQABM-UHFFFAOYSA-N 0.000 description 1

- DKCRDQKHMMPWPG-UHFFFAOYSA-N 3-methylpiperidine-2,6-dione Chemical compound CC1CCC(=O)NC1=O DKCRDQKHMMPWPG-UHFFFAOYSA-N 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- 239000002126 C01EB10 - Adenosine Substances 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 1

- CZPWVGJYEJSRLH-UHFFFAOYSA-N Pyrimidine Chemical compound C1=CN=CN=C1 CZPWVGJYEJSRLH-UHFFFAOYSA-N 0.000 description 1

- 229960005305 adenosine Drugs 0.000 description 1

- 150000001413 amino acids Chemical class 0.000 description 1

- 238000000277 atomic layer chemical vapour deposition Methods 0.000 description 1

- 238000013475 authorization Methods 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 238000005513 bias potential Methods 0.000 description 1

- YXTPWUNVHCYOSP-UHFFFAOYSA-N bis($l^{2}-silanylidene)molybdenum Chemical compound [Si]=[Mo]=[Si] YXTPWUNVHCYOSP-UHFFFAOYSA-N 0.000 description 1

- 150000001720 carbohydrates Chemical class 0.000 description 1

- 235000014633 carbohydrates Nutrition 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000007596 consolidation process Methods 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 230000001276 controlling effect Effects 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000002596 correlated effect Effects 0.000 description 1

- 229940104302 cytosine Drugs 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 239000004205 dimethyl polysiloxane Substances 0.000 description 1

- 238000004090 dissolution Methods 0.000 description 1

- 238000001962 electrophoresis Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 150000002632 lipids Chemical class 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 238000003801 milling Methods 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910021344 molybdenum silicide Inorganic materials 0.000 description 1

- 238000001127 nanoimprint lithography Methods 0.000 description 1

- 239000002105 nanoparticle Substances 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- 239000000615 nonconductor Substances 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 229920001568 phenolic resin Polymers 0.000 description 1

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 1

- 229910021339 platinum silicide Inorganic materials 0.000 description 1

- 229920000435 poly(dimethylsiloxane) Polymers 0.000 description 1

- -1 polydimethylsiloxane Polymers 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 238000011112 process operation Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 235000011149 sulphuric acid Nutrition 0.000 description 1

- 230000008719 thickening Effects 0.000 description 1

- 229940113082 thymine Drugs 0.000 description 1

- MAKDTFFYCIMFQP-UHFFFAOYSA-N titanium tungsten Chemical compound [Ti].[W] MAKDTFFYCIMFQP-UHFFFAOYSA-N 0.000 description 1

- 230000009466 transformation Effects 0.000 description 1

- 238000000844 transformation Methods 0.000 description 1

- 230000005945 translocation Effects 0.000 description 1

- 230000017105 transposition Effects 0.000 description 1

- 229940035893 uracil Drugs 0.000 description 1

- 238000000927 vapour-phase epitaxy Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01N—INVESTIGATING OR ANALYSING MATERIALS BY DETERMINING THEIR CHEMICAL OR PHYSICAL PROPERTIES

- G01N33/00—Investigating or analysing materials by specific methods not covered by groups G01N1/00 - G01N31/00

- G01N33/48—Biological material, e.g. blood, urine; Haemocytometers

- G01N33/483—Physical analysis of biological material

- G01N33/487—Physical analysis of biological material of liquid biological material

- G01N33/48707—Physical analysis of biological material of liquid biological material by electrical means

- G01N33/48721—Investigating individual macromolecules, e.g. by translocation through nanopores

-

- C—CHEMISTRY; METALLURGY

- C12—BIOCHEMISTRY; BEER; SPIRITS; WINE; VINEGAR; MICROBIOLOGY; ENZYMOLOGY; MUTATION OR GENETIC ENGINEERING

- C12Q—MEASURING OR TESTING PROCESSES INVOLVING ENZYMES, NUCLEIC ACIDS OR MICROORGANISMS; COMPOSITIONS OR TEST PAPERS THEREFOR; PROCESSES OF PREPARING SUCH COMPOSITIONS; CONDITION-RESPONSIVE CONTROL IN MICROBIOLOGICAL OR ENZYMOLOGICAL PROCESSES

- C12Q1/00—Measuring or testing processes involving enzymes, nucleic acids or microorganisms; Compositions therefor; Processes of preparing such compositions

- C12Q1/68—Measuring or testing processes involving enzymes, nucleic acids or microorganisms; Compositions therefor; Processes of preparing such compositions involving nucleic acids

- C12Q1/6869—Methods for sequencing

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/06—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material characterised by the coating material

- C23C14/0641—Nitrides

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C14/00—Coating by vacuum evaporation, by sputtering or by ion implantation of the coating forming material

- C23C14/58—After-treatment

- C23C14/5886—Mechanical treatment

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/06—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of metallic material

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

- C23C16/30—Deposition of compounds, mixtures or solid solutions, e.g. borides, carbides, nitrides

- C23C16/34—Nitrides

- C23C16/345—Silicon nitride

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/56—After-treatment

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01N—INVESTIGATING OR ANALYSING MATERIALS BY DETERMINING THEIR CHEMICAL OR PHYSICAL PROPERTIES

- G01N27/00—Investigating or analysing materials by the use of electric, electrochemical, or magnetic means

- G01N27/26—Investigating or analysing materials by the use of electric, electrochemical, or magnetic means by investigating electrochemical variables; by using electrolysis or electrophoresis

- G01N27/416—Systems

- G01N27/447—Systems using electrophoresis

- G01N27/44704—Details; Accessories

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01N—INVESTIGATING OR ANALYSING MATERIALS BY DETERMINING THEIR CHEMICAL OR PHYSICAL PROPERTIES

- G01N27/00—Investigating or analysing materials by the use of electric, electrochemical, or magnetic means

- G01N27/26—Investigating or analysing materials by the use of electric, electrochemical, or magnetic means by investigating electrochemical variables; by using electrolysis or electrophoresis

- G01N27/416—Systems

- G01N27/447—Systems using electrophoresis

- G01N27/44756—Apparatus specially adapted therefor

- G01N27/44791—Microapparatus

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0657—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body

- H01L29/0665—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body the shape of the body defining a nanostructure

- H01L29/0669—Nanowires or nanotubes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/413—Nanosized electrodes, e.g. nanowire electrodes comprising one or a plurality of nanowires

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y40/00—Manufacture or treatment of nanostructures

-

- C—CHEMISTRY; METALLURGY

- C12—BIOCHEMISTRY; BEER; SPIRITS; WINE; VINEGAR; MICROBIOLOGY; ENZYMOLOGY; MUTATION OR GENETIC ENGINEERING

- C12Q—MEASURING OR TESTING PROCESSES INVOLVING ENZYMES, NUCLEIC ACIDS OR MICROORGANISMS; COMPOSITIONS OR TEST PAPERS THEREFOR; PROCESSES OF PREPARING SUCH COMPOSITIONS; CONDITION-RESPONSIVE CONTROL IN MICROBIOLOGICAL OR ENZYMOLOGICAL PROCESSES

- C12Q2565/00—Nucleic acid analysis characterised by mode or means of detection

- C12Q2565/60—Detection means characterised by use of a special device

- C12Q2565/607—Detection means characterised by use of a special device being a sensor, e.g. electrode

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01N—INVESTIGATING OR ANALYSING MATERIALS BY DETERMINING THEIR CHEMICAL OR PHYSICAL PROPERTIES

- G01N27/00—Investigating or analysing materials by the use of electric, electrochemical, or magnetic means

- G01N27/26—Investigating or analysing materials by the use of electric, electrochemical, or magnetic means by investigating electrochemical variables; by using electrolysis or electrophoresis

- G01N27/28—Electrolytic cell components

- G01N27/30—Electrodes, e.g. test electrodes; Half-cells

- G01N27/327—Biochemical electrodes, e.g. electrical or mechanical details for in vitro measurements

- G01N27/3275—Sensing specific biomolecules, e.g. nucleic acid strands, based on an electrode surface reaction

- G01N27/3278—Sensing specific biomolecules, e.g. nucleic acid strands, based on an electrode surface reaction involving nanosized elements, e.g. nanogaps or nanoparticles

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Life Sciences & Earth Sciences (AREA)

- Health & Medical Sciences (AREA)

- Physics & Mathematics (AREA)

- Organic Chemistry (AREA)

- Molecular Biology (AREA)

- Biomedical Technology (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Materials Engineering (AREA)

- General Health & Medical Sciences (AREA)

- General Physics & Mathematics (AREA)

- Immunology (AREA)

- Biochemistry (AREA)

- Analytical Chemistry (AREA)

- Proteomics, Peptides & Aminoacids (AREA)

- Nanotechnology (AREA)

- Metallurgy (AREA)

- Mechanical Engineering (AREA)

- Biophysics (AREA)

- Pathology (AREA)

- Zoology (AREA)

- Power Engineering (AREA)

- Wood Science & Technology (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Chemical & Material Sciences (AREA)

- Medicinal Chemistry (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Hematology (AREA)

- Urology & Nephrology (AREA)

- Food Science & Technology (AREA)

- Microbiology (AREA)

- Computer Hardware Design (AREA)

- Bioinformatics & Cheminformatics (AREA)

- General Engineering & Computer Science (AREA)

- Genetics & Genomics (AREA)

- Ceramic Engineering (AREA)

- Electrochemistry (AREA)

- Biotechnology (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

Abstract

본 개시는 나노-갭 전극을 형성하기 위한 방법을 제공한다. 일부 경우들에서, 측벽의 막 두께에 의해 조절되는 폭을 가진 나노-갭은 제 1 전극-형성 부분과 제 2 전극-형성 부분 사이에, 마스크로서 제 1 전극-형성 부분과 콘택하는 측벽을 사용하여 형성될 수 있다. 그 다음 제 1 전극-형성 부분, 측벽 및 제 2 전극-형성 부분의 표면들이 노출될 수 있다. 그 다음 측벽은 제 1 전극-형성 부분과 제 2 전극-형성 부분 사이에 나노-갭을 형성하도록 제거될 수 있다.

Description

[0001] 본 출원은 2013년 8월 27일 출원된 일본 특허 출원 번호 JP 2013-176132, 및 2013년 8월 28일 출원된 JP 2013-177051에 대한 우선권을 주장하고, 이 출원들 각각은 전체가 인용에 의해 본원에 포함된다.

[0002] 최근에, 나노스케일(nanoscale) 갭이 대향되는 전극들 사이에 형성되는 전극 구조(이후 나노-갭 전극으로 지칭됨)가 관심 집중되었다. 따라서, 나노-갭 전극들을 사용하는 전자 디바이스들, 바이오디바이스(biodevice)들 등에 대해 활발한 연구가 수행되고 있다. 예컨대, 나노-갭 전극을 활용하는 DNA의 뉴클레오티드(nucleotide) 시퀀스를 분석하기 위한 분석 장치가 바이오디바이스들 분야에서 고려되었다(예컨대, WO2011/108540 참조).

[0003] 이런 분석 장치에서, 싱글-스트랜디드(single-stranded) DNA는 나노-갭 전극의 전극들 사이의 나노스케일 (중공) 갭(이후 나노-갭으로 지칭됨)을 거쳐 통과된다. 전극들을 통해 흐르는 전류는, 싱글-스트랜디드 DNA의 염기(base)들이 전극들 사이의 나노-갭을 거쳐 통과할 때 측정될 수 있고, 이에 의해 싱글-스트랜디드 DNA를 구성하는 염기들이 현재 값들에 기초하여 결정되게 된다.

[0004] 상기 언급된 그런 분석 장치에서, 전류의 검출가능 값은, 나노-갭 전극의 전극들 사이의 거리가 증가하는 경우 감소한다. 이것은 높은 감도로 샘플들을 분석하는 것을 어렵게 한다. 따라서, 전극들 사이의 나노-갭이 작은 사이즈로 형성되는 것이 원해진다.

[0005] 나노-갭 전극을 제조하기 위한 기존 방법들은, 금 등으로 만들어진 전극 형성 층 상에 형성된, 티타늄 마스크 같은 금속 마스크가 포커싱된 이온 빔으로 마스크를 조사함으로써 패터닝되고; 이런 패터닝된 금속 마스크를 통해 노출된 아래 놓인 전극 층이 건식-에칭될 수 있고, 나노-갭이 전극 층으로부터 형성될 수 있고, 이에 의해 나노-갭 전극이 형성되는 방법을 포함한다(예컨대, 일본 특허 공개 번호 2004-247203 참조).

[0006] 상기 설명된 바와 같은 나노-갭 전극을 제조하기 위한 그런 방법에서, 패터닝된 금속 마스크로 커버되지 않은 노출된 전극 층은 전극 층의 나노-갭으로서 역할을 하는 갭을 형성하도록 건식-에칭된다. 따라서 전극 층에 형성된 갭(마스크 폭 갭)의 최소 폭은 금속 마스크가 패터닝될 수 있는 가장 작은 폭이다. 그러므로 그 방법은, 표준 리소그래픽 방법들을 사용하여 그 폭보다 작은 나노-갭(종래의 나노-갭)을 형성하는 것이 어렵다는 점에서 문제를 가진다. 따라서, 최근에, 종래의 나노-갭과 동일한 폭의 나노-갭뿐 아니라, 종래의 나노-갭보다 훨씬 작은 나노-갭을 형성할 수 있는 새로운 제조 방법의 개발을 위한 욕구가 있어왔다.

[0007] 따라서, 본 발명의 목적은 종래의 나노-갭과 동일한 폭의 나노-갭뿐 아니라, 종래의 나노-갭보다 폭이 훨씬 더 작은 나노-갭을 형성할 수 있는 나노-갭 전극을 제조하기 위한 방법을 설명하는 것이다.

[0008] 본 발명은 나노-갭 전극 및 나노-갭 전극을 제조하는 방법에 관한 것이다.

[0009] 포커싱된 이온 빔, e-빔 및 나노-임프린트(imprint) 기술들은 20 나노미터(nm), 잠재적으로 적어도 10 nm인 폭들 및 깊이들을 가질 수 있는 나노채널들을 생성하는데 유용한 것으로서 설명되었다. 채널 폭이 더블(double) 스트랜디드 DNA에 대한 회전 반경보다 작은 시스템들이 설명되었지만; 싱글 스트랜디드 DNA의 회전 반경보다 작은 것과 같이 충분히 작은 폭을 가진 시스템들 및 방법들은 설명되지 않았다.

[0010] 나노갭 구조들로의 샘플 생체분자들에 의한 액세스를 허용할 만큼 충분히 작은 치수들을 가진 나노채널들에 대한 필요가 존재하고, 이는 또한 잠재적으로 이차 구조가 생체분자의 상이한 부분들 사이에 형성되는 것을 방지하면서, 보다 높은 퍼센티지의 생체분자들의 문의(interrogation)를 허용한다.

[0011] 상기 설명된 바와 같이 나노-갭 전극을 제조하기 위한 그런 방법에서, 그러나, 패터닝된 금속 마스크로 커버되지 않은 노출된 전극 층은 전극 층의 나노-갭으로서 역할을 하는 갭을 형성하도록 건식-에칭될 수 있다. 따라서, 전극 층에 형성된 갭의 최소 폭(마스크 갭의 폭에 대응함)은, 금속 마스크가 패터닝될 수 있는 최소 폭이다. 그러므로 이 방법은, 금속 마스크 상에 형성될 수 있는 가장 작은 피처의 폭보다 작은 나노-갭을 형성하는 것이 어렵다는 점에서 문제를 가진다.

[0012] 본 개시는 나노-갭 전극들 및 나노채널 시스템들에 대한 디바이스들, 시스템들 및 방법들을 제공한다. 본원에 제공된 방법들은 현재 이용 가능한 다른 방법들을 사용하여 형성된 갭보다 작은 나노-갭을 가진 나노-갭 전극을 형성하기 위하여 사용될 수 있다.

[0013] 일부 실시예들에서, 나노-갭 전극을 제조하는 방법은 마스크로서 전극-형성 부분 상에 배치된 측벽을 사용하는 단계, 및 전극-형성 부분상 측벽의 막 두께에 의해 조절된 폭을 가진 나노-갭을 형성하는 단계를 포함한다.

[0014] 다른 실시예들에서, 나노-갭 전극을 제조하는 방법은 기판상에 형성된 제 1 전극-형성 부분의 측면 벽(lateral wall)상에 측벽(sidewall)을 형성하는 단계, 및 그 다음, 측벽 상에 인접하도록 제 2 전극-형성 부분을 형성하여, 제 1 전극-형성 부분과 제 2 전극-형성 부분 사이에 측벽을 배치하는 단계; 및 제 1 전극-형성 부분, 측벽 및 제 2 전극-형성 부분의 표면들을 노출시키는 단계 및 측벽을 제거하여, 제 1 전극-형성 부분과 제 2 전극-형성 부분 사이에 나노-갭을 형성하는 단계를 포함한다.

[0015] 부가적인 실시예들에서 나노-갭 전극을 제조하는 방법은 전극-형성 부분 상 갭을 가로질러 서로 대향되는 측면 벽들을 가진 갭-형성 마스크를 배치하는 단계; 갭-형성 마스크의 측면 벽들의 둘 다 상에 측벽들을 형성하는 단계, 및 측벽들 사이의 전극-형성 부분을 노출시키는 단계; 및 측벽들 사이에 나노-갭을 형성하기 위하여 측벽들 사이의 노출된 전극-형성 부분을 제거하는 단계를 포함한다.

[0016] 추가 실시예들에서 나노-갭 전극을 제조하는 방법은 갭으로부터 전극-형성 부분을 노출시키기 위하여 갭-형성 마스크에 제공된 측벽들을 제거하여 갭-형성 마스크에 갭을 형성하는 단계; 및 갭으로부터 노출된 전극-형성 부분을 제거하, 갭 내에 나노-갭을 형성하는 단계를 포함한다.

[0017] 다른 실시예들에서 나노-갭 전극을 제조하는 방법은 전극-형성 부분 상에 배치된 측벽-형성 마스크의 측면 벽 상에 측벽을 형성하는 단계, 및 그 다음 수직으로 측벽을 만들도록 측벽-형성 마스크를 제거하는 단계; 측벽을 둘러싸도록 갭-형성 마스크를 형성하는 단계; 측벽을 제거하여 갭-형성 마스크에 갭을 형성하는 단계, 및 갭으로부터 전극-형성 부분을 노출시키는 단계; 및 갭으로부터 노출된 전극-형성 부분을 제거하여 갭 내에 나노-갭을 형성하는 단계를 포함한다.

[0018] 추가 실시예들에서, 나노-갭 전극을 제조하는 방법은 전극-형성 부분 상에 배치된 제 1 갭-형성 마스크의 측면 벽 상에 측벽을 형성하는 단계, 및 그 다음 측벽에 인접하도록 제 2 갭-형성 마스크를 형성하여, 제 1 갭-형성 마스크 및 제 2 갭-형성 마스크 사이에 측벽을 배치하는 단계; 제 1 갭-형성 마스크, 측벽 및 제 2 갭-형성 마스크의 표면들을 노출시키는 단계 및 측벽을 제거하여, 제 1 갭-형성 마스크와 제 2 갭-형성 마스크 사이에 갭을 형성하는 단계; 및 갭 내의 전극-형성 부분을 제거하여 갭 내에 나노-갭을 형성하는 단계를 포함한다.

[0019] 본 발명에 따라, 측벽의 막 두께에 의해 조절되는 폭을 가진 나노-갭을 형성하는 것이 가능하다. 결과적으로, 종래의 나노-갭과 동일한 폭인 나노-갭뿐 아니라, 종래의 나노-갭보다 폭이 훨씬 더 작은 나노-갭을 형성하는 것이 가능하다.

[0020] 본 발명의 양상에 따라, 나노-갭 전극을 제조하는 방법은: 대향하는 전극-형성 부분들 상에 화합물-생성 층의 막을 형성하는 단계, 및 그 다음 열 처리를 수행하는 단계; 전극-형성 부분들을 화합물-생성 층과 반응시키는 단계; 반응에 의해 2개의 부피 팽창된(volumetrically expanded) 대향되는 전극들을 형성하는 단계; 및 부피 팽창에 의해 전극들의 측벽들을 서로에 더 가깝게 하여, 전극들 사이에 나노-갭을 형성하는 단계를 포함할 수 있다.

[0021] 본 개시의 다른 양상에 따라, 나노-갭 전극을 제조하는 방법은:

기판상에 위치된 한 쌍의 대향하는 전극-형성 부분들 상에 특정 폭에 따르게 선택된 마스크를 형성하는 단계;

전극-형성 부분들 상에 화합물-생성 층의 막을 형성하는 단계;

서로 대향되고 반응으로부터 발생하는 부피 팽창에 의해 마스크 아래로 침투하는 2개의 전극들을 형성하기 위하여 화합물-생성 층을 전극-형성 부분들과 반응시키도록 열 처리를 수행하여, 부피 팽창에 의해, 마스크의 폭보다 전극들의 측벽들이 서로 더 가깝게 하는 단계; 및

마스크 및 이전에 마스크 아래 구역에 남아있는 전극-형성 부분들의 임의의 반응되지 않은 부분들을 제거하여, 전극들 사이에 나노-갭을 형성하는 단계를 포함한다.

[0022] 본 발명의 다른 양상에 따라, 나노-갭 전극을 제조하는 방법은:

기판상 갭을 가로질러 서로 대향하여 배치된 2개의 전극-형성 부분들을 형성하는 단계;

전극-형성 부분들 상에 화합물-생성 층의 막을 형성하는 단계; 및

전극-형성 부분들과 화합물-생성 층에 대한 반응이, 상기 반응에 의해 부피 팽창되고 서로 대향되는 2개의 전극들을 형성하게 하도록 열 처리를 수행하여, 갭보다 작은 나노-갭을 형성하도록 전극 부분들의 측벽들이 부피 팽창에 의해 서로 더 가깝게 되는 단계를 포함한다.

[0023] 다른 실시예에서, 전극들 사이의 갭은 전극들의 부피 팽창 양만큼 작게 될 수 있다. 결과적으로, 표준 리소그래픽 프로세싱에 의해 형성된 갭보다 훨씬 작은 나노-갭을 가지는 나노-갭 전극을 제공하고, 그리고 나노-갭 전극을 제조하기 위한 방법을 제공하는 것이 가능하다.

[0024] 일부 실시예들에서, 나노갭 전극 구조의 형성에 유용한 것으로 본원에 설명된 것들과 같은 방법들은 e-빔, 이온 빔 밀링, 또는 나노임프린트 리소그래피 같은 종래의 반도체 프로세스들을 사용하여 형성될 수 있는 것보다 작을 수 있는 나노 채널을 형성하는데 활용될 수 있다.

[0025] 본 개시의 양상은 적어도 하나의 나노-갭을 가진 센서를 제조하기 위한 방법을 제공하고, 상기 방법은 (a) 기판에 인접하게 제 1 전극-형성 부분을, 제 1 전극-형성 부분에 인접하게 측벽을, 그리고 측벽에 인접하게 제 2 전극-형성 부분을 제공하는 단계; (b) 측벽을 제거하여, 제 1 전극-형성 부분과 제 2 전극-형성 부분 사이에 나노-갭을 형성하는 단계; 및 (c) 타겟 종이 전극들 사이에 배치될 때 나노-갭을 횡단하는 전류를 검출하는 전극들로서 사용하기 위하여 제 1 전극-형성 부분 및 제 2 전극-형성 부분을 준비하는 단계를 포함한다. 실시예에서, 전류는 터널링 전류이다.

[0026] 실시예에서, 전극들로서 사용하기 위하여 제 1 전극-형성 부분 및 제 2 전극-형성 부분을 준비하는 단계는 제 1 전극-형성 부분 및 제 2 전극-형성 부분 중 적어도 일부를 제거하여 전극들을 제공하는 단계를 포함한다. 다른 실시예에서, 제 1 및/또는 제 2 전극-형성 부분은 금속 질화물로 형성된다. 다른 실시예에서, 제 1 및/또는 제 2 전극-형성 부분은 티타늄 질화물로 형성된다. 다른 실시예에서, 기판은 반도체 층에 인접한 반도체 산화물 층을 포함한다. 다른 실시예에서, 반도체는 실리콘이다.

[0027] 실시예에서, 측벽은 약 2 나노미터 또는 그 미만의 폭을 가진다. 다른 실시예에서, 폭은 약 1 나노미터보다 작거나 같다. 다른 실시예에서, 폭은 약 0.5 나노미터보다 크다.

[0028] 실시예에서, 방법은 (c) 이전에, 제 1 전극-형성 부분, 측벽 및 제 2 전극-형성 부분의 표면들을 노출시키는 단계를 더 포함한다.

[0029] 실시예에서, 방법은 (b) 이전에, 제 1 전극-형성 부분과 제 2 전극-형성 부분 사이의 측벽의 단면이 사각형 형상을 가지도록 측벽의 일부를 제거하는 단계를 더 포함한다.

[0030] 실시예에서, 방법은 나노-갭을 횡단하는 채널을 형성하는 단계를 더 포함한다. 다른 실시예에서, 채널은 커버된 채널이다.

[0031] 본 개시의 다른 양상은 적어도 하나의 나노-갭을 가진 센서를 형성하기 위한 방법을 제공하고, 상기 방법은 (a) 기판에 인접한 전극-형성 부분상 갭을 가로질러 서로 대향되는 측면 벽들을 가진 갭-형성 마스크를 배치하는 단계 ― 상기 갭은 제 1 폭을 가짐 ―; (b) 갭-형성 마스크의 측면 벽들 상에 측벽들을 형성하는 단계 ― 상기 전극-형성 부분은 측벽들 사이에서 노출됨 ―; (c) 측벽들 사이에서 노출된 전극-형성 부분의 일부를 제거하여 측벽들 사이에 나노-갭을 형성하는 단계 ― 나노-갭은 제 1 폭보다 작은 제 2 폭을 가짐 ―; (d) 측벽들을 제거하여 나노-갭에 의해 분리된 전극-형성 부분의 부분들을 노출시키는 단계; 및 (e) 타겟 종이 전극들 사이에 배치될 때 나노-갭을 횡단하는 전류를 검출하는 전극들로서 사용하기 위하여 전극-형성 부분의 부분들을 준비하는 단계를 포함한다. 실시예에서, 전류는 터널링 전류이다.

[0032] 실시예에서, 전극들로서 사용하기 위하여 전극-형성 부분의 부분들을 준비하는 단계는 전극-형성 부분의 부분들을 제거하여 전극들을 제공하는 단계를 포함한다. 다른 실시예에서, 기판은 반도체 층에 인접한 반도체 산화물 층을 포함한다. 다른 실시예에서, 반도체는 실리콘이다.

[0033] 실시예에서, 제 2 폭은 약 2 나노미터보다 작거나 같다. 다른 실시예에서, 제 2 폭은 약 1 나노미터보다 작거나 같다. 다른 실시예에서, 제 2 폭은 약 0.5 나노미터보다 크다.

[0034] 실시예에서, 타겟 종은 핵산 분자(nucleic acid molecule)이고, 그리고 제 2 폭은 핵산 분자의 직경보다 작다. 다른 실시예에서, 갭-형성 마스크 및 측벽들은 상이한 재료들로 형성된다.

[0035] 실시예에서, 방법은 나노-갭을 횡단하는 채널을 형성하는 단계를 더 포함한다. 다른 실시예에서, 채널은 커버된 채널이다.

[0036] 본 개시의 다른 양상은 적어도 하나의 나노-갭을 가진 센서를 형성하기 위한 방법을 제공하고, 상기 방법은 (a) 측벽을 포함하는 마스크를 제공하는 단계 ― 상기 측벽은 기판에 인접한 전극-형성 부분에 인접하게 배치됨 ―; (b) 측벽을 제거하여 마스크에 갭을 형성하는 단계 ― 갭은 전극-형성 부분의 일부를 노출시킴 ―; (c) 전극-형성 부분의 부분을 제거하여 나노-갭을 형성하는 단계; (d) 마스크를 제거하여 나노-갭에 의해 분리된 전극-형성 부분의 부분들을 노출시키는 단계; 및 (e) 타겟 종이 전극들 사이에 배치될 때 나노-갭을 횡단하는 전류를 검출하는 전극들로서 사용하기 위하여 전극-형성 부분의 부분들을 준비하는 단계를 포함한다. 실시예에서, 전류는 터널링 전류이다. 다른 실시예에서, 타겟 종은 핵산 분자이고, 그리고 측벽은 핵산 분자의 직경보다 작은 폭을 가진다.

[0037] 실시예에서, 전극들로서 사용하기 위하여 전극-형성 부분의 부분들을 준비하는 단계는 전극-형성 부분의 부분들을 제거하여 전극들을 제공하는 단계를 포함한다.

[0038] 실시예에서, (a)는 (ⅰ) 전극-형성 부분에 인접하게 배치된 제 1 마스크의 측면 벽 상에 측벽을 제공하는 단계, (ⅱ) 제 1 마스크를 제거하는 단계, 및 (ⅲ) 측벽에 인접하게 제 2 마스크를 형성하는 단계를 포함하고, 마스크는 제 2 마스크의 적어도 일부를 포함한다. 다른 실시예에서, 제 1 마스크를 제거하는 단계는 전극-형성 부분을 노출시킨다. 다른 실시예에서, 제 2 마스크는 측벽을 커버한다. 다른 실시예에서, 제 1 마스크를 제거한 후, 측벽은 약 10 나노미터(nm), 5 nm, 4 nm, 3 nm, 2 nm, 1 nm, 0.9 nm, 0.8 nm, 0.7 nm, 0.6 nm 또는 0.5 nm 또는 그 미만의 폭을 가진 독립형(free-standing) 측벽이다.

[0039] 실시예에서, (a)는 (ⅰ) 전극-형성 부분에 인접하게 배치된 제 1 마스크의 측면 벽 상에 측벽을 제공하는 단계, (ⅱ) 측벽에 인접하게 제 2 마스크를 형성하는 단계, 및 (ⅲ) 제 2 마스크를 에칭하는 단계를 포함하고, 마스크는 제 1 마스크 및 제 2 마스크의 적어도 일부를 포함한다. 다른 실시예에서, 측벽에 인접하게 제 2 마스크를 형성하는 단계는 제 2 마스크가 제 1 마스크 및 측벽을 커버하는 단계를 포함한다. 다른 실시예에서, 제 2 마스크를 에칭하는 단계는 제 1 마스크 및/또는 측벽을 에칭하는 단계를 포함한다.

[0040] 실시예에서, 방법은 나노-갭을 횡단하는 채널을 형성하는 단계를 더 포함한다. 다른 실시예에서, 채널은 커버된 채널이다.

[0041] 실시예에서, 기판은 반도체 층에 인접한 반도체 산화물 층을 포함한다. 다른 실시예에서, 반도체는 실리콘이다.

[0042] 실시예에서, (a)는 측벽을 형성하도록 측-벽 형성 층을 제공하는 단계 및 측-벽 형성 층을 에칭하는 단계를 더 포함한다.

[0043] 실시예에서, 나노-갭은 약 2 나노미터 또는 그 미만의 폭을 가진다. 다른 실시예에서, 폭은 약 1 나노미터보다 작거나 같다. 다른 실시예에서, 폭은 약 0.5 나노미터보다 크다.

[0044] 실시예에서, 방법은 나노-갭을 횡단하는 채널을 형성하는 단계를 더 포함한다. 다른 실시예에서, 채널은 커버된 채널이다.

[0045] 본 개시의 다른 양상은 나노-갭 전극 센서를 제조하는 방법을 제공하고, 상기 방법은 (a) 제 2 재료를 가진 전극-형성 부분 상에 제 1 재료를 가진 막을 제공하는 단계 ― 전극-형성 부분은 기판에 인접하게 배치됨 ―; (b) 제 1 및 제 2 재료들을 반응시키도록 막을 가열하여, 부피 팽창되고 서로 대향되는 2개의 전극 부분들을 형성하는 단계 ― 전극 부분들의 각각은 측벽을 가짐 ―; (c) 부피 팽창에 의해 전극 부분들의 측벽들을 서로를 향해 움직이게 하여, 전극 부분들 사이에 나노-갭을 형성하는 단계; 및 (d) 타겟 종이 전극들 사이에 배치될 때 나노-갭을 횡단하는 전류를 검출하는 전극들로서 사용하기 위하여 전극 부분들을 준비하는 단계를 포함한다. 실시예에서, 전류는 터널링 전류이다.

[0046] 실시예에서, 전극들로서 사용하기 위하여 전극 부분들을 준비하는 단계는 전극 부분들의 적어도 일부를 제거하여 전극들을 제공하는 단계를 포함한다. 다른 실시예에서, (a)는 (ⅰ) 전극-형성 부분의 폭에 따르게 선택된 마스크를 형성하는 단계, (ⅱ) 전극-형성 부분 상에 막을 형성하는 단계를 포함한다. 다른 실시예에서, 2개의 전극 부분들을 형성할 때, 2개의 전극 부분들은 반응으로부터 발생하는 부피 팽창에 의해 마스크 내로 침투하고, 이에 의해 전극 부분들의 측벽들을 서로를 향하여 움직이게 한다. 다른 실시예에서, 방법은 마스크 및 마스크의 하부 구역에 남아있는 전극 부분들의 반응되지 않은 부분(들)을 제거하여, 전극 부분들 사이에 나노-갭을 형성하는 단계를 더 포함한다.

[0047] 실시예에서, 방법은 나노-갭을 횡단하는 채널을 형성하는 단계를 더 포함한다. 다른 실시예에서, 채널은 커버된 채널이다.

[0048] 본 개시의 다른 양상은 적어도 하나의 나노-갭 전극을 가진 센서를 제조하는 방법을 제공하고, 상기 방법은 (a) 기판에 인접하게 2개의 전극-형성 부분들을 제공하는 단계 ― 전극-형성 부분들은 제 1 폭을 가진 갭을 가로질러 서로 대향하여 배치됨 ―; (b) 전극-형성 부분들 상에 화합물-생성 층의 막을 형성하는 단계; (c) 반응에 의해 부피 팽창된 적어도 하나의 전극 부분을 형성하기 위하여 화합물-생성 층과 전극-형성 부분들 중 적어도 하나 사이의 반응을 가능하게 하도록 열 처리를 수행하여, 제 1 폭보다 작은 제 2 폭을 가진 나노-갭을 형성하도록 부피 팽창에 의해 전극-형성 부분들의 측벽들을 서로를 향해 움직이게 하는 단계; 및 (d) 타겟 종이 전극들 사이에 배치될 때 나노-갭을 횡단하는 전류를 검출하는 전극들로서 사용하기 위하여 전극-형성 부분들을 준비하는 단계를 포함한다. 실시예에서, 전류는 터널링 전류이다.

[0049] 실시예에서, 전극들로서 사용하기 위하여 전극-형성 부분들을 준비하는 단계는 전극-형성 부분의 부분들을 제거하여 전극들을 제공하는 단계를 포함한다. 다른 실시예에서, 화합물-생성 층은 실리사이드(silicide)-생성 층이고, (c)는 반응 동안 전극-형성 부분들의 실리사이드화를 포함하고, 그리고 전극-형성 부분들은 실리사이드화 동안 부피 팽창한다.

[0050] 실시예에서, 제 2 폭은 약 2 나노미터보다 작거나 같다. 다른 실시예에서, 제 2 폭은 약 1 나노미터보다 작거나 같다. 다른 실시예에서, 제 2 폭은 약 0.5 나노미터보다 크다.

[0051] 실시예에서, 타겟 종은 핵산 분자이고, 그리고 제 2 폭은 핵산 분자의 직경보다 작다.

[0052] 실시예에서, (c)는 화합물-생성 층과 전극-형성 부분들 둘 다 사이에서의 반응을 포함한다. 다른 실시예에서, (c)는 화합물-생성 층과 전극-형성 부분들 중 단지 하나 사이의 반응을 포함한다.

[0053] 실시예에서, 방법은 나노-갭을 횡단하는 채널을 형성하는 단계를 더 포함한다. 다른 실시예에서, 채널은 커버된 채널이다.

[0054] 본 개시의 다른 양상은 기판상 나노-갭을 가로질러 대향하여 배치된 적어도 2개의 전극 부분들을 포함하는 나노-갭 전극 센서를 제공하고, 전극 부분들의 대향되는 측벽들은 점진적으로 서로 더 가깝게 되고 측벽들 사이의 폭은 점진적으로 좁아지고, 그리고 전극들은, 타겟 종이 전극들 사이에 배치될 때 나노-갭을 횡단하는 전류를 검출하도록 적응된다. 실시예에서, 전류는 터널링 전류이다.

[0055] 실시예에서, 전극 부분들은 금속 실리사이드로 형성된다. 다른 실시예에서, 나노-갭은, 나노-갭이 기판에 접근할 때 전극 부분들의 측벽들 사이의 거리가 점진적으로 넓어지는 트레일링(trailing) 곡선 형상으로 형성된다. 다른 실시예에서, 측벽들은 기판과 콘택하는 외측으로 팽창하는 부분들을 포함한다.

[0056] 실시예에서, 센서는 나노-갭을 횡단하고 유체 연통하는 채널을 더 포함한다. 다른 실시예에서, 채널은 커버된 채널이다.

[0057] 본 개시의 부가적인 양상들 및 장점들은 다음 상세한 설명으로부터 당업자들에게 쉽게 명백하게 될 것이고, 여기서 본 개시의 단지 예시적 실시예들만이 도시되고 설명된다. 인식될 바와 같이, 본 개시는 다른 그리고 상이한 실시예들을 가질 수 있고, 이의 몇몇 상세들은 모두가 본 개시로부터 벗어나지 않고 다양하고 분명한 측면들에서 수정들을 가질 수 있다. 따라서, 도면들 및 설명 및 제한으로서가 아닌 사실상 예시로서 간주될 것이다.

인용에 의한 통합

[0058] 본 명세서에 언급된 모든 공개물들, 특허들, 및 특허 출원들은, 각각의 개별 공개물, 특허 또는 특허 출원이 구체적으로 그리고 개별적으로 인용에 의해 통합된 것으로 나타난 동일한 범위까지 인용에 의해 본원에 포함된다.

[0059] 본 발명의 신규 피처들은 첨부된 청구항들에서 특수성을 갖게 진술된다. 본 발명의 피처들 및 장점들의 더 나은 이해는 본 발명의 원리들이 활용되는 예시적 실시예들을 진술하는 다음 상세한 설명, 및 첨부 도면들(또한 본원에서 "도면" 및 "도")을 참조하여 얻어질 것이다.

[0060] 도 1은 제조 방법에 의해 제조된 나노-갭 전극의 구성을 예시하는 개략도이다.

[0061] 도 2a-도 2f는 도 1의 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0062] 도 3a-도 3f는 도 1의 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0063] 도 4는 제조 방법에 의해 제조된 나노-갭 전극의 구성을 예시하는 개략도이다.

[0064] 도 5는 도 4의 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도이다.

[0065] 도 6a-도 6c는 도 4에 따른 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0066] 도 7a-도 7c는 도 4의 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0067] 도 8a-도 8c는 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0068] 도 9a-도 9b는 도 8의 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0069] 도 10a-도 10c는 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0070] 도 11a-도 11b는 도 10의 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0071] 도 12a-도 12d는 도 1의 나노갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0072] 도 13a-도 13f는 도 12a-도 12c와 연관된 방법을 설명하기 위한 부가적인 개략도들이다.

[0073] 도 14는 나노-갭 전극을 도시하는 개략도이다.

[0074] 도 15는 전극-형성 부분 및 마스크가 기판상에 형성된 구성을 도시하는 개략도이다.

[0075] 도 16은 나노-갭 전극을 제조하기 위한 방법을 설명하는데 사용된 개략도이다.

[0076] 도 17은 나노-갭 전극을 제조하기 위한 방법을 설명하는데 사용된 다른 개략도이다.

[0077] 도 18은 다른 실시예에 따른 나노-갭 전극의 구성을 도시하는 개략도이다.

[0078] 도 19는 나노-갭 전극을 제조하기 위한 방법을 설명하는데 사용된 개략도이다.

[0079] 도 20은 나노-갭 전극을 제조하기 위한 방법을 설명하는데 사용된 다른 개략도이다.

[0080] 도 21a-도 21c는 몇몇 대안적 전극 형상들을 도시하는 개략 평면도 표현이다.

[0081] 도 22a-도 22f는 DNA를 나노-갭 전극에 전달하기 위한 통합된 채널을 가진 나노-갭 전극을 제조하기 위한 방법을 설명하는데 사용된 단면도들의 개략 표현이다.

[0082] 도 23은 DNA를 하나 또는 그 초과의 나노-갭 전극들에 전달하기 위하여 통합된 채널에 대한 구성을 도시하는 개략 평면도이다.

[0083] 도 24a-도 24c는 단일 측 팽창 접근법을 사용하여 나노-갭 전극을 제조하기 위한 방법을 설명하는데 사용된 개략도이다.

[0084] 도 25a-도 25c는 수직 전극 배향을 사용하여 나노-갭 전극을 제조하기 위한 방법을 설명하는데 사용된 개략도이다.

[0060] 도 1은 제조 방법에 의해 제조된 나노-갭 전극의 구성을 예시하는 개략도이다.

[0061] 도 2a-도 2f는 도 1의 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0062] 도 3a-도 3f는 도 1의 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0063] 도 4는 제조 방법에 의해 제조된 나노-갭 전극의 구성을 예시하는 개략도이다.

[0064] 도 5는 도 4의 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도이다.

[0065] 도 6a-도 6c는 도 4에 따른 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0066] 도 7a-도 7c는 도 4의 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0067] 도 8a-도 8c는 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0068] 도 9a-도 9b는 도 8의 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0069] 도 10a-도 10c는 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0070] 도 11a-도 11b는 도 10의 나노-갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0071] 도 12a-도 12d는 도 1의 나노갭 전극을 제조하기 위한 방법의 설명에 사용된 개략도들이다.

[0072] 도 13a-도 13f는 도 12a-도 12c와 연관된 방법을 설명하기 위한 부가적인 개략도들이다.

[0073] 도 14는 나노-갭 전극을 도시하는 개략도이다.

[0074] 도 15는 전극-형성 부분 및 마스크가 기판상에 형성된 구성을 도시하는 개략도이다.

[0075] 도 16은 나노-갭 전극을 제조하기 위한 방법을 설명하는데 사용된 개략도이다.

[0076] 도 17은 나노-갭 전극을 제조하기 위한 방법을 설명하는데 사용된 다른 개략도이다.

[0077] 도 18은 다른 실시예에 따른 나노-갭 전극의 구성을 도시하는 개략도이다.

[0078] 도 19는 나노-갭 전극을 제조하기 위한 방법을 설명하는데 사용된 개략도이다.

[0079] 도 20은 나노-갭 전극을 제조하기 위한 방법을 설명하는데 사용된 다른 개략도이다.

[0080] 도 21a-도 21c는 몇몇 대안적 전극 형상들을 도시하는 개략 평면도 표현이다.

[0081] 도 22a-도 22f는 DNA를 나노-갭 전극에 전달하기 위한 통합된 채널을 가진 나노-갭 전극을 제조하기 위한 방법을 설명하는데 사용된 단면도들의 개략 표현이다.

[0082] 도 23은 DNA를 하나 또는 그 초과의 나노-갭 전극들에 전달하기 위하여 통합된 채널에 대한 구성을 도시하는 개략 평면도이다.

[0083] 도 24a-도 24c는 단일 측 팽창 접근법을 사용하여 나노-갭 전극을 제조하기 위한 방법을 설명하는데 사용된 개략도이다.

[0084] 도 25a-도 25c는 수직 전극 배향을 사용하여 나노-갭 전극을 제조하기 위한 방법을 설명하는데 사용된 개략도이다.

[0085] 본 발명의 다양한 실시예들이 본원에 도시되고 설명되었지만, 그런 실시예들이 단지 예로써 제공되는 것이 당업자들에게 분명할 것이다. 다수의 변형들, 변화들, 및 대체들은 본 발명에서 벗어나지 않고 당업자들에게 떠오를 수 있다. 본원에 설명된 본 발명의 실시예들에 대한 다양한 대안들이 이용될 수 있다는 것이 이해되어야 한다.

[0086] 본원에 사용된 바와 같은 용어 "갭"은 일반적으로 재료에 형성되거나 다르게 제공된 포어(pore), 채널 또는 통로를 지칭한다. 재료는 기판 같은 고체 상태 재료일 수 있다. 갭은 감지 회로 또는 감지 회로에 커플링된 전극에 인접하게 또는 가까이에 배치될 수 있다. 일부 예들에서, 갭은 약 0.1 나노미터(nm) 내지 약 1000 nm의 특성 폭 또는 직경을 가진다. 몇 나노미터의 폭을 가진 갭은 "나노-갭"으로서 지칭될 수 있다.

[0087] 본원에 사용된 바와 같은 용어 "전극-형성 부분"은 일반적으로 전극을 생성하기 위하여 사용될 수 있는 부분 또는 부재를 지칭한다. 전극-형성 부분은 전극일 수 있거나 전극의 일부일 수 있다. 예컨대, 전극-형성 부분은 제 2 전기 전도체와 전기 통신하는 제 1 전기 전도체이다. 다른 예에서, 전극-형성 부분은 전극이다.

[0088] 본원에 사용된 바와 같은 용어 "핵산"은 일반적으로 하나 또는 그 초과의 핵산 서브유닛(subunit)들을 포함하는 분자를 지칭한다. 핵산은 아데노신(A), 사이토신(C), 구아닌(G), 티민(T) 및 우라실(U), 또는 이들의 변형들로부터 선택된 하나 또는 그 초과의 서브유닛들을 포함할 수 있다. 뉴클레오티드(nucleotide)는 A, C, G, T 또는 U, 또는 이들의 변이체들을 포함할 수 있다. 뉴클레오티드는 성장하는 핵산 스트랜드에 통합될 수 있는 임의의 서브유닛을 포함할 수 있다. 그런 서브유닛은 A, C, G, T, 또는 U일 수 있거나, 또는 하나 또는 그 초과의 상보적 A, C, G, T 또는 U에 특정하거나, 또는 퓨린에 상보적이거나(즉, A 또는 G, 또는 이들의 변이체) 또는 피리미딘에 상보적인(즉, C, T 또는 U, 또는 이들의 변이체) 임의의 다른 서브유닛일 수 있다. 서브유닛은 개별 핵산 염기들 또는 염기들의 그룹들(예컨대, AA, TA, AT, GC, CG, CT, TC, GT, TG, AC, CA, 또는 이들의 우라실-대응부들)이 용해되게 한다. 일부 예들에서, 핵산은 디옥시리보핵산(DNA) 또는 리보 핵산(RNA), 또는 이들의 유도체들이다. 핵산은 싱글-스트랜디드 또는 더블 스트랜디드될 수 있다.

[0089] 본 개시는 생체분자(예컨대, 핵산 분자)를 검출하는 것과 같이, 다양한 애플리케이션들에 사용될 수 있는, 나노-갭 전극들을 가진 센서들을 형성하기 위한 방법들을 제공한다. 본원에 제공된 방법들에 따라 형성된 나노-갭 전극들은 핵산 분자, 그런 디옥시리보핵산(DNA) 또는 리보 핵산(RNA), 또는 이들의 변이체들을 시퀀싱하기 위하여 사용될 수 있다.

[0090] 도 1은 본원에 제공된 방법들에 따라 형성될 수 있는 나노-갭 전극(1)을 도시한다. 이 나노-갭 전극(1)에서, 대향되는 전극들(5 및 6)은 기판(2)상에 배치된다. 나노스케일(예컨대, 1000 나노미터보다 크지 않음)의 폭(W1)을 가진 나노-갭(NG)(또는 포어)은 전극들(5 및 6) 사이에 형성된다. 본원에 설명된 제조 방법들에 의해 제조될 때 나노-갭 전극(1)은 예컨대, 나노-갭(NG)이 0.1 나노미터(nm) 내지 30 nm, 또는 2 nm, 1 nm, 0.9 nm, 0.8 nm, 0.7 nm, 0.6 nm, 또는 0.5보다 크지 않은 폭(W1), 또는 본원에 설명된 바와 같은 임의의 다른 폭들로 형성되게 할 수 있다. 일부 경우들에서, W1은 생체분자(예컨대, DNA 또는 RNA)일 수 있는 타겟 종의 직경보다 작다.

[0091] 기판(2)은 예컨대, 실리콘 기판(3) 및 그 위에 형성된 실리콘 산화물 층(4)으로 구성될 수 있다. 대안으로서, 기판(2)은 게르마늄 또는 갈륨 비화물(이들의 산화물들을 포함함) 같은 그룹 Ⅳ 또는 그룹 Ⅲ-Ⅴ 반도체를 포함하는 다른 반도체 재료(들)를 포함할 수 있다. 기판(2)은, 한 쌍을 형성하는 2개의 전극들(5 및 6)이 실리콘 산화물 층(4)상에 형성될 수 있는 구성을 가질 수 있다. 전극들(5 및 6)은 금속 재료, 이를테면 티타늄 질화물(TiN)을 포함할 수 있고, 일부 실시예들에서 기판(2) 상에서 나노-갭(NG)을 가로질러 거의 양 방향으로 대칭으로 형성될 수 있다. 일부 실시예들에서, 전극들(5 및 6)은 실질적으로 동일한 구성을 가지며 나노-갭(NG)을 형성하는 리딩(leading) 전극 에지들(5b 및 6b)로 구성될 수 있고, 그리고 베이스 부분들(5a 및 6a)은 리딩 전극 에지들(5b 및 6b)의 루트(root) 부분들과 일체형으로 형성될 수 있다. 리딩 전극 에지들(5b 및 6b)은 예컨대, 직사각형 고체들을 포함할 수 있고, 상기 고체들의 길이 방향들은 y 방향으로 연장될 수 있고, 리딩 전극 에지들(5b 및 6b)의 선단(apical) 표면들이 서로를 향하도록 배치될 수 있고; 리딩 에지들(5b 및 6b)은 곡선들을 가질 수 있다(도시되지 않음).

[0092] 베이스 부분들(5a 및 6a)은 자신의 중앙 선단 단부들에 돌출부들을 가질 수 있고 이에 의해 리딩 전극 에지들(5b 및 6b)이 형성될 수 있다. 완만하게 곡선진 표면은 각각의 베이스 부분(5a 및 6a)의 양쪽 측들을 향해 형성되고 각각의 베이스 부분(5a 및 6a)은 중앙에 자신의 중앙 선단 단부를 가진다. 따라서, 베이스 부분들(5a 및 6a)은 곡선진 형상으로 형성될 수 있고 리딩 전극 에지들(5b 및 6b)은 정점(vertex)에 포지셔닝된다. 예컨대, 싱글-스트랜디드 DNA를 포함하는 용액이 전극들(5 및 6)의 길이 방향일 수 있는 y-방향에 직교하는 x-방향으로부터, 전극들(5 및 6)의 수직 방향일 수 있고 이 y-방향과 직각으로 교차할 수 있는 z-방향으로 공급될 때, 용액이 베이스 부분들(5a 및 6a)의 곡선진 표면들을 따라 리딩 전극 에지들(5b 및 6b)로 인도되어 용액이 나노-갭(NG)을 신뢰성 있게 통과하는 것을 가능하게 하도록 구성될 수 있다는 것을 주의하라.

[0093] 상기 설명된 바와 같이 구성된 나노-갭 전극(1)에 대해, 전류가 예컨대 전력 원(도시되지 않음)으로부터 전극들(5 및 6)로 공급될 수 있고, 전극들(5 및 6)을 가로질러 흐르는 전류의 값들이 전류계(도시되지 않음)로 측정될 수 있는 것을 주의하라. 따라서, 나노-갭 전극(1)은 싱글-스트랜디드 DNA가 x-방향으로부터 전극들(5 및 6) 사이의 나노-갭(NG)을 거쳐 지나가게 하고; 싱글-스트랜디드 DNA의 염기들이 전극들(5 및 6) 사이의 나노-갭(NG)을 거쳐 지나갈 때 전류계가 전극들(5 및 6)을 가로질러 흐르는 전류들의 값들을 측정하게 하고; 그리고 싱글-스트랜디드 DNA를 구성하는 염기들이 상관된 전류 값들에 기초하여 결정될 수 있게 한다.

[0094] 다른 실시예들에서, 전극들(5 및 6) 사이에 나노-갭(NG)을 가지는 나노-갭 전극(1)을 제조하기 위한 방법이 본원에 설명된다. 실리콘 산화물 층(4)이 실리콘 기판(3) 상에 형성될 수 있는 기판(2)이 먼저 준비될 수 있고, 예컨대, 티타늄 질화물(TiN)로 만들어지고 측면 벽(9a)을 가지는 사각형 제 1 전극-형성 부분(9)은 도 2a, 및 도 2a의 섹션(A-A')의 측 단면도를 도시하는 도 2b에 도시된 바와 같이, 포토리소그래픽 기술을 사용하여 실리콘 산화물 층(4)의 미리 결정된 구역상에 형성될 수 있다.

[0095] 추후, 도 2a의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 2c 및 도 2b의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 2d에 도시된 바와 같이, 기판(2)의 표면(이 경우 실리콘 산화물 층(4))의 재료와 상이한 티타늄(Ti) 또는 실리콘 질화물(SiN) 같은 재료로 만들어진 측벽-형성 층(10)은 예컨대, CVD(화학 기상 증착) 방법에 의해 제 1 전극-형성 부분(9) 및 기판(2)의 노출된 부분들 상에 막-형성될 수 있다. 이때, 측벽-형성 층(10)은 제 1 전극-형성 부분(9)의 측면 벽(9a)을 따라 형성될 수 있다. 측면 벽(9a)상에 형성될 측벽-형성 층(10)의 막 두께는 나노-갭(NG)의 원하는 폭(W1)에 따라 선택될 수 있다. 즉, 작은 폭(W1)을 가진 나노-갭(NG)이 형성될 때, 측벽-형성 층(10)은 작은 막 두께로 형성될 수 있다. 다른 한편, 큰 폭(W1)을 가진 나노-갭(NG)이 형성될 때, 측벽-형성 층(10)은 큰 막 두께로 형성될 수 있다.

[0096] 추후, 제 1 전극-형성 부분(9) 및 기판(2)의 노출된 부분들 상에 막-형성된 측벽-형성 층(10)은 예컨대, 제 1 전극-형성 부분(9)의 측면 벽(9a)을 따라 측벽-형성 층(10)의 일부를 남기도록 건식 에칭에 의해 에칭 백될 수 있다. 에칭 프로세스는 기판(2)에 관하여 수직이도록 구성될 수 있거나, 또는 측벽-형성 층(10)의 일부가 제 1 전극-형성 부분(9)의 측면 벽(9a)에 의해 에칭으로부터 적어도 부분적으로 보호될 수 있도록 각이 이루어질 수 있다. 따라서, 측벽(11)은 도 2c의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 2e, 및 도 2d의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 2f에 도시된 바와 같이, 제 1 전극-형성 부분(9)의 측면 벽(9a)을 따라 형성될 수 있다. 이런 방식으로 형성된 측벽(11)이 제 1 전극-형성 부분(9)의 측면 벽(9a)의 정점으로부터 기판(2) 쪽으로 점진적으로 두꺼워질 수 있다는 것을 주의하라. 따라서, 측벽(11)의 최대 두께는 본원에 설명된 바와 같이, 이후 형성될 나노-갭(NG)에 대응하는 폭(W1)을 가질 수 있다는 것을 주의하라.

[0097] 추후, 도 2e의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 3a, 및 도 2f의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 3b에 도시된 바와 같이, 티타늄 질화물(TiN) 같은 금속 재료를 포함하는 제 2 전극-형성 부분(12)은 예컨대, 스퍼터링 방법에 의해 제 1 전극-형성 부분(9), 측벽(11) 및 기판(2)의 노출된 부분들 상에 형성될 수 있다. 그 다음, 제 1 전극-형성 부분(9) 및 측벽(11)뿐 아니라, 제 1 전극-형성 부분(9) 및 측벽(11)을 커버하는 제 2 전극-형성 부분(12)의 구역들은 화학 기계적 폴리싱 또는 평탄화(CMP) 같은 평탄화 프로세싱에 의해 폴리싱될 수 있고 오버 폴리싱(over polishe)될 수 있다. 따라서, 제 1 전극-형성 부분(9), 측벽(11) 및 제 2 전극-형성 부분(12)의 상단 표면들은, 도 3a의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 3c 및 도 3b의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 3d에 도시된 바와 같이, 노출될 수 있다.

[0098] 일부 실시예들에서, 측벽(11)의 측 표면의 크게 경사진 상부 구역 및 측벽(11) 및 전극 형성 부분(9) 위 제 2 전극-형성 부분(12)의 부분들은 폴리싱될 수 있고 제 1 전극-형성 부분(9), 측벽(11), 및 제 2 전극-형성 부분(12)은, 제 1 전극-형성 부분(9)과 제 2 전극-형성 부분(12) 사이의 측벽(11)의 단면이 실질적으로 사각형 형상으로 형성될 수 있을 때까지 평탄화 프로세싱으로 오버-폴리싱될 수 있다. 평탄화 프로세싱이 수행될 때 제 1 전극-형성 부분(9), 측벽(11) 및 제 2 전극-형성 부분(12) 모두의 표면들이 노출될 수 있다면, 제 1 전극-형성 부분(9) 및 측벽(11)을 커버하는 제 2 전극-형성 부분(12)의 구역들만이 폴리싱될 수 있다는 것을 주의하라.

[0099] 그 다음, 층-형 레지스트 마스크는 제 1 전극-형성 부분(9), 측벽(11) 및 제 2 전극-형성 부분(12)의 노출된 표면들 상에 형성될 수 있고, 그 다음 제 1 전극-형성 부분(9) 및 제 2 전극-형성 부분(12)은 포토리소그래픽 기술을 사용하여 패터닝될 수 있다. 일부 경우들에서, 레지스트 마스크는 폴리머릭 재료, 이를테면 폴리(메틸 메타크릴레이트)(PMMA), 폴리(메틸 글루타리마이드)(PMGI), 페놀 포름알데히드 수지, 또는 SU-8(Liu 등에 의한, "Process research of high aspect ratio micro structure using SU-8 resist," Microsystem Technologies 2004, V10, (4), 265를 참조하고, 이는 전체가 인용에 의해 본원에 포함됨)을 포함할 수 있다. 마스크는 베이스 부분들(5a 및 6a)에 대하여 완만한 곡선들, 및 리딩 전극 에지들(5b 및 6b)을 위한 돌출부들을 형성하기 위해 사용될 수 있다. 따라서, 부분적으로 제 1 전극-형성 부분(9)에 기초하여 미리 결정된 형상을 가진 전극(5) 및 부분적으로 제 2 전극-형성 부분(12)에 기초하여 미리 결정된 형상을 가진 전극(6)은, 도 3c의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 3e 및 도 3d의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 3f에 도시된 바와 같이, 형성될 수 있고, 이에 의해 리딩 전극 에지들(5b 및 6b)이 기판(2) 상에서 측벽(11)을 가로질러 서로 대향하여 배치될 수 있는 구조를 형성한다. 리딩 전극 에지들(5b 및 6b) 사이의 측벽(11)은 예컨대 습식 에칭에 의해 제거될 수 있다. 따라서, 리딩 전극 에지들(5b 및 6b) 사이에 측벽(11)의 폭(W1)과 동일한 폭(W1)을 가진 나노-갭(NG)을 형성하고, 도 1에 도시된 바와 같은 나노-갭 전극(1)을 제조하는 것이 가능하다. 측벽(11)이 예컨대 기판(2)의 표면상에 위치된 실리콘 산화물 층(4)과 상이한 질화물(N), 또는 일부 경우들에서, 실리콘 질화물(SiN) 같은 재료로 형성될 수 있기 때문에, 측벽(11)만을 선택적으로 제거하고 기판(2) 상에 전극들(5 및 6)을 신뢰성 있게 남기는 것은 가능하다.

[0100] 일부 경우들에서, 제 1 전극-형성 부분(9) 및 제 2 전극-형성 부분(12)은, 타겟 종(예컨대, DNA 또는 RNA 같은 생체분자)이 전극들 사이에 배치될 때 나노-갭을 횡단하는 전류를 검출하는 전극들로서 사용하기 위하여 준비된다. 전류는 터널링 전류일 수 있다. 그런 전류는 나노-갭을 통하여 타겟 종의 흐름시 검출될 수 있다. 일부 경우들에서, 전극들에 커플링된 감지 회로는 전류를 생성하기 위하여 전극들 양단에 인가된 전압을 제공한다. 대안으로서 또는 더하여, 전극들은 타겟 종(예컨대, 핵산 분자의 염기)과 연관된 전기 전도도를 측정 및/또는 식별하기 위하여 사용될 수 있다. 그런 경우에서, 터널링 전류는 전기 전도도에 관련될 수 있다.

[0101] 일부 경우들에서, 측벽(11)은 기판(2) 상에 이전에 형성될 수 있는 제 2 전극-형성 부분(9)의 측면 벽(9a) 상에 형성될 수 있고, 제 2 전극-형성 부분(12)은 제 1 전극-형성 부분(9), 측벽(11) 및 기판(2)의 노출된 부분들 상에 형성될 수 있다. 그 후, 제 2 전극-형성 부분(12)의 부분들은 제거되어 제 2 전극-형성 부분(12)으로 커버되는 제 1 전극-형성 부분(9) 및 측벽(11)의 부분들을 노출시킬 수 있고, 이에 의해 기판(2) 상의 제 1 전극-형성 부분(9), 측벽(11) 및 제 2 전극-형성 부분(12)이 노출된다. 그 다음, 제 1 전극-형성 부분(9)과 제 2 전극-형성 부분(12) 사이의 측벽(11)은 그 사이에 나노-갭(NG)을 형성하도록 제거될 수 있다. 그 후, 제 1 전극-형성 부분(9) 및 제 2 전극 형성 부분(12)은, 나노-갭(NG)이 리딩 전극 에지들(5b 및 6b) 사이에 제공될 수 있는 전극들(5 및 6)을 형성하도록 패터닝될 수 있다.

[0102] 상기 설명된 바와 같은 본 발명의 그런 제조 방법에서, 측벽(11)의 막 두께를 조절함으로써 원하는 폭(W1)을 가진 나노-갭(NG)을 형성하는 것이 가능하다. 게다가, 극히 작은 막 두께를 가진 측벽(11)을 형성하는 것이 가능하다. 그러므로 측벽(11)의 폭(W1)에 대응하는 극히 작은 폭(W1)을 가진 나노-갭(NG)을 형성하는 것이 가능하다.

[0103] 일부 실시예들에서, 폭(W1)을 가진 나노-갭(NG)은 마스크로서 제 1 전극-형성 부분(9)에 인접하게 배치된 측벽(11)을 사용하여 제 1 전극-형성 부분(9)과 제 2 전극-형성 부분(12) 사이에 형성된 측벽(11)의 막 두께를 제어함으로써 조절될 수 있다. 결과적으로, 종래의 나노-갭과 동일한 폭(W1)을 가진 나노-갭(NG)뿐 아니라, 종래의 나노-갭보다 훨씬 더 작은 폭(W1)인 나노-갭(NG)을 형성하는 것이 가능하다.

[0104] 상기 설명된 실시예들에서, 제 2 전극-형성 부분(12)이 도 3b에 도시된 바와 같이, 제조 과정에서 제 1 전극-형성 부분(9) 상에 직접 형성되는 것으로 설명되었다는 것을 주의하라. 다른 실시예들에서, 또한 하드 마스크를 포함하는 표면상의 제 1 전극-형성 부분(9)은 제 1 전극-형성 부분(9) 상에 제 2 전극-형성 부분(12)을 직접 형성하지 않고 사용될 수 있다. 심지어 이 경우, 측벽(11)에 인접하도록 제 2 전극-형성 부분(12)을 형성하고, 제 1 전극-형성 부분(9)과 제 2 전극-형성 부분(12) 사이에 측벽(11)을 배치하는 것이 가능하다. 결과적으로, 측벽(11)을 제거함으로써 제 1 전극-형성 부분(9)과 제 2 전극-형성 부분(12) 사이에 나노-갭(NG)을 형성하는 것이 가능하다.

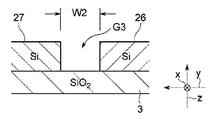

[0105] 대안 나노-갭 전극(21)을 묘사하는 도 4에 도시된 바와 같은 다른 실시예들에서, 자신의 선단 표면들이 서로를 향하는 원주 전극들(25 및 26)이 기판(22) 상에 배치된다. 나노스케일(예컨대, 1000 nm보다 크지 않음)일 수 있는 폭(W1)을 가진 나노-갭(NG)은 전극들(25 및 26) 사이에 형성될 수 있다. 일부 실시예들에서, 나노-갭 전극(21)은 본원에 설명된 바와 같이 제조 방법에 의해 제조될 수 있고, 나노-갭(NG)은 0.1 nm 내지 30 nm, 또는 2 nm, 1 nm, 0.9 nm, 0.8 nm, 0.7 nm, 0.6 nm, 또는 0.5 nm보다 크지 않거나, 본원에 설명된 바와 같은 임의의 다른 폭으로 형성될 수 있다.

[0106] 일부 실시예들에서, 기판(22)은 예컨대, 실리콘 기판(도시되지 않음) 상에 형성된 실리콘 산화물 층(27)을 포함할 수 있고, 전극-지지 부분들(28 및 29)은 실리콘 산화물 층(27) 상에서 서로 대향하여 배치될 수 있다. 기판의 표면상에서, 하나의 전극(25)은 하나의 전극-지지 부분(28) 상에 배치될 수 있고, 전극(25)과 쌍을 형성하는 다른 전극(26)은 전극-지지 부분(29) 상에 배치될 수 있다.

[0107] 양쪽 전극-지지 부분들(28 및 29)이 티타늄 질화물(TiN) 같은 금속을 포함하는 재료로 만들어질 수 있고, 전극 지지 부분들(28 및 29) 사이에서 기판 위에 형성된 미리 결정된 갭을 가로질러 거의 양방향으로 대칭으로 형성될 수 있고, 전극-지지 부분들(28 및 29)의 전면 표면들이 실리콘 산화물 층(27)의 전면 표면과 같은 높이일 수 있다는 것을 주의하라. 일부 실시예들에서, 전극-지지 부분들(28 및 29)은 실질적으로 동일한 구성을 가질 수 있고 팽창된 전극-지지 부분들(28b 및 29b)을 포함할 수 있고 그 결과 전극(25 및 26)은 고정될 수 있고, 베이스 부분들(28a 및 29a)은 팽창된 전극-지지 부분들(28b 및 29b)의 루트 부분들에 일체형으로 형성될 수 있고, 여기서 팽창된 전극-지지 부분들(28b 및 29b)은 전극-형성 베이스 부분들(28a 및 29a)로부터 돌출한다. 일부 실시예들에서, 전극-지지 부분들(28 및 29)의 팽창된 전극-형성 부분들(28b 및 29b)은 실질적으로 반원 형상으로 형성될 수 있고, 전극-형성 베이스 부분들(28a 및 29a)은 팽창된 전극-형성 부분들(28b 및 29b)의 중앙 리딩 에지들을 가지며 자신의 양쪽 측면 부분들 쪽으로 완만하게 경사질 수 있고 팽창된 전극 부분들(28b 및 29b)은 자신의 중심점에 가까운 중앙 축 상에 포지셔닝되어 위치될 수 있다. 따라서, 전체로서 전극-지지 부분들(28 및 29)은 정점들로서 팽창된 전극 부분들(28b 및 29b)이 볼록하게 형성될 수 있다.

[0108] 게다가, 원주 전극들(25 및 26)은 전도 재료, 이를테면 탄소 나노튜브로 형성될 수 있고, 전극들(25 및 26)의 외부 원주 표면은 개별적으로 팽창된 전극 부분들(28b, 29b) 상에 고정될 수 있다. 따라서, 전극들(25 및 26)은, 그 길이 방향이 y-방향으로 연장되고 그 선단 표면들이 서로를 향하도록 배치될 수 있다.

[0109] 상기 설명된 바와 같이 구성된 나노-갭 전극(21)에서, 전류가 예컨대 전력 원(도시되지 않음)으로부터 전극들(25 및 26)에 공급될 수 있고, 전극들(25 및 26)을 가로질러 흐르는 전류의 값들이 전류계(도시되지 않음)로 측정될 수 있다는 것을 주의하라. 따라서, 나노-갭 전극(21)은 싱글-스트랜디드 DNA가 가이딩(guiding) 부재들(도시되지 않음)에 의해 x-방향으로부터 적어도 부분적으로 전극들(25 및 26) 사이의 나노-갭(NG)을 거쳐 통과되게 하고; 싱글-스트랜디드 DNA의 염기들이 전극들(25 및 26) 사이에서 나노-갭(NG)을 거쳐 통과할 때 전류계가 전극들(25 및 26)을 가로질러 흐르는 전류들의 값들을 측정하게 하고; 그리고 싱글-스트랜디드 DNA를 구성하는 염기들이 전류 값들에 기초하여 결정되게 한다.

[0110] 일부 실시예들에서, 나노-갭 전극(21)을 제조하기 위한 방법은 전극들(25 및 26) 사이에 나노-갭(NG)을 형성하는 것을 포함할 수 있다. 도 5를 참조하여, 기판상의 미리 결정된 형상을 가진 전극-지지 부분들(28 및 29)이 실리콘 산화물 층(27)에 인접하여 형성될 수 있다. 그 다음, 원주 전극-형성 부분(31)은 전극-지지 부분들(28 및 29)의 팽창된 전극 부분들(28b 및 29b) 위에서 브리지(bridge)하도록, 실리콘 산화물 층(27)의 표면 위 전극-지지 부분(28)의 표면으로부터 다른 전극-지지 부분(29)의 표면까지 형성될 수 있다. 도 5의 구성 엘리먼트들은 도 4의 구성 엘리먼트들에 대응하고 동일한 참조 번호들에 의해 나타내진다. 도 6a는 도 5의 섹션(B-B')을 따르는 측 단면 구성을 도시한다.

[0111] 추후, 도 6a의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 6b에 도시된 바와 같이, 레지스트 마스크의 막 층은 전극-형성 부분(31), 실리콘 산화물 층(27), 및 전극-지지 부분들(28 및 29) 상에 적용될 수 있다. 그 후, 레지스트 마스크(32)는, 도 4에 도시된 바와 같은 나노-갭의 폭(W1)보다 큰 폭(W2)을 가진 개구(34a)가 형성될 수 있는 포토마스크(34)를 사용하여 노광 및 현상에 의해 패터닝될 수 있다. 갭-형성 마스크로서 역할을 하는 레지스트 마스크(32)가 패터닝될 때, 전극-형성 부분(31)의 나노-갭(NG)이 형성될 포토마스크(34)의 구역에 개구(34a)가 위치되는 것을 주의하라.

[0112] 추후, 도 6b의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 6c에 도시된 바와 같이, 측면 벽들(33a 및 33b) 그 사이에 폭(W2)을 가진 채로 서로 대향하게 배치되는 갭(32a)은, 도 4에 도시된 바와 같이 나노-갭(NG)이 형성될 구역에 대응하는 레지스트 마스크(32)의 구역으로부터 형성될 수 있다. 따라서, 전극-형성 부분(31)은 갭(32a)을 통해 노출될 수 있다. 추후, 도 6c의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 7a에 도시된 바와 같이, 실리콘 산화물 층(27) 및 전극-지지 부분들(28 및 29)의 표면들의 재료와 상이한 티타늄(Ti) 또는 실리콘 질화물(SiN) 같은 재료를 포함할 수 있는 측벽-형성 층(35)은 예컨대, 기상 증착 기술, 예컨대 화학 기상 증착(CVD)과 같은 기상 증착 기술에 의해 레지스트 마스크(32) 상에 및 전극-형성 부분(31)의 부분들 및 레지스트 마스크(32)로부터 형성된 갭(32a) 내에서 노출된 실리콘 산화물 층 상에 막-형성될 수 있다. 이때, 미리 결정된 막 두께를 가질 수 있는 측벽-형성 층(35)은 또한 갭(32a) 내의 레지스트 마스크(32)의 측면 벽들(33a 및 33b) 상에 형성될 수 있다.

[0113] 추후, 전극-형성 부분(31), 및 실리콘 산화물 층(27) 상에 막-형성된 측벽-형성 층(35)은 레지스트 마스크(32)의 측면 벽들(33a 및 33b)을 따라 측벽-형성 층(35)을 남기도록 예컨대 건식 에칭에 의해 레지스트 마스크(32)로부터 형성된 갭(32a) 내에서 에칭 백될 수 있다. 따라서, 측벽들(37)은 도 7a의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 7b에 도시된 바와 같이, 레지스트 마스크(32)의 측면 벽들(33a 및 33b)을 따라 형성될 수 있다. 일부 상황들에서, 측벽들(37)은 레지스트 마스크(32)의 측면 벽들(33a 및 33b)의 정점들로부터 전극-형성 부분(31) 및 실리콘 산화물 층(27) 쪽으로 점진적으로 두꺼워질 수 있다. 따라서, 갭(32a)의 폭(W2)은 양쪽 측벽들(37)의 결합된 두께만큼에 의해 좁아질 수 있다. 그런 두껍게 함은 타겟 분자 검출 같은 다양한 애플리케이션들에 사용하기 위한 나노-갭 폭을 선택하기 위해 사용될 수 있다.

[0114] 결과적으로, 전극-형성 부분(31)이 갭(32a) 내에서 노출될 수 있는 폭(W1)은 측벽들(37)의 막 두께들 만큼에 의해 레지스트 마스크(32)로부터 형성된 갭(32a)의 폭(W2)보다 작게 만들어질 수 있다. 추후, 서로 대향하여 배치된 측벽들(37) 사이의 W1-폭 갭에서 노출된 전극 형성 부분(31)의 부분은 예컨대 건식 에칭에 의해 제거될 수 있다. 따라서, 폭(W1)을 가진 나노-갭(NG)은 측벽들(37) 사이에 형성될 수 있고, 그리고 나노-갭(NG)을 가로질러 서로 대향하여 배치된 2개의 전극들(25 및 26)은 도 7b의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 7c에 도시된 바와 같이, 형성될 수 있다.

[0115] 전극-형성 부분(31)이 본원에 설명된 바와 같은 레지스트 마스크(32)로부터 형성된 갭(32a) 내에서 노출될 수 있는 폭(W1)은 결국 형성될 나노-갭(NG)의 폭(W1)으로서 역할을 할 수 있다. 따라서, 레지스트 마스크(32)의 측면 벽들(32a 및 32b) 상에 측벽-형성 층(35)을 형성하는 프로세스에서, 측벽-형성 층(35)의 막 두께는 나노-갭(NG)의 원하는 폭(W1)에 따라 선택될 수 있다. 즉, 작은 폭(W1)을 가진 나노-갭(NG)이 형성될 때, 측벽-형성 층(35)은 레지스트 마스크(32)로부터 형성된 갭(32a) 내에서 노출된 전극-형성 부분(31)의 폭(W1)을 감소시키도록 두껍게 형성될 수 있다. 다른 한편, 큰 폭(W1)을 가진 나노-갭(NG)이 형성될 때, 측벽-형성 층(35)은 레지스트 마스크(32)로부터 형성된 갭(32a) 내에서 노출된 전극-형성 부분(31)의 폭(W1)을 증가시키도록 얇게 형성될 수 있다.

[0116] 마지막으로, 전극들(25 및 26) 및 실리콘 산화물 층(27) 상에 위치된 측벽들(37)의 부분들은 예컨대 습식 에칭에 의해 제거될 수 있다. 그 후, 전극들(25 및 26) 및 실리콘 산화물 층(27) 상에 위치된 레지스트 마스크(32)는 스트립핑(stripping)에 의해 제거될 수 있다. 따라서, 도 4에 도시된 바와 같이, 전극들(25 및 26) 사이에 나노-갭(NG)을 가진 나노-갭 전극(21)을 형성하는 것은 가능하다. 이 경우에, 측벽들(37)이 먼저 제거되고, 그 다음 레지스트 마스크(32)가 제거되는 것을 주의하라. 대안적으로 레지스트 마스크(32)는 먼저 제거될 수 있고, 그 다음 측벽들(37)이 제거될 수 있다.

[0117] 상기 설명된 구성에서, 갭을 가로질러 서로를 향하는 측면 벽들(33a 및 33b)을 포함하는 레지스트 마스크(32)는 전극-형성 부분(31) 상에 형성될 수 있고, 측벽들(37)은 레지스트 마스크(32)의 양쪽 측면 벽들(33a 및 33b) 상에 개별적으로 형성될 수 있고, 전극 형성 부분(31)은 측벽들(37) 사이에서 노출되고, 그 다음 측벽들(37) 사이에서 노출된 전극-형성 부분(31)이 제거되어 나노-갭(NG)을 형성할 수 있다.

[0118] 상기 설명된 바와 같은 그런 제조 방법에서, 레지스트 마스크(32)로부터 형성된 갭(32a)의 폭(W2)에 더하여, 각각의 측벽(37)의 막 두께를 조절함으로써 원하는 폭(W1)을 가진 나노-갭(NG)을 형성하는 것이 가능하다. 게다가, 측벽들(37)은 이 제조 방법에서 레지스트 마스크(32)로부터 형성된 측면 벽들(33a 및 33b) 상에 형성될 수 있고, 그러므로, 레지스트 마스크(32)로부터 형성된 갭(32a)의 폭(W2)은 측벽들(37)의 막 두께들 만큼에 의해 더 작게 만들어질 수 있다. 따라서, 패터닝된 레지스트 마스크(32)에 형성된 갭(32a)의 폭(W2)보다 훨씬 더 작은 폭(W1)을 가진 나노-갭(NG)을 형성하는 것이 가능하다.

[0119] 상기 설명된 구성에 따라, 측벽들(37)의 막 두께들에 의해 조절된 폭(W1)을 가진 나노-갭(NG)은 마스크의 일부로서 전극-형성 부분(31) 상에 배치된 측벽들(37)을 사용하여 전극-형성 부분(31) 상에 형성될 수 있다. 결과적으로, 종래의 나노-갭과 폭(W1)이 동일한 나노-갭(NG)뿐 아니라, 종래의 리소그래픽 기술들을 사용하여 형성된 종래의 나노-갭보다 폭(W1)이 훨씬 더 작은 나노-갭(NG)을 형성하는 것이 가능하다.

[0120] 일부 경우들에서, 갭(32a)을 가진 레지스트 마스크(32)는 전극-형성 부분(31) 상에 직접 형성될 수 있다. 다른 실시예들에서, 하드 마스크가 형성될 수 있는 표면상의 전극-형성 부분은 하드 마스크에 갭을 가진 갭-형성 마스크를 형성하기 위하여 사용될 수 있고, 갭-형성 마스크는 하드 마스크에 의해 형성된 갭에서 전극-형성 부분 상에 배치될 수 있다.

[0121] 이 실시예에서, 레지스트 마스크(32)로부터 형성된 양쪽 측면 벽들(33a 및 33b) 상에 형성된 측벽들(37) 사이에 노출된 하드 마스크 재료만이 하드 마스크에 갭을 형성하기 위하여 제거될 수 있다. 그 다음, 측벽들(37) 사이에 위치된 하드 마스크의 갭을 통한 전극-형성 부분(31)의 일부는 예컨대 건식 에칭에 의해 제거될 수 있고, 이에 의해 측벽들(37) 사이에 나노-갭(NG)이 형성된다.

[0122] 또한 본원에 설명된 바와 같이, 레지스트 마스크(32)는 마스크로서 적용될 수 있다. 다른 실시예들에서, 레지스트 외에 다양한 재료들 중 하나로 만들어진 마스크는, 갭이 형성될 수 있고 측벽들이 갭의 측면 벽들 상에 형성될 수 있다면, 적용될 수 있다. 결과적으로 제조될 나노-갭 전극이, 도 7c에 도시된 바와 같이 측벽들(37)이 제거되기보다 적소에 남겨질 수 있는 나노-갭 전극일 수 있다는 것을 주의하라. 대안적으로, 측벽들은 추후 프로세스의 부분으로서 제거될 수 있다. 일부 실시예들에서, 레지스트 마스크(32)는 적소에 남겨질 수 있고; 대안으로서, 레지스트 마스크(32)는 제거될 수 있다.

[0123] 도 4에 도시된 나노-갭 전극(21)을 제조하기 위한 대안적인 방법들이 본원에 설명된다. 일부 실시예들에서, 미리 결정된 형상을 가질 수 있는 전극-지지 부분들(28 및 29)이 실리콘 산화물 층(27)에 인접하게 형성될 수 있는 기판이 먼저 준비될 수 있다. 그 다음, 탄소 나노튜브로 만들어진 전극-형성 부분(31)은 도 5에 도시된 바와 같이, 전극-지지 부분들(28 및 29)의 팽창된 전극 부분들(28b 및 29b) 위에서 브리지하도록, 실리콘 산화물 층(27)의 표면 위의 하나의 전극-지지 부분(28)의 표면으로부터 다른 전극-지지 부분(29)의 표면까지 형성 또는 적용될 수 있다.

[0124] 다른 실시예들에서, 전극-형성 부분(31)은 금, Pt 또는 다른 금속 또는 합금 나노와이어들을 포함할 수 있거나, 반도체 나노와이어들을 포함할 수 있고, 여기서 나노와이어들은 나노미터의 직경을 가질 수 있거나, 몇 나노미터만큼 크거나 또는 그 보다 큰 직경을 가질 수 있다.

[0125] 다른 실시예들에서, 전극 형성 부분(31)은 금속 또는 합금 또는 반도체의 얇은 층(예컨대, 모노층(monolayer))을 포함할 수 있다. 추후, 예컨대 레지스트 재료로 만들어진 측벽-형성 마스크(40)의 층은 전극-형성 부분(31) 및 실리콘 산화물 층(27) 상에 막으로서 형성될 수 있다. 그 후, 측벽-형성 마스크(40)는 포토리소그래픽 기술을 사용하여 패터닝될 수 있다. 결과적으로, 도 5의 섹션(B-B')의 측 단면 구성을 도시하는 도 8a에 도시된 바와 같이, 측벽-형성 마스크(40)의 측면 벽(40a)은, 도 4에 도시된 바와 같이 전극-형성 부분(31)의 나노-갭(NG)이 형성될 구역과 정렬하여 전극-형성 부분(31) 및 실리콘 산화물 층(27) 상에 형성될 수 있다.

[0126] 추후, 측벽-형성 층(도시되지 않음)은 측벽-형성 마스크(40) 및 전극-형성 부분(31)의 노출된 부분들 및 전극-형성 부분(31)의 재료와 상이한 티타늄(Ti) 또는 실리콘 질화물(SiN) 같은 재료를 포함할 수 있는 실리콘 산화물 층(27) 상에 막으로서 형성될 수 있다. 그 후, 측벽-형성 층은 측벽-형성 마스크(40)의 측면 벽(40a)을 따라 측벽-형성 층의 일부를 남기도록 건식 에칭에 의해 에칭 백될 수 있다. 따라서, 측벽(37)은 도 8a에 도시된 바와 같이, 측벽-형성 마스크(40)의 측면 벽(40a)을 따라 형성될 수 있다. 이런 방식으로 형성된 측벽(37)이 측벽-형성 마스크(40)의 측면 벽(40a)의 정점으로부터 전극-형성 부분(31) 및 실리콘 산화물 층(27) 쪽으로 점진적으로 두꺼워질 수 있다는 것을 주의하라. 따라서, 측벽(37)의 최대 두께는 결국에 형성될 나노-갭(NG)의 폭(W1)일 수 있다.

[0127] 추후, 도 8a의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 8b에 도시된 바와 같이, 측벽-형성 마스크(40)는 전극-형성 부분(31) 상에 수직으로 만들어진 측벽(37)을 남기도록 제거될 수 있다. 그런 경우 측벽은 독립형 측벽일 수 있다. 독립형 측벽은 약 10 나노미터(nm), 5 nm, 4 nm, 3 nm, 2 nm, 1 nm, 0.9 nm, 0.8 nm, 0.7 nm, 0.6 nm 또는 0.5 nm 또는 그 미만의 폭을 가질 수 있다. 도 8b의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 8c를 참조하여, 갭-형성 마스크로서 역할을 할 수 있는 레지스트 마스크(41)는 전극-형성 부분(31) 및 실리콘 산화물 층(27) 상에 형성될 수 있다. 상기 설명된 바와 같이 그런 레지스트 마스크(41)는 전극-형성 부분(31) 및 실리콘 산화물 층(27)의 노출된 부분들 상에 레지스트 코팅 재료를 코팅하고 레지스트 코팅 재료를 경화함으로써 형성될 수 있다. 여기서, 레지스트 마스크(41)를 형성하도록 선택될 수 있는 레지스트 코팅 재료는 점성이 낮을 수 있다. 따라서, 예컨대 전극-형성 부분(31) 및 실리콘 산화물 층(27) 상에 코팅될 때 레지스트 코팅 재료가 측벽(37)의 상부 부분에 부착되더라도, 재료는 원심력으로 균일한 막으로 형성될 때 재료 자체의 무게, 및 웜심력 등으로 인해 측벽(37)의 상부 부분에서 떨어져 나간다. 따라서, 측벽(37)의 상부 부분은 레지스트 코팅 재료에 매몰되지 않고 노출될 수 있다. 결과적으로, 측벽(37)의 상부 부분은 레지스트마스크(41)의 표면 밖으로 노출될 수 있다.

[0128] 레지스트 코팅 재료의 점성이 높고 측벽(37)의 상부 부분에 부착하는 레지스트 코팅 재료의 일부가 그 위에서 경화하고, 그러므로 전체로서 측벽(37)이 레지스트 마스크(41)로 커버되거나, 레지스트 마스크(41)가 큰 막 두께를 가지며 그러므로, 전체로서 측벽(37)이 레지스트 마스크(41)로 커버되면, 측벽(37)의 상부 부분은 도 8c에 도시된 바와 같이 레지스트 마스크(41)를 에칭 백함으로써 레지스트 마스크(41)의 표면에서 노출될 수 있다는 것을 주의하라.

[0129] 추후, 도 8c의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 9a에 도시된 바와 같이, 노출될 수 있는 상부 부분은 측벽(37)이 위치되는 레지스트 마스크(41)의 구역에 갭(42)을 형성하도록, 예컨대 습식 에칭에 의해 제거될 수 있다. 따라서, 전극-형성 부분(31)은 갭(42)을 통해 노출될 수 있다. 그 다음 도 9a의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 9b에 도시된 바와 같이, 레지스트 마스크(41)의 갭(42)을 통해 노출된 전극-형성 부분(31)의 일부는 예컨대 건식 에칭에 의해 제거될 수 있고, 이에 의해 나노-갭(NG)이 형성되고 여기서 전극들(25 및 26)은 전극-형성 부분(31) 상 나노-갭(NG)을 가로질러 서로 대향하여 배치된다.

[0130] 전극-형성 부분(31)이 본원에 설명된 바와 같이 레지스트 마스크(41)의 갭(42)을 통해 노출될 수 있는 폭은 추후 형성될 도 4에 도시된 바와 같은 나노-갭(NG)의 폭(W1)으로서 역할을 한다. 따라서, 측벽-형성 마스크(40)의 측면 벽(40a) 상에 측벽-형성 층을 형성하는 프로세스에서, 측벽-형성 층의 막 두께는 나노-갭(NG)의 원하는 폭(W1)에 따라 선택될 수 있다. 즉, 작은 폭(W1)을 가진 나노-갭(NG)이 형성될 때, 측벽-형성 층은 레지스트 마스크(41)의 갭(42)을 통하여 노출된 전극-형성 부분(31)의 폭을 감소시키도록 얇게 형성될 수 있다. 다른 한편, 큰 폭(W1)을 가진 나노-갭(NG)이 형성될 때, 측벽-형성 층은 레지스트 마스크(41)의 갭(42)을 통하여 노출된 전극-형성 부분(31)의 폭을 증가시키도록 두껍게 형성될 수 있다.

[0131] 마지막으로, 전극들(25 및 26) 및 실리콘 산화물 층(27) 상에 위치된 레지스트 마스크(41)는 예컨대 스트립핑에 의해 제거될 수 있다. 따라서 도 4에 도시된 바와 같이 전극들(25 및 26) 사이에 나노-갭(NG)을 가진 나노-갭 전극(21)을 형성하는 것은 가능하다. 다른 실시예들에서, 레지스트 마스크(41)가 적소에 남겨질 수 있고, 예컨대 전극들(25 및 26)과 상호작용하도록 DNA가 이동할 수 있는 채널로서 사용될 수 있다.

[0132] 상기 설명된 구성에서, 측벽(37)은 전극-형성 부분(31) 상에 배치된 측벽-형성 마스크(40)의 측면 벽(40a) 상에 형성될 수 있고, 그 다음 측벽-형성 마스크(40)는 측벽(37)을 수직으로 만들기 위하여 제거될 수 있다. 레지스트 마스크(41)는 측벽(37)을 둘러싸도록 형성될 수 있다. 그 다음, 레지스트 마스크(41)에 의해 둘러싸인 측벽(37)은 레지스트 마스크(41) 내에 갭(42)을 형성하고 갭(42)을 통하여 전극-형성 부분(31)을 노출시키도록 제거될 수 있다. 그 후, 갭(42)을 통하여 노출된 전극-형성 부분(31)의 임의의 부분(들)은 갭(42) 내에 나노-갭(NG)을 형성하도록 제거될 수 있다.

[0133] 본원에 설명된 바와 같은 그런 제조 방법에서, 레지스트 마스크(41)에 형성될 갭(42)의 폭은 각각의 측벽(37)의 막 두께를 조절함으로써 조절될 수 있다. 결과적으로, 갭(42) 내에 형성될 나노-갭(NG)은 원하는 폭(W1)으로 형성될 수 있다. 게다가, 측벽(37)이 극히 작은 막 두께로 형성될 수 있기 때문에, 측벽(37)의 두께에 대응하는 극히 작은 폭(W1)을 가진 나노-갭(NG)을 형성하는 것이 가능하다.

[0134] 상기 설명된 구성에 따라, 측벽들(37)의 막 두께들에 의해 조절되는 폭(W1)을 가진 나노-갭(NG)은 마스크로서 전극-형성 부분(31) 상에 배치된 측벽(37)을 사용하여 전극-형성 부분(31) 상에 형성될 수 있다. 결과적으로, 종래의 나노-갭과 폭(W1)이 동일한 나노-갭(NG)뿐 아니라, 종래의 나노-갭보다 폭(W1)이 훨씬 더 작은 나노-갭(NG)을 형성하는 것이 가능하다.

[0135] 상기 본원에 설명된 바와 같이 측벽(37)을 형성하도록 측벽-형성 마스크(40)의 측면 벽(40a)을 따라 남아 있게 만들어진 측벽-형성 층이 벽 형상으로 수직으로 만들어질 수 있는 것을 주의하라. 다른 실시예들에서, 측벽-형성 마스크(40) 상의 측벽-형성 층만이 측벽-형성 마스크(40)의 측면 벽(40a)을 따라 측벽-형성 층을 남기도록 제거될 수 있다. 게다가, 측벽-형성 층은 실리콘 산화물 층(27) 및 전극-형성 부분(31) 상에 남겨지도록 만들어질 수 있고 여기서 측벽-형성 마스크(40)는 존재하지 않는다. 따라서, 단면이 L 형상을 가지는 바닥 표면을 가진 측벽이 형성될 수 있다.

[0136] 갭-형성 마스크로서 역할을 하는 측벽-형성 마스크(40) 및 레지스트 마스크(41)는 레지스트 재료로 형성될 수 있다. 다른 실시예들에서 측벽-형성 마스크(들) 및 갭 형성 마스크(들)은 다양한 다른 재료들로 형성될 수 있다.

[0137] 본 개시는 도 4에 도시된 바와 같이 나노-갭 전극(21)을 제조하기 위한 방법들을 제공한다. 도 4에 도시된 나노-갭 전극(21)의 구성의 설명은 이전 설명을 다시 하는 것을 회피하기 위하여 여기서 생략될 것이라는 것을 주의하라. 일부 실시예들에서, 미리 결정된 형상을 가진 전극-지지 부분들(28 및 29)이 실리콘 산화물 층(27)에 인접하게 형성되는 기판이 먼저 준비될 수 있다. 그 다음, 탄소 나노튜브로 만들어진 전극-형성 부분(31)은 도 5에 도시된 바와 같이 전극-지지 부분들(28 및 29)의 팽창된 전극 부분들(28b 및 29b) 위에서 브리지하도록, 실리콘 산화물 층(27)의 표면을 가로질러 하나의 전극-지지 부분의 표면으로부터 다른 전극-지지 부분(29)의 표면까지 형성될 수 있다.

[0138] 게다가, 측벽이 습식 에칭에 의해 제거되는 이후 설명되는 제조 과정에서 탄소 나노튜브를 포함할 수 있는 전극-형성 부분(31)이 에칭되는 것을 방지하기 위하여, 예컨대 실리콘 질화물(SiN)로 만들어질 수 있는 에칭-스톱 막(도시되지 않음)은 전극-형성 부분(31) 및 실리콘 산화물 층(27) 상에 형성될 수 있다.

[0139] 추후, 예컨대 폴리실리콘 또는 비결정질 실리콘으로 만들어질 수 있는 층-형 제 1 갭-형성 마스크는 CVD 방법 등에 의해 전극-형성 부분(31) 및 실리콘 산화물 층(27) 상에 에칭-스톱 막에 대한 막으로서 형성될 수 있다. 그 후, 제 1 갭-형성 마스크는 포토리소그래픽 기술을 사용하여 패터닝될 수 있다. 결과적으로, 도 5의 섹션(B-B')의 측 단면도를 가진 디바이스를 제조하는 방법을 묘사하는 도 10a에 도시된 바와 같이, 제 1 갭-형성 마스크(45)의 측면 벽(45a)은, 도 4에 도시된 바와 같이 전극-형성 부분(31)의 나노-갭(NG)이 형성될 수 있는 구역과 정렬하여 전극-헝성 부분(31) 및 실리콘 산화물 층(27) 상에 위치될 수 있는 에칭-스톱 막(도시되지 않음) 상에 형성될 수 있다.

[0140] 추후, 예컨대 전극-형성 부분(31)의 재료와 상이한 재료일 수 있는 예컨대 실리콘 산화물로 만들어질 수 있는 측벽-형성 층(도시되지 않음)은 전극-형성 부분(31) 및 실리콘 산화물 층(27) 및 제 1 갭-형성 마스크(45) 상에 에칭-스톱 막에 대한 막으로서 형성될 수 있다. 그 후, 측벽-형성 층은 제 1 갭-형성 마스크(45)의 측면 벽(45a)을 따라 측벽-형성 층을 남기기 위해 건식 에칭에 의해 에칭 백될 수 있다. 따라서, 측벽(37)은 도 10a에 도시된 바와 같이 제 1 갭-형성 마스크(45)의 측면 벽(45a)을 따라 형성될 수 있다. 이런 방식으로 형성된 측벽(37)이 제 1 갭-형성 마스크(45)의 측면 벽(45a)의 정점으로부터 전극-형성 부분(31) 및 실리콘 산화물 층(27) 및 에칭-스톱 층 쪽으로 점진적으로 두꺼워질 수 있다는 것을 주의하라. 따라서, 측벽(37)의 최대 두께는 추후에 형성될 나노-갭(NG)의 폭(W1)일 수 있다.

[0141] 추후에, 도 10a의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 10b에 도시된 바와 같이, 예컨대 폴리실리콘 또는 비결정질 실리콘으로 만들어질 수 있는 제 2 갭-형성 마스크(46)는 CVD 방법 등에 의해 전극-형성 부분(31) 및 실리콘 산화물 층(27) 상에, 측벽(37) 상에 그리고 제 1 갭-형성 마스크(45) 상에 위치된 에칭-스톱 막(도시되지 않음)에 대한 막으로서 형성될 수 있다.

[0142] 그 다음, 제 1 갭-형성 마스크(45) 및 측벽(37), 제 1 갭-형성 마스크(45) 및 측벽(37)을 커버하는 제 2 갭-형성 마스크(46)의 구역들은 CMP 같은 평탄화 프로세싱에 의해 폴리싱될 수 있고 오버-폴리싱될 수 있다. 따라서, 제 1 갭-형성 마스크(45), 측벽(37) 및 제 2 갭-형성 마스크(46)의 표면들은, 도 10b의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 10c에 도시된 바와 같이 노출될 수 있다.

[0143] 일부 실시예들에서, 제 1 갭-형성 마스크(45) 및 제 2 갭-형성 마스크(46) 사이의 측벽(37)의 단면이 실질적으로 사각형 형상으로 형성될 수 있을 때까지 평탄화 프로세싱 동작에서, 측벽(37)의 측 표면의 크게 경사진 상부 구역은 폴리싱될 수 있고 제 1 갭-형성 마스크(45), 측벽(37) 및 제 2 갭-형성 마스크(46)는 폴리싱될 수 있고, 그리고 오버-폴리싱될 수 있다. 일부 실시예들에서, 평탄화 프로세싱 동작이 수행될 때 제 1 갭-형성 마스크(45), 측벽(37), 및 제 2 갭-형성 마스크(46)의 표면들이 노출될 수 있으면, 제 1 갭-형성 마스크(45) 및 측벽(37)을 커버하는 제 2 갭-형성 마스크(46)의 구역들만 폴리싱될 수 있다는 것을 주의하라.

[0144] 추후, 도 10c의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 11a에 도시된 바와 같이, 제 1 갭-형성 마스크(45) 및 제 2 갭-형성 마스크(46) 사이에 위치된 측벽(37)은 측벽(37)과 동일한 폭인 갭(49)을 형성하기 위하여 예컨대 습식 에칭에 의해 제거될 수 있다. 따라서, 전극-형성 부분(31) 상의 에칭-스톱 막(도시되지 않음)은 갭(49)을 통하여 노출될 수 있다.

[0145] 그 다음, 도 11a의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 11b에 도시된 바와 같이, 제 1 갭-형성 마스크와 제 2 갭-형성 마스크(46) 사이의 갭(49)을 통하여 노출된 에칭-스톱 막(도시되지 않음) 및 전극-형성 부분(31)의 부분들은 예컨대 건식 에칭에 의해 제거될 수 있고, 이에 의해 나노-갭(NG) 및 전극-형성 부분(3)의 나노-갭(NG)을 가로질러 서로 대향하여 배치된 전극들(25 및 26)이 형성된다.

[0146] 상기 설명된 바와 같이 제 1 갭-형성 마스크(45)와 제 2 갭-형성 마스크(46) 사이에 위치된 갭(49) 내의 전극-형성 부분(31)의 폭은 추후에 형성될 도 4에 도시된 바와 같은 나노-갭(NG)의 폭(W1)으로서 역할을 한다. 따라서, 제 1 갭-형성 마스크(45)의 측면 벽(45a) 상에 측벽-형성 층을 형성하는 프로세스에서, 측벽-형성 층의 막 두께는 나노-갭(NG)의 원하는 폭(W1)에 따라 선택될 수 있다. 즉, 작은 폭(W1)을 가진 나노-갭(NG)이 형성될 때, 측벽-형성 층은 제 1 갭-형성 마스크(45) 및 제 2 갭-형성 마스크(46) 사이에서 갭(49) 내에서 노출된 전극-형성 부분(31)의 폭을 감소시키도록 얇게 형성될 수 있다. 다른 한편, 큰 폭(W1)을 가진 나노-갭(NG)이 형성될 때, 측벽-형성 층은 제 1 갭-형성 마스크(45)와 제 2 갭-형성 마스크(46) 사이의 갭(49) 내에서 노출된 전극-형성 부분(31)의 폭을 증가시키기 위하여 두껍게 형성될 수 있다.

[0147] 마지막으로, 전극들(25 및 26) 및 실리콘 산화물 층(27) 상에 위치된 제 1 갭-형성 마스크(45) 및 제 2 갭-형성 마스크(46)는 예컨대 습식 에칭에 의해 제거될 수 있다. 따라서, 도 4에 도시된 바와 같이 전극들(25 및 26) 사이에 나노-갭(NG)을 가진 나노-갭 전극(21)을 형성하는 것이 가능하다.

[0148] 상기 설명된 구성에서, 측벽(37)은 전극-형성 부분(31) 상에 배치된 제 1 갭-형성 마스크(45)의 측면 벽(45a) 상에 형성될 수 있고, 그 다음 제 2 갭-형성 마스크(46)는 측벽(37)에 인접하도록 형성될 수 있다. 따라서, 측벽(37)은 제 1 갭-형성 마스크(45)와 제 2 갭-형성 마스크(46) 사이에 배치될 수 있다. 그 다음, 갭-형성 마스크(45), 측벽(37), 및 제 2 갭-형성 마스크(46)의 표면들은 노출될 수 있고, 측벽(37)은 제거되어 제 1 갭-형성 마스크(45) 및 제 2 갭-형성 마스크(46) 사이에서 갭(49)이 형성될 수 있다. 따라서, 나노-갭(NG)은 갭(49) 내의 전극-형성 부분(31)의 일부를 제거함으로써 형성될 수 있다.

[0149] 본원에 설명된 바와 같은 그런 제조 방법에서, 측벽(37)이 막 두께를 조절함으로써 원하는 폭(W1)을 갖는 나노-갭(NG)을 형성하는 것이 가능하다. 게다가, 측벽(37)은 극히 작은 막 두께로 형성될 수 있다. 그러므로 측벽(37)의 두께에 대응하는 극히 작은 폭(W1)을 가진 나노-갭(NG)을 형성하는 것이 가능하다. 게다가, 종래의 제조 방법에서와 달리, 이 제조 방법은 나노-갭(NG)을 형성할 대 금속 마스크를 패터닝하는 것을 요구하지 않는다. 그러므로 과도한 노력 없이 나노-갭(NG)을 형성하는 것이 가능하다.

[0150] 상기 설명된 구성에 따라, 측벽(37)의 막 두께에 의해 조절되는 폭(W1)을 가진 나노-갭(NG)은 마스크로서 전극-형성 부분(31) 상에 배치된 측벽(37)을 사용하여 전극-형성 부분(31)에 형성될 수 있다. 결과적으로, 종래의 나노-갭과 동일한 폭(W1)인 나노-갭(NG)뿐 아니라, 종래의 나노-갭보다 폭(W1)이 훨씬 더 작은 나노-갭(NG)을 형성하는 것이 가능하다.

[0151] 일부 경우들에서, 제 2 갭-형성 마스크(46)는 도 10b에 도시된 바와 같이 제 1 갭-형성 마스크(45) 상에 직접 형성될 수 있다. 다른 실시예들에서, 하드 마스크가 형성되는 표면상의 제 1 갭-형성 마스크(45)는 제 1 갭-형성 마스크(45) 상에 제 2 갭-형성 마스크(46)를 직접 형성하지 않고 사용될 수 있다. 심지어 이 경우에, 제 1 갭-형성 마스크(45)와 제 2 갭-형성 마스크(46) 사이에 측벽(37)을 배치하는 것이 가능하다. 결과적으로, 측벽(37)을 제거함으로써 제 1 갭-형성 마스크(45)와 제 2 갭-형성 마스크(46) 사이에 갭(49)을 형성하는 것이 가능하다.

[0152] 본 발명이 본 실시예들로 제한되는 것이 아니라, 본 발명의 청구 대상의 범위 내에서 다양한 다른 방식들로 수정되고 수행될 수 있다는 것이 주의 되어야 한다. 예컨대, 다양한 재료들은 전극들(5 및 6)(25 및 26), 기판(2), 실리콘 산화물 층(4)(27) 측벽(11)(37) 등의 재료들로서 사용될 수 있다. 게다가, 제 1 전극-형성 부분(9), 제 2 전극-형성 부분(12), 및 전극들(5 및 6)은 다양한 형상들을 가질 수 있다. 마찬가지로, 전극-형성 부분(31) 및 전극들(25 및 26)은 다양한 형상들을 가질 수 있다.

[0153] 예컨대, 전극-형성 부분(31)이 탄소 나노튜브로 만들어지는 것으로 설명되었지만, 본 발명은 이들 실시예들로 제한되지 않는다. 예컨대, 전극-형성 부분은 단순한 직사각형 고체 및 원주 형상들을 포함하여 다양한 다른 형상들 중 하나를 가진 금속 재료로 형성될 수 있다.

[0154] 여기서, 도 6 및 도 7의 설명들과 연관하여 설명된 바와 같이 제조 방법의 설명이 이루어질 것이다. 예컨대, 직사각형 고체-형상 금속 재료로 만들어진 전극-형성 부분이 전극-형성 부분으로서 적용될 수 있다면, 개구(32a)를 가진 레지스트 마스크(32)는 직사각형 고체-형상 전극형성 부분(들) 상에 배치될 수 있고, 측벽들(37)은 레지스트 마스크(32)의 양쪽 측면 벽들(33a 및 33b)을 따라 형성될 수 있고, 그리고 측벽들(37) 사이에서 노출된 전극-형성 부분의 일부는 제거될 수 있다. 따라서, 나노-갭(NG)을 가로질러 서로 대향하게 배치된 직사각형 고체-형상 전극들과 측벽들(37) 사이에 나노-갭(NG)을 형성하는 것은 가능하다.

[0155] 도 6-도 11을 참조하여, 전극-지지 부분들(28 및 29)은 기판상의 실리콘 산화물 층(27)에 인접하여 형성될 수 있고 전극-형성 부분(31)은 전극-지지 부분들(28 및 29)의 표면들 상에 배치될 수 있다. 대안적으로, 다양한 형상들을 가진 전극-형성 부분은, 전극-지지 부분들(28 및 29)이 기판상의 실리콘 산화물 층(27)에 인접하여 배치되는 것이 아니라, 단순히 실리콘 산화물 층이 제공될 수 있거나 단지 실리콘 기판만을 포함할 수 있는 기판상에 배치될 수 있다. 대안적으로, 전극-형성 부분은 기판상에 배치될 수 있고, 전극-지지 부분들은 그 양쪽 측 상에서 전극-형성 부분의 상부 부분들 상에 돌출하여 형성될 수 있다. 따라서, 실시예들은, 전극-형성 부분이 기판상에서 서로를 향하도록 배치된 2개의 전극-지지 부분들 사이에 위치되는 구성을 가질 수 있다.

[0156] 게다가, 상기 설명된 실시예들에서, 싱글-스트랜디드 DNA가 적어도 부분적으로 전극들(5 및 6)(25 및 26) 사이의 나노-갭(NG)을 거쳐 통과될 수 있고, 싱글-스트랜디드 DNA의 염기들이 전극들(5 및 6)(25 및 26) 사이의 나노-갭(NG)을 거쳐 통과할 때 전극들(5 및 6)(25 및 26)을 가로질러 흐르는 전류(들)의 값들이 전류계로 측정될 수 있는 나노-갭 전극(1)(21)의 설명이 이루어졌다. 그러나, 본 발명은 이들 실시예들로 제한되지 않는다. 나노-갭 전극은 다양한 다른 애플리케이션들에 사용될 수 있다. 일부 실시예들에서, 나노-갭은 더블 스트랜디드 DNA에 활용될 수 있고, 그러므로 더블 스트랜디드 DNA의 측정에 더 적당할 수 있는 상이한 치수를 가지도록 제조될 수 있다. 다른 실시예들에서, 나노-갭은 아미노산들, 지방질들, 또는 탄수화물들 같은 다른 생체분자들에 활용될 수 있고, 따라서 각각의 타입의 생체분자에 적당한 폭으로 제조될 수 있다.

[0157] 도 6-도 11을 수반한 설명에서, 측면 벽의 정점으로부터 실리콘 산화물 층(27) 쪽으로 점진적으로 두꺼워지도록 형성될 수 있는 측벽(11 또는 37)이 측벽으로서 적용될 수 있는 방법들이 설명되었다. 다른 실시예들에서, 막 형성 위치에 따라 막 두께가 상이한 측벽-형성 층은 등각 방식으로 측벽 상에 막을 형성하지 않고 다양한 막-형성 조건들(온도, 압력, 사용된 가스, 유량비 등) 하에서 형성될 수 있다. 따라서, 정점으로부터 실리콘 산화물 층을 향해 점진적으로 얇도록 형성되는 측벽에 적용된 막이 있을 수 있거나, 측벽의 폭은 정점과 실리콘 산화물 층 사이의 중간 위치 또는 다양한 다른 위치들에서 최대 폭을 가질 수 있다.

[0158] 본 개시는 전극들(5 및 6) 사이에 나노-갭(NG)을 가진 나노-갭 전극(1)을 제조하기 위한 방법을 제공한다. 실리콘 산화물 층(4)이 실리콘 기판(3) 상에 형성될 수 있는 기판(2)이 먼저 준비될 수 있다. 추후 전극 형성 층(79)이 부가될 수 있고 예컨대 실리콘 질화물(SiN)로 만들어지고 측면 벽(72a)을 가진 제 1 마스크(72)는 포토리소그래픽 기술을 사용하여 전극 형성 층(79)의 미리 결정된 구역상에 형성될 수 있다.

[0159] 추후, 도 12a에 도시된 바와 같이, 전극 형성 층(79)의 표면의 재료(티타늄 질화물을 포함할 수 있음)와 상이한 티타늄(Ti) 같은 재료로 만들어진 측벽-형성 층(80)은 예컨대 화학 기상 증착(CVD) 기술에 의해 전극-형성 부분(79) 및 기판(2)의 노출된 부분들 상에 막으로서 형성될 수 있다. 이때, 측벽-형성 층(80)은 제 1 마스크(72)의 측면 벽(72a)을 다라 형성될 수 있다. 측면 벽(72a) 상에 형성될 측벽-형성 층(80)의 막 두께는 나노-갭(NG)의 원하는 폭(W1)에 따라 선택될 수 있다. 즉, 작은 폭(W1)을 가진 나노-갭(NG)이 형성될 때, 측벽-형성 층(80)은 작은 막 두께로 형성될 수 있다. 다른 한편, 큰 폭(W1)을 가진 나노-갭(NG)이 형성될 때, 측벽-형성 층(80)은 큰 막 두께로 형성될 수 있다.

[0160] 추후, 도 12b에 도시된 바와 같이 제 1 마스크(72) 및 전극 형성 층(79)의 노출된 부분들 상에 막 형성된 측벽-형성 층(80)은 제 1 마스크(72)의 측면 벽(72a)을 따라 측벽-형성 층(80)의 일부를 남기도록 예컨대 건식 에칭에 의해 애칭될 수 있다. 에칭 프로세스는 기판(2)에 관하여 수직이도록 구성될 수 있거나, 측벽-형성 층(80)의 일부가 제 1 마스크(72)의 측면 벽(72a)이 적어도 부분적으로 에칭으로 보호될 수 있도록 각이 이루어질 수 있다.

[0161] 추후, 도 12c에 도시된 바와 같이, 제 2 마스크(73)는 예컨대 스퍼터링 방법에 의해 증착될 수 있다.

[0162] 추후, 도 12d에 도시된 바와 같이 제 1 마스크(72) 및 측벽 형성 층(80)뿐 아니라 제 2 마스크(73)의 구역들은 CMP(화학 및 기계적 폴리싱) 같은 평탄화 프로세싱에 의해 폴리싱될 수 있거나 오버 폴리싱될 수 있다.

[0163] 추후, 도 13a(중앙 단면도) 및 도 13b(평면도)에 도시된 바와 같이 레지스트의 층은 적용되고 패터닝될 수 있다. 그 다음 패터닝된 레지스트(74)에 노출되어 남겨진 제 1 마스크(72) 및 제 2 마스크(73)의 부분들은 에칭 제거될 수 있다. 그 다음 패터닝된 레지스트(74)는 제거될 수 있어서 도 13c(중앙 단면도) 및 도 13d(평면도)에 도시된 바와 같이 남아있는 마스크 층들이 노출된다. 그 다음 남아있는 제 1 마스크(72) 및 남아있는 제 2 마스크(73)는 전극 형성 층(79)을 에칭하기 위하여 사용될 수 있고 추후 도 13e(중앙 단면도) 및 도 13f(평면도)에 도시된 바와 같이 제거될 수 있고 도 1에 도시된 바와 같은 구조가 생성된다.

[0164] 도 14에서, 참조 번호(1)는 본 발명의 일 실시예에 따른 나노-갭 전극을 나타낸다. 이 나노-갭 전극(1)에서, 대향하는 전극들(15 및 16)은 기판(2) 상에 배치될 수 있다. 나노스케일(예컨대, 1000 nm보다 크지 않음)일 수 있는 최소 폭(W1)을 가진 중공 갭(G1)은 이들 전극들(15 및 16) 사이에 형성될 수 있다. 기판(2)은 예컨대, 실리콘 기판(3) 및 그 위에 형성된 실리콘 산화물 층(4)을 포함할 수 있다. 따라서 기판(2)은, 쌍을 형성하는 2개의 전극들(15 및 16)이 실리콘 산화물 층(4) 상에 형성될 수 있는 구성을 가질 수 있다.

[0165] 일부 실시예들에서, 전극들(15 및 16) 사이에 형성된 갭(G1)은 마스크 폭 갭(G2) 및 마스크 폭 갭(G2)에 대응하는 폭(W2)보다 좁은 나노-갭(NG)을 포함할 수 있다. 본 발명의 나노-갭 전극(1)은, 제조 과정(이후 설명됨)에서 사용된 마스크로 형성된 마스크 폭 갭(G2)의 폭(W2)보다 좁은 나노-갭(NG)을 형성하는 것이 가능하다는 점에서 특성화된다. 일부 실시예들에서, 나노-갭(NG)은 0.1 nm 내지 30 nm의 최소 폭(W1), 또는 10 nm보다 크지 않거나, 5 nm보다 크지 않거나, 2 nm보다 크지 않거나, 1 nm보다 크지 않거나, 또는 0.5 nm보다 크지 않은 폭(W1), 또는 1.5 nm 내지 0.3 nm, 1.2 nm 내지 0.5 nm, 또는 0.9 nm 내지 0.65 nm, 또는 1.2 nm 내지 0.9nm, 또는 1.0 nm 내지 0.8 nm, 또는 0.8 nm 내지 0.7 nm의 폭(W1)으로 형성될 수 있다. 본원에 설명된 폭들은 본원에 설명된 임의의 나노-갭들에 대한 갭 간격에 활용될 수 있다.

[0166] 실제로, 이들 전극들(15 및 16)의 각각은 티타늄 실리사이드, 몰리브덴 실리사이드, 백금 실리사이드, 니켈 실리사이드, 코발트 실리사이드, 팔라듐 실리사이드, 및 니오븀 실리사이드 또는 이들의 결합들을 포함하는 다양한 타입들의 금속 실리사이드들, 또는 다른 재료들과 실리사이드들의 합금들 중 하나로 형성될 수 있거나, 반도체들의 도핑에 흔히 사용될 수 있는 바와 같은 다양한 재료들로 도핑될 수 있는 실리사이드들을 포함할 수 있다. 전극들(15 및 16)은 동일한 구성을 가질 수 있고 기판(2) 상에서 나노-갭(NG)을 가로질러 양방향으로 대칭으로 형성될 수 있다. 전극 부분들(15 및 16)의 개별 단부들에서 측벽들(15a 및 16a)은 나노-갭(NG)을 가로질러 서로 대향하여 배치될 수 있다. 실제로, 일부 실시예들에서, 전극들(15 및 16)은 직사각형 고체들로 구성될 수 있고, 이의 길이방향 단면은 사각형이고 이의 길이방향은 y-방향으로 연장될 수 있다. 전극들(15 및 16)은, 자신의 장측 중앙 축들이 동일한 y-축 직선상에 포지셔닝되고, 측벽들(15a 및 16a)의 전면 표면들이 서로를 향하도록 배치될 수 있다.

[0167] 어깨부들(15b 및 16b)은 전극들(15 및 16)의 측벽들(15a 및 16a)의 상부 모서리들에 형성될 수 있는 L 형상 리세스들을 포함할 수 있다. 게다가, 트레일링 곡선 표면들(15c 및 16c)은 측벽들(15a 및 16a)에 형성된 어깨부들(15b 및 16b)의 바닥 표면으로부터 증가된 하강 거리에 대응하게 점점 완만하게 리세스(recess)한다. 따라서, 전극들(15 및 16) 위에서 브리징하는 사각형 마스크 폭 갭(G2) 및 그 사이의 갭은 어깨부들(15b 및 16b) 사이에 형성될 수 있다. 결과적으로, 나노-갭(NG)은 기판(2)에 더 가까이 점점 넓어지는 전극들의 단부들 사이의 거리에 대응하는 곡선진 표면들(15c 및 16c) 사이에 형성된다.

[0168] 다른 실시예들에서, 마스크 폭 갭(G2)을 형성하는 어깨부들(15b 및 16b) 위 표면은 전극들(15 및 16) 사이에 나노-갭(NG)만을 남기도록 예컨대 CMP에 의한 폴리싱에 의해 제거될 수 있다.

[0169] 상기 설명된 바와 같이 구성된 나노-갭 전극(1)에서 전류가 예컨대 전력 원(도시되지 않음)으로부터 전극들(15 및 16)에 공급될 수 있고, 전극들(15 및 16)을 가로질러 흐르는 전류의 값들이 전류계(도시되지 않음)로 측정될 수 있는 것을 주의하라. 따라서, 나노-갭 전극(1)은 단일-스트랜디드 DNA가 전극들(15 및 16)의 길이 방향 축일 수 있는 y-축에 직교하는 x-방향으로부터, 및/또는 전극들(15 및 16)의 높이 축일 수 있는 z- 방향으로부터 전극들(15 및 16) 사이의 나노-갭(NG)을 거쳐 통과하게 하고, y-축과 직각으로 교차하게 하고; 전류계는 싱글-스트랜디드 DNA의 염기들이 전극들(15 및 16) 사이의 나노-갭(NG)을 거쳐 통과할 때 전극들(15 및 16)을 가로질러 흐르는 전류의 값들을 측정하기 위해 활용될수 있고; 그리고 싱글-스트랜디드 DNA를 포함하는 염기들은 전류 값들에 기초하여 결정될 수 있다.

[0170] 일부 실시예들에서, 상기 설명된 바와 같은 나노-갭 전극(1)을 제조하기 위한 방법은, 실리콘 산화물 층(4)일 수 있는 층이 실리콘 기판(3)일 수 있는 기판상에 형성될 수 있는 기판(2)이 도 15에 도시된 바와 같이 준비될 수 있는 방법을 포함할 수 있다. 그 다음, 직사각형으로 형상화될 수 있고, 그리고 실리콘으로 만들어질 수 있고 그리고 y-축으로 연장되는 길이방향 축을 가질 수 있는 전극-형성 부분(18)은 리소그래픽 기술을 사용하여 실리콘 산화물 층(4) 상에 형성될 수 있다. 추후, 실리콘 질화물(SiN)로 만들어질 수 있는 마스크 층(19)(도시되지 않음)은 기판(2) 및 전극-형성 부분(18) 상에 막으로서 형성될 수 있고; 이 마스크 층(19)은 표준 리소그래픽 프로세스들에 의해 패터닝될 수 있는 레지스트 마스크를 사용하여 형성될 수 있다.

[0171] 결과적으로, 직사각형 단면을 가질 수 있고, 실리콘 질화물(SiN)로 만들어질 수 있는 마스크 층(19)은 전극-형성 부분(18)의 길이방향 축일 수 있는 y-축에 직교하는 x-축을 따라 전극-형성 부분(18) 위에서 브리지하도록 형성될 수 있다. 전극들(15 및 16)이 형성될 수 있을 때 마스크 층(19)의 폭(W2)이 전극들(15 및 16) 사이에 마스크 폭(G2)을 형성하는 역할을 하는 것을 주의하라. 그러므로, 일부 실시예들에서 마스크 층(19)의 폭(W2)에 대응하는 레지스트 마스크의 폭을 최소화하는 방법을 요구할 수 있는 마스크 층(19)의 폭(W2)을 선택하기 위하여 레지스트 마스크의 패터닝 방법을 변경하는 것이 바람직할 수 있다.

[0172] 여기서, 나노-갭 전극(1)을 제조하는 프로세스를 설명하기 위하여 도 15의 단면들(A-A' 및 B-B')로 예시된 구조들에 대해 관심이 집중될 것이다. 도 16a는 도 15의 단면(A-A')의 구조를 도시하는 반면, 도 16b는 도 15의 단면(B-B')의 구조를 도시한다. 도 16a의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 16c, 및 도 16b의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 16d에 도시된 바와 같이, 티타늄, 몰리브덴, 백금, 니켈, 코발트, 팔라듐 또는 니오븀 같은 금속 엘리먼트들로 만들어질 수 있는 실리사이드-생성 층(52)은 예컨대 스퍼터링에 의해 마스크 층(19) 및 전극-형성 부분(18) 상에 막으로서 형성될 수 있다. 이때, 실리사이드-생성 층(52)이 또한 마스크 층(19) 및 전극-형성 부분(18)에 의해 커버되지 않은 구역들에서 노출될 수 있는 기판(2) 상에 막으로서 형성될 수 있다는 것을 주의하라.

[0173] 추후, 열 처리는 전극-형성 부분(18)을 실리사이드-생성 층(52)과 반응시키기 위하여 수행될 수 있다. 따라서, 도 16c의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 16e, 및 도 16d의 구성 엘리먼트들에 대응하는 구성 엘리먼트들이 동일한 참조 번호들에 의해 나타내지는 도 16f에 도시된 바와 같이, 실리사이드-생성 층(52)과 콘택하는 전극-형성 부분(18)의 부분들은 전극들(15)을 형성하기 위하여 실리사이드화될 수 있다.

[0174] 일부 경우들에서, 이때 실리사이드-생성 층(52)이 도 16e에 도시된 바와 같이 막으로서 형성되지 않는 마스크 층(19) 아래 전극-형성 부분(18)의 구역들에서 실리사이드를 형성하는 것은 어려울 수 있다. 실리사이드-생성 층(52) 금속 엘리먼트(들)는 마스크 층(19)의 양쪽 측면 측들로부터 마스크 층(19) 아래 구역들을 향해 확산되고; 실리사이딩은 또한 실리사이드-생성 층(52)과 직접 콘택하지 않는 마스크 층(19)의 양쪽 측면 부분들 근처 하부 구역들에서 진행한다. 따라서, 전극들(15 및 16)은 마스크 층(19)의 양쪽 측면 측들로부터 마스크 층(19) 아래에 형성될 수 있다. 이 경우, 전극들(15 및 16)은 마스크 층(19)의 양쪽 측면 부분들의 근처로부터 마스크 층(19) 아래로 확산되고, 이에 의해 실리사이드를 형성하는 실리사이드-생성 층(52) 금속 엘리먼트(들)의 결과로서 아래 마스크 층(19)에 형성될 수 있다. 결과적으로, 전극들(15 및 16)은 마스크 층이 커버하지 않는 전극-형성 부분(18)의 구역의 부피보다 큰 부피로 팽창(부피 팽창)한다. 따라서, 전극들(15 및 16)의 측벽들(15a 및 16a)(구체적으로, 곡선진 표면들(15c 및 16c)은 마스크 층(19)의 하부 부분의 폭(W2)보다 서로 더 가깝도록 형성될 수 있다.

[0175] 또한 이 경우, 전극-형성 부분(18)의 실리사이딩은, 실리콘 산화물 층(4)에 도달될 때까지 진행할 수 있다. 따라서, 실리콘 산화물 층(4)과 콘택하여 전극들(15 및 16)을 형성하는 것이 가능하다. 상기 설명된 바와 같이 전극들(15 및 16)에 대해, 마스크 층(19) 아래 전극들(15 및 16)의 측벽들(15a 및 16a)(곡선진 표면들(15c 및 16c))의 포지션들은 전극 형성 부분(18)의 막 두께, 실리사이드-생성 층(52)의 막 두께, 및 열 처리시 온도, 가열 시간 등을 적당하게 선택함으로써 제어될 수 있다. 그러므로 측벽들(15a 및 16a) 사이의 최소 폭(W1)은 예컨대 0.1 nm 내지 30 nm, 또는 본원에 설명된 바와 같은 임의의 폭으로 설정될 수 있고, 곡선진 표면들(15c 및 16c)의 곡률 정도는 제어될 수 있다.