KR101818504B1 - 반도체 메모리 장치 및 반도체 메모리 시스템 - Google Patents

반도체 메모리 장치 및 반도체 메모리 시스템 Download PDFInfo

- Publication number

- KR101818504B1 KR101818504B1 KR1020110016643A KR20110016643A KR101818504B1 KR 101818504 B1 KR101818504 B1 KR 101818504B1 KR 1020110016643 A KR1020110016643 A KR 1020110016643A KR 20110016643 A KR20110016643 A KR 20110016643A KR 101818504 B1 KR101818504 B1 KR 101818504B1

- Authority

- KR

- South Korea

- Prior art keywords

- domain

- data

- scatter

- measurement

- transform

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/42—Bus transfer protocol, e.g. handshake; Synchronisation

- G06F13/4204—Bus transfer protocol, e.g. handshake; Synchronisation on a parallel bus

- G06F13/4234—Bus transfer protocol, e.g. handshake; Synchronisation on a parallel bus being a memory bus

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0483—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells having several storage transistors connected in series

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

- G11C16/3454—Arrangements for verifying correct programming or for detecting overprogrammed cells

- G11C16/3459—Circuits or methods to verify correct programming of nonvolatile memory cells

Abstract

본 발명은 반도체 메모리 시스템에 관한 것으로, 복수의 메모리 셀들이 배치된 메모리 셀 어레이를 포함하는 메모리 장치와, 복수의 메모리 셀들에 기록하거나 복수의 메모리 셀들로부터 독출한 데이터에 대해 도메인 변환을 수행하고, 도메인 변환된 데이터에 대해 신호 처리를 수행하여 가공된 데이터 또는 제어 신호를 출력함으로써 메모리 장치를 제어하는 메모리 컨트롤러를 포함한다.

Description

본 발명의 기술적 사상은 반도체 장치에 관한 것으로, 더욱 상세하게는, 반도체 메모리 장치 및 반도체 메모리 시스템에 관한 것이다.

반도체 메모리 장치는 데이터를 저장하는데 사용되며, 휘발성 메모리 장치와 비휘발성 메모리 장치로 구분된다. 이러한 반도체 메모리 장치에 데이터를 저장하거나 저장된 데이터를 정확하게 독출하여 반도체 메모리 장치의 신뢰성을 향상시키기 위해서는 해당 데이터에 대하여 효율적인 신호 처리를 수행하는 것이 요구된다.

본 발명의 기술적 사상이 해결하고자 하는 과제는 메모리 셀 어레이에 포함된 복수의 메모리 셀들에 데이터를 기록하거나 복수의 메모리 셀들로부터 데이터를 독출할 때에 해당 데이터에 대하여 적절한 신호 처리를 수행함으로써, 신뢰성을 향상시킬 수 있는 비휘발성 반도체 메모리 장치 및 반도체 메모리 시스템을 제공하는 데에 있다.

상기 과제를 해결하기 위한 본 발명의 일 실시예에 따른 반도체 메모리 시스템은 복수의 메모리 셀들이 배치된 메모리 셀 어레이를 포함하는 메모리 장치; 및 상기 복수의 메모리 셀들에 기록하거나 상기 복수의 메모리 셀들로부터 독출한 데이터에 대해 도메인 변환을 수행하고, 도메인 변환된 상기 데이터에 대해 신호 처리를 수행하여 가공된 데이터 또는 제어 신호를 출력함으로써 상기 메모리 장치를 제어하는 메모리 컨트롤러를 포함한다.

일부 실시예들에 있어서, 상기 메모리 컨트롤러는, 상기 데이터를 시간 도메인에서 주파수 도메인으로 변환할 수 있다.

일부 실시예들에 있어서, 상기 메모리 컨트롤러는, 상기 데이터가 신호 처리에 적합한 형식으로 변경되도록 상기 데이터에 대해 전처리를 수행하는 전처리부; 전처리가 수행된 상기 데이터를 제1 도메인에서 제2 도메인으로 변환하는 도메인 변환부; 및 상기 제2 도메인으로 변환된 상기 데이터에 대해 후처리를 수행하여 상기 가공된 데이터 또는 제어 신호를 출력하는 후처리부를 포함할 수 있다.

일부 실시예들에 있어서, 상기 도메인 변환부는, 전치리가 수행된 상기 데이터에 대해 푸리에 변환(Fourier transform), 힐버트 변환(Hilbert transform), 라플라스 변환(Laplace transform) 및 상기 변환들에 대한 역변환들 중 적어도 하나를 수행할 수 있다.

일부 실시예들에 있어서, 상기 후처리부는, 상기 제2 도메인으로 변환된 상기 데이터에 대해 최대 우도 추정/검출(Maximum likelihood estimation/detection) 및 베이지안 추정/검출(Bayesian estimation/detection) 중 적어도 하나를 수행할 수 있다.

일부 실시예들에 있어서, 상기 메모리 컨트롤러는, 상기 복수의 메모리 셀들로부터 독출한 데이터에 대해 도메인 변환을 수행하고 도메인 변환된 상기 데이터를 기초로 하여 상기 복수의 메모리 셀들에 대한 산포 변화를 추정함으로써, 상기 데이터를 독출하기 위한 독출 전압의 전압 레벨을 제어하는 독출 전압 제어부를 포함할 수 있다.

일부 실시예들에 있어서, 상기 독출 전압 제어부는, 상기 데이터에 대한 산포를 측정하여, 측정 산포를 생성하는 산포 측정부; 상기 측정 산포에 대해 도메인 변환을 수행하여, 도메인 변환된 측정 산포를 생성하는 도메인 변환부; 및 상기 도메인 변환된 측정 산포를 기초로 하여, 기준 산포에 대한 상기 측정 산포의 변화를 나타내는 상기 산포 변화를 추정하는 산포 변화 추정부를 포함할 수 있다. 일부 실시예들에 있어서, 상기 독출 전압 제어부는, 추정된 상기 산포 변화 및 기준 독출 전압을 기초로 하여, 상기 독출 전압의 전압 레벨을 조절하는 전압 레벨 조절부를 더 포함할 수 있다.

일부 실시예들에 있어서, 상기 도메인 변환부는, 상기 측정 산포에 대해 푸리에 변환, 힐버트 변환, 라플라스 변환 및 상기 변환들에 대한 역변환들 중 적어도 하나를 수행하여 상기 도메인 변환된 측정 산포를 생성할 수 있다.

일부 실시예들에 있어서, 상기 산포 변화 추정부는, 상기 도메인 변환된 측정 산포와 도메인 변환된 기준 산포 사이의 위상 차이를 산출하는 위상 차이 산출부; 및 상기 위상 차이를 기초로 하여, 상기 기준 산포에 대한 상기 측정 산포의 산포 중심 이동치를 추정하는 산포 중심 이동치 추정부를 포함할 수 있다. 일부 실시예들에 있어서, 상기 위상 차이 산출부는, 상기 메모리 셀 어레이의 일부 영역 및 외부 저장 매체 중 적어도 하나로부터 상기 기준 산포 또는 상기 도메인 변환된 기준 산포를 수신할 수 있다.

일부 실시예들에 있어서, 상기 산포 변화 추정부는, 상기 도메인 변환된 측정 산포와 도메인 변환된 기준 산포 사이의 크기 차이를 산출하는 크기 차이 산출부; 및 상기 크기 차이를 기초로 하여, 상기 기준 산포에 대한 상기 측정 산포의 분산의 변화량을 추정하는 분산 변화량 추정부를 포함할 수 있다. 일부 실시예들에 있어서, 상기 크기 차이 산출부는, 상기 메모리 셀 어레이의 일부 영역 및 외부 저장 매체 중 적어도 하나로부터 상기 기준 산포 또는 상기 도메인 변환된 기준 산포를 수신할 수 있다.

일부 실시예들에 있어서, 상기 산포 측정부는, 상기 복수의 메모리 셀들에 대한 산포를 측정하기 위한 복수의 독출 레벨들을 설정하고, 상기 복수의 독출 레벨들 각각에서 상기 복수의 메모리 셀들에 대한 독출 동작을 수행하는 데이터 독출부; 및 상기 복수의 독출 레벨들 각각에서 독출된 데이터에서 '1' 또는 '0'의 개수를 산출하고, 산출 결과를 기초로 하여 히스토그램을 생성하는 히스토그램 생성부를 포함할 수 있다.

일부 실시예들에 있어서, 상기 데이터 독출부는, 소정의 문턱 전압 윈도우(window) 내에서 서로 동일한 간격을 갖도록 상기 복수의 독출 레벨들을 설정할 수 있다. 일부 실시예들에 있어서, 상기 데이터 독출부는, 인접한 두 개의 상태들에 대한 산포들 사이의 영역에서 상기 복수의 독출 레벨들 사이의 간격을 상대적으로 작게 설정할 수 있다.

일부 실시예들에 있어서, 상기 복수의 메모리 셀들은 NAND 플래시 메모리 셀들을 포함할 수 있다.

또한, 상기 과제를 해결하기 위한 본 발명의 다른 실시예에 따른 반도체 메모리 시스템은 복수의 메모리 셀들이 배치된 메모리 셀 어레이를 포함하는 메모리 장치; 및 상기 데이터를 독출하기 위한 독출 전압의 전압 레벨을 제어하는 독출 전압 제어부를 포함하고, 상기 독출 전압 제어부는, 상기 데이터에 대한 산포를 측정하여, 측정 산포를 생성하는 산포 측정부; 상기 측정 산포에 대해 도메인 변환을 수행하여, 도메인 변환된 측정 산포를 생성하는 도메인 변환부; 및 상기 도메인 변환된 측정 산포를 기초로 하여, 기준 산포에 대한 상기 측정 산포의 변화를 나타내는 산포 변화를 추정하는 산포 변화 추정부를 포함한다.

일부 실시예들에 있어서, 상기 복수의 메모리 셀들은 NAND 플래시 메모리 셀들을 포함할 수 있다.

또한, 상기 과제를 해결하기 위한 본 발명의 다른 실시예에 따른 비휘발성 반도체 메모리 장치는 복수의 메모리 셀들을 포함하는 메모리 셀 어레이; 및 상기 복수의 메모리 셀들에 기록하거나 상기 복수의 메모리 셀로부터 독출한 데이터에 대해 도메인 변환을 수행하고, 도메인 변환된 상기 데이터를 대해 신호 처리를 수행하여 가공된 데이터 또는 제어 신호를 출력하는 제어부를 포함한다.

일부 실시예들에 있어서, 상기 제어부는, 상기 데이터가 신호 처리에 적합한 형식으로 변경되도록 상기 데이터에 대해 전처리를 수행하는 전처리부; 전처리가 수행된 상기 데이터를 제1 도메인에서 제2 도메인으로 변환하는 도메인 변환부; 및 상기 제2 도메인으로 변환된 상기 데이터에 대해 후처리를 수행하여 상기 가공된 데이터 또는 제어 신호를 출력하는 후처리부를 포함할 수 있다.

일부 실시예들에 있어서, 상기 제어부는, 상기 복수의 메모리 셀들로부터 독출한 데이터에 대해 도메인 변환을 수행하고 도메인 변환된 상기 데이터를 기초로 하여 상기 복수의 메모리 셀들에 대한 산포 변화를 추정함으로써, 상기 데이터를 독출하기 위한 독출 전압의 레벨을 제어하는 독출 전압 제어부를 포함할 수 있다.

일부 실시예들에 있어서, 상기 복수의 메모리 셀들은 NAND 플래시 메모리 셀들을 포함할 수 있다.

본 발명의 기술적 사상에 따르면, 메모리 장치에 포함된 복수의 메모리 셀들에 기록하거나 복수의 메모리 셀들로부터 독출한 데이터에 대해 도메인 변환을 수행하고, 도메인 변환된 데이터에 대해 신호 처리를 수행함으로써, 신호 처리에 있어서 계산의 복잡도를 감소시킬 수 있고, 이에 따라, 신호 처리의 효율성 및 반도체 메모리 시스템의 신뢰성을 향상시킬 수 있다.

또한, 본 발명의 기술적 사상에 따르면, 복수의 메모리 셀들에 저장된 복수의 데이터에 대해 도메인 변환을 수행하고, 도메인 변환된 복수의 데이터를 기초로 하여 복수의 메모리 셀들에 대한 산포 변화를 추정함으로써, 추정 연산의 복잡도를 감소시키면서 RBER(raw bit error rate)를 개선하여 추정 정확도를 향상시킬 수 있다.

또한, 본 발명의 기술적 사상에 따르면, 추정된 산포 변화를 기초로 하여 독출 전압의 전압 레벨을 조절함으로써, 메모리 셀들의 산포가 변하더라도 정확하게 메모리 셀들에 저장된 데이터를 독출할 수 있으므로, 반도체 메모리 장치의 신뢰성을 향상시킬 수 있다. 나아가, 반도체 메모리 장치에서 독출 동작의 오류를 정정하기 위해 여러 독출 레벨들에서 ECC(error correction code) 디코딩을 수행하지 않고서도 독출 전압의 최적 전압 레벨을 결정할 수 있다.

또한, 본 발명의 기술적 사상에 따르면, 전체 문턱 전압 영역이 아닌 소정의 문턱 전압 윈도우 내에서 복수의 독출 레벨들을 설정하고, 설정된 복수의 독출 레벨들에서 독출된 데이터를 기초로 하여 복수의 메모리 셀들에 대한 산포 변화를 추정함으로써, 독출 횟수를 감소시킬 수 있고, 이에 따라, 산포 추정을 위한 독출 단계에서 효율성을 더욱 향상시킬 수 있다.

또한, 본 발명의 기술적 사상에 따르면, 산포를 측정하기 위한 복수의 독출 레벨들 사이의 간격을 상대적으로 크게 설정함으로써, 복수의 독출 레벨들 사이의 해상도는 상대적으로 낮을 수 있고, 이에 따라, 산포 측정을 위한 연산량을 줄일 수 있다. 나아가, 복수의 독출 레벨들 사이의 해상도가 상대적으로 낮음에도 불구하고, 도메인 변환된 데이터를 기초로 하여 복수의 메모리 셀들에 대한 산포 변화를 추정함으로써 산포 변화 추정의 신뢰성을 향상시킬 수 있다.

또한, 본 발명의 기술적 사상에 따르면, 복수의 데이터에 대한 도메인 변환을 수행하는 도메인 변환부의 사이즈를 조절함으로써, 원하는 반도체 메모리 장치의 신뢰성에 따라 추정 정확도를 적응적으로 변경할 수 있다.

또한, 본 발명의 기술적 사상에 따르면, 산포 이동을 추정하기 위한 별도의 모니터링 셀(monitoring cell)과 같은 추가 메모리 셀이 요구되지 않으므로, 실질적으로 데이터를 저장하는데에 사용 가능한 메모리 용량이 더욱 증가될 수 있다.

도 1은 본 발명의 일 실시예에 따른 반도체 메모리 시스템을 나타내는 블록도이다.

도 2는 도 1의 반도체 메모리 시스템의 일 예를 나타내는 블록도이다.

도 3은 도 2의 메모리 셀 어레이에 포함된 메모리 셀의 일 예를 나타내는 단면도이다.

도 4는 도 3의 메모리 셀이 싱글 레벨 셀인 경우, 메모리 셀의 문턱 전압 분포를 나타내는 그래프이다.

도 5는 도 4에 도시된 메모리 셀의 문턱 전압이 감소된 경우를 나타내는 그래프이다.

도 6은 도 3의 메모리 셀이 멀티 레벨 셀인 경우, 메모리 셀의 문턱 전압 분포를 나타내는 그래프이다.

도 7은 도 6에 도시된 메모리 셀의 문턱 전압이 감소된 경우를 나타내는 그래프이다.

도 8은 도 2의 반도체 메모리 시스템을 보다 상세하게 나타내는 블록도이다.

도 9는 도 8에 포함된 독출 전압 제어부의 일 예를 나타내는 블록도이다.

도 10은 도 9에 포함된 산포 측정부의 일 예를 나타내는 블록도이다.

도 11은 도 10의 데이터 독출부의 동작을 설명하기 위하여, 메모리 셀에 대한 변경 전후의 문턱 전압 분포를 나타내는 그래프이다.

도 12는 복수의 메모리 셀들에 대한 기준 산포와 변경 산포의 일 예를 나타내는 그래프이다.

도 13은 도 10의 산포 측정부에서 생성된 히스토그램의 일 예를 나타내는 그래프이다.

도 14는 도 9에 포함된 산포 변화 추정부 및 전압 레벨 조절부의 일 예를 나타내는 블록도이다.

도 15는 도메인 변환된 기준 산포의 위상 및 도메인 변환된 측정 산포의 위상의 일 예를 나타내는 그래프이다.

도 16은 도메인 변환된 기준 산포와 도메인 변환된 측정 산포 사이의 위상 차이의 일 예를 나타내는 그래프이다.

도 17은 도 14의 전압 레벨 조절부의 동작을 설명하기 위하여, 인접한 두 개의 산포들의 일 예를 나타내는 그래프이다.

도 18은 도 9에 포함된 산포 변화 추정부 및 전압 레벨 조절부의 다른 예를 나타내는 블록도이다.

도 19는 도메인 변환된 기준 산포의 크기 및 도메인 변환된 측정 산포의 크기의 일 예를 나타내는 그래프이다.

도 20은 도메인 변환된 기준 산포와 도메인 변환된 측정 산포 사이의 크기 차이의 일 예를 나타내는 그래프이다.

도 21은 도 9에 포함된 산포 변화 추정부 및 전압 레벨 조절부의 또 다른 예를 나타내는 블록도이다.

도 22는 본 발명의 다른 실시예에 따른 반도체 메모리 시스템을 나타내는 블록도이다.

도 23은 도 22의 반도체 메모리 시스템의 일 예를 나타내는 블록도이다.

도 24는 도 23의 반도체 메모리 시스템을 보다 상세하게 나타내는 블록도이다.

도 25는 본 발명의 일 실시예에 따른 반도체 메모리 시스템의 신호 처리 방법을 나타내는 흐름도이다.

도 26은 본 발명의 일 실시예에 따른 반도체 메모리 시스템의 독출 레벨 제어 방법을 나타내는 흐름도이다.

도 27은 도 26에 도시된 독출 전압 제어 방법에 포함된 측정 산포를 생성하는 단계를 더욱 상세하게 나타내는 흐름도이다.

도 28은 본 발명의 일 실시예에 따른 컴퓨팅 시스템을 나타내는 블록도이다.

도 29는 본 발명의 일 실시예에 따른 메모리 카드를 나타내는 블록도이다.

도 30은 본 발명의 일 실시예에 따른 솔리드 스테이트 드라이브(SSD: Solid State Drive)를 나타내는 블록도이다.

도 2는 도 1의 반도체 메모리 시스템의 일 예를 나타내는 블록도이다.

도 3은 도 2의 메모리 셀 어레이에 포함된 메모리 셀의 일 예를 나타내는 단면도이다.

도 4는 도 3의 메모리 셀이 싱글 레벨 셀인 경우, 메모리 셀의 문턱 전압 분포를 나타내는 그래프이다.

도 5는 도 4에 도시된 메모리 셀의 문턱 전압이 감소된 경우를 나타내는 그래프이다.

도 6은 도 3의 메모리 셀이 멀티 레벨 셀인 경우, 메모리 셀의 문턱 전압 분포를 나타내는 그래프이다.

도 7은 도 6에 도시된 메모리 셀의 문턱 전압이 감소된 경우를 나타내는 그래프이다.

도 8은 도 2의 반도체 메모리 시스템을 보다 상세하게 나타내는 블록도이다.

도 9는 도 8에 포함된 독출 전압 제어부의 일 예를 나타내는 블록도이다.

도 10은 도 9에 포함된 산포 측정부의 일 예를 나타내는 블록도이다.

도 11은 도 10의 데이터 독출부의 동작을 설명하기 위하여, 메모리 셀에 대한 변경 전후의 문턱 전압 분포를 나타내는 그래프이다.

도 12는 복수의 메모리 셀들에 대한 기준 산포와 변경 산포의 일 예를 나타내는 그래프이다.

도 13은 도 10의 산포 측정부에서 생성된 히스토그램의 일 예를 나타내는 그래프이다.

도 14는 도 9에 포함된 산포 변화 추정부 및 전압 레벨 조절부의 일 예를 나타내는 블록도이다.

도 15는 도메인 변환된 기준 산포의 위상 및 도메인 변환된 측정 산포의 위상의 일 예를 나타내는 그래프이다.

도 16은 도메인 변환된 기준 산포와 도메인 변환된 측정 산포 사이의 위상 차이의 일 예를 나타내는 그래프이다.

도 17은 도 14의 전압 레벨 조절부의 동작을 설명하기 위하여, 인접한 두 개의 산포들의 일 예를 나타내는 그래프이다.

도 18은 도 9에 포함된 산포 변화 추정부 및 전압 레벨 조절부의 다른 예를 나타내는 블록도이다.

도 19는 도메인 변환된 기준 산포의 크기 및 도메인 변환된 측정 산포의 크기의 일 예를 나타내는 그래프이다.

도 20은 도메인 변환된 기준 산포와 도메인 변환된 측정 산포 사이의 크기 차이의 일 예를 나타내는 그래프이다.

도 21은 도 9에 포함된 산포 변화 추정부 및 전압 레벨 조절부의 또 다른 예를 나타내는 블록도이다.

도 22는 본 발명의 다른 실시예에 따른 반도체 메모리 시스템을 나타내는 블록도이다.

도 23은 도 22의 반도체 메모리 시스템의 일 예를 나타내는 블록도이다.

도 24는 도 23의 반도체 메모리 시스템을 보다 상세하게 나타내는 블록도이다.

도 25는 본 발명의 일 실시예에 따른 반도체 메모리 시스템의 신호 처리 방법을 나타내는 흐름도이다.

도 26은 본 발명의 일 실시예에 따른 반도체 메모리 시스템의 독출 레벨 제어 방법을 나타내는 흐름도이다.

도 27은 도 26에 도시된 독출 전압 제어 방법에 포함된 측정 산포를 생성하는 단계를 더욱 상세하게 나타내는 흐름도이다.

도 28은 본 발명의 일 실시예에 따른 컴퓨팅 시스템을 나타내는 블록도이다.

도 29는 본 발명의 일 실시예에 따른 메모리 카드를 나타내는 블록도이다.

도 30은 본 발명의 일 실시예에 따른 솔리드 스테이트 드라이브(SSD: Solid State Drive)를 나타내는 블록도이다.

이하, 첨부된 도면을 참조하여 본 발명의 실시예를 상세히 설명하기로 한다.

본 발명의 실시예들은 당해 기술 분야에서 통상의 지식을 가진 자에게 본 발명을 더욱 완전하게 설명하기 위하여 제공되는 것이며, 하기 실시예는 여러 가지 다른 형태로 변형될 수 있으며, 본 발명의 범위가 하기 실시예에 한정되는 것은 아니다. 오히려, 이들 실시예는 본 개시를 더욱 충실하고 완전하게 하고, 당업자에게 본 발명의 사상을 완전하게 전달하기 위하여 제공되는 것이다.

도 1은 본 발명의 일 실시예에 따른 반도체 메모리 시스템을 나타내는 블록도이다.

도 1을 참조하면, 반도체 메모리 시스템(1)은 메모리 컨트롤러(10) 및 메모리 장치(20)를 포함할 수 있다. 메모리 컨트롤러(10)는 메모리 장치(20)에 대한 제어 동작을 수행할 수 있는데, 구체적으로, 메모리 컨트롤러(10)는 메모리 장치(20)에 어드레스(address) 및 커맨드(command)를 제공함으로써, 메모리 장치(20)에 대한 프로그램(또는 기록), 독출 및 소거 동작을 제어할 수 있다. 이하에서는, 메모리 컨트롤러(10) 및 메모리 장치(20)에 포함된 구성 요소들에 대하여 상술하기로 한다.

메모리 장치(20)는 메모리 셀 어레이(MCA)를 포함할 수 있는데, 메모리 셀 어레이(MCA)는 복수의 워드 라인들과 복수의 비트 라인들이 교차하는 영역들에 배치되는 복수의 메모리 셀들을 포함할 수 있다. 일 실시예에서, 복수의 메모리 셀들은 플래쉬 메모리 셀들일 수 있고, 메모리 셀 어레이(MCA)는 낸드(NAND) 플래쉬 메모리 셀 어레이 또는 노아(NOR) 플래쉬 메모리 셀 어레이일 수 있다. 이하에서는, 복수의 메모리 셀들이 플래쉬 메모리 셀들인 경우를 예로 하여 본 발명의 실시예들을 상술하기로 한다. 그러나, 본 발명은 이에 한정되지 아니하고, 다른 실시예에서, 복수의 메모리 셀들은 RRAM(resistive RAM), PRAM(phase chage RAM) 또는 MRAM(magnetic RAM)과 같은 저항형 메모리 셀들일 수 있다.

메모리 컨트롤러(10)는 전처리부(11), 변환부(12) 및 후처리부(13)를 포함할 수 있고, 복수의 메모리 셀들에 기록하거나 복수의 메모리 셀들로부터 독출한 데이터에 대해 도메인 변환을 수행하고, 도메인 변환된 데이터에 대해 신호 처리를 수행하여 가공된 데이터 또는 제어 신호를 출력함으로써 메모리 장치(20)를 제어할 수 있다. 이하에서는, 메모리 컨트롤러(10)에 포함된 구성 요소들에 대하여 상술하기로 한다.

전처리부(11)는 복수의 메모리 셀들에 기록하거나 복수의 메모리 셀들로부터 독출한 데이터가 신호 처리에 적합한 형식으로 변경되도록 데이터에 대해 전처리를 수행할 수 있다.

도메인 변환부(12)는 전처리가 수행된 데이터를 제1 도메인에서 제2 도메인으로 변환할 수 있다. 예를 들어, 제1 도메인은 시간 도메인이고, 제2 도메인은 주파수 도메인일 수 있다. 이와 같이, 데이터를 주파수 도메인으로 변환하여 주파수 도메인에서 신호 처리를 수행하는 경우에는, 시간 도메인에서 신호 처리를 수행하는 경우에 비하여 계산의 복잡도를 감소시켜서 효율적으로 신호 처리를 수행할 수 있다.

구체적으로, 도메인 변환부(12)는 전처리가 수행된 데이터에 대하여 아벨 변환(Abel transform), 베이트만 변환(Bateman transform), 푸리에 변환(Fourier transform), 단구간 푸리에 변환(Short-time fourier transform, STFT), 한켈 변환(Hankel transform), 하트리 변환(Hartley transform), 힐버트 변환(Hilbert transform), 힐버트-슈미트 적분 연산자(Hilbert-Schmidt integral operator), 라플라스 변환(Laplace transform), 양면 라플라스 변환(Two-sided Laplace transform), LST(Laplace-Stieltjes transform), LCT(Linear canonical transform), 멜린 변환(Mellin transform), 포아송-멜린-뉴튼 사이클(Poisson-Mellin-Newton cycle), 라돈 변환(Radon transform), 스틸레스 변환(Stieltjes transform), 수무두 변환(Sumudu transform), 라플라스-카슨 변환(Laplace-Carson transform), 웨이블릿 변환(Wavelet transform), 이항 변환(Binomial transform), 이산 푸리에 변환(Discrete Fourier transform), 고속 푸리에 변환(Fast Fourier transform), 이산 코사인 변환(Discrete cosine transform), 변형 이산 코사인 변환(Modified discrete cosine transform), 이산 하트리 변환(Discrete Hartley transform), 이산 사인 변환(Discrete sine transform), 이산 웨이블렛 변환(Discrete wavelet transform), 고속 웨이블릿 변환(Fast wavelet transform), IBDWT(Irrational base discrete weighted transform), 수론 변환(Number-theoretic transform), 스터링 변환(Stirling transform), Z 변환(Z-transform), 카루넨-뢰브 변환(Karhunen-Loeve transform), 백룬트 변환(Backlund transform), 양선형 변환(Bilinear transform), 박스-뮬러 변환(Box-Muller transform), 버로우즈-휠러 변환(Burrows-Wheeler transform), 처플렛 변환(Chirplet transform), 거리 변환(Distance transform), 프랙탈 변환(Fractal transform), 하다마드 변환(Hadamard transform), 허프 변환(Hough transform), 르장드르 변환(Legendre transform), 뫼비우스 변환(Mobius transform), 원근 변환(Perspective transform), Y-델타 변환(Y-delta transform), 하에시안 변환(Hayesian transform) 및 상기 변환들에 대한 역변환들 중 적어도 하나를 수행할 수 있다.

후처리부(13)는 제2 도메인으로 변환된 데이터에 대해 후처리를 수행하여 가공된 데이터 또는 제어 신호를 출력할 수 있다. 구체적으로, 후처리부(13)는 제2 도메인으로 변환된 데이터에 대해 최대 우도 추정/검출(Maximum likelihood estimation/detection), 베이지안 추정/검출(Bayesian estimation/detection), 모멘트 추정법(Method of moments estimation), 최소 평균 제곱 오차(Minimum mean squared error, MMSE), MAP 추정/검출(Maximum a posteriori estimation/detection), 최소 분산 불편 추정량(Minimum variance unbiased estimator, MVUE), 최적 선형 불편 추정량(Best linear unbiased estimator, BLUE), 최소 제곱법(Least square estimation), 불편 추정량(Unbiased estimators), 파티클 필터(Particle filter), MCMC(Markov chain Monte Carlo), 칼만 필터(Kalman filter), 앙상블 칼만 필터(Ensemble Kalman filter, EnKF) 및 위너 필터(Wiener filter) 중 적어도 하나를 수행할 수 있다.

도 2는 도 1의 반도체 메모리 시스템의 일 예를 나타내는 블록도이다.

도 2를 참조하면, 반도체 메모리 시스템(1A)은 메모리 컨트롤러(10A) 및 메모리 장치(20)를 포함할 수 있다. 본 실시예에서, 메모리 컨트롤러(10A)는 독출 전압 제어부(100)를 포함할 수 있고, 독출 전압 제어부(100)는 도 1에 도시된 전처리부(11), 도메인 변환부(12) 및 후처리부(13)를 포함하는 구성에 대응될 수 있다. 구체적인 대응 관계에 대해서는 도 9를 참조하여 상술하기로 한다.

독출 전압 제어부(100)는 메모리 셀 어레이(MCA)에 포함된 복수의 메모리 셀들에 저장된 데이터를 독출하기 위한 독출 전압의 전압 레벨을 제어할 수 있다. 이와 같이, 메모리 컨트롤러(10A)는 독출 전압 제어부(100)를 포함함으로써, 외부 자극 및/또는 마모(wearing) 등에 의해 메모리 셀들의 문턱 전압이 변경되더라도 변경된 문턱 전압을 기초로 하여 독출 전압의 전압 레벨을 제어할 수 있고, 이에 따라, RBER(raw bit error rate)를 개선시킬 수 있다.

도 3은 도 2의 메모리 셀 어레이에 포함된 메모리 셀의 일 예를 나타내는 단면도이다.

도 3을 참조하면, 기판(SUB) 상에 소스(S) 및 드레인(D)이 형성되고, 소스(S)와 드레인(D)의 사이에는 채널 영역이 형성될 수 있다. 채널 영역의 상부에는 플로팅 게이트(FG)가 형성되는데, 채널 영역과 플로팅 게이트(FG)의 사이에는 터널링 절연층과 같은 절연층이 배치될 수 있다. 플로팅 게이트(FG)의 상부에는 컨트롤 게이트(CG)가 형성되는데, 플로팅 게이트(FG)와 컨트롤 게이트(CG)의 사이에는 블로킹 절연층과 같은 절연층이 배치될 수 있다. 기판(SUB), 소스(S), 드레인(D) 및 컨트롤 게이트(CG)에는 메모리 셀에 대한 프로그램, 소거 및 독출 동작에 필요한 전압들이 인가될 수 있다.

플래시 메모리 장치에서는 메모리 셀의 문턱 전압(threshold voltage, Vth)의 구별에 의해 메모리 셀에 저장된 데이터가 독출될 수 있다. 이때, 메모리 셀의 문턱 전압은 플로팅 게이트(FG)에 저장된 전자(electron)의 양에 따라 결정될 수 있다. 구체적으로, 플로팅 게이트(FG)에 저장된 전자가 많을수록 메모리 셀의 문턱 전압은 높아질 수 있다.

메모리 셀의 플로팅 게이트(FG)에 저장된 전자는 다양한 원인들에 의해 화살표 방향으로 누설(leakage)될 수 있고, 이에 따라, 메모리 셀의 문턱 전압이 변경될 수 있다. 예를 들어, 플로팅 게이트(FG)에 저장된 전자는 메모리 셀의 마모(wearing)에 의해 누설될 수 있다. 구체적으로, 메모리 셀에 대한 프로그램, 소거 또는 독출와 같은 액세스 동작을 반복하면 채널 영역과 플로팅 게이트(FG) 사이의 절연막은 마모될 수 있고, 이에 따라, 플로팅 게이트(FG)에 저장된 전자가 누설될 수 있다. 또 다른 예로, 플로팅 게이트(FG)에 저장된 전자는 고온 스트레스 또는 프로그램/독출 시의 온도 차이 등에 의해 누설될 수도 있다.

도 4는 도 3의 메모리 셀이 싱글 레벨 셀인 경우, 메모리 셀의 문턱 전압 분포를 나타내는 그래프이다.

도 4를 참조하면, 가로축은 문턱 전압(Vth)을 나타내고, 세로축은 메모리 셀들의 개수를 나타낸다. 메모리 셀이 싱글 레벨 셀(single level cell, SLC)인 경우, 메모리 셀은 두 개의 상태들(states)(S0, S1) 중 하나를 가질 수 있다.

독출 전압(Vr)이 메모리 셀이 컨트롤 게이트(CG)에 인가되면, 'S0' 상태의 메모리 셀은 턴온되는 반면, 'S1' 상태의 메모리 셀은 턴오프된다. 메모리 셀이 턴온되면 메모리 셀을 통해 전류가 흐르고, 메모리 셀이 턴오프되면 메모리 셀을 통해 전류가 흐르지 않는다. 따라서, 메모리 셀의 턴온 여부에 따라 메모리 셀에 저장된 데이터가 구별될 수 있다. 이때, 'S0' 상태의 메모리 셀은 데이터 '1'이 저장되고, 'S1' 상태의 메모리 셀은 데이터 '0'이 저장된 것으로 구별될 수 있다.

도 5은 도 4에 도시된 메모리 셀의 문턱 전압이 감소된 경우를 나타내는 그래프이다.

도 3을 참조하면, 실선은 메모리 셀의 초기 문턱 전압을 나타내고, 점선은 외부 자극 및/또는 마모 등에 의해 감소된 문턱 전압을 나타낸다. 도 3에서 빗금친 부분에 속하는 메모리 셀들은 'S1' 상태로 프로그램되었음에도 불구하고, 문턱 전압의 감소에 의해 'S0' 상태인 것으로 판단될 수 있다. 이에 따라, 독출 동작에 오류가 발생되어 반도체 메모리 장치의 신뢰성이 저하될 수 있다.

도 6은 도 3의 메모리 셀이 멀티 레벨 셀인 경우, 메모리 셀의 문턱 전압 분포를 나타내는 그래프이다.

도 6을 참조하면, 가로축은 문턱 전압(Vth)을 나타내고, 세로축은 메모리 셀들의 개수를 나타낸다. 메모리 셀이 멀티 레벨 셀(multi level cell, MLC), 예를 들어, 3-비트 멀티 레벨 셀인 경우, 메모리 셀은 8개의 상태들('S0' 내지 'S7') 중 어느 하나를 가질 수 있다. 이때, 'S0'은 소거 상태이고, 'S1' 내지 'S7'은 프로그램 상태를 나타낸다. 싱글 레벨 셀에 비하여 멀티 레벨 셀의 경우, 문턱 전압 분포들 사이의 간격이 좁으므로, 멀티 레벨 셀에서는 문턱 전압의 작은 변화에 의해 중대한 문제가 야기될 수 있다.

도 7은 도 6에 도시된 메모리 셀의 문턱 전압이 감소된 경우를 나타내는 그래프이다.

도 7을 참조하면, 실선은 메모리 셀의 초기 문턱 전압을 나타내고, 점선은 외부 자극 및/또는 마모 등에 의해 감소된 문턱 전압을 나타낸다. 도 3의 그래프와 마찬가지로, 본 그래프에서도 문턱 전압의 감소에 의해 빗금친 부분에 대응되는 메모리 셀들에 대해 독출 오류가 발생할 수 있고, 이에 따라, 반도체 메모리 장치의 신뢰성이 저하될 수 있다.

플래시 메모리 장치로부터 데이터를 독출하는 경우 RBER은 독출 전압의 전압 레벨에 따라 달라지는데, 독출 전압의 최적 전압 레벨은 메모리 셀들의 산포 모양에 따라 결정될 수 있다. 따라서, 메모리 셀들의 산포가 변화함에 따라 플래시 메모리 장치로부터 데이터를 독출하는데 필요한 독출 전압의 최적 전압 레벨도 변경될 수 있다.

그러므로, 산포의 변화를 추정하고 추정된 산포의 변화를 반영하여, 독출 전압의 전압 레벨을 변경하여 독출 전압의 최적 전압 레벨을 결정하는 것이 요구된다. 이 경우, 효율적으로 독출 전압의 최적 전압 레벨을 결정하기 위해서는, 소량의 측정 데이터를 바탕으로 산포 변화에 대하여 정확하게 추정하는 것이 요구된다.

다시 도 2를 참조하면, 독출 전압 제어부(100)는 메모리 셀 어레이(MCA)로부터 획득한 데이터에 대해 도메인 변환을 수행하고, 도메인 변환된 데이터를 기초로 하여 산포 변화를 추정하고, 추정된 산포 변화를 기초로 하여 독출 전압의 전압 레벨을 제어할 수 있다. 이때, 독출 전압 제어부(100)는 제1 도메인의 데이터에 대해 도메인 변환을 수행하여 제2 도메인의 데이터를 생성하고, 생성된 제2 도메인의 데이터를 기초로 하여 산포 변화를 추정할 수 있다. 예를 들어, 제1 도메인은 시간 도메인이고, 제2 도메인은 주파수 도메인일 수 있다. 또한, 다른 예에서, 제1 도메인은 주파수 도메인이고, 제2 도메인은 시간 도메인일 수도 있다.

도 8은 도 2의 반도체 메모리 시스템을 보다 상세하게 나타내는 블록도이다.

도 8을 참조하면, 반도체 메모리 시스템(1A)은 메모리 컨트롤러(10A) 및 메모리 장치(20)를 포함할 수 있다. 메모리 컨트롤러(10A)는 독출 전압 제어부(100)를 포함할 수 있고, 메모리 장치(20)는 메모리 셀 어레이(MCA), 제어 로직(control logic, 21), 전압 발생기(voltage generator, 22), 로우 디코더(row decoder, 23) 및 입출력 회로(I/O circuit, 24)를 포함할 수 있다.

제어 로직(21)은 메모리 컨트롤러(10A)로부터 수신한 커맨드를 기초로 하여 메모리 셀 어레이(MCA)에 데이터를 기입하거나 메모리 셀 어레이(MCA)로부터 데이터를 독출하기 위한 제어 신호를 출력할 수 있다. 이때, 제어 로직(21)에서 출력된 제어 신호는 전압 발생기(22), 로우 디코더(23) 및 입출력 회로(24)에 전달될 수 있다.

전압 발생기(22)는 제어 로직(21)으로부터 수신한 제어 신호를 기초로 하여 복수의 워드 라인들(WL)을 구동하기 위한 구동 전압을 생성할 수 있다. 구체적으로, 구동 전압은 기입 전압(또는 프로그램 전압), 독출 전압, 소거 전압 또는 패스(pass) 전압일 수 있다.

로우 디코더(23)는 로우 어드레스를 기초로 하여 복수의 워드 라인들(WL) 중 일부 워드 라인을 활성화할 수 있다. 구체적으로, 독출 동작 시에 로우 디코더(23)는 선택된 워드 라인에 독출 전압을 인가하고, 비 선택된 워드 라인에 패스 전압을 인가할 수 있다. 한편, 기입 동작 시에 로우 디코더(23)는 선택된 워드 라인에 기입 전압을 인가하고, 비 선택된 워드 라인에 패스 전압을 인가할 수 있다.

입출력 회로(24)는 복수의 비트 라인들(BL)을 통해 메모리 셀 어레이(MCA)에 연결될 수 있다. 구체적으로, 독출 동작 시에 입출력 회로(24)는 감지 증폭기(sense amplifier)로 동작하여 메모리 셀 어레이(MCA)에 저장된 데이터를 출력할 수 있다. 한편, 기입 동작 시에 입출력 회로(24)는 기입 드라이버로 동작하여 메모리 셀 어레이(MCA)에 저장하고자 하는 데이터를 입력시킬 수 있다.

독출 전압 제어부(100)는 입출력 회로(24)로부터 수신된 데이터에 대해 도메인 변환을 수행하고, 도메인 변환된 데이터를 기초로 하여 산포 변화를 추정하고, 추정된 산포 변화를 기초로 하여 독출 전압의 전압 레벨을 변경하기 위한 커맨드를 생성할 수 있다. 일 실시예에서, 독출 전압 제어부(100)는 복수의 독출 전압들 중 일부 독출 전압에 대해서만 전압 레벨을 변경할 수도 있다. 이때, 생성된 커맨드는 제어 로직(21)에 제공될 수 있으며, 제어 로직(21)은 수신된 커맨드를 기초로 하여 제어 신호를 출력할 수 있으며, 전압 발생기(22)는 제어 신호를 기초로 하여 전압 레벨이 변경된 독출 전압을 발생할 수 있다.

본 실시예에서, 독출 전압 제어부(100)는 입출력 회로(24)에서 출력된 복수의 데이터에 대해 도메인 변환을 수행하는데, 예를 들어, 시간 도메인의 데이터를 주파수 도메인의 데이터로 변환할 수 있다. 이와 같이, 독출 전압 제어부(100)는 주파수 도메인으로 변환된 데이터를 기초로 하여 복수의 데이터에 대한 산포 변화를 추정함으로써 연산의 복잡도를 크게 감소시킬 수 있다.

도 9는 도 8에 포함된 독출 전압 제어부의 일 예를 나타내는 블록도이다.

도 8 및 도 9를 참조하면, 독출 전압 제어부(100)는 산포 측정부(distribution measurement unit, 110), 도메인 변환부(domain transformation unit, 120), 산포 변화 추정부(distribution variation estimation unit, 130) 및 전압 레벨 조절부(voltage level adjustment unit, 140)를 포함할 수 있다. 여기서, 산포 측정부(110)는 도 1의 전처리부(11)에 대응될 수 있고, 도메인 변환부(120)는 도 1의 도메인 변환부(12)에 대응될 수 있으며, 산포 변화 추정부(130) 및 전압 레벨 조절부(140)는 도 1의 후처리부(13)에 대응될 수 있다.

산포 측정부(110)는 입출력 회로(24)에서 출력된 복수의 데이터에 대한 산포를 측정하고, 측정 산포(p[i])를 생성할 수 있다. 이때, 산포 측정부(110)에서 출력되는 측정 산포(p[i])는 제1 도메인의 데이터일 수 있고, 예를 들어, 제1 도메인은 시간 도메인일 수 있다.

도메인 변환부(120)는 산포 측정부(110)에서 생성된 측정 산포(p[i])에 대해 도메인 변환을 수행하여, 도메인 변환된 측정 산포(P[k])를 생성할 수 있다. 구체적으로, 도메인 변환부(120)는 측정 산포(p[i])에 대해 상술된 다양한 도메인 변환을 수행하여, 도메인 변환된 측정 산포(P[k])를 생성할 수 있다. 이때, 도메인 변환부(120)에서 생성되는 도메인 변환된 측정 산포(P[k])는 제2 도메인의 데이터일 수 있고, 예를 들어, 제2 도메인은 주파수 도메인일 수 있다. 일 실시예에서, 도메인 변환부(120)는 측정 산포(p[i])에 IFFT(inverse fast fourier transform)를 수행하여 도메인 변환된 측정 산포(P[k])를 생성할 수 있다(즉, P[k] = IFFT{p[i]}).

산포 변화 추정부(130)는 도메인 변환부(120)에서 생성된 도메인 변환된 측정 산포(P[k])를 기초로 하여, 산포 변화를 추정할 수 있다. 여기서, 산포 변화는 기준 산포에 대한 측정 산포의 변화량을 나타내는데, 기준 산포는 메모리 셀들에 대한 문턱 전압의 변경이 생기기 전에 측정된 산포일 수 있다. 이때, 기준 산포에 대해서도 도메인 변환이 수행될 수 있고, 도메인 변환된 기준 산포()는 임의의 영역에 저장될 수 있다. 일 실시예에서, 도메인 변환된 기준 산포()는 메모리 셀 어레이(MCA)의 일부 저장 영역, 예를 들어, 일부 메모리 블록(BLK)에 저장될 수 있고, 다른 실시예에서, 도메인 변환된 기준 산포는 외부 저장 매체(EM)에 저장될 수도 있다.

전압 레벨 조절부(140)는 산포 변화 추정부(130)에서 추정된 산포 변화 및 기준 독출 전압(Vr)을 기초로 하여 독출 전압의 전압 레벨을 조절할 수 있다. 본 실시예에서, 전압 레벨 조절부(140)는 독출 전압 제어부(100)의 일부 구성 요소로서 메모리 컨트롤러(MC) 내에 포함되지만, 본 발명은 이에 한정되지 않는다. 다른 실시예에서, 전압 레벨 조절부(140)는 제어 로직(21)의 일부 구성 요소로서 메모리 장치(MEM) 내에 포함될 수 있다. 또 다른 실시예에서, 전압 레벨 조절부(140)는 독립적인 구성 요소로서 메모리 장치(MEM) 내에 포함될 수도 있다.

도 10는 도 9에 포함된 산포 측정부의 일 예를 나타내는 블록도이다.

도 10을 참조하면, 산포 측정부(110)는 데이터 독출부(data read unit, 111) 및 히스토그램 생성부(histogram generator, 112)를 포함할 수 있다. 이하에서는, 산포 측정부(110)에 포함된 각 구성 요소의 동작에 대하여 상술하기로 한다.

데이터 독출부(111)는 메모리 셀 어레이(MCA)에 포함된 복수의 메모리 셀들에 대한 산포를 측정하기 위한 복수의 독출 레벨들(R1, R2, ..., RN)을 설정하고, 복수의 독출 레벨들(R1, R2, ..., RN) 각각에서 복수의 메모리 셀들에 대한 독출 동작을 수행할 수 있다. 그러나, 다른 실시예에서, 데이터 독출부(111)는 복수의 독출 레벨들(R1, R2, ..., RN)을 외부로부터 수신할 수 있고, 이 경우, 수신된 복수의 독출 레벨들(R1, R2, ..., RN) 각각에서 복수의 메모리 셀들에 대한 독출 동작을 수행할 수 있다.

구체적으로, 데이터 독출부(111)는 제1 독출 레벨(R1)에서 복수의 메모리 셀들에 대한 독출 동작을 수행하는 경우, 복수의 메모리 셀들 중 문턱 전압이 제1 독출 레벨(R1)보다 작은 메모리 셀에 저장된 데이터는 '1'이고, 복수의 메모리 셀들 중 문턱 전압이 제1 독출 레벨(R1)보다 큰 메모리 셀에 저장된 데이터는 '0'으로 판별할 수 있다.

도 11은 도 10의 데이터 독출부의 동작을 설명하기 위하여, 메모리 셀에 대한 변경 전후의 문턱 전압 분포를 나타내는 그래프이다.

도 10 및 도 11을 참조하면, 가로축은 문턱 전압(Vth)을 나타내고, 세로축은 메모리 셀들의 개수를 나타낸다. 여기서, 실선은 메모리 셀의 초기 문턱 전압을 나타내고, 점선은 외부 자극 및/또는 마모 등에 의해 감소된 문턱 전압을 나타낸다. 또한, 굵은 선으로 표시된 영역은 문턱 전압 윈도우(window)(WIN)를 나타낸다.

데이터 독출부(111)는 전체 문턱 전압 영역이 아닌 일부 문턱 전압 영역, 즉, 소정의 문턱 전압 윈도우(WIN) 내에서 복수의 독출 레벨들(R1, R2, ..., RN)을 설정할 수 있다. 메모리 셀들의 산포는 외부 자극 및/또는 마모 등에 의해, 실선에서 점선의 방향으로 변경될 수 있는데, 이때, 복수의 상태들(S1 내지 S7)에 따른 산포들은 서로 유사한 비율로 변경될 수 있다. 그러므로, 복수의 상태들(S1 내지 S7)에 따른 산포들을 모두 획득하지 않고, 일부 상태들(예를 들어, S3 내지 S5)에 따른 산포들의 변화를 획득함으로써 다른 상태들에 따른 산포들의 변화도 추정할 수 있다. 본 실시예에 따르면, 산포 추정을 위한 독출 동작을 수행하는 경우에 있어서, 문턱 전압 윈도우(WIN) 내에서 복수의 독출 레벨들(R1, R2, ..., RN)을 설정함으로써, 독출 횟수를 줄일 수 있으므로, 연산의 복잡도를 감소시키고 산포 추정의 효율성을 향상시킬 수 있다.

일 실시예에서, 복수의 독출 레벨들(R1, R2, ..., RN) 사이의 간격(△)은 서로 동일할 수 있다. 다른 실시예에서, 복수의 독출 레벨들(R1, R2, ..., RN) 사이의 간격(△)은 서로 다르게 결정될 수도 있다. 구체적으로, 인접한 두 개의 상태들에 대한 산포들 사이의 영역(예를 들어, S3와 S4 사이의 영역)에서는 독출 레벨들 사이의 간격을 줄임으로써, 산포 측정부(11)의 성능을 더욱 향상시킬 수도 있다.

다시 도 10을 참조하면, 히스토그램 생성부(112)는 복수의 독출 레벨들(R1, R2, ..., RN) 각각에서 독출된 데이터 중 '1'의 개수 또는 '0'의 개수를 산출하고, 산출 결과를 기초로 하여 히스토그램을 생성할 수 있다. 이때, 생성된 히스토그램은 메모리 셀들의 문턱 전압의 변경에 따른 측정 산포로 이용될 수 있다.

이하에서는, 히스토그램 생성부(112)가 '1'의 개수를 산출하여 히스토그램을 생성하는 경우에 대해 상술하기로 한다. 이때, 히스토그램 생성부(112)는 아래의 수학식 1에 따라 히스토그램을 생성할 수 있다.

[수학식 1]

p[i] = c[i+1] - c[i]

여기서, p[i]는 i번째 독출 레벨에서 히스토그램을 나타내고, c[i]는 i번째 독출 레벨에서 독출된 데이터 중 '1'의 개수를 나타내고, c[i+1]은 i+1번째 독출 레벨에서 독출된 데이터 중 '1'의 개수를 나타내며, i는 N-1 이하의 정수이며, N은 복수의 독출 레벨들의 개수이다.

구체적으로, 히스토그램 생성부(112)는 제1 독출 레벨(R1)에서 독출된 데이터 중 '1'의 개수(c[1])와 제2 독출 레벨(R2)에서 독출된 데이터 중 '1'의 개수(c[2])의 차이를 기초로 하여 p[1]을 획득할 수 있고, 제2 독출 레벨(R2)에서 독출된 데이터 중 '1'의 개수(c[2])와 제3 독출 레벨(R3)에서 독출된 데이터 중 '1'의 개수(c[3])의 차이를 기초로 하여 p[2]을 획득할 수 있다.

도 12는 복수의 메모리 셀들에 대한 기준 산포와 변경 산포의 일 예를 나타내는 그래프이다.

도 12를 참조하면, 가로축은 문턱 전압을 V 단위로 나타내고, 세로축은 산포를 로그 스케일(log scale)로 나타낸다. 이때, 산포는 확률 밀도 함수(probability density function, pdf)에 해당할 수 있는데, 점선은 기준 산포를 나타내고, 실선은 변경 산포를 나타낸다. 본 예에서, 기준 산포와 변경 산포 사이의 평균 변화량(△m)은 0.12 V이고, 기준 산포와 변경 산포 사이의 분산 변화량()은 0.015이다. 이하에서는, 상기 평균 변화량(△m, 즉, 0.12 V) 및 분산 변화량(, 즉, 0.015)에 따라 메모리 셀들의 산포가 변경되는 경우에 대하여, 본 발명의 실시예들 및 이를 적용한 결과에 대해 상술하기로 한다.

반도체 메모리 장치에 포함된 복수의 메모리 셀들에 대한 확률 밀도 함수를 구하는 경우 연산의 복잡도가 매우 크다. 또한, 전체 문턱 전압 영역에서 복수의 독출 레벨들을 설정하고, 설정된 복수의 독출 레벨들 각각에서 히스토그램을 생성하여 산포를 측정하는 경우 연산에 소요되는 시간이 매우 크다.

도 13은 도 10의 산포 측정부에서 생성된 히스토그램의 일 예를 나타내는 그래프이다.

도 13을 참조하면, 가로축은 문턱 전압을 V 단위로 나타내고, 세로축은 산포를 로그 스케일로 나타낸다. 여기서, 복수의 독출 레벨들(R1, R2, ..., RN) 사이의 간격인 △는 0.2V이고, 문턱 전압 윈도우는 0.3V에서 2.7V까지이다. 이때, 산포는 수학식 1을 이용하여 획득한 히스토그램에 해당할 수 있는데, 점선은 기준 산포를 나타내고, 실선을 측정 산포를 나타낸다.

종래 기술에 따르면, 산포를 측정하기 위하여 전체 문턱 전압 영역에서 복수의 독출 레벨들을 설정하고, 복수의 독출 레벨들 각각에서 산포를 측정하였다. 그러나, 본 실시예에서, 산포 측정부(110)는 전체 문턱 전압 영역이 아닌 일부 문턱 전압 영역인 문턱 전압 윈도우에서 복수의 독출 레벨들(R1, R2, ..., RN)을 설정하고, 수학식 1을 이용하여 설정된 복수의 독출 레벨들(R1, R2, ..., RN) 각각에서 히스토그램을 생성할 수 있다. 이와 같이 생성된 히스토그램은 측정 산포로 이용될 수 있다. 따라서, 본 실시예에 따르면, 설정된 복수의 독출 레벨들(R1, R2, ..., RN)의 개수가 종래에 비해 크게 감소하므로, 연산량을 줄일 수 있다.

또한, 종래 기술에 따르면, 산포를 측정하기 위하여 복수의 독출 레벨들 사이의 간격(즉, 목표 해상도(target resolusion))을 약 20 mV 정도로 좁게 설정하고, 복수의 독출 레벨들 각각에서 산포를 측정하였다. 그러나, 본 실시예에서, 복수의 독출 레벨들(R1, R2, ..., RN) 사이의 간격인 △는 약 200 mV로서, 복수의 독출 레벨들 사이의 해상도는 종래 기술에 비해 상대적으로 낮다. 따라서, 본 실시예에 따르면, 상대적으로 낮은 해상도의 복수의 독출 레벨들(R1, R2, ..., RN)을 이용하여 산포를 측정함으로써, 산포 측정을 위한 연산량을 줄일 수 있다. 나아가, 복수의 독출 레벨들 사이의 해상도가 상대적으로 낮음에도 불구하고, 도메인 변환된 데이터를 기초로 하여 복수의 메모리 셀들에 대한 산포 변화를 추정함으로써 산포 변화 추정의 신뢰성을 향상시킬 수 있다. 이에 대해서는 이하에서 상술하기로 한다.

도 14는 도 9에 포함된 산포 변화 추정부 및 전압 레벨 조절부의 일 예를 나타내는 블록도이다.

도 14를 참조하면, 산포 변화 추정부(130A)는 위상 차이 산출부(131) 및 산포 중심 이동치 추정부(132)를 포함할 수 있다. 이에 따라, 복수의 메모리 셀들의 특정 상태의 산포가 특정 방향으로 이동하는 경우, 도메인 변환된 기준 산포()와 도메인 변환된 측정 산포() 사이의 위상 차이를 기초로 하여 산포 중심 이동치()를 추정할 수 있다.

외부 자극 및/또는 마모 등에 의해 메모리 셀의 문턱 전압이 변경되는 경우, 초기 문턱 전압이 V이고, 산포 중심 이동치가 △V이면, 변경된 문턱 전압 V'은 아래의 수학식 2를 이용하여 구할 수 있다.

[수학식 2]

V' = V + △V

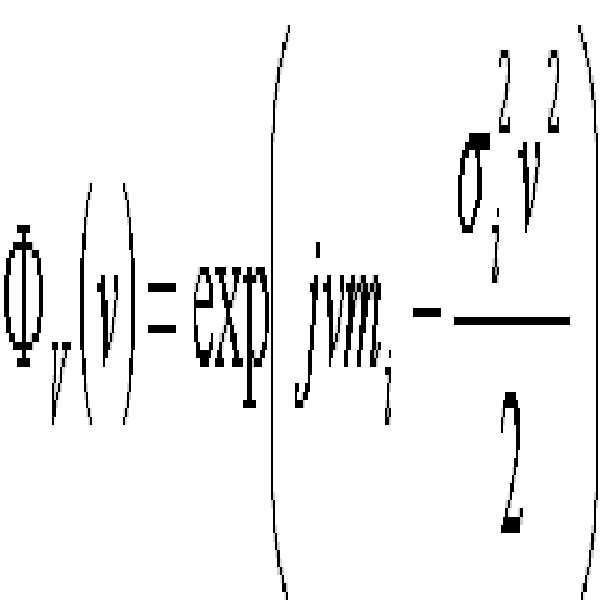

반도체 메모리 장치의 산포는 확률 이론에서 이용되는 확률 밀도 함수에 해당하는데, 확률 밀도 함수의 푸리에 변환 쌍(fourier transform pair)은 특성 함수(characteristic function)이다. 확률 변수 V의 특성 함수는 아래의 수학식 3과 같이 정의할 수 있다.

[수학식 3]

여기서, E[]는 기대값 연산(expectation operation)을 나타내고, 는 변환 전의 변수, 즉, 제1 도메인의 변수를 나타내며, 는 변환 후의 변수, 즉, 제2 도메인의 변수를 나타낸다.

수학식 2와 수학식 3을 이용하면, 변경된 문턱 전압에 해당하는 확률 변수 V'의 특성 함수는 아래의 수학식 4와 같이 정의할 수 있다.

[수학식 4]

수학식 4를 이용하면, △V는 아래의 수학식 5에 따라 산출할 수 있다.

[수학식 5]

이와 같이, 산포 중심 이동 전후의 특성 함수들(즉, 과 ) 사이의 위상 차이는 에 대한 일차식으로 표현할 수 있는데, 해당 일차식의 기울기는 산포 중심 이동치(△V)에 비례한다. 그러므로, 산포 중심 이동 전후의 특성 함수들(즉, 와 ) 사이의 위상 차이를 계산하고, 해당 일차식의 기울기를 추정하면, 문턱 전압의 산포 중심 이동치(△V)가 추정될 수 있다.

그러나, 특성 함수를 직접 계산하는 경우 복잡한 연산이 요구되므로, 본 실시예에서는, 특성 함수를 대신하여 도메인 변환부(12)의 출력, 즉, 도메인 변환된 측정 산포(P[k])를 이용할 수 있다. 이하에서는, 산포 변화 추정부(13A)의 구체적인 동작, 즉, 도메인 변환된 측정 산포(P[k])를 이용한 연산 동작에 대하여 상술하기로 한다.

위상 차이 산출부(131)는 도메인 변환된 측정 산포() 및 도메인 변환된 기준 산포()를 수신하고, 도메인 변환된 측정 산포()와 도메인 변환된 기준 산포() 사이의 위상 차이를 산출할 수 있다. 이때, 도메인 변환된 측정 산포()는 도메인 변환부(12)로부터 수신할 수 있다. 한편, 도메인 변환된 기준 산포()는, 도 9에 도시된 바와 같이, 일 실시예에서, 메모리 셀 어레이(MCA)의 일부 저장 영역, 예를 들어, 일부 메모리 블록(BLK)로부터 수신할 수 있고, 다른 실시예에서, 외부 저장 매체(EM)로부터 수신할 수 있다. 그러나, 다른 실시예에서, 위상 차이 산출부(131)는 도메인 변환되기 전의 기준 산포를 수신할 수도 있다.

구체적으로, 위상 차이 산출부(131)는 아래의 수학식 6을 이용하여 위상 차이를 산출할 수 있다.

[수학식 6]

여기서, 는 도메인 변환된 측정 산포와 도메인 변환된 기준 산포 사이의 위상 차이를 나타내고, 는 도메인 변환된 기준 산포(예를 들어, 기준 산포에 대한 IFFT 결과)이고, 는 도메인 변환된 측정 산포(예를 들어, 변화 이후의 측정 산포에 대한 IFFT 결과)이다. 이때, 와 는 등 간격으로 측정한 산포에 대해 IFFT를 적용한 결과일 수 있다. 여기서, 위상 차이 산출부(131)는 CORDIC(COordinate Rotation DIgital Computer) 알고리듬을 적용할 수 있고, 이로써, 위상 차이 산출부(131)에 대한 효율적인 하드웨어 구현이 가능하다.

도 15는 도메인 변환된 기준 산포의 위상 및 도메인 변환된 측정 산포의 위상의 일 예를 나타내는 그래프이다.

도 15를 참조하면, 가로축은 정규화 주파수(normalized frequency)를 나타내고, 세로축은 위상을 rad 단위로 나타낸다. 이때, 점선은 기준 산포의 위상(즉, ∠)을 나타내고, 실선은 측정 산포의 위상(즉, ∠)을 나타낸다.

도 16은 도메인 변환된 기준 산포와 도메인 변환된 측정 산포 사이의 위상 차이의 일 예를 나타내는 그래프이다.

도 16을 참조하면, 가로축은 정규화 주파수를 나타내고, 세로축은 위상 차이()를 rad 단위로 나타낸다. 도 16에서, 도메인 변환된 기준 산포 및 도메인 변환된 측정 산포 사이의 위상 차이()는 정규화 주파수에 대한 일차 함수로 근사될 수 있다.

다시 도 14를 참조하면, 산포 중심 이동치 추정부(132)는 위상 차이 산출부(131)로부터 수신한 위상 차이()를 기초로 하여 산포 중심 이동치()를 추정할 수 있다. 구체적으로, 산포 중심 이동치 추정부(132)는 수학식 6의 에 대하여 아래의 수학식 7과 같이 선형 최소 자승법(linear least square fitting)을 적용할 수 있다.

[수학식 7]

여기서, 는 산포 측정을 위해 설정한 복수의 독출 레벨들(R1, R2, ..., RN) 사이의 간격을 나타낸다. 이때, E를 최소화하는 를 에 대한 식으로 유도하면, 추정된 산포 중심 이동치()는 아래의 수학식 8과 같이 나타낼 수 있다.

[수학식 8]

[수학식 9]

상기 수학식 8을 도 15의 그래프에 적용하면, 추정된 산포 중심 이동치()는 -0.119 V 이다. 도 12의 그래프에서 기준 산포와 변경 산포 사이의 평균 변화량(△m)은 0.12 V 이므로, 본 실시예에 따른 산포 중심 이동치 추정부(132)에서 추정된 결과값은 추정 정확도가 매우 높은 것을 알 수 있다.

전압 레벨 조절부(140A)는 산포 변화 추정부(130A)에서 추정된 산포 중심 이동치() 및 기준 독출 전압(Vr)을 기초로 하여 독출 전압의 전압 레벨(Vr')을 조절할 수 있다. 여기서, 기준 독출 전압(Vr)은 문턱 전압의 변경이 생기기 전에 측정된 산포에서의 독출 전압이며, 메모리 장치(MEM)에 포함된 메모리 셀 어레이(MCA)의 일부 영역 또는 외부 저장 매체에 저장될 수 있다.

도 17은 도 14의 전압 레벨 조절부의 동작을 설명하기 위하여, 인접한 두 개의 산포들의 일 예를 나타내는 그래프이다.

도 17을 참조하면, 가로축은 문턱 전압을 나타내고, 세로축은 메모리 셀들의 개수를 나타낸다. 도 17에 도시된 제1 산포(Sa)와 제2 산포(Sb)는 동일한 분산을 가질 수 있다. 여기서, 제1 산포(Sa)의 중심 레벨은 m1이고, 제2 산포(Sb)의 중심 레벨은 m2이다. 이때, 제1 및 제2 산포(Sa, Sb)는 기준 산포일 수 있고, 메모리 셀이 3-비트 메모리 셀인 경우, 예를 들어, 제3 및 제4 상태(S3, S4)에 해당하는 산포들일 수 있다.

구체적으로, 전압 레벨 조절부(140A)는 아래의 수학식 10을 이용하여 독출 전압의 전압 레벨을 조절할 수 있다.

[수학식 10]

여기서, 은 산포 중심 이동 이전의 독출 전압의 최적 전압 레벨(Vr)에 해당한다. 이와 같이, 전압 레벨 조절부(14A)는 산포 중심 이동 이전의 독출 전압의 최적 전압 레벨()에 추정된 산포 중심 이동치()를 가산함으로써, 산포 중심 이동 이후의 독출 전압의 최적 전압 레벨(Vr')을 산출할 수 있다.

도 18은 도 9에 포함된 산포 변화 추정부 및 전압 레벨 조절부의 다른 예를 나타내는 블록도이다.

도 18을 참조하면, 산포 변화 추정부(130B)는 크기 차이 산출부(133) 및 분산 변화량 추정부(134)를 포함할 수 있다. 이에 따라, 반도체 메모리 장치의 특정 상태의 산포의 폭이 변화하는 경우, 즉, 분산이 변화하는 경우, 도메인 변환된 기준 산포()와 도메인 변환된 측정 산포() 사이의 크기 차이를 기초로 하여 분산 변화량()을 추정할 수 있다.

반도체 메모리 장치의 문턱 전압(V)이 각 상태 별로 정규 분포(즉, 가우시안 분포)를 따른다고 가정하고, i번째 레벨의 평균을 로, i번째 레벨의 분산을 로 정의하면, i번째 레벨에 해당하는 문턱 전압의 특성 함수는 아래의 수학식 11과 같이 나타낼 수 있다.

[수학식 11]

여기서, 산포의 폭이 변화한 이후의 문턱 전압을 로 정의하고, i번째 레벨의 문턱 전압의 분산 변화량을 이라고 가정하면, 산포의 폭이 변화한 이후의 문턱 전압인 의 특성 함수는 아래의 수학식 12와 같이 나타낼 수 있다.

[수학식 12]

여기서, 수학식 12의 양변에 절대값을 취하고, dB 스케일로 바꾸면 수학식 12는 다음 수학식 13과 같이 나타낼 수 있다.

[수학식 13]

이와 같이, 산포 폭 변화 전후의 특성 함수들(즉, 과 ) 사이의 크기 차이는, 산포 폭 변화 전후의 특성 함수들(즉, , ) 사이의 절대값의 차이를 dB 스케일로 나타낼 수 있다. 이때, 산포 폭 변화 전후의 특성 함수들(즉, 과 ) 사이의 크기 차이는, 에 대한 이차식으로 표현할 수 있는데, 해당 이차식의 계수를 분산 변화량()에 비례한다. 그러므로, 산포 폭 변화 전후의 특성 함수들(즉, 과 ) 사이의 크기 차이를 계산하고, 해당 이차식의 계수를 추정하면, 추정하면 문턱 전압의 분산 변화량()을 추정할 수 있다.

그러나, 특성 함수를 직접 계산하는 경우 복잡한 연산이 요구되므로, 본 실시예에서는, 특성 함수를 대신하여 도메인 변환부(120)의 출력, 즉, 도메인 변환된 측정 산포(P[k])를 이용할 수 있다. 이하에서는, 산포 변화 추정부(130B)의 구체적인 동작, 즉, 도메인 변환된 측정 산포(P[k])를 이용한 연산 동작에 대하여 상술하기로 한다.

크기 차이 산출부(133)는 도메인 변환된 측정 산포() 및 도메인 변환된 기준 산포()를 수신하고, 도메인 변환된 측정 산포()와 도메인 변환된 기준 산포() 사이의 크기 차이를 산출할 수 있다. 이때, 도메인 변환된 측정 산포()는 도메인 변환부(120)로부터 수신할 수 있다. 한편, 도메인 변환된 기준 산포()는, 도 9에 도시된 바와 같이, 일 실시예에서, 메모리 셀 어레이(MCA)의 일부 저장 영역, 예를 들어, 일부 메모리 블록(BLK)로부터 수신할 수 있고, 다른 실시예에서, 외부 저장 매체(EM)로부터 수신할 수 있다. 구체적으로, 크기 차이 산출부(133)는 아래의 수학식 14를 이용하여 크기 차이를 산출할 수 있다.

[수학식 14]

여기서, 는 도메인 변환된 측정 산포와 도메인 변환된 기준 산포 사이의 크기 차이를 나타내고, 는 도메인 변환된 기준 산포(예를 들어, 기준 산포에 대한 IFFT 결과)이고, 는 도메인 변환된 측정 산포(예를 들어, 변화 이후의 측정 산포에 대한 IFFT 결과)이다. 이때, 와 는 등 간격으로 측정한 산포에 대해 IFFT를 적용한 결과일 수 있다.

도 19는 도메인 변환된 기준 산포의 크기 및 도메인 변환된 측정 산포의 크기의 일 예를 나타내는 그래프이다.

도 19를 참조하면, 가로축은 정규화 주파수를 나타내고, 세로축은 크기를 dB 단위로 나타낸다. 이때, 점선은 기준 산포의 크기(즉, )를 나타내고, 실선은 측정 산포의 크기(즉, )를 나타낸다.

도 20은 도메인 변환된 기준 산포와 도메인 변환된 측정 산포 사이의 크기 차이의 일 예를 나타내는 그래프이다.

도 20을 참조하면, 가로축은 정규화 주파수를 나타내고, 세로축은 크기 차이()를 dB 단위로 나타낸다. 도 20에서, 도메인 변환된 기준 산포 및 도메인 변환된 측정 산포 사이의 크기 차이()는 정규화 주파수에 대한 이차 함수로 근사될 수 있다.

다시 도 18을 참조하면, 분산 변화량 추정부(134)는 크기 차이 산출부(133)로부터 수신한 크기 차이()를 기초로 하여 분산 변화량()을 추정할 수 있다. 구체적으로, 분산 변화량 추정부(134)는 수학식 14의 에 대하여 아래의 수학식 15와 같이 선형 최소 자승법을 적용할 수 있다.

[수학식 15]

여기서, 는 산포 측정을 위해 설정한 복수의 독출 레벨들(R1, R2, ..., RN) 사이의 간격을 나타낸다. 이때, E를 최소화하는 를 에 대한 식으로 유도하면, 추정된 분산 변화량()은 아래의 수학식 16과 같이 나타낼 수 있다.

[수학식 16]

[수학식 17]

상기 수학식 6을 도 20의 그래프에 적용하면, 추정된 분산 변화량()은 0.0152이다. 도 12의 그래프에서 기준 산포와 변경 산포 사이의 분산 변화량()은 0.015이므로, 본 실시예에 따른 분산 변화량 추정부(134)에서 추정된 결과값은 추정 정확도가 매우 높은 것을 알 수 있다.

전압 레벨 조절부(140B)는 산포 변화 추정부(130B)에서 추정된 분산 변화량() 및 기준 독출 전압(Vr)을 기초로 하여 독출 전압의 전압 레벨(Vr')을 조절할 수 있다. 여기서, 기준 독출 전압(Vr)은 문턱 전압의 변경이 생기기 전에 측정된 산포에서의 독출 전압이며, 메모리 장치(20)에 포함된 메모리 셀 어레이(MCA)의 일부 영역 또는 외부의 저장 매체에 저장될 수 있다.

도 21은 도 9에 포함된 산포 변화 추정부 및 전압 레벨 조절부의 또 다른 예를 나타내는 블록도이다.

도 21을 참조하면, 산포 변화 추정부(130C)는 위상 차이 산출부(131), 산포 중심 이동치 추정부(132), 크기 차이 산출부(133) 및 분산 변화량 추정부(134)를 포함할 수 있다. 이에 따라, 메모리 셀들에 대한 특정 상태의 산포 중심 및/또는 분산이 변화하는 경우, 도메인 변환된 기준 산포와 도메인 변환된 변경 산포 사이의 크기 차이를 기초로 하여 산포 중심 이동치 및/또는 분산 변화량을 추정할 수 있고, 이로써, 산포 변화를 추정할 수 있다.

위상 차이 산출부(131) 및 산포 중심 이동치 추정부(132)는 도 14의 산포 변화 추정부(130A)에 포함된 각 구성 요소들과 실질적으로 동일하게 동작할 수 있고, 크기 차이 산출부(133) 및 분산 변화량 추정부(134)는 도 18의 산포 변화 추정부(130B)에 포함된 각 구성 요소들과 실질적으로 동일하게 동작할 수 있다. 따라서, 위상 차이 산출부(131), 산포 중심 이동치 추정부(132), 크기 차이 산출부(133) 및 분산 변화량 추정부(134)의 동작에 대한 상세한 설명은 생략하기로 한다.

전압 레벨 조절부(140C)는 산포 변화 추정부(130C)에서 추정된 산포 중심 이동치(), 산포 변화 추정부(130C)에서 추정된 분산 변화량() 및 기준 독출 전압(Vr)을 기초로 하여 독출 전압의 전압 레벨(Vr')을 조절할 수 있다. 여기서, 기준 독출 전압(Vr)은 문턱 전압의 변경이 생기기 전에 측정된 산포에서의 독출 전압이며, 메모리 장치(20)에 포함된 메모리 셀 어레이(MCA)의 일부 영역 또는 외부의 저장 매체에 저장될 수 있다.

구체적으로, 산포 변화 추정부(130C)에서 출력된 값들을 이용하여 각 상태 별로 산포의 평균과 분산을 알아냈다고 가정하면, 전압 레벨 조절부(140C)는 아래의 수학식 18을 이용하여 독출 전압의 최적 전압 레벨()을 결정할 수 있다.

[수학식 18]

여기서, 은 변화 이후의 i번째 산포의 평균으로써, 으로 근사될 수 있고, 은 변화 이후의 i번째 산포의 분산으로써, 으로 근사될 수 있다. 이와 같이, 독출 전압의 최적 전압 레벨()은 각 상태에 따른 산포가 정규 분포를 따른다고 가정했을 때, 인접한 두 상태들의 확률 밀도 함수들이 서로 일치하는 전압 값을 찾음으로써 결정될 수 있다.

상술한 바와 같이, 일 실시예에서, 산포 측정부(110), 도메인 변환부(120), 산포 변화 추정부(130) 및 전압 레벨 조절부(140)는 메모리 컨트롤러(MC)에 포함될 수 있다. 그러나, 다른 실시예에서, 산포 측정부(110), 도메인 변환부(120), 산포 변화 추정부(130)는 메모리 컨트롤러(10A)에 포함되고, 전압 레벨 조절부(140)는 메모리 장치(20)에 포함될 수도 있다. 또 다른 실시예에서, 산포 측정부(110), 도메인 변환부(120)는 메모리 컨트롤러(10A)에 포함되고, 산포 변화 추정부(130) 및 전압 레벨 조절부(140)는 메모리 장치(20)에 포함될 수 있다. 이에 따라, 메모리 컨트롤러(10A)에서 메모리 장치(20)에 대한 독출 횟수를 줄일 수 있다.

도 22는 본 발명의 다른 실시예에 따른 반도체 메모리 시스템을 나타내는 블록도이다.

도 22를 참조하면, 반도체 메모리 시스템(2)은 메모리 컨트롤러(30) 및 메모리 장치(40)를 포함할 수 있다. 메모리 장치(40)는 메모리 셀 어레이(MCA) 및 제어부(CTRL)를 포함할 수 있고, 제어부(CON)는 전처리부(41), 도메인 변환부(42) 및 후처리부(43)를 포함할 수 있다.

메모리 셀 어레이(MCA)는 복수의 메모리 셀들을 포함할 수 있다. 제어부(CTRL)는 복수의 메모리 셀들에 기록하거나 복수의 메모리 셀로부터 독출한 데이터에 대해 도메인 변환을 수행하고, 도메인 변환된 데이터에 대해 신호 처리를 수행하여 가공된 데이터 또는 제어 신호를 출력할 수 있다.

구체적으로, 전처리부(41)는 데이터가 신호 처리에 적합한 형식으로 변경되도록 데이터에 대해 전처리를 수행할 수 있다. 도메인 변환부(42)는 전처리가 수행된 데이터를 제1 도메인에서 제2 도메인으로 변환할 수 있다. 후처리부(43)는 제2 도메인으로 변환된 데이터에 대해 후처리를 수행하여 가공된 데이터 또는 제어 신호를 출력할 수 있다.

본 실시예에 따른 반도체 메모리 시스템(2)은 도 1에 도시된 반도체 메모리 시스템(1)의 변형 실시예로서, 도 1을 참조하여 상술된 내용은 본 실시예에 따른 반도체 메모리 시스템(2)에도 적용될 수 있다. 구체적으로, 도 1에 도시된 반도체 메모리 시스템(1)에서, 전처리부(11), 도메인 변환부(12) 및 후처리부(13)가 메모리 컨트롤러(10)에 포함된 반면, 본 실시예에 따른 반도체 메모리 시스템에서는, 전처리부(41), 도메인 변환부(42) 및 후처리부(43)는 메모리 장치(40)에 포함될 수 있다. 이에 따라, 메모리 컨트롤러(30)와 메모리 장치(40) 사이의 신호 입출력 시에 발생하는 부하를 줄일 수 있다.

도 23은 도 22의 반도체 메모리 시스템의 일 예를 나타내는 블록도이다.

도 23을 참조하면, 반도체 메모리 시스템(2A)은 메모리 컨트롤러(30) 및 메모리 장치(40A)를 포함할 수 있다. 메모리 장치(40A)는 메모리 셀 어레이(MCA) 및 제어부(CTRL)를 포함할 수 있고, 제어부(CTRL)는 독출 전압 제어부(400)를 포함할 수 있다. 구체적으로, 독출 전압 제어부(400)는 복수의 메모리 셀들로부터 독출한 데이터에 대해 도메인 변환을 수행하고 도메인 변환된 데이터를 기초로 하여 복수의 셀들에 대한 산포 변화를 추정함으로써, 데이터를 독출하기 위한 독출 전압의 레벨을 제어할 수 있다.

본 실시예에 따른 반도체 메모리 시스템(2A)은 도 2에 도시된 반도체 메모리 시스템(1A)의 변형 실시예로서, 도 2을 참조하여 상술된 내용은 본 실시예에 따른 반도체 메모리 시스템(2A)에도 적용될 수 있다. 본 실시예에 따른 반도체 메모리 시스템(2A)에서 독출 전압 제어부(400)는 메모리 컨트롤러(30)가 아닌 메모리 장치(40A)에 포함될 수 있다. 이에 따라, 메모리 컨트롤러(30)와 메모리 장치(40A) 사이의 신호 입출력 시에 발생하는 부하를 줄일 수 있다.

도 24는 도 23의 반도체 메모리 시스템을 보다 상세하게 나타내는 블록도이다.

도 24를 참조하면, 반도체 메모리 시스템(2A)은 메모리 컨트롤러(30) 및 메모리 장치(40A)를 포함할 수 있고, 메모리 장치(40A)는 메모리 셀 어레이(MCA), 제어 로직(21), 전압 발생기(22), 로우 디코더(23), 입출력 회로(24) 및 독출 전압 제어부(400)를 포함할 수 있다. 도 8를 참조하여 상술된 내용은 본 실시예에 따른 반도체 메모리 시스템(2A)에도 적용될 수 있다. 또한, 도 9 내지 도 21을 참조하여 상술된 내용은 본 실시예에 따른 독출 전압 제어부(400)에도 적용될 수 있다.

본 발명의 실시예들에 따른 반도체 메모리 장치 및/또는 메모리 컨트롤러는 다양한 형태들의 패키지를 이용하여 구현될 수 있다. 예를 들면, 본 발명의 실시예들에 따른 반도체 메모리 장치 및/또는 메모리 컨트롤러는 PoP(Package on Package), Ball grid arrays(BGAs), Chip scale packages(CSPs), Plastic Leaded Chip Carrier(PLCC), Plastic Dual In-Line Package(PDIP), Die in Waffle Pack, Die in Wafer Form, Chip On Board(COB), Ceramic Dual In-Line Package(CERDIP), Plastic Metric Quad Flat Pack(MQFP), Thin Quad Flatpack(TQFP), Small Outline(SOIC), Shrink Small Outline Package(SSOP), Thin Small Outline(TSOP), Thin Quad Flatpack(TQFP), System In Package(SIP), Multi Chip Package(MCP), Wafer-level Fabricated Package(WFP), Wafer-Level Processed Stack Package(WSP) 등과 같은 패키지들을 이용하여 구현될 수 있다.

도 25는 본 발명의 일 실시예에 따른 반도체 메모리 시스템의 신호 처리 방법을 나타내는 흐름도이다.

도 25를 참조하면, 반도체 메모리 시스템의 신호 처리 방법은 도 1 내지 도 24에 도시된 반도체 메모리 장치 또는 반도체 메모리 시스템에서의 신호 처리 방법을 나타낸다. 따라서, 도 1 내지 도 24를 참조하여 상술된 내용은 본 실시예에도 적용될 수 있다.

S110 단계에서, 메모리 장치로부터 데이터를 독출한다. 한편, 다른 실시예에서는, S110 단계를 대신하여, 메모리 장치에 기입할 데이터를 수신하는 단계를 포함할 수도 있다.

S120 단계에서, 독출된 데이터에 대해 전처리를 수행한다. 구체적으로, 독출된 데이터가 신호 처리에 적합한 형식으로 변경되도록 독출된 데이터에 대해 전처리를 수행할 수 있다.

S130 단계에서, 전처리된 데이터를 제1 도메인에서 제2 도메인으로 변환한다. 구체적으로, 전처리된 데이터에 대해 아벨 변환, 베이트만 변환, 푸리에 변환, 단구간 푸리에 변환, 한켈 변환, 하트리 변환, 힐버트 변환, 힐버트-슈미트 적분 연산자, 라플라스 변환, 양면 라플라스 변환, LST, LCT, 멜린 변환, 포아송-멜린-뉴튼 사이클, 라돈 변환, 스틸레스 변환, 수무두 변환, 라플라스-카슨 변환, 웨이블릿 변환, 이항 변환, 이산 푸리에 변환, 고속 푸리에 변환, 이산 코사인 변환, 변형 이산 코사인 변환, 이산 하트리 변환, 이산 사인 변환, 이산 웨이블렛 변환, 고속 웨이블릿 변환, IBDWT, 수론 변환, 스터링 변환, Z 변환, 카루넨-뢰브 변환, 백룬트 변환, 양선형 변환, 박스-뮬러 변환, 버로우즈-휠러 변환, 처플렛 변환, 거리 변환, 프랙탈 변환, 하다마드 변환, 허프 변환, 르장드르 변환, 뫼비우스 변환, 원근 변환, Y-델타 변환, 하에시안 변환 및 상기 변환들에 대한 역변환들 중 적어도 하나를 수행할 수 있다. 예를 들어, 제1 도메인은 시간 도메인이고, 제2 도메인은 주파수 도메인일 수 있다.

S140 단계에서, 제2 도메인으로 변환된 데이터에 대해 후처리를 수행한다. 구체적으로, 제2 도메인으로 변환된 데이터에 대해 최대 우도 추정/검출, 베이지안 추정/검출, 모멘트 추정법, 최소 평균 제곱 오차, MAP 추정/검출, 최소 분산 불편 추정량, 최적 선형 불편 추정량, 최소 제곱법, 불편 추정량, 파티클 필터, MCMC, 칼만 필터, 앙상블 칼만 필터 및 위너 필터 중 적어도 하나를 수행할 수 있다.

도 26은 본 발명의 일 실시예에 따른 반도체 메모리 시스템의 독출 전압 제어 방법을 나타내는 흐름도이다.

도 26을 참조하면, 반도체 메모리 시스템의 독출 전압 제어 방법은 도 1 내지 도 24에 도시된 반도체 메모리 장치 또는 반도체 메모리 시스템에서의 독출 제어 방법을 나타낸다. 따라서, 도 1 내지 도 24를 참조하여 상술된 내용은 본 실시예에도 적용될 수 있다.

S210 단계에서, 복수의 메모리 셀들에 저장된 복수의 데이터에 대한 산포를 측정하여, 측정 산포를 생성한다. 구체적으로, 복수의 메모리 셀들에 대한 산포를 측정하기 위한 복수의 독출 레벨들을 설정하고, 복수의 독출 레벨들 각각에서 복수의 메모리 셀들에 대한 독출 동작을 수행할 수 있다. 이어서, 복수의 독출 레벨들 각각에서 독출된 데이터 중 '1'의 개수 또는 '0'의 개수를 산출하고, 산출 결과를 기초로 하여 히스토그램을 생성할 수 있으며, 생성된 히스토그램은 측정 산포로 이용될 수 있다.

S220 단계에서, 측정 산포에 대해 도메인 변환을 수행하여, 도메인 변환된 측정 산포를 생성한다. 구체적으로, 측정 산포에 대해 아벨 변환, 베이트만 변환, 푸리에 변환, 단구간 푸리에 변환, 한켈 변환, 하트리 변환, 힐버트 변환, 힐버트-슈미트 적분 연산자, 라플라스 변환, 양면 라플라스 변환, LST, LCT, 멜린 변환, 포아송-멜린-뉴튼 사이클, 라돈 변환, 스틸레스 변환, 수무두 변환, 라플라스-카슨 변환, 웨이블릿 변환, 이항 변환, 이산 푸리에 변환, 고속 푸리에 변환, 이산 코사인 변환, 변형 이산 코사인 변환, 이산 하트리 변환, 이산 사인 변환, 이산 웨이블렛 변환, 고속 웨이블릿 변환, IBDWT, 수론 변환, 스터링 변환, Z 변환, 카루넨-뢰브 변환, 백룬트 변환, 양선형 변환, 박스-뮬러 변환, 버로우즈-휠러 변환, 처플렛 변환, 거리 변환, 프랙탈 변환, 하다마드 변환, 허프 변환, 르장드르 변환, 뫼비우스 변환, 원근 변환, Y-델타 변환, 하에시안 변환 및 상기 변환들에 대한 역변환들 중 적어도 하나를 수행하여 도메인 변환된 측정 산포를 생성할 수 있다.

S230 단계에서, 도메인 변환된 측정 산포를 기초로 하여, 기준 산포에 대한 측정 산포의 변화를 나타내는 산포 변화를 추정한다. 일 실시예에서, 도메인 변환된 측정 산포와 도메인 변환된 기준 산포 사이의 위상 차이를 산출하고, 산출된 위상 차이를 기초로 하여 기준 산포에 대한 측정 산포의 산포 중심 이동치를 추정할 수 있다. 다른 실시예에서, 도메인 변환된 측정 산포와 도메인 변환된 기준 산포 사이의 크기 차이를 산출하고, 산출된 크기 차이를 기초로 하여 기준 산포에 대한 측정 산포의 분산 변화량을 추정할 수 있다. 또 다른 실시예에서, 도메인 변환된 측정 산포와 도메인 변환된 기준 산포 사이의 위상 차이 및 크기 차이를 산출하고, 산출된 위상 차이 및 크기 차이를 기초로 하여, 기준 산포에 대한 측정 산포의 산포 중심 이동치 및 분산 변화량을 추정할 수 있다.

S240 단계에서, 추정된 산포 변화 및 기준 독출 전압을 기초로 하여, 복수의 데이터를 독출하기 위한 독출 전압의 전압 레벨을 조절한다.

상술된 반도체 메모리 장치의 독출 전압 제어 방법은 다양한 컴퓨터 수단을 통하여 수행될 수 있는 프로그램 명령 형태로 구현되어 컴퓨터 판독 가능 매체에 기록될 수 있다. 상기 컴퓨터 판독 가능 매체는 프로그램 명령, 데이터 파일, 데이터 구조 등을 단독으로 또는 조합하여 포함할 수 있다. 상기 매체에 기록되는 프로그램 명령은 본 발명을 위하여 특별히 설계되고 구성된 것들이거나 컴퓨터 소프트웨어 당업자에게 공지되어 사용 가능한 것일 수도 있다. 컴퓨터 판독 가능 기록 매체의 예에는 하드 디스크, 플로피 디스크 및 자기 테이프와 같은 자기 매체(magneticmedia), CD-ROM, DVD와 같은 광기록 매체(optical media), 플롭티컬 디스크(folptical disk)와 같은 자기-광 매체(magneto-optical media), 및 롬(ROM), 램(RAM) 플래시 메모리 등과 같은 프로그램 명령을 저장하고 수행하도록 특별히 구성된 하드웨어 장치가 포함된다. 프로그램 명령 예에는 컴파일러에 의해 만들어지는 것과 같은 기계어 코드뿐만 아니라 인터프리터 등을 사용해서 컴퓨터에 의해서 실행될 수 있는 고급 언어 코드를 포함한다. 상기된 하드웨어 장치는 본 발명의 동작을 수행하기 위해 하나 이상의 소프트 웨어 모듈로서 작동하도록 구성될 수 있으며, 그 역도 마찬가지이다.

도 27은 도 26에 도시된 독출 전압 제어 방법에 포함된 측정 산포를 생성하는 단계를 더욱 상세하게 나타내는 흐름도이다.

도 27을 참조하면, 복수의 메모리 셀들에 저장된 복수의 데이터에 대한 산포를 측정하여 측정 산포를 생성하는 단계는 도 9 내지 도 13을 참조하여 상술된 산포 측정부(110)에서 측정 산포를 생성하는 방법을 나타낸다. 따라서, 도 9 내지 도 13을 참조하여 상술된 내용은 본 실시예에도 적용될 수 있다.

S2110 단계에서, 메모리 셀 어레이에 포함된 복수의 메모리 셀들에 대한 산포를 측정하기 위한 복수의 독출 레벨들 사이의 간격이 상대적으로 넓도록 복수의 독출 레벨들을 설정한다. 예를 들어, 복수의 독출 레벨들 사이의 간격은 약 200 mV일 수 있다. 이와 같이, 복수의 독출 레벨들 사이의 간격을 상대적으로 넓게 설정함으로써, 복수의 독출 레벨들의 해상도는 상대적으로 낮아질 수 있다. 그럼에도 불구하고, 본 실시예에 따르면, 도메인 변환된 데이터를 기초로 하여 복수의 메모리 셀들에 대한 산포 변화를 추정함으로써 산포 변화 추정의 신뢰성을 향상시킬 수 있다.

S2120 단계에서, 설정된 복수의 독출 레벨들 각각에서 복수의 메모리 셀들에 대한 독출 동작을 수행한다. 이와 같이, S2110 단계 및 S2120 단계에 따라 복수의 독출 레벨들의 개수를 줄일 수 있고, 복수의 메모리 셀들에 대한 독출 동작을 수행 횟수를 줄일 수 있으므로, 산포 측정을 위한 연산량을 줄일 수 있다.

S2130 단계에서, 복수의 독출 레벨들 각각에서 독출된 데이터 중 '1'의 개수 또는 '0'의 개수를 산출한다.

S2140 단계에서, 산출된 '1'의 개수 또는 '0'의 개수를 기초로 하여 히스토그램을 생성한다. 여기서, 생성된 히스토그램은 측정 산포로 이용될 수 있다.

도 28은 본 발명의 일 실시예에 따른 컴퓨팅 시스템 장치를 나타내는 블럭도이다.

도 28을 참조하면, 컴퓨팅 시스템 장치(CSYS)은 버스(BUS)에 전기적으로 연결된 프로세서(CPU), 사용자 인터페이스(UI) 및 반도체 메모리 시스템(MSYS)을 구비할 수 있다. 반도체 메모리 시스템(MSYS)은 메모리 컨트롤러(MC) 및 반도체 메모리 장치(MEM)를 포함할 수 있다. 반도체 메모리 장치(MEM)에는 프로세서(CPU)에 의해서 처리된/처리될 N-비트 데이터(N은 1 또는 그 보다 큰 정수)가 저장될 수 있다. 도 1 내지 도 24를 참조하여 상술한 반도체 메모리 시스템들(1, 1A, 2, 2A)는 본 실시예에 따른 반도체 메모리 시스템(MSYS)에 적용될 수 있다.

본 발명의 실시예에 따른 컴퓨팅 시스템 장치(CSYS)는 파워 공급 장치(PS)를 더 구비할 수 있다. 또한, 반도체 메모리 장치(MEM)가 플래시 메모리 장치일 경우, 본 발명의 실시예에 따른 컴퓨팅 시스템 장치(CSYS)는 휘발성 메모리 장치(예를 들어, RAM)을 더 구비할 수 있다.

본 발명의 실시예에 따른 컴퓨팅 시스템 장치(CSYS)가 모바일 장치인 경우, 컴퓨팅 시스템의 동작 전압을 공급하기 위한 배터리 및 베이스밴드 칩셋(baseband chipset)과 같은 모뎀이 추가적으로 제공될 수 있다. 또한, 본 발명의 실시예에 따른 컴퓨팅 시스템 장치(CSYS)에는 응용 칩셋(application chipset), 카메라 이미지 프로세서(Camera Image Processor: CIS), 모바일 디램 등이 더 제공될 수 있음은 이 분야의 통상적인 지식을 습득한 자들에게 자명한 사항인 바, 더 자세한 설명은 생략한다. 메모리 장치(MEM)는 데이터를 저장하는데 불휘발성 메모리를 사용하는 SSD(Solid State Drive/Disk)를 구성할 수 있다.

도 29는 본 발명의 일 실시예에 따른 메모리 카드를 나타내는 블록도이다.

도 29를 참조하면, 본 발명의 실시예에 따른 메모리 카드(MCRD)는, 메모리 컨트롤러(MC) 및 반도체 메모리 장치(MEM)를 구비할 수 있다. 메모리 컨트롤러(MC)는 입출력 수단(I/O)를 통해 수신되는 외부의 호스트(미도시)의 요청에 응답하여 반도체 메모리 장치(MEM)로의 데이터 기입 또는 반도체 메모리 장치(MEM)로부터의 데이터 독출을 제어할 수 있다. 또한, 메모리 컨트롤러(MC)는 반도체 메모리 장치(MEM)가 플래시 메모리 장치인 경우, 반도체 메모리 장치(MEM)에 대한 소거 동작을 제어할 수 있다. 본 발명의 일 실시예에 따른 메모리 카드(MCRD)의 메모리 컨트롤러(MC)는 상기와 같은 제어 동작을 수행하기 위해, 호스트 및 메모리 장치와의 인터페이스를 수행하는 인터페이스부들(미도시) 및 램(RAM) 등을 구비할 수 있다. 특히, 본 발명의 일 실시예에 따른 메모리 카드(MCRD)의 메모리 컨트롤러(MC)는 도 1 내지 도 24의 메모리 컨트롤러(MC)일 수 있다. 또한, 본 발명의 일 실시예에 따른 메모리 카드(MCRD)의 메모리 장치(MEM)는 도 1 내지 도 24의 메모리 장치(MEM)일 수 있다.

도 29의 메모리 카드(MCRD)는 컴팩트 플래시 카드(CFC: Compact Flash Card), 마이크로 드라이브(Microdrive), 스마트 미디어 카드(SMC: Smart Media Card) 멀티미디어 카드(MMC: Multimedia Card), 보안 디지털 카드(SDC: Security Digital Card), 메모리 스틱(Memory Stick), 및 USB 플래시 메모리 드라이버 등으로 구현될 수 있다.

도 30은 본 발명의 일 실시예에 따른 솔리드 스테이트 드라이브(SSD: Solid State Drive)를 나타내는 블록도이다.

도 30을 참조하면, 본 발명의 일 실시예에 따른 SSD는 SSD 컨트롤러(SCTL) 및 메모리 장치(MEM)를 포함할 수 있다. SSD 컨트롤러(SCTL)는 버스(BUS)로 연결되는 프로세서(PROS), 램(RAM), 캐쉬 버퍼(CBUF) 및 메모리 컨트롤러(MC)를 구비할 수 있다. 프로세서(PROS)는 호스트(미도시)의 요청(명령, 어드레스, 데이터)에 응답하여 메모리 컨트롤러(MC)가 메모리 장치(MEM)와 데이터를 송수신하도록 제어한다. 본 발명의 일 실시예에 따른 SSD의 프로세서(PROS) 및 메모리 컨트롤러(MC)는 하나의 ARM 프로세서로 구현될 수도 있다. 프로세서(PROS)의 동작에 필요한 데이터는 램(RAM)에 로딩될 수 있다.

호스트 인터페이스(HOST I/F)는 호스트의 요청을 수신하여 프로세서(PROS)로 전송하거나, 메모리 장치(MEM)로부터 전송된 데이터를 호스트로 전송한다. 호스트 인터페이스(HOST I/F)는 USB(Universal Serial Bus), MMC(Man Machine Communication), PCI-E(Peripheral Component Interconnect-Express), SATA(Serial Advanced Technology Attachment), PATA(Parallel Advanced Technology Attachment), SCSI(Small Computer System Interface), ESDI(Enhanced Small Device Interface), 그리고 IDE(Intelligent Drive Electronics) 등과 같은 다양한 인터페이스 프로토콜로, 호스트와 인터페이스 할 수 있다. 메모리 장치(MEM)로 전송하고자 하거나, 메모리 장치(MEM)로부터 전송된 데이터는 캐쉬 버퍼(CBUF)에 임시로 저장될 수 있다. 캐쉬 버퍼(CBUF)는 SRAM 등일 수 있다.

본 발명의 일 실시예에 따른 SSD에 구비되는 메모리 컨트롤러(MC) 및 메모리 장치(MEM)는 각각, 도 1 내지 도 24의 메모리 컨트롤러(MC) 및 메모리 장치(MEM)일 수 있다.

이상에서 설명한 본 발명이 전술한 실시예 및 첨부된 도면에 한정되지 않으며, 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 여러 가지 치환, 변형 및 변경이 가능하다는 것은, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 있어 명백할 것이다.

Claims (10)

- 복수의 메모리 셀들이 배치된 메모리 셀 어레이를 포함하는 메모리 장치; 및

상기 복수의 메모리 셀들에 기록하거나 상기 복수의 메모리 셀들로부터 독출한 데이터에 대해 도메인 변환을 수행하고, 도메인 변환된 데이터를 제공하며, 상기 도메인 변환된 데이터에 대해 신호 처리를 수행하여 가공된 데이터 또는 제어 신호를 출력함으로써 상기 메모리 장치를 제어하는 메모리 컨트롤러를 포함하고,

상기 메모리 컨트롤러는,

상기 복수의 메모리 셀들로부터 독출한 데이터에 대해 도메인 변환을 수행하고 도메인 변환된 상기 데이터를 기초로 하여 상기 복수의 메모리 셀들에 대한 산포 변화를 추정하여 추정된 산포 변화를 제공함으로써, 상기 데이터를 독출하기 위한 독출 전압의 전압 레벨을 제어하는 독출 전압 제어부를 포함하는 반도체 메모리 시스템. - 제1항에 있어서,

상기 메모리 컨트롤러는, 상기 데이터를 시간 도메인에서 주파수 도메인으로 변환하고, 상기 도메인 변환된 데이터를 제공하는 것을 특징으로 하는 반도체 메모리 시스템. - 제1항에 있어서,

상기 독출 전압 제어부는,

상기 데이터에 대해 전처리를 수행하여, 전처리된 데이터를 상기 신호 처리에 적합한 형식으로 제공하는 전처리부;

상기 전처리된 데이터를 제1 도메인에서 제2 도메인으로 변환하여, 변환된 데이터를 제공하는 도메인 변환부; 및

상기 제2 도메인의 상기 변환된 데이터에 대해 후처리를 수행하여 상기 가공된 데이터 또는 상기 제어 신호를 출력하는 후처리부를 포함하는 것을 특징으로 하는 반도체 메모리 시스템. - 제3항에 있어서,

상기 도메인 변환부는,

전치리가 수행된 상기 데이터에 대해 푸리에 변환(Fourier transform), 힐버트 변환(Hilbert transform), 및 라플라스 변환(Laplace transform) 중 선택된 적어도 하나의 변환 또는 역변환을 수행하는 것을 특징으로 하는 반도체 메모리 시스템. - 제3항에 있어서,

상기 후처리부는,

상기 제2 도메인의 상기 변환된 데이터에 대해 최대 우도 추정/검출(Maximum likelihood estimation/detection) 및 베이지안 추정/검출(Bayesian estimation/detection) 중 적어도 하나를 수행하는 것을 특징으로 하는 반도체 메모리 시스템. - 삭제

- 제1항에 있어서,

상기 독출 전압 제어부는,

상기 데이터에 대한 산포를 측정하여, 측정 산포를 제공하는 산포 측정부;

상기 측정 산포에 대해 도메인 변환을 수행하여, 도메인 변환된 측정 산포를 제공하는 도메인 변환부; 및

상기 도메인 변환된 측정 산포를 기초로 하여, 기준 산포에 대한 상기 측정 산포의 변화를 나타내는 상기 산포 변화를 추정하는 산포 변화 추정부를 포함하는 것을 특징으로 하는 반도체 메모리 시스템. - 제7항에 있어서,

상기 독출 전압 제어부는,

추정된 상기 산포 변화 및 기준 독출 전압을 기초로 하여, 상기 독출 전압의 전압 레벨을 조절하는 전압 레벨 조절부를 더 포함하는 것을 특징으로 하는 반도체 메모리 시스템. - 제7항에 있어서,

상기 산포 변화 추정부는,

상기 도메인 변환된 측정 산포와 도메인 변환된 기준 산포 사이의 위상 차이를 산출하는 위상 차이 산출부; 및

상기 위상 차이를 기초로 하여, 상기 기준 산포에 대한 상기 측정 산포의 산포 중심 이동치를 추정하는 산포 중심 이동치 추정부를 포함하는 것을 특징으로 하는 반도체 메모리 시스템. - 제7항에 있어서,

상기 산포 변화 추정부는,

상기 도메인 변환된 측정 산포와 도메인 변환된 기준 산포 사이의 크기 차이를 산출하는 크기 차이 산출부; 및

상기 크기 차이를 기초로 하여, 상기 기준 산포에 대한 상기 측정 산포의 분산의 변화량을 추정하는 분산 변화량 추정부를 포함하는 것을 특징으로 하는 반도체 메모리 시스템.

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020110016643A KR101818504B1 (ko) | 2011-02-24 | 2011-02-24 | 반도체 메모리 장치 및 반도체 메모리 시스템 |

| US13/404,625 US8817545B2 (en) | 2011-02-24 | 2012-02-24 | Semiconductor memory devices, systems including non-volatile memory read threshold voltage determination |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020110016643A KR101818504B1 (ko) | 2011-02-24 | 2011-02-24 | 반도체 메모리 장치 및 반도체 메모리 시스템 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20120097209A KR20120097209A (ko) | 2012-09-03 |

| KR101818504B1 true KR101818504B1 (ko) | 2018-01-15 |

Family

ID=46719798

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020110016643A KR101818504B1 (ko) | 2011-02-24 | 2011-02-24 | 반도체 메모리 장치 및 반도체 메모리 시스템 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8817545B2 (ko) |

| KR (1) | KR101818504B1 (ko) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103678139B (zh) * | 2012-08-31 | 2017-09-29 | 国际商业机器公司 | 进行瘦供给的方法和装置 |

| US8913438B2 (en) | 2013-02-20 | 2014-12-16 | Seagate Technology Llc | Adaptive architecture in a channel detector for NAND flash channels |

| US9367389B2 (en) * | 2013-03-14 | 2016-06-14 | Seagate Technology Llc | Recovery strategy that reduces errors misidentified as reliable |

| US9195396B2 (en) | 2013-03-14 | 2015-11-24 | SanDisk Technologies, Inc. | Estimating access frequency statistics for storage device |

| US9589673B1 (en) * | 2014-03-20 | 2017-03-07 | SK Hynix Inc. | Estimation of an optimal read threshold using symmetry |

| US9455029B2 (en) * | 2014-05-23 | 2016-09-27 | Micron Technology, Inc. | Threshold voltage analysis |

| KR20160051331A (ko) * | 2014-11-03 | 2016-05-11 | 에스케이하이닉스 주식회사 | 데이터 복구 방법 및 이를 사용한 비휘발성 메모리 시스템 |

| KR20160051328A (ko) * | 2014-11-03 | 2016-05-11 | 에스케이하이닉스 주식회사 | 데이터 복구 방법 및 이를 사용한 비휘발성 메모리 시스템 |

| KR20160108000A (ko) * | 2015-03-06 | 2016-09-19 | 에스케이하이닉스 주식회사 | 복수의 전압 상태들을 갖는 메모리 셀들을 포함하는 메모리 시스템 및 그것의 동작 방법 |

| CN106293539A (zh) * | 2016-08-18 | 2017-01-04 | 华为技术有限公司 | 一种闪存设备的访问方法、装置和系统 |

| KR102620820B1 (ko) | 2016-09-23 | 2024-01-03 | 삼성전자주식회사 | 비휘발성 메모리 장치의 데이터 독출 방법 |

| US10236067B2 (en) * | 2017-08-02 | 2019-03-19 | International Business Machines Corporation | State-dependent read voltage threshold adaptation for nonvolatile memory |

| US11335417B1 (en) | 2020-10-28 | 2022-05-17 | SK Hynix Inc. | Read threshold optimization systems and methods using model-less regression |

| US20220276143A1 (en) * | 2021-02-26 | 2022-09-01 | Saudi Arabian Oil Company | Method and system for automatic evaluation of cutting element during wear test |

| US11875867B2 (en) * | 2021-12-08 | 2024-01-16 | Micron Technology, Inc. | Weighted wear leveling for improving uniformity |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20100118608A1 (en) | 2008-11-10 | 2010-05-13 | Samsung Electronics Co., Ltd. | Non-volatile memory device, memory card and system, and method determining read voltage in same |

| US20110246136A1 (en) | 2010-03-31 | 2011-10-06 | Haratsch Erich F | Methods and apparatus for computing a probability value of a received value in communication or storage systems |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4945187B2 (ja) | 2006-07-31 | 2012-06-06 | 株式会社東芝 | 半導体記憶装置 |

| US7903468B2 (en) | 2007-04-23 | 2011-03-08 | Ramot At Telaviv University Ltd. | Adaptive dynamic reading of flash memories |

| US7957187B2 (en) | 2008-05-09 | 2011-06-07 | Sandisk Corporation | Dynamic and adaptive optimization of read compare levels based on memory cell threshold voltage distribution |

-

2011

- 2011-02-24 KR KR1020110016643A patent/KR101818504B1/ko active IP Right Grant

-

2012

- 2012-02-24 US US13/404,625 patent/US8817545B2/en active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20100118608A1 (en) | 2008-11-10 | 2010-05-13 | Samsung Electronics Co., Ltd. | Non-volatile memory device, memory card and system, and method determining read voltage in same |

| US20110246136A1 (en) | 2010-03-31 | 2011-10-06 | Haratsch Erich F | Methods and apparatus for computing a probability value of a received value in communication or storage systems |

Also Published As

| Publication number | Publication date |

|---|---|

| US8817545B2 (en) | 2014-08-26 |

| KR20120097209A (ko) | 2012-09-03 |

| US20120221772A1 (en) | 2012-08-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101818504B1 (ko) | 반도체 메모리 장치 및 반도체 메모리 시스템 | |

| US9324420B2 (en) | Method of estimating deterioration state of memory device and related method of wear leveling | |

| US7911848B2 (en) | Memory device and memory data determination method | |

| KR101437102B1 (ko) | 메모리 장치 및 멀티 비트 셀 특성 추정 방법 | |

| US11587624B2 (en) | Coarse calibration based on signal and noise characteristics of memory cells collected in prior calibration operations | |

| US20120287711A1 (en) | Flash memory device and memory system including the same | |

| US11636908B2 (en) | Global-local read calibration | |

| JP5773367B2 (ja) | メモリ装置およびメモリプログラミング方法 | |

| US11468959B2 (en) | Detection of an incorrectly located read voltage | |

| KR20110004100A (ko) | 불휘발성 메모리 장치의 읽기 방법 및 그것을 포함하는 메모리 시스템 | |

| US11024401B1 (en) | Compute an optimized read voltage | |

| US11238953B2 (en) | Determine bit error count based on signal and noise characteristics centered at an optimized read voltage | |

| US11875846B2 (en) | Optimization of soft bit windows based on signal and noise characteristics of memory cells | |

| US11244729B1 (en) | Search for an optimized read voltage | |

| KR20150000358A (ko) | 메모리 시스템 및 이의 독출 방법 | |

| US11562801B2 (en) | Determine signal and noise characteristics centered at an optimized read voltage | |

| US20220084607A1 (en) | Read Disturb Mitigation based on Signal and Noise Characteristics of Memory Cells Collected for Read Calibration | |

| US11355203B2 (en) | Determine optimized read voltage via identification of distribution shape of signal and noise characteristics | |

| US11227666B1 (en) | Track charge loss based on signal and noise characteristics of memory cells collected in calibration operations | |

| KR101400691B1 (ko) | 메모리 장치 및 메모리 프로그래밍 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |