KR101482920B1 - 반도체 장치 - Google Patents

반도체 장치 Download PDFInfo

- Publication number

- KR101482920B1 KR101482920B1 KR20070072546A KR20070072546A KR101482920B1 KR 101482920 B1 KR101482920 B1 KR 101482920B1 KR 20070072546 A KR20070072546 A KR 20070072546A KR 20070072546 A KR20070072546 A KR 20070072546A KR 101482920 B1 KR101482920 B1 KR 101482920B1

- Authority

- KR

- South Korea

- Prior art keywords

- thin film

- film transistor

- wiring

- channel

- region

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 80

- 239000010409 thin film Substances 0.000 claims abstract description 104

- 238000000034 method Methods 0.000 claims description 87

- 239000012535 impurity Substances 0.000 claims description 48

- 230000015572 biosynthetic process Effects 0.000 claims description 40

- 239000000758 substrate Substances 0.000 claims description 38

- 239000010410 layer Substances 0.000 description 158

- 239000010408 film Substances 0.000 description 75

- 239000000463 material Substances 0.000 description 45

- 239000003990 capacitor Substances 0.000 description 28

- 239000011159 matrix material Substances 0.000 description 20

- 229920005989 resin Polymers 0.000 description 19

- 239000011347 resin Substances 0.000 description 19

- 239000011230 binding agent Substances 0.000 description 16

- 239000011229 interlayer Substances 0.000 description 13

- 239000003566 sealing material Substances 0.000 description 12

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 11

- 229910052581 Si3N4 Inorganic materials 0.000 description 10

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 10

- 229910052814 silicon oxide Inorganic materials 0.000 description 10

- 150000001875 compounds Chemical class 0.000 description 9

- 238000010304 firing Methods 0.000 description 9

- 238000004519 manufacturing process Methods 0.000 description 9

- 230000006866 deterioration Effects 0.000 description 8

- 229910010272 inorganic material Inorganic materials 0.000 description 8

- 239000012212 insulator Substances 0.000 description 8

- 239000011368 organic material Substances 0.000 description 8

- 239000002245 particle Substances 0.000 description 8

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 239000010949 copper Substances 0.000 description 7

- 239000011147 inorganic material Substances 0.000 description 7

- 150000002500 ions Chemical class 0.000 description 7

- 150000002894 organic compounds Chemical class 0.000 description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- 239000000460 chlorine Substances 0.000 description 6

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- 239000000565 sealant Substances 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 239000010703 silicon Substances 0.000 description 6

- 229910052782 aluminium Inorganic materials 0.000 description 5

- 229910002113 barium titanate Inorganic materials 0.000 description 5

- 239000002274 desiccant Substances 0.000 description 5

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 5

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 5

- 238000005240 physical vapour deposition Methods 0.000 description 5

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 5

- 230000001681 protective effect Effects 0.000 description 5

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 5

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 238000000137 annealing Methods 0.000 description 4

- 230000004888 barrier function Effects 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 239000013078 crystal Substances 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 238000005401 electroluminescence Methods 0.000 description 4

- 229910052733 gallium Inorganic materials 0.000 description 4

- 238000004020 luminiscence type Methods 0.000 description 4

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 4

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 4

- 238000005192 partition Methods 0.000 description 4

- -1 polyethylene Polymers 0.000 description 4

- 230000009467 reduction Effects 0.000 description 4

- 238000003746 solid phase reaction Methods 0.000 description 4

- 238000010532 solid phase synthesis reaction Methods 0.000 description 4

- 239000000243 solution Substances 0.000 description 4

- 229910001936 tantalum oxide Inorganic materials 0.000 description 4

- 229910001928 zirconium oxide Inorganic materials 0.000 description 4

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 3

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 3

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 3

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 3

- 239000005083 Zinc sulfide Substances 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 3

- 229910052801 chlorine Inorganic materials 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 239000003822 epoxy resin Substances 0.000 description 3

- 229910052731 fluorine Inorganic materials 0.000 description 3

- 239000011737 fluorine Substances 0.000 description 3

- 239000007791 liquid phase Substances 0.000 description 3

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 3

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 3

- 229910052760 oxygen Inorganic materials 0.000 description 3

- 239000001301 oxygen Substances 0.000 description 3

- 238000000059 patterning Methods 0.000 description 3

- 229920000647 polyepoxide Polymers 0.000 description 3

- 238000005215 recombination Methods 0.000 description 3

- 230000006798 recombination Effects 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 3

- 239000004332 silver Substances 0.000 description 3

- 125000001424 substituent group Chemical group 0.000 description 3

- 229910052984 zinc sulfide Inorganic materials 0.000 description 3

- WUPHOULIZUERAE-UHFFFAOYSA-N 3-(oxolan-2-yl)propanoic acid Chemical compound OC(=O)CCC1CCCO1 WUPHOULIZUERAE-UHFFFAOYSA-N 0.000 description 2

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 2

- 229910003781 PbTiO3 Inorganic materials 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 238000003877 atomic layer epitaxy Methods 0.000 description 2

- JRPBQTZRNDNNOP-UHFFFAOYSA-N barium titanate Chemical compound [Ba+2].[Ba+2].[O-][Ti]([O-])([O-])[O-] JRPBQTZRNDNNOP-UHFFFAOYSA-N 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 239000005380 borophosphosilicate glass Substances 0.000 description 2

- 229910052980 cadmium sulfide Inorganic materials 0.000 description 2

- 239000001506 calcium phosphate Substances 0.000 description 2

- 229910000389 calcium phosphate Inorganic materials 0.000 description 2

- 235000011010 calcium phosphates Nutrition 0.000 description 2

- 238000000975 co-precipitation Methods 0.000 description 2

- 239000003086 colorant Substances 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- 239000006185 dispersion Substances 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 125000001153 fluoro group Chemical group F* 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 239000001257 hydrogen Substances 0.000 description 2

- 229910052739 hydrogen Inorganic materials 0.000 description 2

- 230000006698 induction Effects 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 125000000962 organic group Chemical group 0.000 description 2

- 239000011236 particulate material Substances 0.000 description 2

- 230000035515 penetration Effects 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 239000005360 phosphosilicate glass Substances 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 239000000843 powder Substances 0.000 description 2

- LLHKCFNBLRBOGN-UHFFFAOYSA-N propylene glycol methyl ether acetate Chemical compound COCC(C)OC(C)=O LLHKCFNBLRBOGN-UHFFFAOYSA-N 0.000 description 2

- 238000000197 pyrolysis Methods 0.000 description 2

- 238000007789 sealing Methods 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- 238000001179 sorption measurement Methods 0.000 description 2

- 238000004528 spin coating Methods 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- VEALVRVVWBQVSL-UHFFFAOYSA-N strontium titanate Chemical compound [Sr+2].[O-][Ti]([O-])=O VEALVRVVWBQVSL-UHFFFAOYSA-N 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- QORWJWZARLRLPR-UHFFFAOYSA-H tricalcium bis(phosphate) Chemical compound [Ca+2].[Ca+2].[Ca+2].[O-]P([O-])([O-])=O.[O-]P([O-])([O-])=O QORWJWZARLRLPR-UHFFFAOYSA-H 0.000 description 2

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 2

- 229910021342 tungsten silicide Inorganic materials 0.000 description 2

- BQCIDUSAKPWEOX-UHFFFAOYSA-N 1,1-Difluoroethene Chemical compound FC(F)=C BQCIDUSAKPWEOX-UHFFFAOYSA-N 0.000 description 1

- KXJGSNRAQWDDJT-UHFFFAOYSA-N 1-acetyl-5-bromo-2h-indol-3-one Chemical compound BrC1=CC=C2N(C(=O)C)CC(=O)C2=C1 KXJGSNRAQWDDJT-UHFFFAOYSA-N 0.000 description 1

- ARXJGSRGQADJSQ-UHFFFAOYSA-N 1-methoxypropan-2-ol Chemical compound COCC(C)O ARXJGSRGQADJSQ-UHFFFAOYSA-N 0.000 description 1

- MFKRHJVUCZRDTF-UHFFFAOYSA-N 3-methoxy-3-methylbutan-1-ol Chemical compound COC(C)(C)CCO MFKRHJVUCZRDTF-UHFFFAOYSA-N 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- ODINCKMPIJJUCX-UHFFFAOYSA-N Calcium oxide Chemical compound [Ca]=O ODINCKMPIJJUCX-UHFFFAOYSA-N 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- 229910052684 Cerium Inorganic materials 0.000 description 1

- VEXZGXHMUGYJMC-UHFFFAOYSA-M Chloride anion Chemical compound [Cl-] VEXZGXHMUGYJMC-UHFFFAOYSA-M 0.000 description 1

- 229910021591 Copper(I) chloride Inorganic materials 0.000 description 1

- 229910052691 Erbium Inorganic materials 0.000 description 1

- 229910052693 Europium Inorganic materials 0.000 description 1

- 229910005228 Ga2S3 Inorganic materials 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- 229910003334 KNbO3 Inorganic materials 0.000 description 1

- 229910012463 LiTaO3 Inorganic materials 0.000 description 1

- 229920000877 Melamine resin Polymers 0.000 description 1

- 239000004640 Melamine resin Substances 0.000 description 1

- ZCQWOFVYLHDMMC-UHFFFAOYSA-N Oxazole Chemical compound C1=COC=N1 ZCQWOFVYLHDMMC-UHFFFAOYSA-N 0.000 description 1

- 229910020608 PbNbO3 Inorganic materials 0.000 description 1

- 239000004693 Polybenzimidazole Substances 0.000 description 1

- 239000004698 Polyethylene Substances 0.000 description 1

- 239000004743 Polypropylene Substances 0.000 description 1

- 239000004793 Polystyrene Substances 0.000 description 1

- 239000004372 Polyvinyl alcohol Substances 0.000 description 1

- 229910052777 Praseodymium Inorganic materials 0.000 description 1

- 229910052772 Samarium Inorganic materials 0.000 description 1

- 229910002808 Si–O–Si Inorganic materials 0.000 description 1

- UCKMPCXJQFINFW-UHFFFAOYSA-N Sulphide Chemical compound [S-2] UCKMPCXJQFINFW-UHFFFAOYSA-N 0.000 description 1

- 229910052771 Terbium Inorganic materials 0.000 description 1

- 229910052775 Thulium Inorganic materials 0.000 description 1

- 229910021536 Zeolite Inorganic materials 0.000 description 1

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 1

- 229910007709 ZnTe Inorganic materials 0.000 description 1

- VVJRYKIRUIWNGU-UHFFFAOYSA-N [Sr].[Sr] Chemical compound [Sr].[Sr] VVJRYKIRUIWNGU-UHFFFAOYSA-N 0.000 description 1

- 229910052946 acanthite Inorganic materials 0.000 description 1

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 1

- 150000001342 alkaline earth metals Chemical class 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 239000004760 aramid Substances 0.000 description 1

- 150000004945 aromatic hydrocarbons Chemical class 0.000 description 1

- 229920003235 aromatic polyamide Polymers 0.000 description 1

- NWAIGJYBQQYSPW-UHFFFAOYSA-N azanylidyneindigane Chemical compound [In]#N NWAIGJYBQQYSPW-UHFFFAOYSA-N 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 238000001354 calcination Methods 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- JJWKPURADFRFRB-UHFFFAOYSA-N carbonyl sulfide Chemical compound O=C=S JJWKPURADFRFRB-UHFFFAOYSA-N 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- GWXLDORMOJMVQZ-UHFFFAOYSA-N cerium Chemical compound [Ce] GWXLDORMOJMVQZ-UHFFFAOYSA-N 0.000 description 1

- 238000004040 coloring Methods 0.000 description 1

- 229920000547 conjugated polymer Polymers 0.000 description 1

- OXBLHERUFWYNTN-UHFFFAOYSA-M copper(I) chloride Chemical compound [Cu]Cl OXBLHERUFWYNTN-UHFFFAOYSA-M 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- NKZSPGSOXYXWQA-UHFFFAOYSA-N dioxido(oxo)titanium;lead(2+) Chemical compound [Pb+2].[O-][Ti]([O-])=O NKZSPGSOXYXWQA-UHFFFAOYSA-N 0.000 description 1

- HNPSIPDUKPIQMN-UHFFFAOYSA-N dioxosilane;oxo(oxoalumanyloxy)alumane Chemical compound O=[Si]=O.O=[Al]O[Al]=O HNPSIPDUKPIQMN-UHFFFAOYSA-N 0.000 description 1

- 238000007598 dipping method Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 238000005566 electron beam evaporation Methods 0.000 description 1

- UYAHIZSMUZPPFV-UHFFFAOYSA-N erbium Chemical compound [Er] UYAHIZSMUZPPFV-UHFFFAOYSA-N 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- OGPBJKLSAFTDLK-UHFFFAOYSA-N europium atom Chemical compound [Eu] OGPBJKLSAFTDLK-UHFFFAOYSA-N 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 239000000945 filler Substances 0.000 description 1

- 239000010419 fine particle Substances 0.000 description 1

- 238000004108 freeze drying Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- LNTHITQWFMADLM-UHFFFAOYSA-N gallic acid Chemical compound OC(=O)C1=CC(O)=C(O)C(O)=C1 LNTHITQWFMADLM-UHFFFAOYSA-N 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- CJNBYAVZURUTKZ-UHFFFAOYSA-N hafnium(iv) oxide Chemical compound O=[Hf]=O CJNBYAVZURUTKZ-UHFFFAOYSA-N 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 150000004678 hydrides Chemical class 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 150000002484 inorganic compounds Chemical class 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 238000005224 laser annealing Methods 0.000 description 1

- 238000005499 laser crystallization Methods 0.000 description 1

- 230000008774 maternal effect Effects 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 229910021645 metal ion Inorganic materials 0.000 description 1

- 239000000693 micelle Substances 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 229920003986 novolac Polymers 0.000 description 1

- 238000007645 offset printing Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 239000003960 organic solvent Substances 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 239000012466 permeate Substances 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- 239000000049 pigment Substances 0.000 description 1

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 1

- 229920002480 polybenzimidazole Polymers 0.000 description 1

- 229920002577 polybenzoxazole Polymers 0.000 description 1

- 229920000573 polyethylene Polymers 0.000 description 1

- 239000002861 polymer material Substances 0.000 description 1

- 229920001155 polypropylene Polymers 0.000 description 1

- 229920002223 polystyrene Polymers 0.000 description 1

- 229920002451 polyvinyl alcohol Polymers 0.000 description 1

- PUDIUYLPXJFUGB-UHFFFAOYSA-N praseodymium atom Chemical compound [Pr] PUDIUYLPXJFUGB-UHFFFAOYSA-N 0.000 description 1

- 239000002243 precursor Substances 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 239000000047 product Substances 0.000 description 1

- 238000010298 pulverizing process Methods 0.000 description 1

- 238000000746 purification Methods 0.000 description 1

- KZUNJOHGWZRPMI-UHFFFAOYSA-N samarium atom Chemical compound [Sm] KZUNJOHGWZRPMI-UHFFFAOYSA-N 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- SBIBMFFZSBJNJF-UHFFFAOYSA-N selenium;zinc Chemical compound [Se]=[Zn] SBIBMFFZSBJNJF-UHFFFAOYSA-N 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 229910002027 silica gel Inorganic materials 0.000 description 1

- 239000000741 silica gel Substances 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- HKZLPVFGJNLROG-UHFFFAOYSA-M silver monochloride Chemical compound [Cl-].[Ag+] HKZLPVFGJNLROG-UHFFFAOYSA-M 0.000 description 1

- FSJWWSXPIWGYKC-UHFFFAOYSA-M silver;silver;sulfanide Chemical compound [SH-].[Ag].[Ag+] FSJWWSXPIWGYKC-UHFFFAOYSA-M 0.000 description 1

- 238000005245 sintering Methods 0.000 description 1

- 238000005118 spray pyrolysis Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 238000000859 sublimation Methods 0.000 description 1

- 230000008022 sublimation Effects 0.000 description 1

- 150000004763 sulfides Chemical class 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GZCRRIHWUXGPOV-UHFFFAOYSA-N terbium atom Chemical compound [Tb] GZCRRIHWUXGPOV-UHFFFAOYSA-N 0.000 description 1

- 229920002803 thermoplastic polyurethane Polymers 0.000 description 1

- FRNOGLGSGLTDKL-UHFFFAOYSA-N thulium atom Chemical compound [Tm] FRNOGLGSGLTDKL-UHFFFAOYSA-N 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 238000012795 verification Methods 0.000 description 1

- 125000000391 vinyl group Chemical group [H]C([*])=C([H])[H] 0.000 description 1

- 229920002554 vinyl polymer Polymers 0.000 description 1

- 238000004804 winding Methods 0.000 description 1

- RUQSMSKTBIPRRA-UHFFFAOYSA-N yttrium Chemical compound [Y].[Y] RUQSMSKTBIPRRA-UHFFFAOYSA-N 0.000 description 1

- 239000010457 zeolite Substances 0.000 description 1

- DRDVZXDWVBGGMH-UHFFFAOYSA-N zinc;sulfide Chemical compound [S-2].[Zn+2] DRDVZXDWVBGGMH-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09F—DISPLAYING; ADVERTISING; SIGNS; LABELS OR NAME-PLATES; SEALS

- G09F9/00—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements

- G09F9/30—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements in which the desired character or characters are formed by combining individual elements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09F—DISPLAYING; ADVERTISING; SIGNS; LABELS OR NAME-PLATES; SEALS

- G09F9/00—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements

- G09F9/30—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements in which the desired character or characters are formed by combining individual elements

- G09F9/33—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements in which the desired character or characters are formed by combining individual elements being semiconductor devices, e.g. diodes

- G09F9/335—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements in which the desired character or characters are formed by combining individual elements being semiconductor devices, e.g. diodes being organic light emitting diodes [OLED]

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09F—DISPLAYING; ADVERTISING; SIGNS; LABELS OR NAME-PLATES; SEALS

- G09F9/00—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements

- G09F9/30—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements in which the desired character or characters are formed by combining individual elements

- G09F9/35—Indicating arrangements for variable information in which the information is built-up on a support by selection or combination of individual elements in which the desired character or characters are formed by combining individual elements being liquid crystals

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1251—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs comprising TFTs having a different architecture, e.g. top- and bottom gate TFTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/15—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components with at least one potential-jump barrier or surface barrier specially adapted for light emission

- H01L27/153—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components with at least one potential-jump barrier or surface barrier specially adapted for light emission in a repetitive configuration, e.g. LED bars

- H01L27/156—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components with at least one potential-jump barrier or surface barrier specially adapted for light emission in a repetitive configuration, e.g. LED bars two-dimensional arrays

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/78654—Monocrystalline silicon transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/7866—Non-monocrystalline silicon transistors

- H01L29/78663—Amorphous silicon transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/7866—Non-monocrystalline silicon transistors

- H01L29/78672—Polycrystalline or microcrystalline silicon transistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1213—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1216—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/124—Insulating layers formed between TFT elements and OLED elements

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

Abstract

본 발명은, 개구율이 높은 표시장치 또는 소자의 면적이 큰 반도체 장치를 제공하는 것을 과제로 한다. 인접하는 화소전극(또는 소자의 전극)의 사이에 형성된 배선과의 아래쪽에 멀티 게이트 구조의 TFT의 채널형성영역을 형성한다. 그리고, 복수의 채널형성영역의 채널폭의 방향을 상기 화소전극의 형상에 있어서의 길이방향과 평행한 방향으로 설정한다. 또한, 채널폭의 길이를 채널 길이의 길이보다 길게 하는 것으로써, 채널형성영역의 면적을 크게 한다.

표시장치, 반도체 장치, 박막 트랜지스터, 채널 폭, 채널 폭 방향

Description

본 발명은, 액티브 매트릭스형의 표시장치, 및 매트릭스 형상으로 소자가 배치된 반도체 장치에 관한 것이다.

종래로부터, 화상표시장치로서, 액정표시장치, 전계발광(Electro Luminescence: 이하, EL라고 부른다)표시장치 등이 알려져 있다. 이들의 표시장치의 형식으로서는, 패시브 매트릭스형과 액티브 매트릭스형이 있다. 그리고, 액티브 매트릭스형 표시장치는, 화소수가 증가한 경우에도, 고속동작을 할 수 있다고 하는 특징을 가진다.

액티브 매트릭스형 표시장치는, TFT, 용량소자, 배선, 화소전극 등을 동일의 기판 위에 형성하기 때문에, 개구율이 감소하기 쉽다. 그렇기 때문에, 이들의 재료, 형상, 수, 또는 배치 등의 설계를 궁리함으로써, 개구율을 높이는 시도를 한다. 예를 들면, 특허문헌 1에 있어서는, 비유전율이 높은 산화탄탈을 용량소자의 유전체로서 이용하는 것으로써, 용량소자의 소면적화를 도모하는 방법이 개시된다.

[특허문헌 1]특개평 11-312808호 공보

한편, 개구율을 높이기 위해, 비유전율이 높은 재료를 용량소자에 사용하는 방법은, 공정수의 증가에 관련된다는 문제가 있다.

여기서, 공정수를 증가시키지 않고 개구율을 높이기 위해서는, 개구부의 면적을 크게 하면 좋다. 그러나, 개구부의 면적을 크게 하기 위하여 배선의 사이에 개구부를 형성하도록 하면, 개구부의 형상은 복잡한 형상이 된다. 그리고, EL 표시장치에 있어서, 개구부의 형상을 복잡한 형상으로 하면, 개구부의 에지(단부)의 길이가 크게 되기 때문에, EL 발광부의 쉬링크(shrink)가 촉진된다고 하는 문제가 생긴다.

여기서, EL 발광부의 쉬링크는, EL층이 물리적으로 수축하는 것이 아니라, EL 소자의 유효면적(EL층이 발광하는 부분의 면적)이, 단부로부터 서서히 수축하는 상태를 의미한다.

또한, 표시장치 이외의 반도체 장치(예를 들면, DRAM 등)에 있어서도, 트랜지스터와 접속되는 소자의 면적을 크게 하는 것이 바람직하다.

그래서, 본 발명은, 개구율이 높은 표시장치(또는, 소자의 면적이 큰 반도체 장치)를 제공하는 것을 과제로 한다.

본 명세서에 있어서, TFT의 채널형성영역은, 게이트 전극의 아래에 게이트 절연막을 개재하여 배치된 반도체 영역을 의미한다. 또한, 채널 길이는, 채널형성 영역에 있어서의 캐리어가 흐르는 방향의 길이를 의미한다. 그리고, 채널 폭은, 채널 길이 방향에 대해서 수직방향의 채널형성영역의 길이를 의미한다.

또한, 멀티 게이트 구조의 TFT의 경우, 채널 길이 및 채널 폭은, 하나의 채널형성영역마다의 치수를 의미한다.

또한, 멀티 게이트 구조는, TFT 하나에 복수의 채널형성영역을 형성한 구조이다. 한편, 싱글 게이트 구조는, TFT 하나에 채널형성영역 하나를 형성한 구조이다.

그리고, 본 발명의 표시장치는, 인접하는 화소전극의 사이에 형성된 배선과, 박막 트랜지스터를 가지고, 상기 박막 트랜지스터의 채널형성영역은, 상기 배선의 아래쪽에 형성되고, 상기 채널형성영역은 상기 배선과 겹치는 위치에 형성되고, 상기 채널형성영역의 채널 폭의 방향은, 상기 배선에 있어서의 전류가 흐르는 방향과 평행한 방향인 것을 특징으로 한다.

본 발명의 표시장치는, 인접하는 화소전극의 사이에 형성된 배선과, 복수의 채널형성영역을 가지는 박막 트랜지스터를 가지고, 상기 복수의 채널형성영역은, 상기 배선의 아래쪽에 형성되고, 상기 복수의 채널형성영역은 상기 배선과 겹치는 위치에 형성되고, 상기 복수의 채널형성영역의 채널 폭의 방향은, 상기 배선에 있어서의 전류의 흐르는 방향과 평행한 방향인 것을 특징으로 한다.

본 발명의 표시장치는, 인접하는 화소전극의 사이에 형성된 배선과, 박막 트랜지스터를 가지고, 상기 박막 트랜지스터의 채널형성영역은, 상기 배선의 아래쪽에 형성되고, 상기 채널형성영역은 상기 배선과 겹치는 위치에 형성되고, 상기 채 널형성영역의 채널폭의 방향은, 상기 배선의 형상에 있어서의 길이방향과 평행한 방향인 것을 특징으로 한다.

본 발명의 표시장치는, 인접하는 화소전극의 사이에 형성된 배선과, 복수의 채널형성영역을 가지는 박막 트랜지스터를 가지고, 상기 복수의 채널형성영역은, 상기 배선의 아래쪽에 형성되고, 상기 복수의 채널형성영역은 상기 배선과 겹치는 위치에 형성되고, 상기 복수의 채널형성영역의 채널 폭의 방향은, 상기 배선의 형상에 있어서의 길이방향과 평행한 방향인 것을 특징으로 한다.

본 발명의 표시장치는, 인접하는 화소전극의 사이에 형성된 배선과, 박막 트랜지스터를 가지고, 상기 박막 트랜지스터의 채널형성영역은, 상기 배선의 아래쪽에 형성되고, 상기 채널형성영역은 상기 배선과 겹치는 위치에 형성되고, 상기 채널형성영역의 채널 폭의 방향은, 상기 화소전극의 형상에 있어서의 길이방향과 평행한 방향인 것을 특징으로 한다.

본 발명의 표시장치는, 인접하는 화소전극의 사이에 형성된 배선과, 복수의 채널형성영역을 가지는 박막 트랜지스터를 가지고, 상기 복수의 채널형성영역은, 상기 배선의 아래쪽에 형성되고, 상기 복수의 채널형성영역의 채널 폭의 방향은, 상기 화소전극의 형상에 있어서의 길이방향과 평행한 방향인 것을 특징으로 한다.

본 발명의 표시장치에 있어서, 상기 박막 트랜지스터는, 선형 영역에서 동작하는 것을 특징으로 한다.

트랜지스터의 게이트와 소스의 사이의 전압을 Vgs, 트랜지스터의 소스와 드레인의 사이의 전압을 Vds, 트랜지스터의 임계 값 전압을 Vth로 설정한다. 이 경 우, 선형 영역은, |Vgs - Vth| > |Vds|의 관계식이 성립하는 범위를 의미한다.

즉, 상기 박막 트랜지스터는, 게이트와 소스의 사이의 전압(Vgs)이, 소스와 드레인의 사이의 전압(Vds)보다 임계 값 전압(Vth)분 이상 큰 범위로 동작하는 것을 특징으로 한다.

본 발명의 표시장치에 있어서, 상기 채널형성영역의 채널 폭의 길이는, 상기 채널형성영역의 채널 길이의 길이 보다 긴 것을 특징으로 한다.

본 발명의 표시장치에 있어서, 상기 채널형성영역들을 접속하는 불순물 영역의 형상에 있어서의 길이방향은, 채널 폭의 방향과 평행한 방향인 것을 특징으로 한다.

본 발명의 표시장치에 있어서, 상기 채널형성영역은, 비정질 반도체 또는 다결정 반도체인 것을 특징으로 한다.

본 발명의 표시장치에 있어서, 상기 채널형성영역은, 단결정인 것을 특징으로 한다.

본 발명의 표시장치에 있어서, 상기 박막 트랜지스터는, 섬형상 반도체층과, 게이트 절연막과, 게이트 전극을 가지고, 상기 섬형상 반도체층은, 상기 복수의 채널형성영역과, 복수의 불순물 영역을 가지고, 상기 복수의 채널형성영역 위에는, 게이트 절연막을 개재하여 게이트 전극이 형성되는 것을 특징으로 한다.

본 발명의 표시장치에 있어서, 상기 배선은, 층간 절연막을 개재하여 상기 게이트 전극 위에 형성되는 것을 특징으로 한다.

본 발명의 표시장치에 있어서, 상기 섬형상 반도체층과 상기 섬형상 반도체 층 위의 상기 게이트 절연막과, 상기 게이트 절연막 위의 상기 게이트 전극으로 되는 제 1 용량과, 상기 게이트 전극과, 상기 게이트 전극 위의 층간 절연막과, 상기 층간 절연막 위의 상기 배선으로 되는 제 2 용량이 형성되어 있는 것을 특징으로 한다.

본 발명의 표시장치에 있어서, 상기 게이트 전극의 형상에 있어서의 길이방향은, 상기 채널 폭의 방향인 것을 특징으로 한다.

본 발명의 표시장치에 있어서, 상기 배선은 상기 화소전극의 단부를 덮어 형성된 격벽(절연물)의 아래쪽에 형성되는 것을 특징으로 한다.

본 발명의 표시장치에 있어서, 상기 박막 트랜지스터의 소스 단자(영역) 또는 드레인 단자(영역)의 한쪽은, 상기 인접하는 화소전극의 한쪽에 접속되는 것을 특징으로 한다.

본 발명의 표시장치에 있어서, 상기 박막 트랜지스터의 소스 단자(영역) 또는 드레인 단자(영역)의 한쪽은, 상기 인접하는 화소전극의 한쪽에 접속되는 것을 특징으로 한다.

본 발명의 반도체 장치는, 인접하는 전극의 사이에 형성된 배선과, 박막 트랜지스터를 가지고, 상기 박막 트랜지스터의 채널형성영역은, 상기 배선의 아래쪽에 형성되고, 상기 채널형성영역은 상기 배선과 겹치는 위치에 형성되고, 상기 채널형성영역의 채널 폭의 방향은, 상기 배선에 있어서의 전류의 흐르는 방향(또는, 상기 배선의 형상에 있어서의 길이방향)과 평행한 방향인 것을 특징으로 한다.

본 발명의 반도체 장치는, 인접하는 전극의 사이에 형성된 배선과, 박막 트 랜지스터를 가지고, 상기 박막 트랜지스터의 채널형성영역은, 상기 배선의 아래쪽에 형성되고, 상기 채널형성영역은 상기 배선과 겹치는 위치에 형성되고, 상기 채널형성영역의 채널 폭의 방향은, 상기 전극의 형상에 있어서의 길이방향과 평행한 방향인 것을 특징으로 한다.

본 발명의 반도체 장치는, 인접하는 소자의 사이에 형성된 배선과, 박막 트랜지스터를 가지고, 상기 박막 트랜지스터의 채널형성영역은, 상기 배선의 아래쪽에 형성되고, 상기 채널형성영역은 상기 배선과 겹치는 위치에 형성되고, 상기 채널형성영역의 채널 폭의 방향은, 상기 배선에 있어서의 전류의 흐르는 방향(또는, 상기 배선의 형상에 있어서의 길이방향)과 평행한 방향인 것을 특징으로 한다.

본 발명의 반도체 장치는, 인접하는 소자의 사이에 형성된 배선과, 박막 트랜지스터를 가지고, 상기 박막 트랜지스터의 채널형성영역은, 상기 배선의 아래쪽에 형성되고, 상기 채널형성영역은 상기 배선과 겹치는 위치에 형성되고, 상기 채널형성영역의 채널 폭의 방향은, 상기 소자의 형상에 있어서의 길이방향과 평행한 방향인 것을 특징으로 한다.

본 발명의 반도체 장치에 있어서, 상기 채널형성영역의 채널 폭의 길이는, 상기 채널형성영역의 채널 길이의 길이보다 긴 것을 특징으로 한다.

본 발명에 의하여, 개구율이 높은 표시장치(또는 소자의 면적이 큰 반도체 장치)를 실현할 수 있다.

또한, 개구율을 높이기 위해서, 화소전극(또는, 소자의 전극)의 형상을 복잡 한 형상으로 할 필요도 없다.

또한, 개구율을 높게 하는 것으로써, 소자에 대한 전류밀도가 낮게 되기 때문에, 소자의 장수명화가 가능하게 된다.

이하에, 본 발명의 실시형태를 도면에 의거하여 설명한다. 그러나, 본 발명은 많은 다른 모양으로 실시하는 것이 가능하고, 본 발명의 형태 및 상세한 사항은 본 발명의 취지 및 범위에서 벗어남이 없이 다양하게 변경될 수 있다는 것은 당업자라면 용이하게 이해할 수 있다. 따라서, 본 발명이 하기 실시형태의 기재 내용에 한정하여 해석되는 것은 아니다.

또한, 이하의 실시형태 1 내지 실시형태 11은, 적절히 조합할 수 있다.

(실시형태 1)

본 실시형태에서는, 본 발명의 표시장치의 화소구성과 레이아웃에 대해서 설명한다. 또한, 여기서는, 2개의 TFT로 구성되는 화소에 대해서 설명한다.

우선, 도 3을 사용하여 본 발명의 표시장치의 화소구성에 대해서 설명한다. 화소는, 화소전극에 접속된 TFT(구동용 TFT(301))와, 용량소자(300)와, 스위칭용 TFT(302)와, 표시소자(303)와, 주사선(305)과, 신호선(304)과, 전원공급선(306)을 가진다. 또한, 구동용 TFT(301)와 스위칭용 TFT(302)는, 2개의 채널형성영역을 가지는 더블 게이트 구조이다.

또한, 구동용 TFT(301)는 싱글 게이트 구조라도 좋고, 3개 이상의 채널형성영역을 가지는 멀티 게이트 구조라도 좋다.

스위칭용 TFT(302)의 소스 단자 또는 드레인 단자의 한 쪽은, 신호선(304)에 접속된다.

스위칭용 TFT(302)의 게이트 단자는 주사선(305)에 접속된다.

스위칭용 TFT(302)의 소스 단자 또는 드레인 단자의 다른 쪽은 구동용 TFT(301)의 게이트 단자 및 용량소자의 전극의 한 쪽에 전기적으로 접속된다.

구동용 TFT(301)의 소스 단자 또는 드레인 단자의 한 쪽은 전원공급선(306)에 접속된다.

구동용 TFT(301)의 소스 단자 또는 드레인 단자의 다른 쪽은 표시소자(303)에 접속된다.

구동용 TFT(301)의 게이트 단자는 용량소자의 전극의 한 쪽 및 스위칭용 TFT(302)의 소스 단자 또는 드레인 단자의 다른 쪽에 접속된다.

용량소자(300)의 다른 쪽의 단자는, 전원공급선(306)에 전기적으로 접속된다.

용량소자(300)의 한 쪽의 단자는, 구동용 TFT의 게이트 단자 및 스위칭용 TFT(302)의 소스 단자 또는 드레인 단자의 다른 쪽과 전기적으로 접속된다.

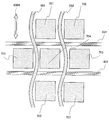

다음, 화소부의 레이아웃에 대해서 도 1 내지 도 2를 사용하여 설명한다. 도 2는 도 1에 대응하는 상면도이며, 제 1 반도체층(101), 제 2 반도체층(102)과 게이트 배선(105), 게이트 전극(100)을 형성한 단계의 도면이다.

도 1 내지 도 2와 도 3의 대응관계에 대해서 설명한다.

파선부(6001)로 둘러싸인 부분이 구동용 TFT(301)에 대응한다.

파선부(6011)로 둘러싸인 부분이 스위칭용 TFT(302)에 대응한다.

파선부(6012)로 둘러싸인 부분이 용량소자(300) 대응한다.

화소전극(107)이 표시소자(303)의 화소전극에 대응한다.

신호선(104)이 신호선(304)에 대응한다.

전원공급선(106)이 전원공급선(306)에 대응한다.

도 1에 있어서, 제 1 반도체층(101)은, 스위칭용 TFT의 섬형상 반도체층이다. 게이트 배선(105)과 겹치는 영역이 채널형성영역, 신호선(104)과 접속하는 영역이 소스 단자(또는 드레인 단자), 콘택트 홀을 통하여 접속전극(103)과 접속하는 영역이 드레인 단자(또는 소스 단자)이다. 또한, 스위칭용 TFT는, 2개의 채널형성영역을 가지는 더블 게이트 구조이다.

또한, 스위칭용 TFT는, 싱글 게이트 구조라도 좋고, 3개 이상의 채널형성영역을 가지는 멀티 게이트 구조라도 좋다.

또한, 제 2 반도체층(102)은 표시소자를 구동하는 구동용 TFT(301)의 섬형상 반도체층이다. 그리고, 게이트 전극(100)과 겹치는 영역이 채널형성영역이다. 그리고, 구동용 TFT(301)의 게이트 전극은, 콘택트 홀을 통하여 접속전극(103)과 접속한다. 또한, 구동용 TFT(301)의 소스 단자(또는 드레인 단자)와 전원공급선(106)이 콘택트 홀을 통하여 접속된다. 구동용 TFT(301)의 드레인 단자(또는 소스 단자)와 접속전극(108)이 콘택트 홀을 통하여 접속된다. 또한, 상기 접속전 극(108)과 접하여 화소전극(107)이 형성된다.

또한, 제 2 반도체층(102) 중, 게이트 전극(100)과 게이트 절연막을 개재하여 겹치는 채널형성영역의 상방에는, 전원공급선(106)이 배치된다. 이 게이트 전극(100)과 전원공급선(106)의 사이에서 형성되는 용량은, 표시소자의 유지용량으로서 사용할 수 있다.

게이트 전극(100)과 전원공급선(106)의 사이에는, 층간절연막이 끼워져 있다.

또한, 게이트 전극(100)이 용량소자의 전극의 한 쪽으로 되고, 전원공급선 중의 게이트 전극과 겹치는 부분이 용량소자의 전극의 다른 쪽이 된다.

또한, 표시소자의 전극의 단락을 방지하기 위해서, 발광 에어리어 이외의 영역을 격벽(절연물)으로 덮는다. 이웃하여 인접하는 좌우의 화소간에 형성되는 격벽의 폭은, 예를 들면, 20um 내지 25um 정도이다. 본 실시형태에 있어서, 폭이 20um의 격벽의 아래(즉, 인접하는 화소전극의 사이)에 신호선(104)과 전원공급선(106)을 배치한다.

또한, 본 실시형태에 있어서는, 전원공급선(106)의 길이방향과 화소전극의 형상에 있어서의 길이방향(화소전극의 길이방향)이 평행으로 되도록 배치한다. 또한, 전원공급선(106)의 아래쪽에 구동용 TFT를 겹치도록 배치한다. 그리고, 채널 폭의 방향을 상기 길이방향과 평행하게 배치한다.

그러나, 본 발명은, 항상 화소전극의 형상에 있어서의 길이방향과 평행하게 전원공급선(106)을 배치하고, 구동용 TFT(301)를 전원공급선(106)의 아래쪽에 배치 할 필요는 없다.

따라서, 신호선(104)을 화소전극의 형상에 있어서의 길이방향과 평행하게 배치한 경우는, 신호선(104)의 아래쪽에 겹치도록 구동용 TFT(301)를 배치하여도 좋다.

또한, 화소전극의 형상이, 정방형, 대략 정방형(예를 들면, 정방형의 모서리에 절결부를 형성한 형상, 또는, 정방형의 모서리가 둥글게 되는 형상(모서리 모두가 둥글게 될 필요는 없다. 일부의 모서리만 둥글게 되어도 좋다.) 등), 원형 등과 같이, 길이방향이 존재하지 않는 경우는, 전원공급선(106) 또는 신호선(104)의 아래 어느 쪽에 구동용 TFT(301)를 배치하여도 문제는 없다.

또한, 화소전극의 형상에는, 장방형, 또는 대략 장방형(예를 들면, 장방형의 모서리에 절결부를 형성한 형상, 또는, 장방형의 모서리의 형상이 둥글게 되는 형상(모서리 모두가 둥글게 될 필요는 없다. 일부의 모서리만 둥글게 되어도 좋다.), 타원형, 다각형, 대략 다각형(예를 들면, 다각형의 모서리에 절결부를 형성한 형상, 또는, 다각형의 모서리의 형상이 둥글게 되는 형상(모서리 모두가 둥글게 될 필요는 없다. 일부의 모서리만 둥글게 되어도 좋다.) 등의 여러가지 형상을 고려할 수 있다. 또한, 화소전극의 형상은, 이들 예시된 형상으로 한정되지 않다. 또한, 화소전극의 형상이 장방형 또는 대략 장방형의 경우, 배선을 격자형상으로 배치하기 쉽기 때문에, 레이아웃의 설계를 하기 쉬워 바람직하다.

또한, 화소전극의 크기가 화소마다 달라도 좋다. 또한, 화소전극의 형상이 화소마다 달라도 좋다.

또한, 요구되는 채널 폭의 길이가 화소전극의 형상에 있어서의 단척방향의 길이보다 짧은 경우는, 상기 단척방향과 평행하게 배치된 배선의 아래쪽에 겹치도록 구동용 TFT(301)를 배치하여도 좋다.

또한, 전원공급선(106)의 일부가, 화소전극의 상방 또는 아래쪽에 배치되어도 좋다. 이러한 배치로 할 경우, 구동용 TFT(301)의 게이트 전극을, 전원공급선(106)의 일부와 겹치도록 구동용 TFT(301)를 배치한다.

또한, 구동용 TFT(301)의 채널 폭의 방향은, 배선의 형상에 있어서의 길이방향(배선의 길이방향)과 평행한 방향으로 한다. 따라서, 채널 폭의 길이를 길게 할 수 있기 때문이다. 또한, 배선은 인접하는 화소전극의 사이에 배치하기 위해, 배선의 형상에 있어서의 길이방향(배선의 길이방향)은, 화소전극의 길이방향 또는 단척방향과 평행한 방향으로 하는 것으로써, 개구율을 높일 수 있다.

또한, 보통 배선의 길이방향에 전류를 흐르기 때문에, 채널 폭의 방향은, 채널형성영역의 상방에 배치된 배선에 있어서, 전류가 흐르는 방향과 평행한 방향이라고도 말할 수 있다.

또한, 본 실시형태에서는, 선형 영역에서 동작할 경우이다. 채널 길이를 L, 채널 폭을 W로 하면, 구동용 TFT는 L< W의 더블 게이트 구조로 한다. 여기서는, 구동용 TFT는 L = 7um, W = 20um 정도의 더블 게이트 구조로 한다. 그리고, 화소의 레이아웃을 할 때에, 폭 20um의 격벽의 아래에 배선을 배치하고, 배선의 아래에 구동용 TFT를 배치하는 것으로써, 구동용 TFT의 사이즈가 크게 되어도 개구율을 높일 수 있다.

본 실시형태에서는, 반도체층을 게이트 전극(100)에 대해서 ㄷ자형으로 꾸부리도록 패터닝한다(도 1 내지 도 2의 파선부(6001)). 따라서, 채널 폭의 방향을 화소전극의 형상에 있어서의 길이방향과 평행하게 배치할 수 있다(도 1 내지 도 2의 화살표(7001)).

또한, 채널형성영역들을 접속하는 불순물 영역의 형상에 있어서의 길이방향을, 채널 폭의 방향과 평행한 방향으로 하는 것이 바람직하다. 따라서, 화소전극의 사이의 좁은 스페이스(인접하는 화소전극의 사이의 스페이스)에 가능한 한 큰 사이즈의 TFT를 배치할 수 있기 때문에, 개구율의 증가를 기대할 수 있기 때문이다. 또한, 상기 불순물 영역에 있어서는, 상기 불순물 영역의 형상에 있어서의 길이방향에 전류가 흐르기 때문에, 상기 불순물 영역의 저항 값을 높일 수 있다. 따라서, 오프전류를 저감할 수 있다.

다만, 본 발명은, 채널 폭의 방향이 화소전극의 길이방향과 수직방향으로 되면, 상기 길이방향의 길이분까지 채널 폭을 증가시킬 수 있다. 따라서, TFT의 섬형상 반도체층의 형상은, 본 실시형태와 같이, ㄷ자형 형상으로 한정되지 않는다.

또한, 용량소자(300)는, 제 2 반도체층(102)과 게이트 전극(100)과, 제 2 반도체층(102)과 게이트 전극(100)의 사이에 형성되는 게이트 절연막(제 1 유지용량) 및 게이트 전극(100)과 전원공급선(106)과, 게이트 전극(100)과 전원공급선(106)의 사이에 형성되는 층간절연막(제 2 유지용량)으로 형성할 수 있다.

그리고, 이 경우, 파선부(6012)에 있어서, 게이트 전극(100)과, 제 2 반도체층(102)과, 게이트 전극(1000)과 제 2 반도체층(102)의 사이에 형성된 게이트 절연 막으로 유지용량을 형성한다. 따라서, 파선부(6012)에 있어서의 게이트 전극의 면적을 크게 하는 것으로써, 유지용량도 크게 할 수 있다.

상기 구성에 따라, 화소전극간의 좁은 스페이스(인접하는 화소전극의 사이의 스페이스)에 가능한 한 큰 사이즈의 TFT(특히, 채널 폭이 큰 사이즈의 TFT)를 배치할 수 있다. 따라서, 개구율의 증가가 가능하게 된다.

또한, TFT는 매우 작은 사이즈이기 때문에, 게이트 절연막의 막 두께의 변동 또는 막질의 변동, 이온 도핑 처리시의 주입 도즈량의 변동 등에 따라, 전기적 특성이 변동하기 쉬운 문제가 있다.

특히, TFT의 반도체로서 비정질규소, 미결정규소, 또는 다결정규소를 사용할 때는, 반도체의 결정성에 기인한 TFT의 특성(예를 들면, 온 전류, 오프 전류, 임계 값 전압, 이동도 등)의 변동이 생겨버린다. 특히, 화소에 접속된 TFT의 특성이 변동한 경우, 화소에 공급되는 전류(또는 전압)가 변동하기 때문에, 표시장치의 시인성이 악화하여 버리는 문제가 있다.

그래서, 상기 문제를 해결하기 위해서 멀티 게이트 구조를 채용하는 방법이 있지만, 멀티 게이트 구조의 TFT는, 싱글 게이트 구조의 TFT와 비교하면, 면적이 크게 된다. 따라서, TFT의 전기적 특성의 변동을 저감하기 위하여 멀티 게이트 구조의 TFT를 채용하면 개구율이 저하해 버린다. 그러나, 본 발명의 구성을 적용하는 것으로써, TFT의 특성의 변동저감과, 개구율의 상승의 양쪽을 실현할 수 있다.

여기서, 본 실시형태에서는, 구동용 TFT를 선형 영역에서 동작시키는, 이른바 정전압 구동방식의 일례를 설명한다. 그래서, 정전압 구동방식에 대해서 이하 설명한다.

TFT는, 포화영역에서 동작시키는 경우와 선형 영역에서 동작시키는 경우가 있다. 트랜지스터의 게이트와 소스 간의 전압을 Vgs, 트랜지스터의 소스와 드레인 간의 전압을 Vds, 트랜지스터의 임계 값 전압을 Vth로 한다. 이 경우, 포화영역은, |Vgs-Vth| < |Vds|의 관계식이 성립하는 범위를 의미한다. 한편, 선형 영역은, |Vgs - Vth| > |Vds|의 관계식이 성립하는 범위를 의미한다.

그리고, EL 소자의 화소전극에 접속된 TFT(이하, 「구동용 TFT」라고 한다)를 포화영역에서 동작시키는 것으로써, 표시소자에 일정의 전류를 흘리는 방식을 정전류 구동방식이라고 한다.

정전류 구동방식은, 일정의 전류를 EL 소자에 계속해서 흘릴 수 있기 때문에, 표시소자의 열화에 의한 변동을 저감할 수 있다. 그러나, 정전류 구동방식은, 구동용 TFT가 열화하면, 상기 구동용 TFT에 흐르는 전류도 감소한다. 따라서, TFT의 변동은, 표시소자의 휘도의 변동에 영향을 끼치기 쉽다.

한편, 구동용 TFT를 선형 영역에서 동작시키는 것으로써, 일정의 전압을 EL 소자에 인가하는 방식을 정전압 방식이라고 한다.

정전압 구동방식은, 선형상 영역에서 동작하기 때문에, 소스와 드레인의 사이의 전압을 표시소자의 양쪽의 전극간의 전압과 비교해서 낮게 할 수 있다. 그렇기 때문에, 구동용 TFT의 변동의 EL 소자에 흐르는 전류에 대한 영향을 저감할 수 있다. 따라서, TFT의 열화의 변동은, 표시소자의 휘도의 변동에 영향을 끼치기 어렵다.

그러나, 구동용 TFT를 선형 영역에서 동작시켜도, TFT의 반도체층으로서 비정질 규소, 미결정 규소, 다결정 규소 등을 사용한 경우, 기판 면내에 있어서의 결정성의 변동의 영향을 무시할 수 없다.

그래서, 구동용 TFT의 변동을 억제하기 위해서, 구동용 TFT의 채널형성영역의 면적을 크게 하는 것이 바람직하다. 즉, 채널 길이와 채널 폭을 크게 하는 것이 바람직하다.

또한, 채널 폭이 길수록, 소스와 드레인간의 전압을 낮게 할 수 있다. 또한, 채널 길이가 짧을수록, 소스와 드레인간의 전압을 낮게 할 수 있다. 따라서, 채널 폭은, 채널 길이보다 긴 것이 바람직하다.

따라서, TFT를 선형 영역에서 동작시킬 경우, 구동용 TFT의 채널형성영역의 면적을 증대시키기 위해서는, 채널 폭을 길게 하는 것이 바람직하다.

여기서는, 일반적으로는, 채널형성영역의 면적을 증대시키는 것으로써, 표시장치의 개구율은 저하하는 경향이 있다. 즉, TFT의 특성의 변동저감을 도모할 경우, 개구율이 저하하여 버린다. 즉, 일반적으로는, TFT의 특성의 변동저감과, 개구율의 상승의 양쪽을 동시에 실현하는 것은 매우 어렵다. 본 실시형태와 같이, 멀티 게이트 구조의 TFT의 채널형성영역의 면적을 증대시킬 경우, 이 일은 특히 현저하게 된다.

그러나, 본 실시형태의 구성을 적용하는 것으로써, TFT의 특성의 변동저감과, 개구율의 상승의 양쪽을 동시에 실현할 수 있다.

또한, 개구율을 높이는 것은, 소비전력의 감소, 및 표시소자의 신뢰성의 향 상이 된다. 즉, 일정의 휘도가 요구되는 경우, 개구율이 크면 적은 전류(또는 전압)로 요구되는 휘도를 얻을 수 있기 때문이다. 그리고, 표시소자에 공급되는 전류(또는 전압)가 적으면, 표시소자의 열화속도는 감소되기 때문이다.

또한, 표시소자의 열화속도도 표시소자마다 변동이 있다. 따라서, 개구율을 높이고, 표시소자의 열화속도를 감소시킨 경우, 표시소자의 휘도열화의 변동도 저감할 수 있다. 따라서, TFT의 특성의 변동저감과 개구율의 증가에 의한 변동저감의 상승 효과에 의하여 표시장치의 시인성을 높일 수 있다.

또한, 멀티 게이트 구조의 TFT는, TFT의 오프전류를 저감시킬 수 있다. 따라서, TFT의 반도체가, 비단결정이라도, 단결정이라도, 멀티 게이트 구조의 TFT를 채용하는 것은 바람직하다.

또한, 본 실시형태와 같이, 구동 트랜지스터와, 상기 구동 트랜지스터에 접속되는 스위칭 트랜지스터를 함께 배선(신호선 또는 전원공급선)의 아래쪽에 배치하고, 스위칭 트랜지스터의 채널 길이의 방향과, 구동 트랜지스터의 채널 길이의 방향을 수직방향으로 배치하고, 구동 트랜지스터의 채널 폭의 방향을 상기 배선에 있어서, 전류가 흐르는 방향으로 함으로써, 개구율을 상승시킬 수 있다.

(실시형태 2)

본 실시형태에서는, 「배선의 형상에 있어서의 길이방향(배선의 길이방향)」의 의의에 대해서 도 5 내지 도 7을 사용하여 구체적으로 설명한다.

「배선의 형상에 있어서의 길이방향」(「채널 폭의 방향」)은, 「(상술한)채널형성영역의 상방에 배치된 배선에 있어서 전류가 흐르는 방향과 평행한 방향」이 다. 또한, 후술의 지그재그 모양 또는 구불구불한 모양의 배선의 경우, 반드시 배선에 있어서 전류가 직선방향으로 흐르지는 않다. 이 경우, 「배선의 형상에 있어서의 길이방향」(「채널 폭의 방향」)은, 「채널형성영역의 상방에 배치된 배선영역에 있어서, 전류가 흐르는 방향과 대략 평행한 방향」으로 한다.

여기서, 배선의 형상은, 반드시 도 5에 나타내는 바와 같이, 직선일 필요는 없다. 예를 들면, 도 6과 같이, 제 1 배선(501, 502)과 같이, 지그재그 모양으로 하여도 좋다. 또한, 도 7과 같이, 제 1 배선(501, 502)와 같이, 구불구불한 모양으로 하여도 좋다.

또한, 도 5 내지 도 7은, 배선과 화소전극의 배치를 나타내는 모식도이다. 따라서, TFT는 도시하지 않다. 501 내지 504는 제 1 배선이며, 601 내지 602는 제 2 배선이며, 701 내지 707은 화소전극이다. 또한, 제 1 배선 및 제 2 배선은, 한쪽이 소스 신호선이며, 다른쪽이 전원 공급선이다.

지그재그 형상은, 직선이 좌우로 몇번이나 구부러지는 형상을 의미한다. 또한, 구불구불함(meander)은, 「구불구불하여 흐르다」라고 하는 의미를 가진다. 그리고, 구불구불한 모양은, 그와 같은 형상을 의미한다.

그리고, 도 5와 같이, 제 1 배선(501-504) 및 제 2 배선(601)이 직선적인 형상의 경우, 「배선의 형상에 있어서의 길이방향(도 5의 제 1 화살표(8001))」은, 「채널형성영역의 상방에 배치된 제 1 배선에 있어서 전류가 흐르는 방향(도 5의 제 1 화살표(8001))」과 평행한 방향이다.

그리고, 도 6과 같이, 배선이 지그재그 모양의 경우, 예를 들면, 도 6의 제 1 배선영역(5001)의 아래쪽에 TFT를 배치한다. 이 경우, 「배선의 형상에 있어서의 길이방향(도 6의 제 2 화살표(8002))」은, 「채널형성영역의 상방에 배치된 배선에 있어서 전류가 흐르는 방향(도 6의 제 2 화살표(8002))」과 평행한 방향이다.

한편, 예를 들면, 도 6의 제 1 배선영역(5002)의 아래쪽에 TFT를 배치한 경우, 「배선의 형상에 있어서의 길이방향(도 6의 제 3 화살표(8003))」은, 「채널형성영역의 상방에 배치된 배선에 있어서 전류가 흐르는 방향(도 6의 제 3 화살표(8003))」과 평행한 방향이다.

또한, 도 7과 같이, 배선이 구불구불한 모양이어도, 전류는 배선의 형상을 따라서 흐른다. 따라서, 배선의 형상에 있어서의 길이방향과 평행하지 않는 방향으로 전류가 흐르는 개소가 존재한다. 그러나, 최종적으로는, 전자는 배선의 형상에 있어서의 길이방향과 평행방향으로 흐른다(도 7의 제 4 화살표(8004)). 따라서, 이러한 배선의 형상으로 하는 경우, 채널 폭의 방향을 「채널형성영역의 상방에 배치된 배선영역에 있어서 전류가 흐르는 방향과 대략 평행한 방향」 또는, 「배선의 형상에 있어서의 길이방향과 평행한 방향」으로 한다.

상기 구성에 따라, 화소전극간의 좁은 스페이스(인접하는 화소전극간의 스페이스)에 배선을 배치할 수 있다. 그 배선의 아래쪽에 가능한 한 큰 사이즈의 TFT(특히, 채널 폭이 큰 사이즈의 TFT)를 배치할 수 있다. 따라서, 개구율의 증가가 가능하게 된다.

(실시형태 3)

본 실시형태에서는, 본 발명의 구동 트랜지스터의 레이아웃의 다른 베리에이 션을 예시한다. 또한, 본 발명은, 본 실시형태에 예시하는 레이아웃으로 한정되지 않다.

도 8은, 싱글 게이트 구조의 레이아웃이다. 제 1 반도체층(101)은, 스위칭용 TFT의 섬형상 반도체층이다. 게이트 배선(105)과 겹치는 영역이 채널형성영역, 신호선(104)과 콘택트 홀을 개재하여 접속하는 영역이 소스 단자(또는 드레인 단자), 접속전극(103)과 접속하는 영역이 드레인 단자(또는 소스 단자)이다.

또한, 제 2 반도체층(102)은 표시소자를 구동하는 구동용 TFT(301)의 섬형상 반도체층이다. 그리고, 게이트 전극(100)과 겹치는 영역이 채널형성영역이다. 그리고, 구동용 TFT(301)의 게이트 전극은, 접속전극(103)과 콘택트 홀을 개재하여 접속한다. 또한, 구동용 TFT(301)의 소스 단자(또는 드레인 단자)와 전원공급선(106)이 접속된다. 구동용 TFT(301)의 드레인 단자(또는 소스 단자)와 접속전극(108)이 콘택트 홀을 개재하여 접속된다. 또한, 상기 접속전극(108)과 접하여 화소전극(107)이 형성된다.

또한, 도 8과 도 3의 대응관계는 이하에 나타낸다.

파선부(6002)로 둘러싸인 부분이 구동용 TFT(301)에 대응한다.

파선부(6021)로 둘러싸인 부분이 스위칭용 TFT(302)에 대응한다.

파선부(6022)로 둘러싸인 부분이 용량소자(300)에 대응한다.

화소전극(107)이 표시소자(303)의 화소전극에 대응한다.

신호선(104)이 신호선(304)에 대응한다.

전원공급선(106)이 전원공급선(306)에 대응한다.

또한, 도 9는 도 8에 대응하는 상면도이며, 제 1 반도체층(101), 제 2 반도체층(102)과 게이트 배선(105), 게이트 전극(100)을 형성한 단계의 도면이다.

그리고, 반도체층의 불순물 영역이 화소전극의 길이방향(또는, 배선에 있어서의 전류의 흐르는 방향, 또는, 배선의 형상에 있어서의 길이방향)과 평행하게 되도록 패터닝한다(도 8 내지 도 9의 파선부(6002)). 따라서, 채널 폭의 방향을 화소전극의 형상에 있어서의 길이방향과 평행하게 배치할 수 있다(도 8 내지 도 9의 화살표(7002)).

도 10은, 트리플 게이트 구조의 레이아웃이다. 제 1 반도체층(101)은, 스위칭용 TFT의 섬형상 반도체층이다. 게이트 배선(105)과 겹치는 영역이 채널형성영역, 신호선(104)과 접속하는 영역이 소스 단자(또는 드레인 단자), 접속전극(103)과 콘택트 홀을 개재하여 접속하는 영역이 드레인 단자(또는 소스 단자)이다.

또한, 제 2 반도체층(102)은 표시소자를 구동하는 구동용 TFT(301)의 섬형상 반도체층이다. 그리고, 게이트 전극(100)과 겹치는 영역이 채널형성영역이다. 그리고, 구동용 TFT(301)의 게이트 전극은, 접속전극(103)과 접속한다. 또한, 구동용 TFT(301)의 소스 단자(또는 드레인 단자)와 전원공급선(106)이 콘택트 홀을 개재하여 접속된다. 구동용 TFT(301)의 드레인 단자(또는 소스 단자)와 접속전극(108)이 콘택트 홀을 개재하여 접속된다. 또한, 상기 접속전극(108)과 접하여 화소전극(107)이 형성된다.

또한, 도 10과 도 3의 대응관계는 이하에 나타낸다.

파선부(6003)로 둘러싸인 부분이 구동용 TFT(301)에 대응한다.

파선부(6031)로 둘러싸인 부분이 스위칭용 TFT(302)에 대응한다.

파선부(6032)로 둘러싸인 부분이 용량소자(300)에 대응한다.

화소전극(107)이 표시소자(303)의 화소전극에 대응한다.

신호선(104)이 신호선(304)에 대응한다.

전원공급선(106)이 전원공급선(306)에 대응한다.

또한, 도 11은 도 10에 대응하는 상면도이며, 제 1 반도체층(101), 제 2 반도체층(102)과 게이트 배선(105), 게이트 전극(100)을 형성한 단계의 도면이다.

그리고, 반도체층의 불순물 영역이 화소전극의 길이방향(또는 배선에 있어서의 전류의 흐르는 방향, 또는, 배선의 형상에 있어서의 길이방향)과 평행하게 되도록(예를 들면, S자형) 패터닝한다(도 10 내지 도 11의 파선부(6003)). 따라서, 채널 폭의 방향을 화소전극의 형상에 있어서의 길이방향과 평행하게 배치할 수 있다(도 10 내지 도 11의 화살표(7003)).

본 실시형태에서는, 채널형성영역을 1개 또는 3개 가지는 TFT의 레이아웃에 대해서 설명했다. 또한, 실시형태 1에서는, 채널형성영역을 2개 가지는 TFT의 레이아웃에 대해서 설명했다. 그러나, 본 발명의 구성은 이들의 실시 형태의 구성으로 한정되지 않고, 4개 이상의 채널형성영역을 가지는 TFT에 대해서도 적용할 수 있다.

(실시형태 4)

본 발명은, 2개의 TFT로 구성되는 화소로 한정되지 않는다. L< W의 더블 게 이트 구조의 구동용 TFT를 가지는 화소구성의 경우, 개구율의 향상이나 심플한 개구부의 형상, 채널 폭의 길이를 길게 하는 배치가 되도록 적절히 사용할 수 있다.

(실시형태 5)

본 실시형태에서는, 표시장치의 제작공정에 대해서 설명한다. 또한, 설명은, 화소부에 대해서만 설명하지만, 구동회로부에 있어서는, 제작공정은 이것으로 한정되지 않고, 여기서는 설명을 생략한다.

도 4a에 나타내는 바와 같이, 바륨 보로실리케이트 유리, 또는 알루미노 보로실리케이트 유리 등의 유리로 이루어진 기판 위에, 산화규소막, 질화규소막, 또는 산화질화규소막으로 이루어진 하지막을 형성한다. 그 후, 비정질 구조를 가지는 반도체막을 레이저 결정화법이나 공지의 열결정화법을 사용하여 결정화한 결정질 반도체막을 소망의 형상으로 패터닝하고, 섬형상 반도체층(4101, 4102)을 얻는다. 또한, 하지막 및 반도체 막을 공지의 성막법(예를 들면, CVD법, PVD법 등)에 의하여 형성할 수 있다.

또한, 여기서는, 반도체 막을 결정화하고 다결정 규소막을 사용한다. 그러나, 본 발명은, 비정질규소, 또는 미결정규소를 사용하여도 좋다. 또한, 단결정규소를 사용하여도 좋다.

단결정 규소를 사용할 경우, 기판 위에 얇은 단결정 규소층이 배치되는 SOI기판(Silicon On Insulator기판) 등을 사용하면 좋다.

여기서, 섬형상 반도체층(4101) 중의 제 1 용량부분이 되는 제 1 영역에 불순물을 첨가하는 것으로써, 제 1 영역을 제 1 용량의 제 1 전극으로서 기능시킬 수 있다. 여기서, p형 도전성을 부여하는 붕소를 이온 도핑법에 의하여 주입한다. n형 도전성을 부여하는 불순물을 주입해도 좋다. n형 도정성을 부여하는 불순물로서는, 인, 비소 등이 있다. 또한, 불순물의 첨가에 대해서는, 공지의 방법(예를 들면, 이온 도핑법, 이온 샤워법 등)을 사용할 수 있다.

다음, 섬형상 반도체층(4101, 4102)을 덮은 게이트 절연막을 형성한다. 그 후, Ta, W, Ti, Mo, Al, Cu 등으로부터 선택된 원소, 또는, 상기 원소를 주성분으로 하는 합금재료 또는 화합물 재료를 사용하여, 게이트 전극을 형성하기 위한 도전막을 형성한다. 그 후, 소망의 형상으로 패터닝하여, 게이트 전극(4103, 4104)(4104는 주사선을 겸한다)을 얻는다(도 4b 참조).

다음, 섬형상 반도체층(4101, 4102)의 불순물 영역에 불순물을 첨가하는 것으로써, 소스 영역, 드레인 영역, 채널 영역을 형성한다. 여기서는, p채널형 트랜지스터를 형성하기 위해서 p형 도전성을 부여하는 붕소를 이온 도핑법에 의하여 주입한다. n채널형 트랜지스터를 형성할 경우는, n형 도전성을 부여하는 불순물로서는, 인, 비소 등이 있다. 또한, 불순물의 첨가에 대해서는, 공지의 방법(예를 들면, 이온 도핑법, 이온 샤워법 등)을 사용할 수 있다. 또한, 채널형성영역과 접하는 부분에 LDD영역을 형성하여도 좋다.

다음, 아닐링을 하여 첨가한 불순물을 활성화한다. 아닐링의 방법으로서는, 퍼니스 아닐링, 레이저 아닐링 등의 공지의 기술을 사용하면 좋다. 또한, 아닐링을 하기 전에 게이트 절연막을 보호하기 위해서 패시베이션 막(예를 들면, 산화규소 등)을 공지의 방법(예를 들면, CVD법, PVD법 등)에 의해서 형성하여도 좋다.

다음, 층간절연막을 형성한다. 층간절연막은, 유기절연막이어도 무기절연막이어도 좋다. 유기절연막으로서는, 아크릴, 폴리이미드, 실록산 등이 있다. 유기절연막의 형성 방법은 공지의 방법(스핀코팅 법, 딥 법 등)을 사용할 수 있다. 또한, 무기절연막으로서는, 산화규소, 질화규소 등이 있다. 공지의 방법(예를 들면, CVD법, PVD법 등)으로 형성하여도 좋다. 또한, 질화규소 등의 비유전율이 높은 재료를 사용하는 것은, 용량을 증가할 수 있다. 한편, 유기 절연막을 사용할 경우는, 평탄화할 수 있다.

또한, 층간절연막은 공지의 기술(예를 들면, CMP법)에 의해서 평탄화 처리를 하여도 좋다.

다음, 도 4c에 나타내는 바와 같이, 섬형상 반도체층(4101,4102), 게이트 전극(4103, 4104)에 도달하는 콘택트 홀(4105)을 형성하고, 배선(4106, 4107, 4108)(4106은 소스 신호선, 4107은 전원공급선으로 된다)) 및 전극(4110)을 형성한다.

다음, 도 4d에 나타내는 바와 같이, 화소전극(4109)을 형성한다. 화소전극의 재료로서는, 인듐주석산화물(통칭: ITO) 등이 대표적이다. 화소전극(4109)도, 상기 재료로 되는 막을 형성한 후, 패터닝에 의하여 소망의 형상을 얻는다. 여기서, 전극(4110)과, 화소전극(4109)은, 콘택트 홀(4105)을 통하여 접한다.

다음, 인접하는 화소의 사이에 격벽을 형성하고, 발광 에어리어로 되는 부분을 패터닝에 의해서 개구한다. 그 후, 개구부분에 EL 층을 형성한다.

본 실시형태에 있어서는, 톱 게이트형의 TFT의 제작방법에 대해서 설명한다. 그러나, 본 발명은 보텀 게이트형의 TFT에도 적용할 수 있다.

(실시형태 6)

본 실시형태에서는, 발광표시패널의 외관의 일례에 대해서, 도 14a 내지 도 14b를 사용하여 설명한다. 도 14a는, 제 1 기판과, 제 2 기판의 사이를 제 1 시일재(1205) 및 제 2 시일재(1206)에 의하여 밀봉된 패널의 상면도이며, 도 14b는, 도 14a의 A-A’, B-B’의 각각에 있어서의 단면도에 상당한다.

도 14a는, 점선으로 나타내는 화소부(1202), 모니터 소자부(1230), 주사선 구동회로(1203)(게이트선 구동회로)를 나타낸다. 본 실시형태에 있어서, 화소부(1202), 및 주사선 구동회로(1203)는, 제 1 시일재 및 제 2 시일재로 밀봉되는 영역내에 있다. 또한, 1201은, 신호선(소스선)구동회로이며, 신호선 구동회로가 제 1 기판(1200) 위에 형성된다. 제 1 시일재로서는, 필러를 포함하는 점성이 높은 에폭시계 수지를 사용하는 것이 바람직하다. 또한, 제 2 시일재로서는, 점성이 낮은 에폭시계 수지를 사용하는 것이 바람직하다. 또한, 제 1 시일재(1205) 및 제 2 시일재(1206)는 가능한 한 수분이나 산소를 투과하지 않는 재료가 바람직하다.

또한, 화소부(1202)와 제 1 시일재(1205)와의 사이에 건조제를 설치하여도 좋다. 또한, 화소부에 있어서, 주사선 또는 신호선 위에 건조제를 설치하여도 좋다. 건조제로서는, 산화칼슘(CaO)이나 산화바륨(BaO) 등과 같은 알칼리토류 금속의 산화물과 같은 화학 흡착에 의해 물(H2O)을 흡착하는 물질을 사용하는 것이 바람직하다. 그러나, 이것에 한정되지 않고, 제올라이트나 실리카 겔 등의 물리 흡착에 의해 물을 흡착하는 물질을 사용하여도 상관없다.

또한, 층간절연막으로서 투습성이 높은 수지에 입상의 물질을 포함시킨 물을 사용하여, 층간절연막과 제 2 기판(1204)을 시일재로 고정할 수 있다. 또한, 투습성이 높은 수지 대신에, PSG(포스포실리케이트 유리), BPSG(보로포스포실리케이트 유리) 등의 무기물을 사용하여도 좋다.

또한, 주사선과 중첩하는 영역에 건조제를 설치하여도 좋다. 또한, 층간절연막으로서 투습성이 높은 수지에 입상의 물질을 포함시킨 것을 사용하여, 층간절연막과 제 2 기판(1204)을 시일재로 고정하여도 좋다. 이들의 건조제를 설치함으로써, 개구율을 저하시키지 않고 표시소자에의 수분의 침입 및 그것에 기인하는 열화를 억제할 수 있다. 따라서, 화소부(1202)의 주변부와 중앙부에 있어서의 표시소자의 열화의 변동을 억제할 수 있다.

또한, 접속배선(1210)은, 신호선 구동회로(1201) 및 주사선 구동회로(1203)에 입력되는 신호를 전송하기 위한 접속 배선이며, 외부 입력 단자로서 작용하는 FPC(1209)(가요성 프린트 회로)으로부터 접속 배선(1208)을 통하여 비디오 신호나 클록 신호를 받는다.

다음, 단면구조에 대해서 도 14b를 사용하여 설명한다. 제 1 기판(1200) 위에는, 구동회로 및 회소부가 형성되고, TFT를 대표하는 반도체 소자를 복수 가진다. 구동회로로서는, 신호선 구동회로(1201)와 화소부(1202)를 나타낸다. 또한, 신호선 구동회로(1201)는 n채널형 TFT(1221)와 p채널형 TFT(1222)를 조합한 CMOS회로가 형성된다.

본 실시형태에 있어서는, 동일 기판 위에 주사선 구동회로, 및 화소부의 TFT 가 형성된다. 따라서, 발광표시장치의 용적을 축소할 수 있다.

또한, 화소부(1202)는, 스위칭용 TFT(1211)와, 구동용 TFT(1212)와 그 소스 또는 드레인의 다른 쪽에 전기적으로 접속된 반사성을 가지는 도전막으로 되는 제 1 화소전극(1213)(양극)을 포함하는 복수의 화소에 의하여 형성된다.

또한, 제 1 화소 전극(양극)(1213)의 양 끝에는 절연물(1214)(뱅크, 격벽, 장벽, 제방 등이라고 불림)이 형성된다. 절연물(1214)에 형성하는 막의 피복율 (커버리지)을 양호하게 하기 위해, 절연물(1214)의 상단부 또는 하단부에 곡률반경을 가지는 곡면이 형성되도록 한다. 또한, 절연층(1214)의 표면을 질화알루미늄막, 질화산화알루미늄막, 탄소를 주성분으로 하는 박막, 또는 질화규소막으로 된 보호막으로 덮어도 좋다. 또한, 절연층(1214)으로서, 검은색 안료, 색소 등의 가시광을 흡수하는 재료를 용해 또는 분산시켜서 된 유기 재료를 사용하는 것으로써, 후에 형성되는 표시소자로부터의 미광을 흡수할 수 있다. 따라서, 각 화소의 콘트라스트가 향상된다. 본 발명에 있어서는, 상기 절연물의 아래쪽에 주사선, 신호선, 및 TFT를 배치한다. 또한, 주사선 또는 신호선의 아래쪽에 TFT를 배치한다. 주사선의 아래쪽에 TFT를 배치할 경우, 주사선의 형상에 있어서의 길이방향(또는 전류의 흐르는 방향)과 TFT의 채널 폭의 방향을 평행하게 배치한다. 신호선의 아래쪽에 TFT를 배치한 경우, 신호선의 형상에 있어서의 길이방향(또는 전류의 흐르는 방향)과 TFT의 채널 폭의 방향을 평행하게 배치한다.

또한, 제 1 화소 전극(1213)(양극) 위에는 유기 화합물 재료를 증착하여 전계 발광층(1215)을 선택적으로 형성한다. 또한, 전계 발광층(1215) 위에 제 2 화 소 전극(1216; 음극)을 형성한다.

이렇게 하여, 제 1 화소 전극(1213)(양극), 전계 발광층(1215) 및 제 2 화소 전극(1216)(음극)을 포함하는 발광 소자(1217)가 형성된다. 표시 소자(1217)는 제 2 기판(1204) 측으로 발광한다.

또한, 표시소자(1217)를 밀봉하기 위해 보호적층(1218)을 형성한다. 보호적층(1218)은, 제 1 무기 절연막과, 응력 완화막과, 제 2 무기 절연막과의 적층으로 이루어진다. 그 다음, 보호적층(1218)과 제 2 기판(1204)을 제 1 시일재(1205) 및 제 2 시일재(1206)로 접착한다. 제 2 시일재를 시일재를 적하하는 장치를 사용하여 적하하는 것이 바람직하다. 시일재를 디스펜서로부터 적하 또는 토출시켜 시일재를 액티브 매트릭스 기판 위에 형성한 후, 진공 중에서 제 2 기판과 액티브 매트릭스 기판을 부착시키고, 자외선 경화를 행하여 밀봉할 수 있다.

또한, 제 2 기판(1204)의 표면에는, 외광이 기판 표면에서 반사하는 것을 방지하기 위한 반사방지막(1226)을 형성한다. 또한, 제 2 기판과 반사방지막과의 사이에, 편광판 및 위상차판 중의 어느 한쪽 또는 양쪽을 형성하여도 좋다. 위상차판 또는 편광판을 제공함으로써, 외광이 화소전극에서 반사하는 것을 방지할 수 있다. 또한, 제 1 화소전극(1213) 및 제 2 화소전극(1216)을 투광성을 가지는 도전막 또는 반투광성을 가지는 도전막으로 형성하여, 층간절연막을 가시광을 흡수하는 재료, 또는 가시광을 흡수하는 재료를 용해 또는 분산시킨 유기재료를 사용하여 형성하면, 각 화소 전극에서 외광이 반사하지 않으므로, 위상차판 및 편광판을 사용하지 않아도 된다.

접속배선(1208)과 FPC(1209)는, 이방성 도전막 또는 이방성 도전 수지(1227)로 전기적으로 접속된다. 또한, 각 배선층과 접속 단자와의 접속부를 밀봉수지로 밀봉하는 것이 바람직하다. 이 구조에 의해, 단면부로부터 수분이 표시소자에 침입하여, 열화하는 것을 방지할 수 있다.

또한, 제 2 기판(1204)과 보호적층(1218)의 사이의 공간을, 제 2 시일재(1206) 대신에, 불활성 가스, 예를 들어, 질소가스로 충전함으로써, 열화를 방지하여도 좋다.

또한, 제 2 기판과 편광판의 사이에 착색층을 형성할 수 있다. 이 경우, 화소부에 백색 발광이 가능한 표시 소자를 형성하고, RGB를 나타내는 착색층을 별도 형성함으로써, 풀 컬러 표시를 할 수 있다. 또는, 화소부에 청색 발광이 가능한 발광 소자를 형성하고, 색 변환층 등을 별도 형성함으로써, 풀 컬러 표시를 할 수 있다. 또한, 각 화소부에, 적색, 녹색, 청색의 발광을 나타내는 표시소자를 형성하고, 착색층을 사용할 수도 있다. 이와 같은 표시 모듈은 각 RGB의 색순도가 높고, 고정세의 표시가 가능하게 된다.

또한, 제 1 기판(1200) 또는 제 2 기판(1204) 중의 어느 한쪽, 또는 양쪽 모두에 필름 또는 수지 등의 기판을 사용하여 발광 표시 모듈을 형성하여도 좋다. 이와 같이, 필름 또는 수지 등의 기판을 사용하면, 표시장치의 경량화, 소형화, 박막화를 향상시킬 수 있다.

또는, 외부 입력 단자로서 작용하는 FPC(1209)(가요성 프린트 회로)의 표면 또는 단부에 콘트롤러, 메모리, 화소 구동회로와 같은 IC 칩을 형성하여 발광 표시 모듈을 형성하여도 좋다.

(실시형태 7)

발광소자는, 전계가 생기면, 발광하는 유기화합물층을, 양극 및 음극으로 끼우는 구조를 가지는 소자(OLED 소자)를 나타낸다. 다만, 이것으로 한정되지 않는다.

또한, 발광소자는, 싱글렛 여기자(singlet exciton)로부터 기저상태로 천이할 때의 발광(형광)을 사용하는 것과 트리플렛 여기자로부터 기저상태로 천이할 때의 발광(인광)을 사용하는 것의 양쪽 모두를 의미한다.

유기화합물층으로서는, 정공 주입층, 정공 수송층, 발광층, 전자 수송층, 전자 주입층 등을 들 수 있다. 발광 소자는, 기본적으로는 양극과 발광층과 음극을 차례로 적층한 구조로 나타내지만, 그 이외에도, 양극과 정공 주입층과 발광층과 전자 주입층 및 음극을 차례로 적층한 구조이나, 양극과 정공 주입층과 정공 수송층과 발광층과 전자 수송층과 전자 주입층과 음극을 차례로 적층한 구조 등이 있다.

또한, 유기화합물층은, 정공 주입층, 정공 수송층, 발광층, 전자 수송층, 전자 주입층 등이 명확하게 구별되는 적층 구조를 가지는 층으로 한정되지 않는다. 즉, 유기화합물층은 정공 주입층, 정공 수송층, 발광층, 전자 수송층, 전자 주입층 등을 구성하는 재료가 혼합한 층을 포함하는 구조이라도 좋다.

또한, 무기물이 혼합되어도 좋다.

또한, OLED 소자의 유기화합물층으로서는, 저분자 재료, 고분자 재료, 중분 자 재료의 어느 재료라도 좋다.

또한, 본 명세서에 있어서, 중분자 재료는, 연쇄하는 분자의 길이가 10um이하이고, 승화성을 가지지 않은 것으로 한다.

(실시형태 8)

본 발명의 표시소자에 적용할 수 있는 다른 구성을, 도 12a 내지 도 13c를 사용하여 설명한다.

전계발광을 이용하는 발광소자(표시소자)는, 발광 재료가 유기화합물인지, 무기화합물인지에 따라 구별된다. 일반적으로, 전자는 유기 EL소자, 후자는 무기 EL소자라고 부른다.

무기 EL소자는, 그 소자구성에 따라, 분산형 무기 EL소자와 박막형 무기 EL소자로 분류된다. 전자는, 발광 재료의 입자를 바인더 내에 분산시킨 전계발광층을 가지고, 후자는, 발광 재료의 박막으로 이루어진 전계발광층을 가지는 점에 차이는 있다. 하지만, 고전계에 의해 가속된 전자가 필요하는 점에서 공통된다. 또한, 얻어지는 발광의 메커니즘으로서는, 도너 준위와 억셉터 준위를 이용하는 도너-억셉터 재결합형 발광과, 금속이온의 내각 전자천이를 이용하는 국재형 발광이 있다. 일반적으로, 분산형 무기 EL소자에는 도너-억셉터 재결합형 발광, 박막형 무기 EL소자에는 국재형 발광인 경우가 많다.

본 발명에서 사용할 수 있는 발광 재료는, 모체재료와 발광중심이 되는 불순물원소로 구성된다. 함유시키는 불순물원소를 변화시킴으로써, 여러 가지 색의 발광을 얻을 수 있다. 발광 재료의 제작 방법으로서는, 고상법이나 액상법(공침법) 등의 여러 가지 방법을 이용할 수 있다. 또한, 분무열분해법, 복분해법, 프리커서의 열분해반응에 의한 방법, 역 미셀법이나 이들 방법과 고온소성을 조합한 방법, 동결 건조법 등의 액상법 등도 사용할 수 있다.

고상법은, 모체재료와, 불순물원소 또는 불순물원소를 포함한 화합물을 칭량하고, 유발로 혼합하고, 전기로로 가열하고, 소성을 행해 반응시킴으로써, 모체재료에 불순물원소를 함유시키는 방법이다. 소성온도는, 700 내지 1500℃가 바람직하다. 온도가 지나치게 낮은 경우에는 고상반응이 진행하지 않고, 온도가 지나치게 높은 경우에는 모체재료가 분해하기 때문이다. 또한, 분말 상태에서 소성을 행해도 되는데, 팰릿 상태에서 소성을 행하는 것이 바람직하다. 비교적 고온에서의 소성이 필요하지만, 고상법이 간단하므로, 생산성이 높은 대량생산에 적합하다.

액상법(공침법)은, 모체재료 또는 모체재료를 포함하는 화합물과, 불순물원소 또는 불순물원소를 포함한 화합물을 용액 내에서 반응시키고, 건조시킨 후, 소성을 하는 방법이다. 발광 재료의 입자는 균일하게 분포하고, 입경이 작고 낮은 소성온도라도 반응이 진행할 수 있다.

발광 재료에 사용하는 모체재료로는, 황화물, 산화물, 질화물을 사용할 수 있다. 황화물로서는, 예를 들면, 유화아연(ZnS), 황화카드뮴(CdS), 유화칼슘(CaS), 유화이트륨(Y2S3), 유화갈륨(Ga2S3), 유화스트론튬(SrS), 유화바륨(BaS) 등을 사용할 수 있다. 또한, 산화물로서는, 예를 들면, 산화아연(ZnO), 산화이트륨(Y2O3) 등을 사용할 수 있다. 또한, 질화물로서는, 예를 들면, 질화알루미늄(AlN), 질화갈륨(GaN), 질화인듐(InN) 등을 사용할 수 있다. 또한, 셀렌화아 연(ZnSe), 텔루르화아연(ZnTe) 등도 사용할 수 있고, 유화칼슘-갈륨(CaGa2S4), 유화스트론튬-갈륨(SrGa2S4), 유화바륨-갈륨(BaGa2S4) 등의 3원계 혼정도 사용할 수 있다.

국재형 발광의 발광중심으로서, 망간(Mn), 구리(Cu), 사마륨(Sm), 테르븀(Tb), 에르븀(Er), 툴륨(Tm), 유로퓸(Eu), 세륨(Ce), 프라세오디뮴(Pr) 등을 사용할 수 있다. 또한, 전하보상으로서, 불소(F), 염소(Cl) 등의 할로겐 원소가 첨가되어 있어도 된다.

한편, 도너-억셉터 재결합형 발광의 발광중심으로서, 도너 준위를 형성하는 제 1 불순물원소 및 억셉터 준위를 형성하는 제 2 불순물원소를 포함하는 발광 재료를 사용할 수 있다. 제 1 불순물원소는, 예를 들면, 불소(F), 염소(Cl), 알루미늄(Al) 등을 사용할 수 있다. 제 2 불순물원소로는, 예를 들면, 구리(Cu), 은(Ag) 등을 사용할 수 있다.

도너-억셉터 재결합형 발광의 발광 재료를 고상법을 이용해서 합성할 경우, 모체재료와, 제 1 불순물원소 또는 제 1 불순물원소를 포함한 화합물과, 제 2 불순물원소 또는 제 2 불순물원소를 포함한 화합물을 각각 칭량하고, 유발로 혼합한 후, 전기로에서 가열, 소성을 행한다. 모체재료로서는, 상술한 모체재료를 사용할 수 있고, 제 1 불순물원소로서는, 예를 들면, 불소(F), 염소(Cl) 등을 사용할 수 있고, 제 1 불순물원소를 포함한 화합물로서는, 예를 들면, 유화알루미늄(Al2S3) 등을 사용할 수 있고, 제 2 불순물원소로서는, 예를 들면, 구리(Cu), 은(Ag) 등을 사용할 수 있고, 제 2 불순물원소를 포함한 화합물로서는, 유화구리(Cu2S), 유화 은(Ag2S) 등을 사용할 수 있다. 소성온도는, 700 내지 1500℃가 바람직하다. 온도가 지나치게 낮은 경우에는 고상반응이 진행하지 않고, 온도가 지나치게 높은 경우에는 모체재료가 분해하기 때문이다. 또한, 분말상태에서 소성을 행해도 되지만, 팰릿 상태에서 소성을 행하는 것이 바람직하다.

또한, 고상반응을 이용할 경우의 불순물원소로서, 제 1 불순물원소와 제 2 불순물원소로 구성되는 화합물을 조합해서 사용해도 된다. 이 경우, 불순물원소가 확산되기 쉽고, 고상반응이 진행되기 쉬워지므로, 균일한 발광 재료를 얻을 수 있다. 또한, 여분한[여분의] 불순물원소가 혼입하지 않으므로, 순도가 높은 발광 재료를 얻을 수 있다. 제 1 불순물원소와 제 2 불순물원소로 구성되는 화합물로서는, 예를 들면, 염화구리(CuCl), 염화은(AgCl) 등을 사용할 수 있다.

또한, 이들 불순물원소의 농도는, 모체재료에 대하여 0.01 내지 10atom%이면 좋고, 바람직하게는, 0.05 내지 5atom%의 범위로 한다.

박막형 무기 EL의 경우, 전계발광층은, 상기 발광 재료를 포함한 층이며, 저항가열증착법, 전자빔증착(EB증착)법 등의 진공증착법, 스퍼터링법 등의 물리기상성장법(PVD), 유기금속CVD법, 하이드라이드 수송 감압CVD법 등의 화학기상성장법(CVD), 원자층 에피택시법(ALE) 등을 이용해서 형성할 수 있다.

도 12a 내지 12c에 발광소자로서 사용할 수 있는 박막형 무기 EL소자의 일례를 나타낸다. 도 12a 내지 도 12c에 있어서, 표시소자는, 제 1 전극층(50), 전계발광층(52), 제 2 전극층(53)을 포함한다.