JP6213148B2 - ストレージ装置、ストレージ装置の制御方法およびストレージ装置制御プログラム - Google Patents

ストレージ装置、ストレージ装置の制御方法およびストレージ装置制御プログラム Download PDFInfo

- Publication number

- JP6213148B2 JP6213148B2 JP2013222060A JP2013222060A JP6213148B2 JP 6213148 B2 JP6213148 B2 JP 6213148B2 JP 2013222060 A JP2013222060 A JP 2013222060A JP 2013222060 A JP2013222060 A JP 2013222060A JP 6213148 B2 JP6213148 B2 JP 6213148B2

- Authority

- JP

- Japan

- Prior art keywords

- processing

- storage device

- unit

- accommodation

- performance

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0602—Interfaces specially adapted for storage systems specifically adapted to achieve a particular effect

- G06F3/061—Improving I/O performance

- G06F3/0613—Improving I/O performance in relation to throughput

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0629—Configuration or reconfiguration of storage systems

- G06F3/0631—Configuration or reconfiguration of storage systems by allocating resources to storage systems

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0628—Interfaces specially adapted for storage systems making use of a particular technique

- G06F3/0655—Vertical data movement, i.e. input-output transfer; data movement between one or more hosts and one or more storage devices

- G06F3/0659—Command handling arrangements, e.g. command buffers, queues, command scheduling

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/0671—In-line storage system

- G06F3/0673—Single storage device

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/06—Digital input from, or digital output to, record carriers, e.g. RAID, emulated record carriers or networked record carriers

- G06F3/0601—Interfaces specially adapted for storage systems

- G06F3/0668—Interfaces specially adapted for storage systems adopting a particular infrastructure

- G06F3/0671—In-line storage system

- G06F3/0683—Plurality of storage devices

- G06F3/0689—Disk arrays, e.g. RAID, JBOD

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Human Computer Interaction (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Debugging And Monitoring (AREA)

- Information Retrieval, Db Structures And Fs Structures Therefor (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

Description

なお、前記目的に限らず、後述する発明を実施するための最良の形態に示す各構成により導かれる作用効果であって、従来の技術によっては得られない作用効果を奏することも本件の他の目的の一つとして位置付けることができる。

まず、図1〜図5を参照しながら、本実施形態の構成について説明する。

〔1−1〕本実施形態のストレージシステムの構成

図1は、本実施形態に係るストレージシステム1の構成の一例を示す図である。図1に示すように、ストレージシステム1は、ホスト10a,ホスト10bおよびストレージ装置100を有する。また、ストレージシステム1において、ストレージ装置100は、ホスト10aおよびホスト10bと接続される。なお、ストレージ装置100と接続するホストの数は図示に限定されるものではなく、変更可能である。

続いて、図1を参照しながら、ホスト10aおよびホスト10bの構成について説明する。ホスト10aおよびホスト10bは、サーバなどの情報処理装置である。ホスト10aは、FC(Fibre Channel)−A(Adapter)11a,FC−A12a,iSCSI(internet Small Computer System Interface)−A13a,iSCSI−A14aを有する。FC−A11a,12bは、通常、FC−HBA(Host Bus Adapter)の形態であり、iSCSI−A13a,14aは、通常、NIC(Network Interface Card)を使用し、そこでiSCSIプロトコルを動作させる形態である。

続いて、図1を参照しながら、本実施形態に係るストレージ装置100の構成について説明する。本実施形態に係るストレージ装置100は、HDD(Hard Disk Drive)101a〜101dと、CM200a,200bとを有する。

HDD101a〜101dは、RAID(Redundant Arrays of Inexpensive Drives)を構成し、ユーザデータを記憶する。CM200a,200bは、ストレージ装置100のシステム全体を制御するストレージ制御モジュールである。CM200a,200bとで冗長化されている。なお、ストレージ装置100が有するHDD,CMの数は、図示したものに限定されるものではなく、変更可能である。また、コントローラエンクロジャーのストレージ装置(ストレージ制御装置)として、複数のCMを搭載し、HDD等の物理ディスクは、ディスクエンクロージャのストレージ装置に搭載して、接続することでストレージシステムを構成してもよい。

また、ストレージ装置100は、HDD101a〜101d(一以上の物理記憶装置)を論理的に分割した論理ユニット(以下LUという)として使用される。各LU(記憶装置)は、それぞれが論理的な1台のHDDとしてホスト10a,10bにより認識される。

次に、図2を参照しながら、ストレージ装置100により実行されるファームウェアにより実現される処理部300の機能構成について説明する。図2は、ストレージ装置100により実行されるファームウェアにより実現される処理部300の機能構成を示すブロック図である。なお、処理部300は、メモリ210aおよびメモリ210bと、CPU220aおよびCPU220bとが協働して実現される。

次に、図3を参照しながら、SCSIターゲット制御部303の機能構成およびQoS制御域213の情報について説明する。図3は、本実施形態に係るSCSIターゲット制御部303の機能構成およびQoS制御域213の情報を示すブロック図である。

QoS管理テーブル501は、対象毎に、「優先順位」と「性能値」と「実行可能な入出力処理数」と「実行した入出力処理数」とを対応付けた情報を記憶する。ここで、QoS管理テーブル501の詳細な説明をする前に、まず、図4を参照しながら「優先順位」と「性能値」との対応関係について説明する。図4は、優先順位と性能値との対応関係の一例を示す図である。

待ちキュー格納部502は、キューであり、コマンド受信部504が受信したコマンドのうち、所定時間経過後にスケジュールされるコマンドを格納する。また、待ちキュー格納部502は、ホストとLUNとの組合せ毎またはポートとLUNとの組合せ毎(LU毎)に設けられる。

性能設定部503は、QoS管理テーブル501が記憶する情報のうち「対象」,「優先順位」,「Nミリ秒I/O数」,「Nミリ秒ブロック数」のそれぞれに、管理者から受け付けた値を設定する。また、性能設定部503は、表1を参照しながら後述するミクロ性能融通およびマクロ性能融通の各種条件や、当該各種条件に係る値などを、管理者からの指示に応じて設定する機能も有する。なお、管理者は、各ホスト10の性能や各ホスト10が実行するアプリケーションなどを加味して、優先順位や各種条件に係る値などを設定する。さらに、性能設定部503は、ストレージ装置100に接続するホスト10や、ホスト10とLUNとの組合せ(LU)が変化した場合に、QoS管理テーブル501が記憶する情報を更新する。

コマンド受信部504は、ホスト10からコマンド(入出力要求)を受信して受け付けるとともに、実行待ちのコマンドがあるか否かを判定する。例えば、コマンド受信部504は、実行待ちのコマンドがあると判定した場合、受信したコマンドを待ちキュー格納部502に格納させる。また、コマンド受信部504は、実行待ちのコマンドがないと判定した場合、後述するスケジュール部506に受信したコマンドの実行順をスケジュールさせる。なお、コマンド受信部504の詳細な動作(コマンド受信処理の処理手順)については、図10を参照しながら後述する。

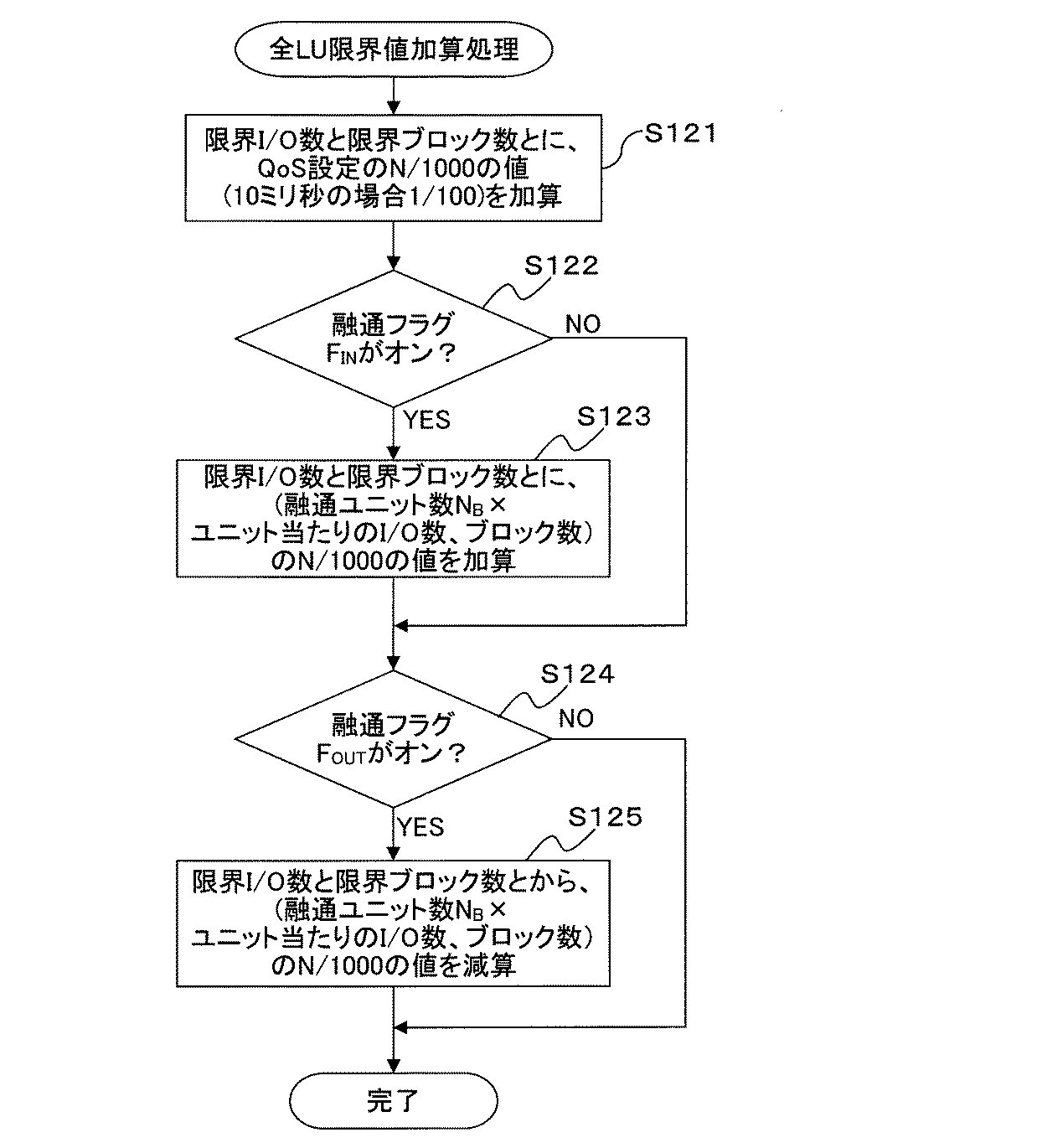

算出部505は、ホスト10,ポートおよびLUのそれぞれに対して設定された優先順位に基づいて決定される入出力処理量の上限値(即ち限界I/O数と限界ブロック数)を所定の時間(Nミリ秒)毎に算出する。ここで、算出部505は、10ミリ秒毎に限界I/O数と限界ブロック数とを算出するものとして説明する。例えば、算出部505は、10ミリ秒毎に、限界I/O数にNミリ秒I/O数を加算する。また、算出部505は、10ミリ秒毎に、限界ブロック数にNミリ秒ブロック数を加算する。算出部505は、算出した限界I/O数と限界ブロック数とをQoS管理テーブル501に格納させる。

スケジュール部506は、ホスト10から受け付けたコマンド数と、算出部505により算出された限界I/O数および限界ブロック数とに基づいて、コマンドの実行順をスケジュールする。例えば、スケジュール部506は、所定の時間が経過する毎に、コマンドの実行順をスケジュールする。なお、スケジュール部506の詳細な動作(QoS I/O起動スケジュール処理の処理手順)については、図8および図9を参照しながら後述する。

実行部507は、スケジュール部506によりスケジュールされた実行順でコマンドを待ちキュー格納部502からデキューし、コマンドを起動して入出力処理を実行する。

次に、マクロ融通チェック部510,マクロ融通処理部520,マクロ融通復旧処理部530,ミクロ融通処理部540について説明するのに先立ち、本実施形態で採用される2種類の性能融通方式について説明する。2種類の性能融通方式は、ミクロ性能融通方式とマクロ性能融通方式とである。

次に、上述したミクロ性能融通およびマクロ性能融通を実行すべく、図3に示すように、QoS制御域213に、LU(LUN#1〜#m;mは2以上の整数)毎に保持される、各LUの性能融通情報について説明する。つまり、QoS制御域213には、LU毎に、例えば、6種類の融通フラグFIN,FOUT,FINMAX,FOUTMAX,FMICIN,FMICOUTと8種類の数値NB,NC,ND,NE,NF,NG,NH,NIとが性能融通情報として保存される。これらの融通フラグや数値は、管理者からの指示に応じて性能設定部503により設定されるか、もしくは、ミクロ性能融通およびマクロ性能融通の実行中にSCSIターゲット制御部303の機能によって設定・更新される。

融通フラグFOUTは、対象LUが他のLUに対しマクロ性能融通を行なっている場合つまり対象LUが融通元LUである場合にオンに設定され、それ以外の場合にオフに設定される。

融通フラグFOUTMAXは、対象LUから他のLUに対するマクロ性能融通の融通量が予め設定された下限に到達している場合(下限到達時)にオンに設定され、それ以外の場合にオフに設定される。

融通フラグFMICOUTは、対象LUが他のLUに対しミクロ性能融通を行なっている場合にオンに設定され、それ以外の場合にオフに設定される。

待ちブロック数NDは、対象LUにおける、QoS制御で待ち状態のI/O(ホスト10からの入出力要求またはコマンド)の総ブロック数である。

これらの待ちI/O数NCおよび待ちブロック数NDから、QoS制御で待ち状態のI/Oに対応するユニット数(待ちユニット数)が換算される。

ミクロ融通ユニット数NHは、今回のミクロ性能融通によって、対象LUが他のLUから受ける一時的な融通量、もしくは、対象LUが他のLUに対し融通する一時的な融通量に対応するユニット数である。つまり、ミクロ融通ユニット数NHは、当該一時的な融通量を、上述した所定の性能融通単位(ユニット)の数に換算した値である。

マクロ融通チェック部510は、第1判定部521および第2判定部522によりマクロ性能融通を実行するか否かを判定するために必要な情報(最小余りユニット数NEおよび最小待ちユニット数NF)をチェックして取得する。このため、マクロ融通チェック部510は、第1取得部511および第2取得部512を有する。なお、マクロ融通チェック部510の詳細な動作(マクロ融通1秒チェック処理の処理手順)については、図13を参照しながら後述する。

マクロ融通処理部520は、マクロ融通チェック部510の第1取得部511および第2取得部512によりそれぞれ取得された最小待ちユニット数NFおよび最小余りユニット数NEに基づき、マクロ性能融通を実行する。マクロ融通処理部520は、第1判定部521,第2判定部522および変更部523を有する。なお、マクロ融通処理部520の詳細な動作(マクロ融通処理の処理手順)については、図14および図15を参照しながら後述する。

(a2)第2判定部522による判定結果: 他のLU(第2記憶装置)がマクロ性能融通の上記「融通する条件」を満たす融通元LUである場合。

(a3)変更処理: 融通先LUについて算出された性能制限値に、上記所定の性能融通単位で1ユニット分に対応する値を加算するとともに、融通元LUについて算出された性能制限値から、上記所定の性能融通単位で1ユニット分に対応する値を減算する。

マクロ融通復旧処理部530は、各LUが上記「復帰条件」を満たした場合、融通先LUに融通した処理量を、融通先LUから融通元LUに復帰させる復旧処理を実行する。マクロ融通復旧処理部530は、第3判定部531および復旧処理部532を有する。なお、マクロ融通復旧処理部530(特に復旧処理部532)の詳細な動作(マクロ融通復旧処理の処理手順)については、図16〜図20を参照しながら後述する。

ミクロ融通処理部540は、ミクロ性能融通を実行するもので、第4判定部541,融通処理部542および融通後処理部543を有する。なお、ミクロ融通処理部540の詳細な動作(ミクロ融通処理およびミクロ融通後処理の処理手順)については、図11および図12を参照しながら後述する。ミクロ融通処理部540によるミクロ性能融通の実行回数は、1マクロサイクル当たり、QoS制御域213においてミクロ融通数NGとして設定される値(例えば4)に制限される。

次に、図6〜図20を参照しながら、本実施形態に係るストレージ装置100の動作、特に、本実施形態に係るストレージ装置100による処理の処理手順について説明する。

まず、図6に示すフローチャート(ステップS101〜S111)に従って、本実施形態のSCSIターゲット制御部303によって実行されるNミリ秒タイマスケジュール処理の処理手順について説明する。Nは、例えば、10であり、SCSIターゲット制御部303は、各ポートについて、10ミリ秒毎に、図6に示すNミリ秒タイマスケジュール処理を実行する。これにより、図7〜図9および図11〜図20を参照しながら詳述するごとく、QoS制御(QoS I/O起動スケジュール),マクロ性能融通およびミクロ性能融通が実行される。

上述のような全LU限界値加算処理(ステップS103,S121〜S125)をNミリ秒毎に実行することで、マクロ性能融通がNミリ秒毎に実行される。なお、ホスト10を性能融通対象とする場合には、算出部505は、ステップS102において、全てのホストのそれぞれに対し、図7に示す全LU限界値加算処理と同様の全ホスト限界値加算処理を実行する。

次に、図8および図9に示すフローチャート(ステップS201〜S217)に従って、本実施形態のスケジュール部506によって実行されるQoS I/O起動スケジュール処理(図6のステップS108)の処理手順について詳細に説明する。QoS I/O起動スケジュール処理では、LU毎に設けた待ちキュー内にコマンドが待機している場合、以下のように、当該LUの限界I/O数および限界ブロック数に従って、待ちキュー内のコマンドが実行される。

ここで、図10に示すフローチャート(ステップS301〜S309)に従って、本実施形態のコマンド受信部504によって実行されるコマンド受信処理の処理手順について詳細に説明する。ストレージ装置100は、例えば、コマンドを受信したことを契機にこのコマンド受信処理を実行する。コマンド受信処理では、ホストからコマンドを受信した際、以下のように、受信したコマンドは、限界I/O数および限界ブロック数に応じて、即座に実行されるか、もしくは、待ちキューにエンキューされる。

次に、図11に示すフローチャート(ステップS401〜S411)に従って、本実施形態のミクロ融通処理部540(第4判定部541および融通処理部542)によって実行されるミクロ融通処理(図6のステップS104)の処理手順について説明する。ミクロ融通処理は、図6に示すNミリ秒タイマスケジュール処理がNミリ秒毎に実行される中で、1ミクロサイクル(例えば0.5秒=500ミリ秒)毎に、スケジュール部506によるQoS I/O起動スケジュール処理前に実行される。

次に、図12に示すフローチャート(ステップS501〜S507)に従って、本実施形態の融通後処理部543によって実行されるミクロ融通後処理(図6のステップS111)の処理手順について説明する。ミクロ融通後処理は、図6に示すNミリ秒タイマスケジュール処理がNミリ秒毎に実行される中で、1ミクロサイクル(0.5秒)毎に、スケジュール部506によるQoSI/O起動スケジュール処理後に実行される。特に、ミクロ融通後処理は、図6に示すように、QoSI/O起動スケジュール処理およびマクロ融通処理が実行され、1秒毎のQoSカウントがクリアされた後の、Nミリ秒タイマスケジュール処理の最終ステップS111で実行される。

次に、図13に示すフローチャート(ステップS601〜S608)に従って、本実施形態のマクロ融通チェック部510によって実行されるマクロ融通1秒チェック処理(図6のステップS105)の処理手順について説明する。マクロ融通1秒チェック処理では、第1判定部521および第2判定部522によりマクロ性能融通を実行するか否かを判定するために必要な情報である、最小余りユニット数NEおよび最小待ちユニット数NFが取得される。マクロ融通1秒チェック処理は、図6に示すNミリ秒タイマスケジュール処理がNミリ秒毎に実行される中で、例えば1秒毎に実行される。

Uに待ちI/Oがあるか否か、つまり、対象LUが、融通元LUでありながら処理性能不足の生じた融通復旧LUであるか否かを判定する(ステップS602)。

次に、図14および図15に示すフローチャート(ステップS701〜S713)に従って、本実施形態のマクロ融通処理部520によって実行されるマクロ融通処理(図6のステップS109)の処理手順について説明する。マクロ融通処理は、図6に示すNミリ秒タイマスケジュール処理がNミリ秒毎に実行される中で、1マクロサイクル(例えば30秒)毎に、スケジュール部506によるQoS I/O起動スケジュール処理後に起動される。マクロ融通処理では、QoS I/O起動スケジュール後に、1マクロサイクル毎のタイミングで、連続的に処理性能に余裕のあるLUから連続的に処理性能が不足しているLUにマクロ性能融通が行なわれる。

次に、図16および図17に示すフローチャート(ステップS801〜S818)に従って、本実施形態の復旧処理部532によって実行されるマクロ融通復旧処理(図6のステップS107)の処理手順について説明する。マクロ融通復旧処理は、図6に示すNミリ秒タイマスケジュール処理がNミリ秒毎に実行される中で、他のLUへ性能を融通しているLUで性能不足を検出した場合(図6のステップS106のYESルート)、当該LUの性能を元の設定性能に戻すために実行される。つまり、マクロ融通復旧処理では、融通復旧LUが他のLUに融通した処理量が、融通先LUから融通復旧LUに復帰される。その際、復旧処理部532は、融通先LUに対し融通された処理量の残量が均等もしくはほぼ均等になるように、当該処理量を融通先LUから融通復旧LUに復帰させる。

本実施形態のストレージ装置100によれば、使用されるホストとLUとの組合せの性能レベル(優先度)に従って、ストレージ装置100の性能を配分し、ストレージのQoS機能を容易に実現することができる。

以上、本発明の好ましい実施形態について詳述したが、本発明は、係る特定の実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲内において、種々の変形、変更して実施することができる。

以上の各実施例を含む実施形態に関し、さらに以下の付記を開示する。

(付記1)

複数の記憶装置に設定された優先度に基づいて決定される入出力処理量の上限値を前記記憶装置毎に算出する算出部と、

情報処理装置から受信した入出力要求に係る処理量と、前記算出部により算出された前記上限値とに基づいて、前記入出力要求に係る処理の実行順をスケジュールするスケジュール部と、

前記スケジュール部によりスケジュールされた前記実行順で前記入出力要求に係る処理を実行する実行部と、

前記記憶装置毎に、当該記憶装置に対する入出力要求に係る処理量が第1所定時間に亘って当該記憶装置の処理性能を超えているか否かを判定する第1判定部と、

当該記憶装置に対する入出力要求に係る処理量が当該記憶装置の処理性能を超えていると前記第1判定部により判定された場合、当該記憶装置についての前記上限値を、所定の性能融通単位で変更する変更部と、

を有する、ストレージ装置。

前記記憶装置毎に、当該記憶装置に対する入出力要求に係る処理量が第2所定時間に亘って当該記憶装置の処理性能を下回っているか否かを判定する第2判定部を、さらに有し、

前記複数の記憶装置のうち第1記憶装置に対する入出力要求に係る処理量が前記第1所定時間に亘って前記第1記憶装置の処理性能を超えていると前記第1判定部により判定され、且つ、前記複数の記憶装置のうち第2記憶装置に対する入出力要求に係る処理量が前記第2所定時間に亘って前記第2記憶装置の処理性能を下回っていると前記第2判定部により判定された場合、前記変更部は、前記上限値を前記所定の性能融通単位で変更することで、前記第2記憶装置から前記第1記憶装置への性能融通を前記所定の性能融通単位で行なう、

付記1に記載のストレージ装置。

前記変更部は、前記第1記憶装置について算出された前記上限値に、前記所定の性能融通単位に対応する値を加算するとともに、前記第2記憶装置について算出された前記上限値から、前記所定の性能融通単位に対応する値を減算するように、前記上限値を変更することで、前記第2記憶装置から前記第1記憶装置への性能融通を前記所定の性能融通単位で行なう、

付記2に記載のストレージ装置。

前記所定の性能融通単位に対応する値は、前記優先度に基づいて決定される前記入出力処理量の最小間隔以下である、

付記3に記載のストレージ装置。

前記記憶装置毎に、前記第1所定時間よりも短い時間間隔で、当該記憶装置に対する入出力要求の処理待ち量を取得し、前記第1所定時間内に取得された前記処理待ち量のうち最小のものを最小待ち量として取得する第1取得部を、さらに有し、

前記第1判定部は、前記第1記憶装置について前記第1取得部により取得された前記最小待ち量が0でない場合、前記第1記憶装置に対する入出力要求に係る処理量が前記第1所定時間に亘って前記第1記憶装置の処理性能を超えていると判定する、

付記2〜付記4のいずれか一項に記載のストレージ装置。

前記第1取得部は、前記最小待ち量として、前記最小待ち量を前記所定の性能融通単位に換算した最小待ちユニット数を取得する、

付記5に記載のストレージ装置。

前記記憶装置毎に、前記第2所定時間よりも短い時間間隔で、当該記憶装置に対する入出力要求に係る処理量の、当該記憶装置の処理性能に対する処理余り量を取得し、前記第2所定時間内に取得された前記処理余り量のうち最小のものを最小余り量として取得する第2取得部を、さらに有し、

前記第2判定部は、前記第2取得部により取得された前記最小余り量が0でない場合、前記第2記憶装置に対する入出力要求に係る処理量が前記第2所定時間に亘って前記第2記憶装置の処理性能を下回っていると判定する、

付記2〜付記6のいずれか一項に記載のストレージ装置。

前記第2取得部は、前記最小余り量として、前記最小余り量を前記所定の性能融通単位に換算した最小余りユニット数を取得する、

付記7に記載のストレージ装置。

前記記憶装置毎に、当該記憶装置が、一以上の前記第1記憶装置への前記性能融通を行なった前記第2記憶装置であり、且つ、当該記憶装置に対する入出力要求の処理待ちの生じた融通復旧対象であるか否かを判定する第3判定部と、

前記第3判定部により当該記憶装置が前記融通復旧対象であると判定された場合、前記融通復旧対象の記憶装置が他の記憶装置に融通した処理量を、前記一以上の前記第1記憶装置から前記融通復旧対象の記憶装置に復帰させる復旧処理部と、

をさらに有する、付記2〜付記8のいずれか一項に記載のストレージ装置。

前記復旧処理部は、前記一以上の前記第1記憶装置に対し融通された処理量の残量が均等もしくはほぼ均等になるように、当該処理量を前記一以上の前記第1記憶装置から前記融通復旧対象の記憶装置に復帰させる、

付記9に記載のストレージ装置。

前記記憶装置毎に、当該記憶装置に対する入出力要求に係る処理量が当該記憶装置の処理性能の所定数倍以上であるか否かを判定する第4判定部と、

当該記憶装置に対する入出力要求に係る処理量が当該記憶装置の処理性能の所定数倍以上であると前記第4判定部により判定された場合、当該記憶装置に対する入出力要求に係る処理量を超える処理余裕をもつ記憶装置から当該記憶装置への性能融通を行なう融通処理部と、

をさらに有する、付記1〜付記10のいずれか一項に記載のストレージ装置。

前記複数の記憶装置のそれぞれは、一以上の物理記憶装置を論理的に分割した複数の論理ユニットの一つである、

付記1〜付記11のいずれか一項に記載のストレージ装置。

ストレージ装置が、

複数の記憶装置に設定された優先度に基づいて決定される入出力処理量の上限値を前記記憶装置毎に算出し、

情報処理装置から受信した入出力要求に係る処理量と、算出された前記上限値とに基づいて、前記入出力要求に係る処理の実行順をスケジュールし、

スケジュールされた前記実行順で前記入出力要求に係る処理を実行し、

前記記憶装置毎に、当該記憶装置に対する入出力要求に係る処理量が第1所定時間に亘って当該記憶装置の処理性能を超えているか否かを判定し、

当該記憶装置に対する入出力要求に係る処理量が当該記憶装置の処理性能を超えていると判定された場合、当該記憶装置についての前記上限値を、所定の性能融通単位で変更する、

ことを特徴とするストレージ装置の制御方法。

前記ストレージ装置が、さらに、

前記記憶装置毎に、当該記憶装置に対する入出力要求に係る処理量が第2所定時間に亘って当該記憶装置の処理性能を下回っているか否かを判定し、

前記複数の記憶装置のうち第1記憶装置に対する入出力要求に係る処理量が前記第1所定時間に亘って前記第1記憶装置の処理性能を超えていると前記第1判定部により判定され、且つ、前記複数の記憶装置のうち第2記憶装置に対する入出力要求に係る処理量が前記第2所定時間に亘って前記第2記憶装置の処理性能を下回っていると前記第2判定部により判定された場合、前記上限値を前記所定の性能融通単位で変更することで、前記第2記憶装置から前記第1記憶装置への性能融通を前記所定の性能融通単位で行なう、

付記13に記載のストレージ装置の制御方法。

前記ストレージ装置が、さらに、

前記第1記憶装置について算出された前記上限値に、前記所定の性能融通単位に対応する値を加算するとともに、前記第2記憶装置について算出された前記上限値から、前記所定の性能融通単位に対応する値を減算するように、前記上限値を変更することで、前記第2記憶装置から前記第1記憶装置への性能融通を前記所定の性能融通単位で行なう、

付記14に記載のストレージ装置の制御方法。

前記所定の性能融通単位に対応する値は、前記優先度に基づいて決定される前記入出力処理量(性能値)の最小間隔以下である、

付記15に記載のストレージ装置の制御方法。

ストレージ装置に含まれるコンピュータに、

複数の記憶装置に設定された優先度に基づいて決定される入出力処理量の上限値を前記記憶装置毎に算出し、

情報処理装置から受信した入出力要求に係る処理量と、算出された前記上限値とに基づいて、前記入出力要求に係る処理の実行順をスケジュールし、

スケジュールされた前記実行順で前記入出力要求に係る処理を実行し、

前記記憶装置毎に、当該記憶装置に対する入出力要求に係る処理量が第1所定時間に亘って当該記憶装置の処理性能を超えているか否かを判定し、

当該記憶装置に対する入出力要求に係る処理量が当該記憶装置の処理性能を超えていると判定された場合、当該記憶装置についての前記上限値を、所定の性能融通単位で変更する、

処理を実行させる、ストレージ装置制御プログラム。

前記コンピュータに、さらに、

前記記憶装置毎に、当該記憶装置に対する入出力要求に係る処理量が第2所定時間に亘って当該記憶装置の処理性能を下回っているか否かを判定し、

前記複数の記憶装置のうち第1記憶装置に対する入出力要求に係る処理量が前記第1所定時間に亘って前記第1記憶装置の処理性能を超えていると前記第1判定部により判定され、且つ、前記複数の記憶装置のうち第2記憶装置に対する入出力要求に係る処理量が前記第2所定時間に亘って前記第2記憶装置の処理性能を下回っていると前記第2判定部により判定された場合、前記上限値を前記所定の性能融通単位で変更することで、前記第2記憶装置から前記第1記憶装置への性能融通を前記所定の性能融通単位で行なう、

処理を実行させる、付記17に記載のストレージ装置制御プログラム。

前記コンピュータに、さらに、

前記第1記憶装置について算出された前記上限値に、前記所定の性能融通単位に対応する値を加算するとともに、前記第2記憶装置について算出された前記上限値から、前記所定の性能融通単位に対応する値を減算するように、前記上限値を変更することで、前記第2記憶装置から前記第1記憶装置への性能融通を前記所定の性能融通単位で行なう、

付記18に記載のストレージ装置制御プログラム。

前記所定の性能融通単位に対応する値は、前記優先度に基づいて決定される前記入出力処理量の最小間隔以下である、

付記19に記載のストレージ装置制御プログラム。

10a,10b ホスト(情報処理装置)

100 ストレージ装置

101a〜101d HDD(一以上の物理記憶装置)

200a,200b CM

201a,201b,1010 FC−CA(ポート)

202a,202b,1020 iSCSI−CA(ポート)

203a,203b,1030 SAS

210a,210b メモリ

211a,211b キャッシュ域

212a,212b 制御域

213 QoS制御域

220a,220b,1070 CPU(コンピュータ)

303 SCSIターゲット制御部

304 SCSIコマンド制御部

501 QoS管理テーブル

502 待ちキュー格納部

503 性能設定部

504 コマンド受信部

505 算出部

506 スケジュール部

507 実行部

510 マクロ融通チェック部

511 第1取得部

512 第2取得部

520 マクロ融通処理部

521 第1判定部

522 第2判定部

523 変更部

530 マクロ融通復旧処理部

531 第3判定部

532 復旧処理部

540 ミクロ融通処理部

541 第4判定部

542 融通処理部

543 融通後処理部

1000 コンピュータ

1040 RAM

1050 フラッシュメモリ

1060 ROM

1061 ストレージ装置制御プログラム

1071 ストレージ装置制御プロセス

Claims (9)

- 複数の記憶装置に設定された優先度に基づいて決定される入出力処理量の上限値を前記記憶装置毎に算出する算出部と、

情報処理装置から受信した入出力要求に係る処理量と、前記算出部により算出された前記上限値とに基づいて、前記入出力要求に係る処理の実行順をスケジュールするスケジュール部と、

前記スケジュール部によりスケジュールされた前記実行順で前記入出力要求に係る処理を実行する実行部と、

前記記憶装置毎に、当該記憶装置に対する入出力要求に係る処理量が第1所定時間に亘って当該記憶装置の処理性能を超えているか否かを判定する第1判定部と、

当該記憶装置に対する入出力要求に係る処理量が当該記憶装置の処理性能を超えていると前記第1判定部により判定された場合、当該記憶装置についての前記上限値を、前記優先度に基づいて決定される前記入出力処理量の最小間隔以下である所定の性能融通単位で変更する変更部と、

を有する、ストレージ装置。 - 前記記憶装置毎に、当該記憶装置に対する入出力要求に係る処理量が第2所定時間に亘って当該記憶装置の処理性能を下回っているか否かを判定する第2判定部を、さらに有し、

前記複数の記憶装置のうち第1記憶装置に対する入出力要求に係る処理量が前記第1所定時間に亘って前記第1記憶装置の処理性能を超えていると前記第1判定部により判定され、且つ、前記複数の記憶装置のうち第2記憶装置に対する入出力要求に係る処理量が前記第2所定時間に亘って前記第2記憶装置の処理性能を下回っていると前記第2判定部により判定された場合、前記変更部は、前記上限値を前記所定の性能融通単位で変更することで、前記第2記憶装置から前記第1記憶装置への性能融通を前記所定の性能融通単位で行なう、

請求項1に記載のストレージ装置。 - 前記変更部は、前記第1記憶装置について算出された前記上限値に、前記所定の性能融通単位に対応する値を加算するとともに、前記第2記憶装置について算出された前記上限値から、前記所定の性能融通単位に対応する値を減算するように、前記上限値を変更することで、前記第2記憶装置から前記第1記憶装置への性能融通を前記所定の性能融通単位で行なう、

請求項2に記載のストレージ装置。 - 前記記憶装置毎に、前記第1所定時間よりも短い時間間隔で、当該記憶装置に対する入出力要求の処理待ち量を取得し、前記第1所定時間内に取得された前記処理待ち量のうち最小のものを最小待ち量として取得する第1取得部を、さらに有し、

前記第1判定部は、前記第1記憶装置について前記第1取得部により取得された前記最小待ち量が0でない場合、前記第1記憶装置に対する入出力要求に係る処理量が前記第1所定時間に亘って前記第1記憶装置の処理性能を超えていると判定する、

請求項2または請求項3に記載のストレージ装置。 - 前記記憶装置毎に、前記第2所定時間よりも短い時間間隔で、当該記憶装置に対する入出力要求に係る処理量の、当該記憶装置の処理性能に対する処理余り量を取得し、前記第2所定時間内に取得された前記処理余り量のうち最小のものを最小余り量として取得する第2取得部を、さらに有し、

前記第2判定部は、前記第2取得部により取得された前記最小余り量が0でない場合、前記第2記憶装置に対する入出力要求に係る処理量が前記第2所定時間に亘って前記第2記憶装置の処理性能を下回っていると判定する、

請求項2〜請求項4のいずれか一項に記載のストレージ装置。 - 前記記憶装置毎に、当該記憶装置が、一以上の前記第1記憶装置への前記性能融通を行なった前記第2記憶装置であり、且つ、当該記憶装置に対する入出力要求の処理待ちの生じた融通復旧対象であるか否かを判定する第3判定部と、

前記第3判定部により当該記憶装置が前記融通復旧対象であると判定された場合、前記融通復旧対象の記憶装置が他の記憶装置に融通した処理量を、前記一以上の前記第1記憶装置から前記融通復旧対象の記憶装置に復帰させる復旧処理部と、

をさらに有する、請求項2〜請求項5のいずれか一項に記載のストレージ装置。 - 前記記憶装置毎に、当該記憶装置に対する入出力要求に係る、前記第1所定時間よりも短い第3所定時間間隔における処理量が当該記憶装置の処理性能の所定数倍以上であるか否かを判定する第4判定部と、

前記複数の記憶装置のうち第3記憶装置に対する入出力要求に係る、前記第3所定時間間隔における処理量が前記第3記憶装置の処理性能の所定数倍以上であると前記第4判定部により判定された場合、前記第3記憶装置に対する入出力要求に係る処理量を超える処理余裕をもつ記憶装置から前記第3記憶装置への性能融通を行なう融通処理部と、

をさらに有する、請求項1〜請求項6のいずれか一項に記載のストレージ装置。 - ストレージ装置が、

複数の記憶装置に設定された優先度に基づいて決定される入出力処理量の上限値を前記記憶装置毎に算出し、

情報処理装置から受信した入出力要求に係る処理量と、算出された前記上限値とに基づいて、前記入出力要求に係る処理の実行順をスケジュールし、

スケジュールされた前記実行順で前記入出力要求に係る処理を実行し、

前記記憶装置毎に、当該記憶装置に対する入出力要求に係る処理量が第1所定時間に亘って当該記憶装置の処理性能を超えているか否かを判定し、

当該記憶装置に対する入出力要求に係る処理量が当該記憶装置の処理性能を超えていると判定された場合、当該記憶装置についての前記上限値を、前記優先度に基づいて決定される前記入出力処理量の最小間隔以下である所定の性能融通単位で変更する、

ことを特徴とするストレージ装置の制御方法。 - ストレージ装置に含まれるコンピュータに、

複数の記憶装置に設定された優先度に基づいて決定される入出力処理量の上限値を前記記憶装置毎に算出し、

情報処理装置から受信した入出力要求に係る処理量と、算出された前記上限値とに基づいて、前記入出力要求に係る処理の実行順をスケジュールし、

スケジュールされた前記実行順で前記入出力要求に係る処理を実行し、

前記記憶装置毎に、当該記憶装置に対する入出力要求に係る処理量が第1所定時間に亘って当該記憶装置の処理性能を超えているか否かを判定し、

当該記憶装置に対する入出力要求に係る処理量が当該記憶装置の処理性能を超えていると判定された場合、当該記憶装置についての前記上限値を、前記優先度に基づいて決定される前記入出力処理量の最小間隔以下である所定の性能融通単位で変更する、

処理を実行させる、ストレージ装置制御プログラム。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013222060A JP6213148B2 (ja) | 2013-10-25 | 2013-10-25 | ストレージ装置、ストレージ装置の制御方法およびストレージ装置制御プログラム |

| US14/493,441 US9582200B2 (en) | 2013-10-25 | 2014-09-23 | Storage apparatus, method of controlling storage apparatus, and computer-readable recording medium having stored therein storage apparatus control program |

| EP14186171.6A EP2866136B1 (en) | 2013-10-25 | 2014-09-24 | Storage apparatus, method of controlling storage apparatus, and storage apparatus control program |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013222060A JP6213148B2 (ja) | 2013-10-25 | 2013-10-25 | ストレージ装置、ストレージ装置の制御方法およびストレージ装置制御プログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015084143A JP2015084143A (ja) | 2015-04-30 |

| JP6213148B2 true JP6213148B2 (ja) | 2017-10-18 |

Family

ID=51687793

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013222060A Active JP6213148B2 (ja) | 2013-10-25 | 2013-10-25 | ストレージ装置、ストレージ装置の制御方法およびストレージ装置制御プログラム |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US9582200B2 (ja) |

| EP (1) | EP2866136B1 (ja) |

| JP (1) | JP6213148B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CA2882446A1 (en) * | 2014-02-21 | 2015-08-21 | Coho Data, Inc. | Methods, systems and devices for parallel network interface data structures with differential data storage service capabilities |

| US9411626B2 (en) * | 2014-06-18 | 2016-08-09 | International Business Machines Corporation | Optimizing runtime performance of an application workload by minimizing network input/output communications between virtual machines on different clouds in a hybrid cloud topology during cloud bursting |

| US10348490B2 (en) * | 2015-12-10 | 2019-07-09 | Ns Solutions Corporation | Information processing device, authorization system, information processing method, and recording medium |

| US10048874B1 (en) * | 2016-06-29 | 2018-08-14 | EMC IP Holding Company LLC | Flow control with a dynamic window in a storage system with latency guarantees |

| JP7225190B2 (ja) * | 2020-12-10 | 2023-02-20 | 株式会社日立製作所 | 計算機システム |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006053601A (ja) | 2004-08-09 | 2006-02-23 | Hitachi Ltd | ストレージ装置 |

| JP2008059478A (ja) * | 2006-09-01 | 2008-03-13 | Hitachi Ltd | 記憶システム及びデータ入出力制御方法 |

| JP2009087175A (ja) * | 2007-10-02 | 2009-04-23 | Hitachi Ltd | ストレージ装置、処理制御装置、及び記憶システム |

| US7653773B2 (en) | 2007-10-03 | 2010-01-26 | International Business Machines Corporation | Dynamically balancing bus bandwidth |

| JP5853569B2 (ja) * | 2011-10-12 | 2016-02-09 | 富士通株式会社 | 制御方法及びプログラム、並びにコンピュータ |

| JP5903873B2 (ja) | 2011-12-19 | 2016-04-13 | 富士通株式会社 | ストレージ装置、ストレージ装置の制御方法及びストレージ装置制御プログラム |

| EP3796169A1 (en) * | 2011-12-27 | 2021-03-24 | Netapp, Inc. | Proportional quality of service based on client usage and system metrics |

-

2013

- 2013-10-25 JP JP2013222060A patent/JP6213148B2/ja active Active

-

2014

- 2014-09-23 US US14/493,441 patent/US9582200B2/en active Active

- 2014-09-24 EP EP14186171.6A patent/EP2866136B1/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20150121020A1 (en) | 2015-04-30 |

| EP2866136A1 (en) | 2015-04-29 |

| US9582200B2 (en) | 2017-02-28 |

| JP2015084143A (ja) | 2015-04-30 |

| EP2866136B1 (en) | 2018-01-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8850152B2 (en) | Method of data migration and information storage system | |

| US10853139B2 (en) | Dynamic workload management based on predictive modeling and recommendation engine for storage systems | |

| US11792263B2 (en) | Methods and systems for managing a resource in a networked storage environment | |

| US7506101B2 (en) | Data migration method and system | |

| US9658778B2 (en) | Method and system for monitoring and analyzing quality of service in a metro-cluster | |

| KR101413899B1 (ko) | 스토리지 장치, 스토리지 장치의 제어 방법 및 기억 매체 | |

| JP6409613B2 (ja) | 情報処理装置,マルチパス制御方法及びマルチパス制御プログラム | |

| JP6213148B2 (ja) | ストレージ装置、ストレージ装置の制御方法およびストレージ装置制御プログラム | |

| JP2004246852A (ja) | 論理ボリュームコピー先性能調整方法及び装置 | |

| JP2009122873A (ja) | ストレージシステム間でのリモートコピーを管理する装置 | |

| JP6451307B2 (ja) | ストレージ装置およびストレージ装置制御プログラム | |

| US9542103B2 (en) | Method and system for monitoring and analyzing quality of service in a storage system | |

| WO2010134134A1 (en) | Storage system comprising plurality of processor units | |

| US11513849B2 (en) | Weighted resource cost matrix scheduler | |

| JP6451308B2 (ja) | ストレージ装置およびストレージ装置制御プログラム | |

| US20160085446A1 (en) | Control device and storage system | |

| WO2016080953A1 (en) | Method and apparatus for data cache in converged system | |

| US10992532B1 (en) | Automated network configuration changes for I/O load redistribution | |

| US8201018B2 (en) | Control of sparing in storage systems | |

| US8788667B2 (en) | Computer system and management method | |

| JP6255895B2 (ja) | ストレージ制御装置、およびプログラム | |

| JP6940761B2 (ja) | 情報処理装置、仮想マシン監視プログラム、および情報処理システム | |

| JP2019191886A (ja) | 情報処理装置,情報処理方法およびプログラム | |

| US9619173B1 (en) | Updating synchronization progress | |

| US20180246824A1 (en) | System provided with computer and storage apparatus and method for control of system |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160705 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170321 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170322 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170516 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170822 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170904 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6213148 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |