JP6131818B2 - キャッシュ方法、キャッシュ装置、およびコンピュータプログラム - Google Patents

キャッシュ方法、キャッシュ装置、およびコンピュータプログラム Download PDFInfo

- Publication number

- JP6131818B2 JP6131818B2 JP2013212613A JP2013212613A JP6131818B2 JP 6131818 B2 JP6131818 B2 JP 6131818B2 JP 2013212613 A JP2013212613 A JP 2013212613A JP 2013212613 A JP2013212613 A JP 2013212613A JP 6131818 B2 JP6131818 B2 JP 6131818B2

- Authority

- JP

- Japan

- Prior art keywords

- unit data

- page

- accessed

- expected value

- unit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/12—Replacement control

- G06F12/121—Replacement control using replacement algorithms

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0891—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches using clearing, invalidating or resetting means

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/12—Replacement control

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0866—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches for peripheral storage systems, e.g. disk cache

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/12—Replacement control

- G06F12/121—Replacement control using replacement algorithms

- G06F12/122—Replacement control using replacement algorithms of the least frequently used [LFU] type, e.g. with individual count value

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Memory System Of A Hierarchy Structure (AREA)

Description

1つの側面では、本件は、キャッシュヒット率を向上させることを目的とする。

〔第1の実施の形態〕

まず第1の実施の形態について説明する。

なお、図1に示す計算手段13、決定手段14、およびアクセス手段15は、例えばキャッシュ装置10が有するプロセッサにより実現することができる。また、第1の記憶手段は、例えばキャッシュ装置10が有するRAMなどのメモリにより実現することができる。さらに第2の記憶装置12は、例えばキャッシュ装置10が有するHDDにより実現することができる。

〔第2の実施の形態〕

次に第2の実施の形態について説明する。第2の実施の形態は、1階マルコフ連鎖を用いて、期待値を求めるものである。以下、第2の実施の形態の説明において単にマルコフ連鎖と呼んだ場合、1階マルコフ連鎖を指すものとする。また第2の実施の形態では、データのアクセスをページ単位で行うものとする。

図2は、第2の実施の形態に用いるコンピュータのハードウェアの一構成例を示す図である。コンピュータ100は、プロセッサ101によって装置全体が制御されている。プロセッサ101には、バス109を介してメモリ102と複数の周辺機器が接続されている。プロセッサ101は、マルチプロセッサであってもよい。プロセッサ101は、例えばCPU(Central Processing Unit)、MPU(Micro Processing Unit)、またはDSP(Digital Signal Processor)である。プロセッサ101の機能の少なくとも一部を、ASIC(Application Specific Integrated Circuit)、PLD(Programmable Logic Device)などの電子回路で実現してもよい。

図3は、キャッシュ機能を示すブロック図である。図3に示すように、HDD103には、複数のページ31が格納されている。HDD103に対しては、ページ単位でリードまたはライトのアクセスが行われる。

期待値計算部130は、遷移行列に基づいて、マルコフ連鎖における状態(ページアクセス後の状態)ごとに、その状態から別の各状態となるまでの遷移回数(実行されたアクセス回数)の期待値を計算する。期待値が大きい状態ほど、その状態に遷移するまでのページアクセス回数が多くなる可能性が高い。なお、ある状態から別の状態となるまでの遷移回数は、別の状態に対応するページがキャッシュ領域32に保持されているとき、そのページが次にアクセスされるまでキャッシュ領域を占有し続ける期間である。その占有期間は、アクセスシーケンス34上の長さで表される。そこで、ある状態から別の状態となるまでのアクセスシーケンス34上での長さを、占有シーケンス長と呼ぶこととする。以降、単に期待値と呼んだ場合も、占有シーケンス長の期待値を指すものとする。

図4は、アドレス変換表の一例を示す図である。アドレス変換表33には、ページ番号に対応付けて、HDD上のアドレスが設定されている。アクセス部150は、ページに対してアクセスする場合、アドレス変換表33を参照して、HDD103内のページとページ番号との対応関係を把握できる。例えばアクセス部150は、アプリケーションプログラムを実行するプロセスなどから、ページ番号を指定したアクセス要求を受け付けると、アドレス変換表33を参照し、指定されたページ番号に対応するHDD103のアドレスを取得する。そしてアクセス部150は、取得したアドレスに格納されたページを、HDD103から読み出す。

図5は、アクセスシーケンスの作成状況を示す図である。図5に示すように、アクセスシーケンス34は、アクセスされたページのページ番号がアクセスされた順に並べられた、期待値順位表である。

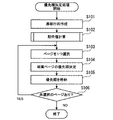

[ステップS104]優先順決定部140は、選択したページを直近のアクセス対象ページとした場合の、HDD103内の各ページの占有シーケンス長の期待値に基づいて、キャッシュ領域32から破棄するページの優先順を決定する。

[ステップS106]優先順決定部140は、未選択のページがあるか否かを判断する。未選択のページがあれば、処理がステップS103に進められる。すべてのページが選択済みであれば、優先順決定処理が終了する。

次に、マルコフ連鎖の遷移行列の生成方法について詳細に説明する。

図7は、マルコフ連鎖を説明する図である。ここでマルコフ連鎖により、ある状態i(iは1以上の整数)の次に状態j(jは1以上の整数)に遷移する確率を、確率aijとする。例えば、ページAが読み込まれた状態を状態iとし、他のページBが読み込まれた状態を状態jとし、ページAが読み込まれた状態で、次にページBが読み込まれる確率が、確率aijである。

図8は、期待値計算手順の一例を示す図である。

[ステップS112]期待値計算部130は、遷移行列Aの第k列のすべての成分を「0」に変更した行列Bを生成する。

このようにして、占有シーケンス長の期待値が計算される。

図10は、方程式による期待値の計算例を示す図である。図10に示すマルコフ連鎖の状態遷移図43には、2つの状態がある。この状態遷移図43によれば、HDD103内に2つのページがある。そして、ページ番号「1」のページにアクセスされた場合、確率「1/3」で、再度、次にページ番号「1」のページにアクセスされ、確率「2/3」で、次にページ番号「2」のページにアクセスされる。ページ番号「2」のページにアクセスされた場合、確率「1」で、次にページ番号「1」のページにアクセスされる。

図12は、ページのアクセス処理の手順を示すフローチャートの一例である。

[ステップS124]アクセス部150は、HDD103から、取得したアドレスaの位置のページを読み出し、キャッシュ領域32に格納する。

図13は、LRUとのキャッシュアルゴリズムの違いを説明する図である。図13に示すマルコフ連鎖の状態遷移図44には8つの状態がある。すなわちHDD103に8つのページが格納されている場合を想定している。ここで、8つのページをページ番号順に並べ、ページ番号「8」のページの次を、ページ番号「1」のページとする。このとき、各ページがアクセスされたとき、ページ番号順で1つ後のページが次にアクセスされる確率が「a」である。またページ番号で3つ前のページが次にアクセスされる確率が「b」である。さらにページ番号で2つ前のページに次にアクセスされる確率が「c」である。またaはbより大きく、bはcより大きい(a≫b≫c)ものとする。そして、キャッシュ領域32には、ページ番号「6」、「7」、「8」それぞれのページが格納されているものとする。このような状況下で、ページ番号「1」のページがアクセスされ、HDD103からそのページが読み込まれたものとする。

次に第3の実施の形態について説明する。第3の実施の形態は、高階マルコフ連鎖を用いて、キャッシュ領域から破棄するページを決定するものである。以下、第3の実施の形態における、第2の実施の形態との相違点について説明する。なお、第3の実施の形態を実現するためのハードウェアやキャッシュ機能の構成は、図2,図3に示した第2の実施の形態の構成と同様である。

次に第4の実施の形態について説明する。第4の実施の形態は、占有シーケンス長の期待値を、近似値で求め、計算負荷を軽減するものである。

第2〜第4の実施の形態では、HDD103内のデータをメモリ102にキャッシュする例であるが、他の記憶装置の組み合わせに対しても、上記各実施の形態に示したキャッシュアルゴリズムを適用可能である。例えば、アクセス速度の異なる複数の半導体メモリを有するシステムにおいて、高速にアクセス可能な半導体メモリをキャッシュとして使用する場合にも、各実施の形態に示したキャッシュアルゴリズムを適用できる。さらにネットワークを介して接続された他のコンピュータから取得したデータを、キャッシュする場合にも、各実施の形態に示したキャッシュアルゴリズムを適用できる。またHDD103に代えてSSD(Solid State Drive)を用いることもできる。

11 第1の記憶装置

11a キャッシュ領域

11b 状態遷移図

11c 期待値表

12 第2の記憶装置

13 計算手段

14 決定手段

15 アクセス手段

Claims (10)

- アクセス可能な複数の単位データの一部を記憶装置内のキャッシュ領域に保持する処理をコンピュータに実行させるコンピュータプログラムにおいて、

前記コンピュータに、

前記複数の単位データそれぞれがアクセスされたときに、次にアクセスされる可能性のある単位データについての、次にアクセスされる確率に基づいて、前記複数の単位データのうちの2つの単位データからなる組それぞれについて、一方の単位データがアクセスされた後に他方の単位データがアクセスされるまでのアクセス回数として期待される値を計算し、

単位データへのアクセス要求に応じて、前記キャッシュ領域外から該単位データが読み出された場合、該単位データがアクセスされた後に前記複数の単位データそれぞれがアクセスされるまでのアクセス回数として期待される値に基づいて、前記キャッシュ領域から破棄する単位データを決定する、

処理を実行させるコンピュータプログラム。 - 期待される値の計算では、前記複数の単位データそれぞれがアクセスされたときに、次にアクセスされる可能性のある単位データについての、次にアクセスされる確率に基づいて、遷移行列を生成し、前記遷移行列を用いた行列計算により、期待される値を算出することを特徴とする請求項1記載のコンピュータプログラム。

- 破棄する単位データの決定では、期待される値が最も大きい単位データを破棄するものと決定することを特徴とする請求項1または2記載のコンピュータプログラム。

- 前記コンピュータに、さらに、

前記複数の単位データそれぞれについての、他の単位データがアクセスされた後にアクセスされるまでのアクセス回数の期待値に基づいて、前記複数の単位データそれぞれについて、該単位データが前記キャッシュ領域外から読み出されたときの他の単位データの破棄の優先順を決定し、決定した優先順を前記記憶装置に格納する処理を実行させ、

破棄する単位データの決定では、前記キャッシュ領域外から単位データが読み出されたとき、該単位データが読み出されたときの破棄の優先順に基づいて、破棄する単位データを決定する、

ことを特徴とする請求項1乃至3のいずれかに記載のコンピュータプログラム。 - 優先順の格納では、期待される値が小さい方から所定数の単位データの識別情報を、破棄の優先順に沿って並べ、並べられた識別情報を格納し、

破棄する単位データの決定では、前記キャッシュ領域外から単位データが読み出されたとき、該単位データが読み出されたときの破棄の優先順が示されていない単位ページが前記キャッシュ領域にあれば、該単位データを破棄対象に決定し、該単位ページがなければ、前記キャッシュ領域に保持された単位ページのうち、優先順が最も高い単位データを破棄対象に決定する、

ことを特徴とする請求項4記載のコンピュータプログラム。 - 期待される値の計算では、単位データへのアクセスを状態遷移としたマルコフ連鎖における遷移確率に基づいて期待される値を計算することを特徴とする請求項1乃至5のいずれかに記載のコンピュータプログラム。

- 期待される値の計算では、所定数の単位データへの複数回のアクセスを状態遷移とした高階のマルコフ連鎖における遷移確率に基づいて期待される値を計算することを特徴とする請求項6記載のコンピュータプログラム。

- 期待される値の計算では、期待される値を近似的に求めることを特徴とする請求項1乃至7のいずれかに記載のコンピュータプログラム。

- アクセス可能な複数の単位データの一部を記憶装置内のキャッシュ領域に保持する処理をコンピュータで実行するキャッシュ方法において、

前記コンピュータが、

前記複数の単位データそれぞれがアクセスされたときに、次にアクセスされる可能性のある単位データについての、次にアクセスされる確率に基づいて、前記複数の単位データのうちの2つの単位データからなる組それぞれについて、一方の単位データがアクセスされた後に他方の単位データがアクセスされるまでのアクセス回数として期待される値を計算し、

単位データへのアクセス要求に応じて、前記キャッシュ領域外から該単位データが読み出された場合、該単位データがアクセスされた後に前記複数の単位データそれぞれがアクセスされるまでのアクセス回数として期待される値に基づいて、前記キャッシュ領域から破棄する単位データを決定する、

キャッシュ方法。 - アクセス可能な複数の単位データの一部を記憶装置内のキャッシュ領域に保持するキャッシュ装置において、

前記複数の単位データそれぞれがアクセスされたときに、次にアクセスされる可能性のある単位データについての、次にアクセスされる確率に基づいて、前記複数の単位データのうちの2つの単位データからなる組それぞれについて、一方の単位データがアクセスされた後に他方の単位データがアクセスされるまでのアクセス回数として期待される値を計算する計算手段と、

単位データへのアクセス要求に応じて、前記キャッシュ領域外から該単位データが読み出された場合、該単位データがアクセスされた後に前記複数の単位データそれぞれがアクセスされるまでのアクセス回数として期待される値に基づいて、前記キャッシュ領域から破棄する単位データを決定する決定手段と、

を有するキャッシュ装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013212613A JP6131818B2 (ja) | 2013-10-10 | 2013-10-10 | キャッシュ方法、キャッシュ装置、およびコンピュータプログラム |

| US14/494,217 US9824028B2 (en) | 2013-10-10 | 2014-09-23 | Cache method and cache apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013212613A JP6131818B2 (ja) | 2013-10-10 | 2013-10-10 | キャッシュ方法、キャッシュ装置、およびコンピュータプログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015075978A JP2015075978A (ja) | 2015-04-20 |

| JP6131818B2 true JP6131818B2 (ja) | 2017-05-24 |

Family

ID=52810655

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013212613A Expired - Fee Related JP6131818B2 (ja) | 2013-10-10 | 2013-10-10 | キャッシュ方法、キャッシュ装置、およびコンピュータプログラム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9824028B2 (ja) |

| JP (1) | JP6131818B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP3101549B1 (en) * | 2015-06-04 | 2018-09-26 | Tata Consultancy Services Limited | Estimating cache size for cache routers in information centric networks |

| KR102036419B1 (ko) * | 2017-12-27 | 2019-10-24 | 충북대학교 산학협력단 | 그래프 처리 성능 향상을 위한 복수 계층 캐싱 방법 및 복수 계층 캐싱 시스템 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0256653A (ja) * | 1988-08-23 | 1990-02-26 | Toshiba Corp | 階層化メモリ管理方式 |

| JPH02219147A (ja) * | 1989-02-21 | 1990-08-31 | Mitsubishi Electric Corp | 高速緩衝記憶装置 |

| JP3707854B2 (ja) * | 1996-03-01 | 2005-10-19 | 株式会社東芝 | キャッシュ機能を有するコンピュータ及びキャッシュメモリ制御方法 |

| WO1999060564A2 (en) | 1998-05-15 | 1999-11-25 | Storage Technology Corporation | Caching method for data blocks of variable size |

| US6678805B1 (en) * | 2000-05-25 | 2004-01-13 | Microsoft Corporation | Structure organization for improved cache performance |

| US6738865B1 (en) | 2000-06-09 | 2004-05-18 | International Business Machines Corporation | Method, system, and program for demoting data from cache based on least recently accessed and least frequently accessed data |

| JP4500850B2 (ja) * | 2007-12-27 | 2010-07-14 | 富士通株式会社 | 制御装置,ストレージシステム,及びメモリ制御方法 |

-

2013

- 2013-10-10 JP JP2013212613A patent/JP6131818B2/ja not_active Expired - Fee Related

-

2014

- 2014-09-23 US US14/494,217 patent/US9824028B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20150106570A1 (en) | 2015-04-16 |

| US9824028B2 (en) | 2017-11-21 |

| JP2015075978A (ja) | 2015-04-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN114253458B (zh) | 内存缺页异常的处理方法、装置、设备及存储介质 | |

| JP5460486B2 (ja) | データをソートする装置及び方法 | |

| US10684832B2 (en) | Code placement using a dynamic call graph | |

| US9471497B2 (en) | Methods for combining access history and sequentiality for intelligent prefetching and devices thereof | |

| CN104063330B (zh) | 数据预取方法及装置 | |

| CN107220188B (zh) | 一种自适应缓冲块替换方法 | |

| CN105302830B (zh) | 一种地图瓦片缓存方法及装置 | |

| JP6402647B2 (ja) | データ配置プログラム、データ配置装置およびデータ配置方法 | |

| CN116910314B (zh) | 基于键值分离的键值存储系统中范围查询优化方法及装置 | |

| CN113127382A (zh) | 用于追加写的数据读取方法、装置、设备和介质 | |

| US11281588B2 (en) | Method, apparatus and computer program product for managing I/O operation using prediction model to predict storage area to be accessed | |

| CN104021226B (zh) | 预取规则的更新方法及装置 | |

| CN117130663B (zh) | 一种指令读取方法及l2指令缓存、电子设备和存储介质 | |

| JP6131818B2 (ja) | キャッシュ方法、キャッシュ装置、およびコンピュータプログラム | |

| JP5447523B2 (ja) | データ処理装置、データ記録方法、データ記録プログラム | |

| CN118210739A (zh) | 多级缓存管理方法、设备及计算机可读存储介质 | |

| JP2013218636A (ja) | クラスタリング処理装置、クラスタリング処理方法、及びプログラム | |

| JP5278538B2 (ja) | コンパイルシステム、コンパイル方法およびコンパイルプログラム | |

| JP6394231B2 (ja) | データ配置制御プログラム、データ配置制御装置およびデータ配置制御方法 | |

| CN103761052B (zh) | 一种管理高速缓存的方法及存储装置 | |

| CN118820311B (zh) | 键值缓存方法、文本解码方法、装置以及计算机存储介质 | |

| JP6194875B2 (ja) | キャッシュ装置、キャッシュシステム、キャッシュ方法、及びキャッシュプログラム | |

| JP2023505783A (ja) | Gpuパケット集約システム | |

| JP2018511131A (ja) | オンライン媒体のための階層的なコストベースのキャッシング | |

| JP6112193B2 (ja) | アクセス制御プログラム、ディスク装置及びアクセス制御方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160606 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170308 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170321 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170403 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6131818 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |