JP6089891B2 - 演算処理装置、情報処理装置及び情報処理装置の制御方法 - Google Patents

演算処理装置、情報処理装置及び情報処理装置の制御方法 Download PDFInfo

- Publication number

- JP6089891B2 JP6089891B2 JP2013074711A JP2013074711A JP6089891B2 JP 6089891 B2 JP6089891 B2 JP 6089891B2 JP 2013074711 A JP2013074711 A JP 2013074711A JP 2013074711 A JP2013074711 A JP 2013074711A JP 6089891 B2 JP6089891 B2 JP 6089891B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- arithmetic processing

- unit

- taken out

- cluster

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0804—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches with main memory updating

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0806—Multiuser, multiprocessor or multiprocessing cache systems

- G06F12/0815—Cache consistency protocols

- G06F12/0817—Cache consistency protocols using directory methods

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0806—Multiuser, multiprocessor or multiprocessing cache systems

- G06F12/0811—Multiuser, multiprocessor or multiprocessing cache systems with multilevel cache hierarchies

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/10—Providing a specific technical effect

- G06F2212/1016—Performance improvement

- G06F2212/1024—Latency reduction

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2212/00—Indexing scheme relating to accessing, addressing or allocation within memory systems or architectures

- G06F2212/10—Providing a specific technical effect

- G06F2212/1028—Power efficiency

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Memory System Of A Hierarchy Structure (AREA)

Description

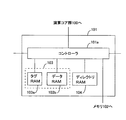

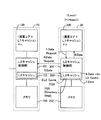

図1は、比較例に係る情報処理装置1における一部のクラスタ構成を示す。図1に示すように、クラスタ10は、演算コアとL1キャッシュの組をn組(nは自然数)有する演算コア群100、L2キャッシュ制御部101、メモリ102を有する。L2キャッシュ制御部101はL2キャッシュ103を有する。クラスタ20、30も、クラスタ10と同様、演算コア群200、300、L2キャッシュ制御部201、301、メモリ202、302、L2キャッシュ203、303をそれぞれ有する。

するクラスタをホーム(Home)と呼ぶ。さらに、ローカルでないクラスタをリモート(Remote)と呼ぶ。各クラスタは、データの要求元及び要求先に応じて、ローカルにもホームにもリモートにもなる。また、あるデータ取得要求の処理において、ローカルのクラスタは、ホームのクラスタを兼ねる場合がある。また、リモートのクラスタが、ホームのクラスタを兼ねる場合もある。さらに、ホームのクラスタが管理するホームのメモリに格納されているデータの状態情報をディレクトリ情報と呼ぶ。これらの詳細については後述する。

コントローラ201aに対して、当該データのデータ取得要求を行う。

コントローラ101aは、データRAM103bから当該データを取得する。そして、コントローラ101aは、当該データをクラスタ20のL2キャッシュ制御部201のコントローラ201aに送る。

って、この場合でも、ディレクトリRAMを参照する処理の分、情報処理装置の性能が低下し、データ取得に伴うレイテンシが発生し、消費電力も増加する可能性がある。

クラスタ50が自身のメモリ502へのアクセスを処理する際に、カウンタ501bの値が0であるとする。これは、ディレクトリRAM504に「他(リモート)のクラスタに持ち出されていることを示すエントリ」が存在しないことを示す。そこで、クラスタ50では、ディレクトリRAM504の参照処理が省略され、メモリ502に対するデータ要求が実行される。

の2つのモードを有する。具体的には、「モードオン」とは、各クラスタ内のカウンタの動作を有効にする動作モードである。また、「モードオフ」とは、各クラスタ内のカウンタの動作を無効にする動作モードである。なお、これらの動作モードにおける処理の詳細については後述する。本実施例では、情報処理装置2において、情報処理装置2のOS(Operating System)の起動前やアプリケーションの実行前に動作モードの切り換えを行う。さらに、本実施例では、情報処理装置2のOSがモードレジスタ80の動作モードの切り換えを制御する。なお、動作モードの切り換えは、情報処理装置2のユーザが明示的にOSに指示をして行ってもよいし、実行するアプリケーションのメモリ使用量等の情報に基づいてOSが自律的に行ってもよい。

また、クラスタ70によるデータ取得が排他的でない場合は、ディレクトリRAM504に記憶されるタイプコードはSharedである。また、クラスタ70において持ち出されたデータの内容が変更された場合、ディレクトリRAM504にはModifiedのタイプコードが記憶される。すなわち、メモリ502内のデータが他のクラスタに持ち出されたときに、ディレクトリRAM504に記憶されるタイプコードはInvalid以外である。そして、ク

ラスタ70から当該データがクラスタ50に戻されるとき、ディレクトリRAM504に記憶されるタイプコードはInvalidである。

、すなわち、いずれの入力もタイプコードがInvalidである場合に「0」を出力する。

bは、この指示信号に従って現在の値をインクリメントする。上述の通り、ここで「モードオン」とは、モードレジスタ80によってカウンタ501bの動作が有効にされている場合をいう。また、ANDゲート501hは、モードレジスタ80により動作モードが「モードオン」にされ、ORゲート501cの出力が「1」であり、ORゲート501dの出力がインバータ501fで反転されて「1」となる場合に指示信号CountDownを出力す

る。カウンタ501bは、この指示信号に従って現在の値をデクリメントする。

要求する。

ある。そのため、ORゲート501cは「0」を出力する。一方、更新後のディレクトリ情報は、当該データがリモートのクラスタ70に持ち出されていることを示す。すなわち、リモートのクラスタ70に関する当該データのタイプコードはSharedあるいはExclusiveである。したがって、ORゲート501dは「1」を出力する。

fからともに「0」が入力される。このため、ANDゲート501hから指示信号CountDownは出力されない。

cは「1」を出力する。一方、更新後のディレクトリ情報は、当該データが他のいずれのクラスタにも持ち出されていないことを示す。すなわち、リモートのクラスタに関する当該データのタイプコードは、いずれもInvalidである。したがって、ORゲート501d

は「0」を出力する。

本実施例においては、クラスタ50の動作モードが「モードオフ」である場合は、上記の比較例に従って、ディレクトリRAM504へのアクセスやメモリ502へのアクセスが

実行される。また、クラスタ50の動作モードが「モードオン」である場合は、クラスタ50に対してデータ取得処理が発生したときに、カウンタ501bの値が0であると、ディレクトリRAM504へのアクセスが発生しない。そして、メモリ502へのアクセスが発生し、データ取得要求により要求されているデータがメモリ502から取得される。

グチャートである。以下の説明において、チャート内のステップをSと略記する。S101において、コントローラ501aは、演算コア群500からメモリ502に格納されるデータのデータ要求を受信する。当該データ要求には、要求するデータの格納先を示すアドレス、すなわちメモリ502内の当該データの格納先を示すアドレスも含まれる。S102において、コントローラ501aは、タグRAM503aに対して、当該アドレスがデータ格納先であるデータがデータRAM503bに存在するか否かを確認する。S103において、タグRAM503aは、当該データはデータRAM503bにない(miss)ことをコントローラ501aに通知する。

十ビットで収まると考えられる。すなわち、カウンタ501bに用いる容量は、ディレクトリRAM504の容量に比べて小さい容量で構成することができる。したがって、カウンタ501bの参照処理に伴う情報処理量は、比較例において発生するディレクトリRAM504の参照処理に伴う情報処理量に比べて小さいと考えられる。また、カウンタ501bを設けることによって生じる消費電力量が、ディレクトリRAM504の参照処理を省略することにより実現される消費電力の削減量を上回らないとも言える。

きに、コントローラは、カウンタをインクリメントする。そして、その逆の遷移の場合は、コントローラは、カウンタをデクリメントする。なお、ディレクトリRAMから一度に読み出されるエントリ群とカウント処理における複数エントリ単位とを対応付けると、コントローラは、カウント処理を効率よく制御することができる。

コントローラ501a返す。この結果は、実質的に、ディレクトリRAM504において要求されているデータに関するディレクトリ情報がないことを意味する。そして、コントローラ501aは、当該結果を受け取ると、メモリ502に対するデータ要求を行う。このため、実質的に、コントローラ501aはディレクトリRAM504のディレクトリ情報の参照処理を省略して、メモリ502からデータを取得する。なお、NANDゲート501oとセレクタ501pがデータ使用状況通知部の一例に相当する。

クトリRAM804が属するクラスタ(図示せず)のメモリ(図示せず)の物理アドレス空間の前半部分のディレクトリ情報(前半アドレス)を管理する領域を有する。さらに、ディレクトリRAM804は、当該メモリの物理アドレス空間の後半部分のディレクトリ情報(後半アドレス)を管理する別の領域を有する。そして、クラスタ内のコントローラ(図示せず)は、カウンタ801bを制御して、ディレクトリRAM804の上記の前半アドレスに対応するディレクトリ情報を対象にカウント処理を行う。また、コントローラは、カウンタ901bを制御して、ディレクトリRAM804の上記の後半アドレスに対応するディレクトリ情報を対象にカウント処理を行う。なお、カウンタ801b、901bの値のインクリメント処理及びデクリメント処理は、上記の実施例と同様であるため、詳細な説明は省略する。

コンピュータその他の機械、装置(以下、コンピュータ等)に上記情報処理装置の設定を行うための管理ツール、OSその他を実現させるプログラムをコンピュータ等が読み取り可能な記録媒体に記録することができる。ここで、設定とは、例えばレジスタの設定等を意味する。そして、コンピュータ等に、この記録媒体のプログラムを読み込ませて実行させることにより、その機能を提供させることができる。ここで、コンピュータは、例えば、クラスタやコントローラ等である。

他の演算処理装置に接続される演算処理装置において、

自身が管理する第1のデータと他の演算処理装置から取得した第2のデータとを用いて演算処理する演算処理部と、

前記第1のデータを記憶するメモリ部と、

前記第1のデータが他の演算処理装置に持ち出されているか否かを示すデータ使用状況を記憶するデータ使用状況記憶部と、前記データ使用状況記憶部に記憶されたデータ使用状況について、前記第1のデータが他の演算処理装置に持ち出されている状態と前記第1のデータが他の演算処理装置に持ち出されていない状態との間の遷移を示す指標部とを有し、前記指標部が、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す場合に、前記第1のデータを取得する要求が発生したときに、前記データ使用状況記憶部に対するデータ使用状況の参照を省略する制御部と、

を有することを特徴とする演算処理装置。

前記演算処理装置が、前記指標部の動作を動作状態に設定する設定部をさらに有し、

前記設定部によって前記指標部が動作状態に設定されている場合に、前記指標部は前記遷移を示す

ことを特徴とする付記1に記載の演算処理装置。

前記指標部は、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す基準値からの指標値の増減によって前記遷移を示し、前記第1のデータが他の演算処理装置に持ち出されていない状態から他の演算処理装置に持ち出されている状態に遷移するときに前記指標値をインクリメントし、前記第1のデータが他の演算処理装置に持ち出されている状態から他の演算処理装置に持ち出されていない状態に遷移するときに前記指標値をデクリメントすることを特徴とする付記1又は付記2に記載の演算処理装置。

前記演算処理装置は、前記指標部を複数有し、

前記演算処理装置において、各指標部は、前記メモリ部に記憶されるそれぞれ異なるデータのデータ使用状況について、他の演算処理装置に持ち出されている状態と他の演算処理装置に持ち出されていない状態との間の遷移を示す

ことを特徴とする付記1から付記3のいずれかに記載の演算処理装置。

前記演算処理装置は、前記制御部に所定の信号を供給する信号処理部をさらに有し、

前記制御部は、前記所定の信号に従って前記データ使用状況記憶部を参照し、

前記信号処理部は、前記指標部が、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す場合に、前記第1のデータを取得する要求が発生したときに、前記制御部に対する前記所定の信号の供給を停止する

ことを特徴とする付記1から付記4のいずれかに記載の演算処理装置。

前記指標部が、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す場合に、前記第1のデータを取得する要求が発生したときに、前記データ使用状況記憶部には前記要求された第1のデータに関するデータ使用状況が存在しないことを前記制御部に通知するデータ使用状況通知部をさらに有することを特徴とする付記1から付記4のいずれかに記載の演算処理装置。

他の演算処理装置と、前記他の演算処理装置に接続される演算処理装置とを有する情報処理装置において、

前記演算処理装置は、

自身が管理する第1のデータと他の演算処理装置から取得した第2のデータとを用いて演算処理する演算処理部と、

前記第1のデータを記憶するメモリ部と、

前記第1のデータが他の演算処理装置に持ち出されているか否かを示すデータ使用状況を記憶するデータ使用状況記憶部と、前記データ使用状況記憶部に記憶されたデータ使用状況について、前記第1のデータが他の演算処理装置に持ち出されている状態と前記第1のデータが他の演算処理装置に持ち出されていない状態との間の遷移を示す指標部とを有し、前記指標部が、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す場合に、前記第1のデータを取得する要求が発生したときに、前記データ使用状況記憶部に対するデータ使用状況の参照を省略する制御部と、

を有する

ことを特徴とする情報処理装置。

前記演算処理装置が、前記指標部の動作を動作状態に設定する設定部をさらに有し、

前記設定部によって前記指標部が動作状態に設定されている場合に、前記指標部は前記遷移を示す

ことを特徴とする付記7に記載の情報処理装置。

前記指標部は、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す基準値からの指標値の増減によって前記遷移を示し、前記第1のデータが他の演算処理装置に持ち出されていない状態から他の演算処理装置に持ち出されている状態に遷移するときに前記指標値をインクリメントし、前記第1のデータが他の演算処理装置に持ち出されている状態から他の演算処理装置に持ち出されていない状態に遷移するときに前記指標値をデクリメントすることを特徴とする付記7又は付記8に記載の情報処理装置。

前記演算処理装置は、前記指標部を複数有し、

前記演算処理装置において、各指標部は、前記メモリ部に記憶されるそれぞれ異なるデータのデータ使用状況について、他の演算処理装置に持ち出されている状態と他の演算処理装置に持ち出されていない状態との間の遷移を示す

ことを特徴とする付記7から付記9のいずれかに記載の情報処理装置。

前記演算処理装置は、前記制御部に所定の信号を供給する信号処理部をさらに有し、

前記制御部は、前記所定の信号に従って前記データ使用状況記憶部を参照し、

前記信号処理部は、前記指標部が、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す場合に、前記第1のデータを取得する要求が発生したときに、前記制御部に対する前記所定の信号の供給を停止する

ことを特徴とする付記7から付記10のいずれかに記載の情報処理装置。

前記指標部が、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す場合に、前記第1のデータを取得する要求が発生したときに、前記データ使用状況記憶部には前記要求された第1のデータに関するデータ使用状況が存在しないことを前記制御部に通知するデータ使用状況通知部をさらに有することを特徴とする付記7から付記10のいずれかに記載の情報処理装置。

他の演算処理装置と、前記他の演算処理装置に接続されるとともに、自身が管理する第1のデータと他の演算処理装置から取得した第2のデータとを用いて演算処理を行う演算処理部と、前記第1のデータを記憶するメモリ部とを含む演算処理装置とを有する情報処理装置の制御方法において、

前記演算処理装置が有するデータ使用状況記憶部が、前記第1のデータが他の演算処理装置に持ち出されているか否かを示すデータ使用状況を記憶し、

前記演算処理装置が有する指標部が、前記データ使用状況記憶部に記憶されたデータ使用状況について、前記第1のデータが他の演算処理装置に持ち出されている状態と前記第1のデータが他の演算処理装置に持ち出されていない状態との間の遷移を示し、

前記演算処理装置が有する制御部が、前記指標部が、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す場合に、前記第1のデータを取得する要求が発生したときに、前記データ使用状況記憶部に対するデータ使用状況の参照を省略することを特徴とする情報処理装置の制御方法。

前記演算処理装置が有する設定部が、前記指標部の動作を動作状態に設定し、

前記設定部が前記指標部を動作状態に設定した場合に、前記指標部は前記遷移を示す

ことを特徴とする付記13に記載の情報処理装置の制御方法。

前記指標部は、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す基準値からの指標値の増減によって前記遷移を示し、前記第1のデータが他の演算処理装置に持ち出されていない状態から他の演算処理装置に持ち出されている状態に遷移するときに前記指標値をインクリメントし、前記第1のデータが他の演算処理装置に持ち出されている状態から他の演算処理装置に持ち出されていない状態に遷移するときに前記指標値をデクリメントすることを特徴とする付記13又は付記14に記載の情報処理装置の制御方法。

前記演算処理装置は、前記指標部を複数有し、

前記演算処理装置において、各指標部は、前記メモリ部に記憶されるそれぞれ異なるデータのデータ使用状況について、他の演算処理装置に持ち出されている状態と他の演算処理装置に持ち出されていない状態との間の遷移を示す

ことを特徴とする付記13から付記15のいずれかに記載の情報処理装置の制御方法。

前記演算処理装置が有する信号処理部が、前記制御部に所定の信号を供給し、

前記制御部は、前記所定の信号に従って前記データ使用状況記憶部を参照し、

前記信号処理部は、前記指標部が、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す場合に、前記第1のデータを取得する要求が発生したときに、前記制御部に対する前記所定の信号の供給を停止する

ことを特徴とする付記13から付記16のいずれかに記載の情報処理装置の制御方法。

前記演算処理装置が有するデータ使用状況通知部が、前記指標部が前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す場合に、前記第1のデータを取得する要求が発生したときに、前記データ使用状況記憶部には該データに関するデータ使用状況が存在しないことを前記記憶制御部に通知することを特徴とする付記13から付記16のいずれかに記載の情報処理装置の制御方法。

10、20、30、50、60、70 クラスタ

80 モードレジスタ

100、200、300、500、600、700 演算コア群

101、201、301、501、601、701 L2キャッシュ制御部

102、202、302、502、602、702 メモリ

103、203、303、503、603、703 L2キャッシュ

101a、201a、301a、501a、601a コントローラ

501b、801b、901b カウンタ

103a、203a、503a、603a タグRAM

103b、203b、503b、603b データRAM

104、204、504、604、804 ディレクトリRAM

501p セレクタ

Claims (7)

- 他の演算処理装置に接続される演算処理装置において、

自身が管理する第1のデータと他の演算処理装置から取得した第2のデータとを用いて演算処理する演算処理部と、

前記第1のデータを記憶するメモリ部と、

前記第1のデータが他の演算処理装置に持ち出されているか否かを示すデータ使用状況を記憶するデータ使用状況記憶部と、前記データ使用状況記憶部に記憶されたデータ使用状況について、前記第1のデータが他の演算処理装置に持ち出されている状態と前記第1のデータが他の演算処理装置に持ち出されていない状態との間の遷移を示す指標部とを有し、

自身が実行するアプリケーションごとに前記指標部の動作を有効にする第1のモードまたは前記指標部の動作を無効にする第2のモードを設定する設定部と、

前記設定部が前記第1のモードに設定し、さらに前記指標部が、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す場合に、前記第1のデータを取得する要求が発生したときに、前記データ使用状況記憶部に対するデータ使用状況の参照を省略する制御部と、

を有することを特徴とする演算処理装置。 - 前記指標部は、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す基準値からの指標値の増減によって前記遷移を示し、前記第1のデータが他の演算処理装置に持ち出されていない状態から他の演算処理装置に持ち出されている状態に遷移するときに前記指標値をインクリメントし、前記第1のデータが他の演算処理装置に持ち出されている状態から他の演算処理装置に持ち出されていない状態に遷移するときに前記指標値をデクリメントすることを特徴とする請求項1に記載の演算処理装置。

- 前記演算処理装置は、前記指標部を複数有し、

前記演算処理装置において、各指標部は、前記メモリ部に記憶されるそれぞれ異なるデータのデータ使用状況について、他の演算処理装置に持ち出されている状態と他の演算処理装置に持ち出されていない状態との間の遷移を示す

ことを特徴とする請求項1または請求項2に記載の演算処理装置。 - 前記演算処理装置は、前記制御部に所定の信号を供給する信号処理部をさらに有し、

前記制御部は、前記所定の信号に従って前記データ使用状況記憶部を参照し、

前記信号処理部は、前記指標部が、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す場合に、前記第1のデータを取得する要求が発生したときに、前記制御部に対する前記所定の信号の供給を停止する

ことを特徴とする請求項1から請求項3のいずれか1項に記載の演算処理装置。 - 前記指標部が、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す場合に、前記第1のデータを取得する要求が発生したときに、前記データ使用状況記憶部には前記要求された第1のデータに関するデータ使用状況が存在しないことを前記制御部に通知するデータ使用状況通知部をさらに有することを特徴とする請求項1から請求項3のいずれか1項に記載の演算処理装置。

- 他の演算処理装置と、前記他の演算処理装置に接続される演算処理装置とを有する情報処理装置において、

前記演算処理装置は、

自身が管理する第1のデータと他の演算処理装置から取得した第2のデータとを用いて演算処理する演算処理部と、

前記第1のデータを記憶するメモリ部と、

前記第1のデータが他の演算処理装置に持ち出されているか否かを示すデータ使用状況を記憶するデータ使用状況記憶部と、前記データ使用状況記憶部に記憶されたデータ使用状況について、前記第1のデータが他の演算処理装置に持ち出されている状態と前記第1のデータが他の演算処理装置に持ち出されていない状態との間の遷移を示す指標部と、自身が実行するアプリケーションごとに前記指標部の動作を有効にする第1のモードまたは前記指標部の動作を無効にする第2のモードを設定する設定部とを有し、前記設定部が前記第1のモードに設定し、さらに前記指標部が、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す場合に、前記第1のデータを取得する要求が発生したときに、前記データ使用状況記憶部に対するデータ使用状況の参照を省略する制御部と、

を有する

ことを特徴とする情報処理装置。 - 他の演算処理装置と、前記他の演算処理装置に接続されるとともに、自身が管理する第1のデータと他の演算処理装置から取得した第2のデータとを用いて演算処理を行う演算処理部と、前記第1のデータを記憶するメモリ部とを含む演算処理装置とを有する情報処理装置の制御方法において、

前記演算処理装置が有するデータ使用状況記憶部が、前記第1のデータが他の演算処理装置に持ち出されているか否かを示すデータ使用状況を記憶し、

前記演算処理装置が有する指標部が、前記データ使用状況記憶部に記憶されたデータ使用状況について、前記第1のデータが他の演算処理装置に持ち出されている状態と前記第1のデータが他の演算処理装置に持ち出されていない状態との間の遷移を示し、

前記演算処理装置が有する設定部が、自身が実行するアプリケーションごとに前記指標部の動作を有効にする第1のモードまたは前記指標部の動作を無効にする第2のモードを設定し、

前記演算処理装置が有する制御部が、前記設定部が前記第1のモードに設定し、さらに前記指標部が、前記第1のデータがいずれも他の演算処理装置に持ち出されていない状態を示す場合に、前記第1のデータを取得する要求が発生したときに、前記データ使用状況記憶部に対するデータ使用状況の参照を省略することを特徴とする情報処理装置の制御方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013074711A JP6089891B2 (ja) | 2013-03-29 | 2013-03-29 | 演算処理装置、情報処理装置及び情報処理装置の制御方法 |

| EP14161212.7A EP2784684A1 (en) | 2013-03-29 | 2014-03-24 | Operation processing apparatus, information processing apparatus and method of controlling information processing apparatus |

| US14/224,108 US20140297957A1 (en) | 2013-03-29 | 2014-03-25 | Operation processing apparatus, information processing apparatus and method of controlling information processing apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013074711A JP6089891B2 (ja) | 2013-03-29 | 2013-03-29 | 演算処理装置、情報処理装置及び情報処理装置の制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2014199576A JP2014199576A (ja) | 2014-10-23 |

| JP6089891B2 true JP6089891B2 (ja) | 2017-03-08 |

Family

ID=50486747

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013074711A Expired - Fee Related JP6089891B2 (ja) | 2013-03-29 | 2013-03-29 | 演算処理装置、情報処理装置及び情報処理装置の制御方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20140297957A1 (ja) |

| EP (1) | EP2784684A1 (ja) |

| JP (1) | JP6089891B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10740116B2 (en) * | 2015-09-01 | 2020-08-11 | International Business Machines Corporation | Three-dimensional chip-based regular expression scanner |

| JP6319473B1 (ja) * | 2017-02-07 | 2018-05-09 | 日本電気株式会社 | 情報処理装置 |

| US10521112B2 (en) * | 2017-03-17 | 2019-12-31 | International Business Machines Corporation | Layered clustered scale-out storage system |

| US10915445B2 (en) * | 2018-09-18 | 2021-02-09 | Nvidia Corporation | Coherent caching of data for high bandwidth scaling |

| US11836523B2 (en) * | 2020-10-28 | 2023-12-05 | Red Hat, Inc. | Introspection of a containerized application in a runtime environment |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3769411B2 (ja) | 1999-03-09 | 2006-04-26 | 日本電気株式会社 | マルチプロセッサシステム |

| US6721856B1 (en) * | 2000-10-26 | 2004-04-13 | International Business Machines Corporation | Enhanced cache management mechanism via an intelligent system bus monitor |

| US7089372B2 (en) * | 2003-12-01 | 2006-08-08 | International Business Machines Corporation | Local region table for storage of information regarding memory access by other nodes |

| JP4119380B2 (ja) * | 2004-02-19 | 2008-07-16 | 株式会社日立製作所 | マルチプロセッサシステム |

-

2013

- 2013-03-29 JP JP2013074711A patent/JP6089891B2/ja not_active Expired - Fee Related

-

2014

- 2014-03-24 EP EP14161212.7A patent/EP2784684A1/en not_active Withdrawn

- 2014-03-25 US US14/224,108 patent/US20140297957A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| JP2014199576A (ja) | 2014-10-23 |

| EP2784684A1 (en) | 2014-10-01 |

| US20140297957A1 (en) | 2014-10-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8762651B2 (en) | Maintaining cache coherence in a multi-node, symmetric multiprocessing computer | |

| JP6089891B2 (ja) | 演算処理装置、情報処理装置及び情報処理装置の制御方法 | |

| TW201717040A (zh) | 用於具有調適分割之一共用快取之系統及方法 | |

| JP6040840B2 (ja) | 演算処理装置、情報処理装置及び情報処理装置の制御方法 | |

| JP2018005395A (ja) | 演算処理装置、情報処理装置および演算処理装置の制御方法 | |

| US10705977B2 (en) | Method of dirty cache line eviction | |

| US12399829B2 (en) | Dynamic extension of cache coherence snoop filter entry | |

| JP2019517689A (ja) | 他のキャッシュでのエントリの可用性に基づくキャッシュエントリの置換 | |

| EP4026005B1 (en) | Producer-to-consumer active direct cache transfers | |

| JP6036457B2 (ja) | 演算処理装置、情報処理装置及び情報処理装置の制御方法 | |

| US9983994B2 (en) | Arithmetic processing device and method for controlling arithmetic processing device | |

| US11593167B2 (en) | Thread embedded cache management | |

| US8397029B2 (en) | System and method for cache coherency in a multiprocessor system | |

| JP6094303B2 (ja) | 演算処理装置、情報処理装置及び情報処理装置の制御方法 | |

| US10565111B2 (en) | Processor | |

| US20160342516A1 (en) | Cache coherence in multi-compute-engine systems | |

| US20060015689A1 (en) | Implementation and management of moveable buffers in cache system | |

| JP5045334B2 (ja) | キャッシュシステム | |

| JP5574039B2 (ja) | 演算処理装置及び演算処理装置の制御方法 | |

| CN112955877B (zh) | 修改存储数据的装置和方法 | |

| US20250139008A1 (en) | Snoop filter entry using a partial vector | |

| JP6631317B2 (ja) | 演算処理装置、情報処理装置および情報処理装置の制御方法 | |

| WO2014056534A1 (en) | Context-sensitive data-cache |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20151204 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160929 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161011 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161209 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170110 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170123 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6089891 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |