JP5069950B2 - Semiconductor device, display device, liquid crystal display device, display module, and electronic apparatus - Google Patents

Semiconductor device, display device, liquid crystal display device, display module, and electronic apparatus Download PDFInfo

- Publication number

- JP5069950B2 JP5069950B2 JP2007143414A JP2007143414A JP5069950B2 JP 5069950 B2 JP5069950 B2 JP 5069950B2 JP 2007143414 A JP2007143414 A JP 2007143414A JP 2007143414 A JP2007143414 A JP 2007143414A JP 5069950 B2 JP5069950 B2 JP 5069950B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- wiring

- capacitor

- electrode

- potential

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Description

本発明は、半導体装置及び半導体装置の駆動方法に関する。また、半導体装置を具備する表示装置、特に半導体装置を具備する液晶表示装置、及び当該液晶表示装置を具備する電子機器に関する。 The present invention relates to a semiconductor device and a method for driving the semiconductor device. In addition, the present invention relates to a display device including a semiconductor device, in particular, a liquid crystal display device including a semiconductor device, and an electronic apparatus including the liquid crystal display device.

近年、液晶表示装置や発光装置などの表示装置は、液晶テレビなどの大型表示装置の増加から、活発に開発が進められている。特に絶縁体上に非結晶半導体により形成されたトランジスタを用いて、画素回路、及びシフトレジスタ回路等を含む駆動回路(以下、内部回路という)を一体形成する技術は、低消費電力化、低コスト化に大きく貢献するため、活発に開発が進められている。絶縁体上に形成された内部回路は、FPC等を介して絶縁体の外に配置されたコントローラIC等に(以下、外部回路という)と接続され、その動作が制御されている。 In recent years, display devices such as liquid crystal display devices and light-emitting devices have been actively developed due to an increase in large display devices such as liquid crystal televisions. In particular, a technology in which a driver circuit including a pixel circuit and a shift register circuit (hereinafter referred to as an internal circuit) is integrally formed using a transistor formed of an amorphous semiconductor over an insulator has low power consumption and low cost. In order to make a significant contribution to the development, development is actively underway. An internal circuit formed on the insulator is connected to a controller IC or the like (hereinafter referred to as an external circuit) disposed outside the insulator via an FPC or the like, and its operation is controlled.

また、絶縁体上に形成された内部回路として、様々なレベルシフタが考案されている(特許文献1、特許文献2参照)。

上記特許文献1、及び特許文献2に示すレベルシフタでは、入力信号の負電源側、及び正電源側を同時にレベルシフトすることができない。つまり、入力信号を負電源側及び正電源側にレベルシフトするためには、入力信号の負電源側をレベルシフトするためのレベルシフタと、入力信号の正電源側をレベルシフトするためのレベルシフタとが必要になっていた。

In the level shifters shown in

上記問題を鑑み、本発明では、入力信号を負電源側、及び正電源側に同時にレベルシフトできるレベルシフタ、及びこのようなレベルシフタを具備する半導体装置、並びに液晶表示装置等の表示装置、及び当該表示装置を具備する電子機器を提供することを目的とする。 In view of the above problems, in the present invention, a level shifter capable of simultaneously shifting the level of an input signal to the negative power supply side and the positive power supply side, a semiconductor device including such a level shifter, a display device such as a liquid crystal display device, and the display An object is to provide an electronic apparatus including the device.

本発明の一は、第1の容量素子と、第2の容量素子と、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタとを有し、前記第1の容量素子の第1電極が第3の配線に電気的に接続され、前記第2の容量素子の第1電極が第4の配線に電気的に接続され、前記第1のトランジスタのゲートが前記第1の容量素子の第2電極に電気的に接続され、前記第1のトランジスタの第1端子が第2の配線に電気的に接続され、前記第1のトランジスタの第2端子が前記第2の容量素子の第2電極に電気的に接続され、前記第2のトランジスタのゲートが前記第2の容量素子の第2電極に電気的に接続され、前記第2のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第2のトランジスタの第2端子が前記第1の容量素子の第2電極に電気的に接続され、前記第3のトランジスタのゲートが前記第2の容量素子の第2電極に電気的に接続され、前記第3のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第3のトランジスタの第2端子が第5の配線に電気的に接続され、前記第4のトランジスタのゲート及び第1の端子が第1の配線に電気的に接続され、前記前記第4のトランジスタの第2端子が第5の配線に電気的に接続されていることを特徴とする構成である。 One aspect of the present invention includes a first capacitor, a second capacitor, a first transistor, a second transistor, a third transistor, and a fourth transistor. The first electrode of the capacitor element is electrically connected to the third wiring, the first electrode of the second capacitor element is electrically connected to the fourth wiring, and the gate of the first transistor is The first capacitor is electrically connected to the second electrode, the first terminal of the first transistor is electrically connected to the second wiring, and the second terminal of the first transistor is electrically connected to the second electrode. And the gate of the second transistor is electrically connected to the second electrode of the second capacitor element, and the first terminal of the second transistor is connected to the second electrode of the capacitor element. A second wiring of the second transistor electrically connected to the second wiring; A child is electrically connected to the second electrode of the first capacitor element, a gate of the third transistor is electrically connected to a second electrode of the second capacitor element, and The first terminal is electrically connected to the second wiring, the second terminal of the third transistor is electrically connected to the fifth wiring, and the gate and the first terminal of the fourth transistor are connected to each other. It is electrically connected to a first wiring, and the second terminal of the fourth transistor is electrically connected to a fifth wiring.

なお、前記第1のトランジスタ乃至前記第4のトランジスタは同じ導電型のトランジスタであっても良い。前記第1のトランジスタ乃至前記第4のトランジスタはPチャネル型トランジスタの場合には前記第1の配線の電位は前記第2の配線の電位よりも高いことを特徴としても良い。また、前記第1のトランジスタ乃至前記第4のトランジスタはNチャネル型トランジスタの場合には、前記第1の配線の電位は前記第2の配線の電位よりも低いことを特徴としても良い。 Note that the first to fourth transistors may be transistors of the same conductivity type. In the case where the first to fourth transistors are P-channel transistors, the potential of the first wiring may be higher than the potential of the second wiring. In the case where the first to fourth transistors are N-channel transistors, the potential of the first wiring may be lower than the potential of the second wiring.

本発明の一は、第1の容量素子と、第2の容量素子と、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタとを有し、前記第1の容量素子の第1電極が第3の配線に電気的に接続され、前記第2の容量素子の第1電極が第4の配線に電気的に接続され、前記第1のトランジスタのゲートが前記第1の容量素子の第2電極に電気的に接続され、前記第1のトランジスタの第1端子が第2の配線に電気的に接続され、前記第1のトランジスタの第2端子が前記第2の容量素子の第2電極に電気的に接続され、前記第2のトランジスタのゲートが前記第2の容量素子の第2電極に電気的に接続され、前記第2のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第2のトランジスタの第2端子が前記第1の容量素子の第2電極に電気的に接続され、前記第3のトランジスタのゲートが前記第2の容量素子の第2電極に電気的に接続され、前記第3のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第3のトランジスタの第2端子が第5の配線に電気的に接続され、前記第4のトランジスタのゲート及び第1端子が第1の配線に電気的に接続され、前記第4のトランジスタの第2端子が前記第5の配線に電気的に接続され、前記第5のトランジスタのゲートが前記第1の容量素子の第2電極に電気的に接続され、前記第5のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第5のトランジスタの第2の端子が第6の配線に電気的に接続され、前記第6のトランジスタのゲート及び第1端子が前記第1の配線に電気的に接続され、前記第6のトランジスタの第2端子が前記第6の配線に電気的に接続されていることを特徴とする構成である。 According to one embodiment of the present invention, a first capacitor, a second capacitor, a first transistor, a second transistor, a third transistor, a fourth transistor, and a fifth transistor are provided. And a first electrode of the first capacitor is electrically connected to a third wiring, and a first electrode of the second capacitor is electrically connected to a fourth wiring. Connected, a gate of the first transistor is electrically connected to a second electrode of the first capacitor, a first terminal of the first transistor is electrically connected to a second wiring, and The second terminal of the first transistor is electrically connected to the second electrode of the second capacitor element, and the gate of the second transistor is electrically connected to the second electrode of the second capacitor element. , The first terminal of the second transistor is electrically connected to the second wiring. And the second terminal of the second transistor is electrically connected to the second electrode of the first capacitor, and the gate of the third transistor is the second electrode of the second capacitor. The first terminal of the third transistor is electrically connected to the second wiring, the second terminal of the third transistor is electrically connected to the fifth wiring, The gate and first terminal of the fourth transistor are electrically connected to a first wiring, the second terminal of the fourth transistor is electrically connected to the fifth wiring, and the fifth transistor And the second terminal of the fifth transistor is electrically connected to the second electrode of the first capacitor, the first terminal of the fifth transistor is electrically connected to the second wiring, Are electrically connected to the sixth wiring, The gate and first terminal of the sixth transistor are electrically connected to the first wiring, and the second terminal of the sixth transistor is electrically connected to the sixth wiring. The configuration is as follows.

なお、前記第1のトランジスタ乃至前記第6のトランジスタは同じ導電型のトランジスタであっても良い。前記第1のトランジスタ乃至前記第6のトランジスタはPチャネル型トランジスタの場合には前記第1の配線の電位は前記第2の配線の電位よりも高いことを特徴としても良い。また、前記第1のトランジスタ乃至前記第6のトランジスタはNチャネル型トランジスタの場合には、前記第1の配線の電位は前記第2の配線の電位よりも低いことを特徴としても良い。 Note that the first to sixth transistors may be transistors of the same conductivity type. In the case where the first to sixth transistors are P-channel transistors, the potential of the first wiring may be higher than the potential of the second wiring. In the case where the first to sixth transistors are N-channel transistors, the potential of the first wiring may be lower than the potential of the second wiring.

本発明の一は、第1の容量素子と、第2の容量素子と、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタとを有し、前記第1の容量素子の第1電極が第3の配線に電気的に接続され、前記第2の容量素子の第1電極が第4の配線に電気的に接続され、前記第1のトランジスタのゲートが前記第1の容量素子の第2電極に電気的に接続され、前記第1のトランジスタの第1端子が第2の配線に電気的に接続され、前記第1のトランジスタの第2端子が前記第2の容量素子の第2電極に電気的に接続され、前記第2のトランジスタのゲートが前記第2の容量素子の第2電極に電気的に接続され、前記第2のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第2のトランジスタの第2端子が前記第1の容量素子の第2電極に電気的に接続され、前記第3のトランジスタのゲートが前記第2の容量素子の第2電極に電気的に接続され、前記第3のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第4のトランジスタのゲート及び第1端子が第1の配線に電気的に接続され、前記第4のトランジスタの第2端子が前記第3のトランジスタの第2端子に電気的に接続され、前記第5のトランジスタのゲートが前記第2の容量素子の第2電極に電気的に接続され、前記第5のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第5のトランジスタの第2端子が第5の配線に電気的に接続され、前記第6のトランジスタのゲートが前記第3のトランジスタの第2端子及び前記第4のトランジスタの第2端子に電気的に接続され、前記第6のトランジスタの第1端子が前記第1の配線に電気的に接続され、前記第6のトランジスタの第2端子が前記第5の配線に電気的に接続されていることを特徴とする構成である。 According to one embodiment of the present invention, a first capacitor, a second capacitor, a first transistor, a second transistor, a third transistor, a fourth transistor, and a fifth transistor are provided. And a first electrode of the first capacitor is electrically connected to a third wiring, and a first electrode of the second capacitor is electrically connected to a fourth wiring. Connected, a gate of the first transistor is electrically connected to a second electrode of the first capacitor, a first terminal of the first transistor is electrically connected to a second wiring, and The second terminal of the first transistor is electrically connected to the second electrode of the second capacitor element, and the gate of the second transistor is electrically connected to the second electrode of the second capacitor element. , The first terminal of the second transistor is electrically connected to the second wiring. And the second terminal of the second transistor is electrically connected to the second electrode of the first capacitor, and the gate of the third transistor is the second electrode of the second capacitor. , The first terminal of the third transistor is electrically connected to the second wiring, and the gate and the first terminal of the fourth transistor are electrically connected to the first wiring. And the second terminal of the fourth transistor is electrically connected to the second terminal of the third transistor, and the gate of the fifth transistor is electrically connected to the second electrode of the second capacitor. The first terminal of the fifth transistor is electrically connected to the second wiring, the second terminal of the fifth transistor is electrically connected to a fifth wiring, and the sixth terminal The gate of the transistor is the third transistor And a second terminal of the fourth transistor is electrically connected to the second terminal of the fourth transistor, and a first terminal of the sixth transistor is electrically connected to the first wiring. The second terminal is electrically connected to the fifth wiring.

なお、前記第1のトランジスタ乃至前記第6のトランジスタは同じ導電型のトランジスタであっても良い。前記第1のトランジスタ乃至前記第6のトランジスタはPチャネル型トランジスタの場合には前記第1の配線の電位は前記第2の配線の電位よりも高いことを特徴としても良い。また、前記第1のトランジスタ乃至前記第6のトランジスタはNチャネル型トランジスタの場合には、前記第1の配線の電位は前記第2の配線の電位よりも低いことを特徴としても良い。 Note that the first to sixth transistors may be transistors of the same conductivity type. In the case where the first to sixth transistors are P-channel transistors, the potential of the first wiring may be higher than the potential of the second wiring. In the case where the first to sixth transistors are N-channel transistors, the potential of the first wiring may be lower than the potential of the second wiring.

また、本発明の一は、液晶素子を有する画素と、駆動回路とを有し、前記駆動回路は、第1の容量素子と、第2の容量素子と、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタとを有し、前記第1の容量素子の第1電極が第3の配線に電気的に接続され、前記第2の容量素子の第1電極が第4の配線に電気的に接続され、前記第1のトランジスタのゲートが前記第1の容量素子の第2電極に電気的に接続され、前記第1のトランジスタの第1端子が第2の配線に電気的に接続され、前記第1のトランジスタの第2端子が前記第2の容量素子の第2電極に電気的に接続され、前記第2のトランジスタのゲートが前記第2の容量素子の第2電極に電気的に接続され、前記第2のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第2のトランジスタの第2端子が前記第1の容量素子の第2電極に電気的に接続され、前記第3のトランジスタのゲートが前記第2の容量素子の第2電極に電気的に接続され、前記第3のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第3のトランジスタの第2端子が第5の配線に電気的に接続され、前記第4のトランジスタのゲート及び第1の端子が第1の配線に電気的に接続され、前記前記第4のトランジスタの第2端子が第5の配線に電気的に接続されていることを特徴とする液晶表示装置である。 One embodiment of the present invention includes a pixel including a liquid crystal element and a driver circuit, and the driver circuit includes a first capacitor element, a second capacitor element, a first transistor, and a second transistor. A first transistor including a transistor, a third transistor, and a fourth transistor, wherein the first electrode of the first capacitor is electrically connected to a third wiring; Is electrically connected to the fourth wiring, the gate of the first transistor is electrically connected to the second electrode of the first capacitor, and the first terminal of the first transistor is the second electrode. Electrically connected to the wiring, the second terminal of the first transistor is electrically connected to the second electrode of the second capacitor, and the gate of the second transistor is connected to the second capacitor. A first terminal of the second transistor electrically connected to the second electrode; The second wiring is electrically connected to the second wiring, the second terminal of the second transistor is electrically connected to the second electrode of the first capacitor, and the gate of the third transistor is the second wiring. The third transistor is electrically connected to the second electrode, the first terminal of the third transistor is electrically connected to the second wiring, and the second terminal of the third transistor is the fifth wiring. The gate and first terminal of the fourth transistor are electrically connected to a first wiring, and the second terminal of the fourth transistor is electrically connected to a fifth wiring. The liquid crystal display device is connected.

なお、前記第1のトランジスタ乃至前記第4のトランジスタは同じ導電型のトランジスタであっても良い。前記第1のトランジスタ乃至前記第4のトランジスタはPチャネル型トランジスタの場合には前記第1の配線の電位は前記第2の配線の電位よりも高いことを特徴としても良い。また、前記第1のトランジスタ乃至前記第4のトランジスタはNチャネル型トランジスタの場合には、前記第1の配線の電位は前記第2の配線の電位よりも低いことを特徴としても良い。 Note that the first to fourth transistors may be transistors of the same conductivity type. In the case where the first to fourth transistors are P-channel transistors, the potential of the first wiring may be higher than the potential of the second wiring. In the case where the first to fourth transistors are N-channel transistors, the potential of the first wiring may be lower than the potential of the second wiring.

また、本発明の一は、液晶素子を有する画素と、駆動回路とを有し、前記駆動回路は、第1の容量素子と、第2の容量素子と、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタとを有し、前記第1の容量素子の第1電極が第3の配線に電気的に接続され、前記第2の容量素子の第1電極が第4の配線に電気的に接続され、前記第1のトランジスタのゲートが前記第1の容量素子の第2電極に電気的に接続され、前記第1のトランジスタの第1端子が第2の配線に電気的に接続され、前記第1のトランジスタの第2端子が前記第2の容量素子の第2電極に電気的に接続され、前記第2のトランジスタのゲートが前記第2の容量素子の第2電極に電気的に接続され、前記第2のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第2のトランジスタの第2端子が前記第1の容量素子の第2電極に電気的に接続され、前記第3のトランジスタのゲートが前記第2の容量素子の第2電極に電気的に接続され、前記第3のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第3のトランジスタの第2端子が第5の配線に電気的に接続され、前記第4のトランジスタのゲート及び第1端子が第1の配線に電気的に接続され、前記第4のトランジスタの第2端子が前記第5の配線に電気的に接続され、前記第5のトランジスタのゲートが前記第1の容量素子の第2電極に電気的に接続され、前記第5のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第5のトランジスタの第2の端子が第6の配線に電気的に接続され、前記第6のトランジスタのゲート及び第1端子が前記第1の配線に電気的に接続され、前記第6のトランジスタの第2端子が前記第6の配線に電気的に接続されていることを特徴とする液晶表示装置である。 One embodiment of the present invention includes a pixel including a liquid crystal element and a driver circuit, and the driver circuit includes a first capacitor element, a second capacitor element, a first transistor, and a second transistor. A first transistor including a transistor, a third transistor, a fourth transistor, a fifth transistor, and a sixth transistor, wherein the first electrode of the first capacitor is electrically connected to the third wiring; A first electrode of the second capacitor element is electrically connected to a fourth wiring; a gate of the first transistor is electrically connected to a second electrode of the first capacitor element; The first terminal of the first transistor is electrically connected to the second wiring, the second terminal of the first transistor is electrically connected to the second electrode of the second capacitor, and the second terminal The gate of the transistor is electrically connected to the second electrode of the second capacitor element. Connected, the first terminal of the second transistor is electrically connected to the second wiring, and the second terminal of the second transistor is electrically connected to the second electrode of the first capacitor. The gate of the third transistor is electrically connected to the second electrode of the second capacitor, the first terminal of the third transistor is electrically connected to the second wiring, The second terminal of the third transistor is electrically connected to the fifth wiring, the gate and the first terminal of the fourth transistor are electrically connected to the first wiring, and the fourth terminal of the fourth transistor is electrically connected. Two terminals are electrically connected to the fifth wiring, a gate of the fifth transistor is electrically connected to a second electrode of the first capacitor, and a first terminal of the fifth transistor is Electrically connected to the second wiring; The second terminal of the fifth transistor is electrically connected to the sixth wiring, the gate and the first terminal of the sixth transistor are electrically connected to the first wiring, and the sixth transistor The liquid crystal display device is characterized in that the second terminal is electrically connected to the sixth wiring.

なお、前記第1のトランジスタ乃至前記第6のトランジスタは同じ導電型のトランジスタであっても良い。前記第1のトランジスタ乃至前記第6のトランジスタはPチャネル型トランジスタの場合には前記第1の配線の電位は前記第2の配線の電位よりも高いことを特徴としても良い。また、前記第1のトランジスタ乃至前記第6のトランジスタはNチャネル型トランジスタの場合には、前記第1の配線の電位は前記第2の配線の電位よりも低いことを特徴としても良い。 Note that the first to sixth transistors may be transistors of the same conductivity type. In the case where the first to sixth transistors are P-channel transistors, the potential of the first wiring may be higher than the potential of the second wiring. In the case where the first to sixth transistors are N-channel transistors, the potential of the first wiring may be lower than the potential of the second wiring.

また、本発明の一は液晶素子を有する画素と、駆動回路とを有し、前記駆動回路は、第1の容量素子と、第2の容量素子と、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタとを有し、前記第1の容量素子の第1電極が第3の配線に電気的に接続され、前記第2の容量素子の第1電極が第4の配線に電気的に接続され、前記第1のトランジスタのゲートが前記第1の容量素子の第2電極に電気的に接続され、前記第1のトランジスタの第1端子が第2の配線に電気的に接続され、前記第1のトランジスタの第2端子が前記第2の容量素子の第2電極に電気的に接続され、前記第2のトランジスタのゲートが前記第2の容量素子の第2電極に電気的に接続され、前記第2のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第2のトランジスタの第2端子が前記第1の容量素子の第2電極に電気的に接続され、前記第3のトランジスタのゲートが前記第2の容量素子の第2電極に電気的に接続され、前記第3のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第4のトランジスタのゲート及び第1端子が第1の配線に電気的に接続され、前記第4のトランジスタの第2端子が前記第3のトランジスタの第2端子に電気的に接続され、前記第5のトランジスタのゲートが前記第2の容量素子の第2電極に電気的に接続され、前記第5のトランジスタの第1端子が前記第2の配線に電気的に接続され、前記第5のトランジスタの第2端子が第5の配線に電気的に接続され、前記第6のトランジスタのゲートが前記第3のトランジスタの第2端子及び前記第4のトランジスタの第2端子に電気的に接続され、前記第6のトランジスタの第1端子が前記第1の配線に電気的に接続され、前記第6のトランジスタの第2端子が前記第5の配線に電気的に接続されていることを特徴とする液晶表示装置である。 One embodiment of the present invention includes a pixel including a liquid crystal element and a driver circuit, and the driver circuit includes a first capacitor element, a second capacitor element, a first transistor, and a second transistor. A third transistor, a fourth transistor, a fifth transistor, and a sixth transistor, wherein the first electrode of the first capacitor is electrically connected to the third wiring. The first electrode of the second capacitor element is electrically connected to a fourth wiring, the gate of the first transistor is electrically connected to the second electrode of the first capacitor element, and A first terminal of one transistor is electrically connected to a second wiring, a second terminal of the first transistor is electrically connected to a second electrode of the second capacitor, and the second terminal The gate of the transistor is electrically connected to the second electrode of the second capacitor element. The first terminal of the second transistor is electrically connected to the second wiring, and the second terminal of the second transistor is electrically connected to the second electrode of the first capacitor. The gate of the third transistor is electrically connected to the second electrode of the second capacitor, the first terminal of the third transistor is electrically connected to the second wiring, A gate and a first terminal of a fourth transistor are electrically connected to a first wiring; a second terminal of the fourth transistor is electrically connected to a second terminal of the third transistor; A gate of the fifth transistor is electrically connected to a second electrode of the second capacitor, a first terminal of the fifth transistor is electrically connected to the second wiring, and the fifth transistor The second terminal of the And the gate of the sixth transistor is electrically connected to the second terminal of the third transistor and the second terminal of the fourth transistor, and the first terminal of the sixth transistor is connected to the second terminal of the fourth transistor. The liquid crystal display device is characterized in that it is electrically connected to one wiring and the second terminal of the sixth transistor is electrically connected to the fifth wiring.

なお、前記第1のトランジスタ乃至前記第6のトランジスタは同じ導電型のトランジスタであっても良い。前記第1のトランジスタ乃至前記第6のトランジスタはPチャネル型トランジスタの場合には前記第1の配線の電位は前記第2の配線の電位よりも高いことを特徴としても良い。また、前記第1のトランジスタ乃至前記第6のトランジスタはNチャネル型トランジスタの場合には、前記第1の配線の電位は前記第2の配線の電位よりも低いことを特徴としても良い。 Note that the first to sixth transistors may be transistors of the same conductivity type. In the case where the first to sixth transistors are P-channel transistors, the potential of the first wiring may be higher than the potential of the second wiring. In the case where the first to sixth transistors are N-channel transistors, the potential of the first wiring may be lower than the potential of the second wiring.

なお、本発明に示すスイッチは、様々な形態のものを用いることができ、一例として、電気的スイッチや機械的なスイッチなどがある。つまり、電流の流れを制御できるものであればよく、特定のものに限定されず、様々なものを用いることができる。例えば、トランジスタでもよいし、ダイオード(例えば、PNダイオード、PINダイオード、ショットキーダイオード、ダイオード接続のトランジスタなど)でもよいし、サイリスタでもよいし、それらを組み合わせた論理回路でもよい。よって、スイッチとしてトランジスタを用いる場合、そのトランジスタは、単なるスイッチとして動作するため、トランジスタの極性(導電型)は特に限定されない。ただし、オフ電流が少ない方が望ましい場合、オフ電流が少ない方の極性のトランジスタを用いることが望ましい。オフ電流が少ないトランジスタとしては、LDD領域を設けているものやマルチゲート構造にしているもの等がある。また、スイッチとして動作させるトランジスタのソース端子の電位が、低電位側電源(Vss、GND、0Vなど)に近い状態で動作する場合はNチャネル型を、ソース端子の電位が、高電位側電源(Vddなど)に近い状態で動作する場合はPチャネル型を用いることが望ましい。なぜなら、ゲートソース間電圧の絶対値を大きくできるため、スイッチとして機能させやすいからである。 Note that various types of switches can be used as a switch shown in the present invention, and examples thereof include an electrical switch and a mechanical switch. In other words, any device can be used as long as it can control the flow of current, and it is not limited to a specific device, and various devices can be used. For example, it may be a transistor, a diode (for example, a PN diode, a PIN diode, a Schottky diode, a diode-connected transistor, or the like), a thyristor, or a logic circuit that combines them. Therefore, when a transistor is used as a switch, the transistor operates as a mere switch, and thus the polarity (conductivity type) of the transistor is not particularly limited. However, when it is desirable that the off-state current is small, it is desirable to use a transistor having a polarity with a small off-state current. As a transistor with low off-state current, there are a transistor provided with an LDD region and a transistor having a multi-gate structure. In the case where the transistor operates as a switch when the potential of the source terminal of the transistor is close to a low potential side power supply (Vss, GND, 0V, etc.), the N channel type is used. When operating in a state close to Vdd, etc., it is desirable to use a P-channel type. This is because the absolute value of the gate-source voltage can be increased, so that it can easily function as a switch.

なお、Nチャネル型とPチャネル型の両方を用いて、CMOS型のスイッチにしてもよい。CMOS型のスイッチにすると、Pチャネル型かNチャネル型かのいずれかのスイッチが導通すれば電流を流すことができるため、スイッチとして機能しやすくなる。例えば、スイッチへの入力信号の電圧が高い場合でも、低い場合でも、適切に電圧を出力させることが出来る。また、スイッチをオン・オフさせるための信号の電圧振幅値を小さくすることが出来るので、消費電力を小さくすることも出来る。 Note that both N-channel and P-channel switches may be used as CMOS switches. When a CMOS switch is used, a current can flow when either the P-channel switch or the N-channel switch is turned on, so that the switch can easily function as a switch. For example, the voltage can be appropriately output regardless of whether the voltage of the input signal to the switch is high or low. In addition, since the voltage amplitude value of the signal for turning on / off the switch can be reduced, the power consumption can be reduced.

なお、スイッチとしてトランジスタを用いる場合は、入力端子(ソース端子またはドレイン端子の一方)と、出力端子(ソース端子またはドレイン端子の他方)と、導通を制御する端子(ゲート端子)とを有している。一方、スイッチとしてダイオードを用いる場合は、導通を制御する端子を有していない場合がある。そのため、端子を制御するための配線を少なくすることが出来る。 Note that in the case where a transistor is used as a switch, the transistor has an input terminal (one of a source terminal or a drain terminal), an output terminal (the other of the source terminal or the drain terminal), and a terminal (gate terminal) that controls conduction. Yes. On the other hand, when a diode is used as a switch, it may not have a terminal for controlling conduction. Therefore, the wiring for controlling the terminals can be reduced.

なお、本発明において、接続されているとは、電気的に接続されている場合と機能的に接続されている場合と直接接続されている場合とを含むものとする。したがって、本発明が開示する構成において、所定の接続関係以外のものも含むものとする。例えば、ある部分とある部分との間に、電気的な接続を可能とする素子(例えば、スイッチやトランジスタや容量素子やインダクタや抵抗素子やダイオードなど)が1個以上配置されていてもよい。また、機能的な接続を可能とする回路(例えば、論理回路(インバータやNAND回路やNOR回路など)や信号変換回路(DA変換回路やAD変換回路やガンマ補正回路など)や電位レベル変換回路(昇圧回路や降圧回路などの電源回路やH信号やL信号の電位レベルを変えるレベルシフタ回路など)や電圧源や電流源や切り替え回路や増幅回路(オペアンプや差動増幅回路やソースフォロワ回路やバッファ回路など、信号振幅や電流量などを大きく出来る回路など)や信号生成回路や記憶回路や制御回路など)が間に1個以上配置されていてもよい。あるいは、間に他の素子や他の回路を挟まずに、直接接続されて、配置されていてもよい。 Note that in the present invention, the term “connected” includes the case of being electrically connected, the case of being functionally connected, and the case of being directly connected. Therefore, the configuration disclosed by the present invention includes other than the predetermined connection relationship. For example, one or more elements (for example, a switch, a transistor, a capacitor, an inductor, a resistor, a diode, or the like) that can be electrically connected may be arranged between a certain portion. In addition, a circuit (for example, a logic circuit (an inverter, a NAND circuit, a NOR circuit, etc.), a signal conversion circuit (a DA conversion circuit, an AD conversion circuit, a gamma correction circuit, etc.) or a potential level conversion circuit ( Power supply circuits such as booster circuits and step-down circuits, level shifter circuits that change the potential level of H and L signals, etc., voltage sources, current sources, switching circuits, and amplifier circuits (op amps, differential amplifier circuits, source follower circuits, and buffer circuits) Etc.), or a signal generation circuit, a memory circuit, a control circuit, etc.) may be disposed between them. Alternatively, they may be arranged directly connected without interposing other elements or other circuits therebetween.

なお、素子や回路を間に介さずに接続されている場合のみを含む場合は、直接接続されている、と記載するものとする。また、電気的に接続されている、と記載する場合は、電気的に接続されている場合(つまり、間に別の素子を挟んで接続されている場合)と機能的に接続されている場合(つまり、間に別の回路を挟んで接続されている場合)と直接接続されている場合(つまり、間に別の素子や別の回路を挟まずに接続されている場合)とを含むものとする。 In addition, when only including the case where it is connected without interposing an element or a circuit, it shall be described as being directly connected. In addition, when it is described as being electrically connected, when it is electrically connected (that is, when connected with another element in between) and when it is functionally connected (That is, connected with another circuit in between) and directly connected (that is, connected without another element or circuit in between). .

なお、表示素子や表示装置や発光素子や発光装置は、様々な形態を用いたり、様々な素子を有したりすることが出来る。例えば、表示素子や表示装置や発光素子や発光装置としては、EL素子(有機EL素子、無機EL素子又は有機物及び無機物を含むEL素子)、電子放出素子、液晶素子、電子インク、グレーティングライトバルブ(GLV)、プラズマディスプレイ(PDP)、デジタルマイクロミラーデバイス(DMD)、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用によりコントラストが変化する表示媒体を適用することができる。なお、EL素子を用いた表示装置としてはELディスプレイ、電子放出素子を用いた表示装置としてはフィールドエミッションディスプレイ(FED)やSED方式平面型ディスプレイ(SED:Surface−conduction Electron−emitter Disply)など、液晶素子を用いた表示装置としては液晶ディスプレイ、透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、電子インクを用いた表示装置としては電子ペーパーがある。 Note that the display element, the display device, the light-emitting element, and the light-emitting device can have various forms or have various elements. For example, as a display element, a display device, a light emitting element, and a light emitting device, an EL element (an organic EL element, an inorganic EL element, or an EL element containing an organic substance and an inorganic substance), an electron-emitting element, a liquid crystal element, electronic ink, GLV), plasma display (PDP), digital micromirror device (DMD), piezoelectric ceramic display, carbon nanotube, and other display media whose contrast is changed by an electromagnetic action can be applied. Note that a display device using an EL element is an EL display, and a display device using an electron-emitting device is a liquid crystal display such as a field emission display (FED) or a SED type flat display (SED: Surface-conduction Electron-emitter Display) A display device using the element includes a liquid crystal display, a transmissive liquid crystal display, a transflective liquid crystal display, a reflective liquid crystal display, and a display device using electronic ink includes electronic paper.

なお、本発明において、トランジスタは、様々な形態のトランジスタを適用させることが出来る。よって、適用可能なトランジスタの種類に限定はない。したがって、例えば、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を有する薄膜トランジスタ(TFT)などを適用することが出来る。これらにより、製造温度が高くなくても製造できたり、低コストで製造できたり、大型基板上に製造できたり、透明基板上に製造できたり、トランジスタで光を透過させたりすることが出来る。また、半導体基板やSOI基板を用いて形成されるトランジスタ、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタなどを適用することが出来る。これらにより、バラツキの少ないトランジスタを製造できたり、電流供給能力の高いトランジスタを製造できたり、サイズの小さいトランジスタを製造できたり、消費電力の少ない回路を構成したりすることが出来る。また、ZnO、a−InGaZnO、SiGe、GaAsなどの化合物半導体を有するトランジスタや、さらに、それらを薄膜化した薄膜トランジスタなどを適用することが出来る。これらにより、製造温度が高くなくても製造できたり、室温で製造できたり、耐熱性の低い基板、例えばプラスチック基板やフィルム基板に直接トランジスタを形成したりすることが出来る。また、インクジェットや印刷法を用いて作成したトランジスタなどを適用することが出来る。これらにより、室温で製造したり、真空度の低い状態で製造したり、大型基板で製造したりすることができる。また、マスク(レチクル)を用いなくても製造することが可能となるため、トランジスタのレイアウトを容易に変更することが出来る。また、有機半導体やカーボンナノチューブを有するトランジスタ、その他のトランジスタを適用することができる。これらにより、曲げることが可能な基板上にトランジスタを形成することが出来る。なお、非単結晶半導体膜には水素またはハロゲンが含まれていてもよい。また、トランジスタが配置されている基板の種類は、様々なものを用いることができ、特定のものに限定されることはない。従って例えば、単結晶基板、SOI基板、ガラス基板、石英基板、プラスチック基板、紙基板、セロファン基板、石材基板、ステンレス・スチル基板、ステンレス・スチル・ホイルを有する基板などに配置することが出来る。また、ある基板でトランジスタを形成し、その後、別の基板にトランジスタを移動させて、別の基板上に配置するようにしてもよい。これらの基板を用いることにより、特性のよいトランジスタを形成したり、消費電力の小さいトランジスタを形成したり、壊れにくい装置にしたり、耐熱性を持たせたりすることが出来る。 Note that in the present invention, various types of transistors can be used as a transistor. Thus, there is no limitation on the type of applicable transistor. Therefore, for example, a thin film transistor (TFT) including a non-single-crystal semiconductor film typified by amorphous silicon or polycrystalline silicon can be used. As a result, they can be manufactured even at a low manufacturing temperature, can be manufactured at low cost, can be manufactured on a large substrate, can be manufactured on a transparent substrate, and light can be transmitted through a transistor. In addition, a transistor formed using a semiconductor substrate or an SOI substrate, a MOS transistor, a junction transistor, a bipolar transistor, or the like can be used. Accordingly, a transistor with little variation can be manufactured, a transistor with high current supply capability can be manufactured, a transistor with a small size can be manufactured, and a circuit with low power consumption can be configured. In addition, a transistor including a compound semiconductor such as ZnO, a-InGaZnO, SiGe, or GaAs, or a thin film transistor obtained by thinning them can be used. Accordingly, the transistor can be manufactured even at a low manufacturing temperature, can be manufactured at room temperature, or a transistor can be directly formed on a substrate having low heat resistance, such as a plastic substrate or a film substrate. In addition, a transistor formed using an inkjet method or a printing method can be used. By these, it can manufacture at room temperature, can manufacture in a state with a low degree of vacuum, or can manufacture with a large sized board | substrate. Further, since the transistor can be manufactured without using a mask (reticle), the layout of the transistor can be easily changed. In addition, a transistor including an organic semiconductor or a carbon nanotube, or another transistor can be used. Thus, a transistor can be formed over a substrate that can be bent. Note that the non-single-crystal semiconductor film may contain hydrogen or halogen. In addition, various types of substrates on which the transistor is arranged can be used, and the substrate is not limited to a specific type. Therefore, for example, it can be disposed on a single crystal substrate, an SOI substrate, a glass substrate, a quartz substrate, a plastic substrate, a paper substrate, a cellophane substrate, a stone substrate, a stainless steel substrate, a stainless steel substrate, a foil substrate, or the like. Alternatively, a transistor may be formed using a certain substrate, and then the transistor may be moved to another substrate and placed on another substrate. By using these substrates, it is possible to form a transistor with good characteristics, to form a transistor with low power consumption, to make the device hard to break, or to have heat resistance.

トランジスタの構成は、様々な形態をとることができる。特定の構成に限定されない。例えば、ゲート電極が2個以上になっているマルチゲート構造を用いてもよい。マルチゲート構造にすると、チャネル領域が直列に接続されるような構成となるため、複数のトランジスタが直列に接続されたような構成となる。マルチゲート構造にすることにより、オフ電流を低減したり、トランジスタの耐圧を向上させて信頼性を良くしたり、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることなどができる。また、チャネルの上下にゲート電極が配置されている構造でもよい。チャネルの上下にゲート電極が配置されている構造にすることにより、チャネル領域が増えるため、電流値を大きくしたり、空乏層ができやすくなってS値を小さくしたりすることができる。チャネルの上下にゲート電極が配置されると、複数のトランジスタが並列に接続されたような構成となる。また、チャネルの上にゲート電極が配置されている構造でもよいし、チャネルの下にゲート電極が配置されている構造でもよいし、正スタガ構造であってもよいし、逆スタガ構造でもよいし、チャネル領域が複数の領域に分かれていてもよいし、並列に接続されていてもよいし、直列に接続されていてもよい。また、チャネル(もしくはその一部)にソース電極やドレイン電極が重なっていてもよい。チャネル(もしくはその一部)にソース電極やドレイン電極が重なっている構造にすることにより、チャネルの一部に電荷がたまって、動作が不安定になることを防ぐことができる。また、LDD領域があってもよい。LDD領域を設けることにより、オフ電流を低減したり、トランジスタの耐圧を向上させて信頼性を良くしたり、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。 The structure of the transistor can take various forms. It is not limited to a specific configuration. For example, a multi-gate structure having two or more gate electrodes may be used. When the multi-gate structure is used, the channel regions are connected in series, so that a plurality of transistors are connected in series. The multi-gate structure reduces the off current, improves the breakdown voltage of the transistor to improve reliability, and even when the drain-source voltage changes when operating in the saturation region. The inter-current does not change so much, and flat characteristics can be achieved. Alternatively, a structure in which gate electrodes are arranged above and below the channel may be employed. By adopting a structure in which the gate electrodes are arranged above and below the channel, the channel region is increased, so that the current value can be increased or a depletion layer can be easily formed and the S value can be decreased. When gate electrodes are provided above and below a channel, a structure in which a plurality of transistors are connected in parallel is obtained. Further, a structure in which a gate electrode is disposed above a channel, a structure in which a gate electrode is disposed below a channel, a normal staggered structure, or an inverted staggered structure may be employed. The channel region may be divided into a plurality of regions, may be connected in parallel, or may be connected in series. In addition, a source electrode or a drain electrode may overlap with the channel (or a part thereof). By using a structure in which a source electrode or a drain electrode overlaps with a channel (or part of it), it is possible to prevent electric charges from being accumulated in part of the channel and unstable operation. There may also be an LDD region. By providing an LDD region, the off-current can be reduced, the breakdown voltage of the transistor can be improved to improve reliability, or the drain-source voltage can be changed even when the drain-source voltage changes when operating in the saturation region. The current does not change so much, and a flat characteristic can be obtained.

なお、本発明におけるトランジスタは、様々なタイプを用いることができ、様々な基板上に形成させることができる。したがって、回路の全てが、ガラス基板上に形成されていてもよいし、プラスチック基板に形成されていてもよいし、単結晶基板に形成されていてもよいし、SOI基板上に形成されていてもよいし、どのような基板上に形成されていてもよい。回路の全てが同じ基板上に形成されていることにより、部品点数を減らしてコストを低減したり、回路部品との接続点数を減らして信頼性を向上させたりすることができる。あるいは、回路の一部が、ある基板に形成されており、回路の別の一部が、別の基板に形成されていてもよい。つまり、回路の全てが同じ基板上に形成されていなくてもよい。例えば、回路の一部は、ガラス基板上にトランジスタを用いて形成し、回路の別の一部は、単結晶基板上に形成し、そのICチップをCOG(Chip On Glass)で接続してガラス基板上に配置してもよい。あるいは、そのICチップをTAB(Tape Automated Bonding)やプリント基板を用いてガラス基板と接続してもよい。このように、回路の一部が同じ基板に形成されていることにより、部品点数を減らしてコストを低減したり、回路部品との接続点数を減らして信頼性を向上させたりすることができる。また、駆動電圧が高い部分や駆動周波数が高い部分は、消費電力が大きくなってしまうので、そのような部分は同じ基板に形成しないようにすれば、消費電力の向上を防ぐことができる。 Note that various types of transistors can be used in the present invention and can be formed over various substrates. Therefore, the entire circuit may be formed on a glass substrate, may be formed on a plastic substrate, may be formed on a single crystal substrate, or may be formed on an SOI substrate. Alternatively, it may be formed on any substrate. Since all the circuits are formed on the same substrate, the number of parts can be reduced to reduce the cost, and the number of connection points with circuit parts can be reduced to improve the reliability. Alternatively, a part of the circuit may be formed on a certain substrate, and another part of the circuit may be formed on another substrate. That is, all of the circuits may not be formed on the same substrate. For example, part of a circuit is formed using a transistor over a glass substrate, another part of the circuit is formed over a single crystal substrate, and the IC chip is connected with COG (Chip On Glass) to form a glass. You may arrange | position on a board | substrate. Alternatively, the IC chip may be connected to the glass substrate using TAB (Tape Automated Bonding) or a printed board. As described above, since a part of the circuit is formed on the same substrate, the number of parts can be reduced to reduce the cost, and the number of connection points with the circuit parts can be reduced to improve the reliability. In addition, since the power consumption increases in a portion where the drive voltage is high or a portion where the drive frequency is high, an improvement in power consumption can be prevented if such a portion is not formed on the same substrate.

なお、本発明においては、一画素とは、明るさを制御できる要素一つ分を示すものとする。よって、一例としては、一画素とは、一つの色要素を示すものとし、その色要素一つで明るさを表現する。従って、そのときは、R(赤)G(緑)B(青)の色要素からなるカラー表示装置の場合には、画像の最小単位は、Rの画素とGの画素とBの画素との三画素から構成されるものとする。なお、色要素は、三色に限定されず、それ以上の数を用いても良いし、RGB以外の色を用いても良い。例えば、白色を加えて、RGBW(Wは白)としてもよい。また、RGBに、例えば、イエロー、シアン、マゼンタ、エメラルドグリーン、朱色などを一色以上追加したものでもよい。また、例えばRGBの中の少なくとも一色について、類似した色を追加してもよい。例えば、R、G、B1、B2としてもよい。B1とB2とは、どちらも青色であるが、少し周波数が異なっている。このような色要素を用いることにより、より実物に近い表示を行うことができたり、消費電力を低減したりすることが出来る。また、別の例としては、1つの色要素について、複数の領域を用いて明るさを制御する場合は、その領域一つ分を一画素とする。よって、一例としては、面積階調を行う場合、一つの色要素につき、明るさを制御する領域が複数あり、その全体で階調を表現するわけであるが、明るさを制御する領域の一つ分を一画素とする。よって、その場合は、一つの色要素は、複数の画素で構成されることとなる。また、その場合、画素によって、表示に寄与する領域の大きさが異なっている場合がある。また、一つの色要素につき複数ある、明るさを制御する領域において、つまり、一つの色要素を構成する複数の画素において、各々に供給する信号を僅かに異ならせるようにして、視野角を広げるようにしてもよい。なお、一画素(三色分)と記載する場合は、RとGとBの三画素分を一画素と考える場合であるとする。一画素(一色分)と記載する場合は、一つの色要素につき、複数の画素がある場合、それらをまとめて一画素と考える場合であるとする。 In the present invention, one pixel represents one element whose brightness can be controlled. Therefore, as an example, one pixel represents one color element, and brightness is expressed by one color element. Therefore, at that time, in the case of a color display device composed of R (red), G (green), and B (blue) color elements, the minimum unit of an image is an R pixel, a G pixel, and a B pixel. It is assumed to be composed of three pixels. Note that the color elements are not limited to three colors, and more than that may be used, or colors other than RGB may be used. For example, RGBW (W is white) may be added by adding white. Further, RGB may be obtained by adding one or more colors such as yellow, cyan, magenta, emerald green, vermilion, and the like. Further, for example, a similar color may be added for at least one of RGB. For example, R, G, B1, and B2 may be used. B1 and B2 are both blue, but have slightly different frequencies. By using such a color element, it is possible to perform display closer to the real thing or to reduce power consumption. As another example, in the case where brightness is controlled using a plurality of areas for one color element, one area corresponds to one pixel. Therefore, as an example, when performing area gradation, there are a plurality of areas for controlling the brightness for each color element, and the gradation is expressed as a whole. One portion is defined as one pixel. Therefore, in that case, one color element is composed of a plurality of pixels. In that case, the size of the region contributing to the display may be different depending on the pixel. Further, in a plurality of brightness control areas for one color element, that is, in a plurality of pixels constituting one color element, a signal supplied to each is slightly different to widen the viewing angle. You may do it. Note that the description of one pixel (for three colors) is a case where three pixels of R, G, and B are considered as one pixel. In the case of describing one pixel (for one color), it is assumed that when there are a plurality of pixels for one color element, they are collectively considered as one pixel.

なお、本発明において、画素は、マトリクス状に配置(配列)されている場合を含んでいる。ここで、画素がマトリクスに配置(配列)されているとは、縦方向もしくは横方向において、直線上に並んで配置されている場合や、ギザギザな線上に並んでいる場合を含んでいる。よって、例えば三色の色要素(例えばRGB)でフルカラー表示を行う場合に、ストライプ配置されている場合や、三つの色要素のドットがいわゆるデルタ配置されている場合も含むものとする。さらに、ベイヤー配置されている場合も含んでいる。なお、色要素は、三色に限定されず、それ以上でもよく、例えば、RGBW(Wは白)や、RGBに、イエロー、シアン、マゼンタなどを一色以上追加したものなどがある。また、色要素のドット毎にその表示領域の大きさが異なっていてもよい。これにより、消費電力を低下させたり、表示素子の寿命を延ばしたりすることが出来る。 In the present invention, the case where the pixels are arranged (arranged) in a matrix is included. Here, the arrangement (arrangement) of pixels in a matrix includes a case where pixels are arranged side by side in a vertical direction or a horizontal direction or a case where they are arranged on a jagged line. Therefore, for example, when full color display is performed with three color elements (for example, RGB), the case where stripes are arranged and the case where dots of three color elements are arranged in a so-called delta are also included. Furthermore, the case where a Bayer is arranged is also included. Note that the color elements are not limited to three colors, and may be more than that, for example, RGBW (W is white) or RGB in which one or more colors of yellow, cyan, magenta, and the like are added. Further, the size of the display area may be different for each dot of the color element. Thereby, power consumption can be reduced and the lifetime of the display element can be extended.

なお、トランジスタとは、それぞれ、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことが出来る。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるため、いずれがソースまたはドレインであるかを限定することが困難である。そこで、本発明においては、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一例としては、それぞれを第1端子、第2端子と表記する場合がある。 Note that a transistor is an element having at least three terminals including a gate, a drain, and a source, and has a channel region between the drain region and the source region. Current can flow through the source region. Here, since the source and the drain vary depending on the structure and operating conditions of the transistor, it is difficult to limit which is the source or the drain. Therefore, in the present invention, a region functioning as a source and a drain may not be called a source or a drain. In that case, as an example, there are cases where they are referred to as a first terminal and a second terminal, respectively.

なお、トランジスタは、ベースとエミッタとコレクタとを含む少なくとも三つの端子を有する素子であってもよい。この場合も同様に、エミッタとコレクタとを、第1端子、第2端子と表記する場合がある。 Note that the transistor may be an element having at least three terminals including a base, an emitter, and a collector. Similarly in this case, the emitter and the collector may be referred to as a first terminal and a second terminal.

なお、ゲートとは、ゲート電極とゲート配線(ゲート線またはゲート信号線等とも言う)とを含んだ全体、もしくは、それらの一部のことを言う。ゲート電極とは、チャネル領域やLDD(Lightly Doped Drain)領域などを形成する半導体と、ゲート絶縁膜を介してオーバーラップしている部分の導電膜のことを言う。ゲート配線とは、各画素のゲート電極の間を接続したり、ゲート電極と別の配線とを接続したりするための配線のことを言う。 Note that a gate refers to the whole or part of a gate electrode and a gate wiring (also referred to as a gate line or a gate signal line). A gate electrode refers to a conductive film which overlaps with a semiconductor that forms a channel region, an LDD (Lightly Doped Drain) region, and the like with a gate insulating film interposed therebetween. The gate wiring refers to wiring for connecting between the gate electrodes of each pixel or connecting the gate electrode to another wiring.

ただし、ゲート電極としても機能し、ゲート配線としても機能するような部分も存在する。そのような部分は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。つまり、ゲート電極とゲート配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているゲート配線とオーバーラップしてチャネル領域がある場合、その領域はゲート配線として機能しているが、ゲート電極としても機能していることになる。よって、そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。 However, there is a portion that functions as a gate electrode and also functions as a gate wiring. Such a portion may be called a gate electrode or a gate wiring. That is, there is a region where the gate electrode and the gate wiring cannot be clearly distinguished. For example, when there is a channel region that overlaps with an extended gate wiring, the region functions as a gate wiring, but also functions as a gate electrode. Therefore, such a region may be called a gate electrode or a gate wiring.

また、ゲート電極と同じ材料で形成され、ゲート電極とつながっている領域も、ゲート電極と呼んでも良い。同様に、ゲート配線と同じ材料で形成され、ゲート配線とつながっている領域も、ゲート配線と呼んでも良い。このような領域は、厳密な意味では、チャネル領域とオーバーラップしていなかったり、別のゲート電極と接続させる機能を有してなかったりする場合がある。しかし、製造工程の関係上、ゲート電極やゲート配線と同じ材料で形成され、ゲート電極やゲート配線とつながっている領域がある。よって、そのような領域もゲート電極やゲート配線と呼んでも良い。 A region formed of the same material as the gate electrode and connected to the gate electrode may also be called a gate electrode. Similarly, a region formed of the same material as the gate wiring and connected to the gate wiring may be called a gate wiring. In a strict sense, such a region may not overlap with the channel region or may not have a function of being connected to another gate electrode. However, due to the manufacturing process, there is a region formed of the same material as the gate electrode and the gate wiring and connected to the gate electrode and the gate wiring. Therefore, such a region may also be called a gate electrode or a gate wiring.

また、例えば、マルチゲートのトランジスタにおいて、1つのトランジスタのゲート電極と、別のトランジスタのゲート電極とは、ゲート電極と同じ材料で形成された導電膜で接続される場合が多い。そのような領域は、ゲート電極とゲート電極とを接続させるための領域であるため、ゲート配線と呼んでも良いが、マルチゲートのトランジスタを1つのトランジスタであると見なすことも出来るため、ゲート電極と呼んでも良い。つまり、ゲート電極やゲート配線と同じ材料で形成され、それらとつながって配置されているものは、ゲート電極やゲート配線と呼んでも良い。

また、例えば、ゲート電極とゲート配線とを接続してさせている部分の導電膜も、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。

For example, in a multi-gate transistor, the gate electrode of one transistor and the gate electrode of another transistor are often connected by a conductive film formed using the same material as the gate electrode. Such a region is a region for connecting the gate electrode and the gate electrode, and may be referred to as a gate wiring. However, a multi-gate transistor can be regarded as a single transistor, and thus the gate electrode You can call it. That is, what is formed of the same material as the gate electrode and the gate wiring and is connected to the gate electrode and the gate wiring may be called a gate electrode and a gate wiring.

For example, a portion of the conductive film where the gate electrode and the gate wiring are connected may be called a gate electrode or a gate wiring.

なお、ゲート端子とは、ゲート電極の領域や、ゲート電極と電気的に接続されている領域について、その一部分のことを言う。 Note that a gate terminal refers to a part of a region of a gate electrode or a region electrically connected to the gate electrode.

なお、ソースとは、ソース領域とソース電極とソース配線(ソース線またはソース信号線等とも言う)とを含んだ全体、もしくは、それらの一部のことを言う。ソース領域とは、P型不純物(ボロンやガリウムなど)やN型不純物(リンやヒ素など)が多く含まれる半導体領域のことを言う。従って、少しだけP型不純物やN型不純物が含まれる領域、いわゆる、LDD(Lightly Doped Drain)領域は、ソース領域には含まれない。ソース電極とは、ソース領域とは別の材料で形成され、ソース領域と電気的に接続されて配置されている部分の導電層のことを言う。ただし、ソース電極は、ソース領域も含んでソース電極と呼ぶこともある。ソース配線とは、各画素のソース電極の間を接続したり、ソース電極と別の配線とを接続したりするための配線のことを言う。 Note that a source refers to the whole or part of a source region, a source electrode, and a source wiring (also referred to as a source line, a source signal line, or the like). The source region refers to a semiconductor region containing a large amount of P-type impurities (such as boron and gallium) and N-type impurities (such as phosphorus and arsenic). Therefore, a region containing a little P-type impurity or N-type impurity, that is, a so-called LDD (Lightly Doped Drain) region is not included in the source region. A source electrode refers to a portion of a conductive layer which is formed using a material different from that of a source region and is electrically connected to the source region. However, the source electrode may be referred to as a source electrode including the source region. The source wiring is a wiring for connecting between the source electrodes of each pixel or connecting the source electrode and another wiring.

しかしながら、ソース電極としても機能し、ソース配線としても機能するような部分も存在する。そのような部分は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。つまり、ソース電極とソース配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているソース配線とオーバーラップしてソース領域がある場合、その領域はソース配線として機能しているが、ソース電極としても機能していることになる。よって、そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。 However, there is a portion that functions as a source electrode and also functions as a source wiring. Such a portion may be called a source electrode or a source wiring. That is, there is a region where the source electrode and the source wiring cannot be clearly distinguished. For example, when there is a source region that overlaps with an extended source wiring, the region functions as a source wiring, but also functions as a source electrode. Therefore, such a region may be called a source electrode or a source wiring.

また、ソース電極と同じ材料で形成され、ソース電極とつながっている領域や、ソース電極とソース電極とを接続する部分も、ソース電極と呼んでも良い。また、ソース領域とオーバーラップしている部分も、ソース電極と呼んでも良い。同様に、ソース配線と同じ材料で形成され、ソース配線とつながっている領域も、ソース配線と呼んでも良い。このような領域は、厳密な意味では、別のソース電極と接続させる機能を有していたりすることがない場合がある。しかし、製造工程の関係上、ソース電極やソース配線と同じ材料で形成され、ソース電極やソース配線とつながっている領域がある。よって、そのような領域もソース電極やソース配線と呼んでも良い。 A region formed of the same material as the source electrode and connected to the source electrode, or a portion connecting the source electrode and the source electrode may also be referred to as a source electrode. A portion overlapping with the source region may also be called a source electrode. Similarly, a region formed of the same material as the source wiring and connected to the source wiring may be called a source wiring. In a strict sense, such a region may not have a function of connecting to another source electrode. However, due to the manufacturing process, there is a region formed of the same material as the source electrode and the source wiring and connected to the source electrode and the source wiring. Therefore, such a region may also be called a source electrode or a source wiring.

また、例えば、ソース電極とソース配線とを接続させている部分の導電膜も、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。 Further, for example, a conductive film in a portion where the source electrode and the source wiring are connected may be called a source electrode or a source wiring.

なお、ソース端子とは、ソース領域の領域や、ソース電極や、ソース電極と電気的に接続されている領域について、その一部分のことを言う。 Note that a source terminal refers to a part of a source region, a source electrode, or a region electrically connected to the source electrode.

なお、ドレインについては、ソースと同様である。 The drain is the same as the source.

なお、本発明において、半導体装置とは半導体素子(トランジスタやダイオードなど)を含む回路を有する装置をいう。また、半導体特性を利用することで機能しうる装置全般でもよい。 Note that in the present invention, a semiconductor device refers to a device having a circuit including a semiconductor element (such as a transistor or a diode). In addition, any device that can function by utilizing semiconductor characteristics may be used.

また、表示装置とは、表示素子(液晶素子や発光素子など)を有する装置のことを言う。なお、液晶素子やEL素子などの表示素子を含む複数の画素やそれらの画素を駆動させる周辺駆動回路が同一基板上に形成された表示パネル本体のことでもよい。また、ワイヤボンディングやバンプなどによって基板上に配置された周辺駆動回路、いわゆるチップオングラス(COG)を含んでいても良い。さらに、フレキシブルプリントサーキット(FPC)やプリント配線基盤(PWB)が取り付けられたもの(ICや抵抗素子や容量素子やインダクタやトランジスタなど)も含んでもよい。さらに、偏光板や位相差板などの光学シートを含んでいても良い。さらに、バックライトユニット(導光板やプリズムシートや拡散シートや反射シートや光源(LEDや冷陰極管など)を含んでいても良い)を含んでいても良い。 A display device refers to a device having a display element (such as a liquid crystal element or a light-emitting element). Note that a display panel body in which a plurality of pixels including display elements such as a liquid crystal element and an EL element and peripheral drive circuits for driving these pixels are formed over the same substrate may be used. Further, it may include a peripheral drive circuit, so-called chip on glass (COG), which is disposed on the substrate by wire bonding or bumps. Furthermore, a device to which a flexible printed circuit (FPC) or a printed wiring board (PWB) is attached (such as an IC, a resistor, a capacitor, an inductor, or a transistor) may also be included. Furthermore, an optical sheet such as a polarizing plate or a retardation plate may be included. Furthermore, a backlight unit (which may include a light guide plate, a prism sheet, a diffusion sheet, a reflection sheet, and a light source (such as an LED or a cold cathode tube)) may be included.

また、発光装置とは、特にEL素子やFEDで用いる素子などの自発光型の表示素子を有している表示装置をいう。液晶表示装置とは、液晶素子を有している表示装置をいう。 A light-emitting device refers to a display device including a self-luminous display element such as an EL element or an element used in an FED. A liquid crystal display device refers to a display device having a liquid crystal element.

なお、本発明において、ある物の上に形成されている、あるいは、〜上に形成されている、というように、〜の上に、あるいは、〜上に、という記載については、ある物の上に直接接していることに限定されない。直接接してはいない場合、つまり、間に別のものが挟まっている場合も含むものとする。従って例えば、層Aの上に(もしくは層A上に)、層Bが形成されている、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層(例えば層Cや層Dなど)が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。また、〜の上方に、という記載についても同様であり、ある物の上に直接接していることに限定されず、間に別のものが挟まっている場合も含むものとする。従って例えば、層Aの上方に、層Bが形成されている、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層(例えば層Cや層Dなど)が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。なお、〜の下に、あるいは、〜の下方に、の場合についても、同様であり、直接接している場合と、接していない場合とを含むこととする。 In addition, in the present invention, it is formed on a certain object, or is formed on the top. It is not limited to being in direct contact with. This includes cases where they are not in direct contact, that is, cases where another object is sandwiched between them. Therefore, for example, when the layer B is formed on the layer A (or on the layer A), the case where the layer B is formed in direct contact with the layer A and the case where the layer B is formed In which another layer (for example, layer C or layer D) is formed in direct contact with layer B and layer B is formed in direct contact therewith. The same applies to the description of “above”, and it is not limited to being in direct contact with a certain object, and includes a case where another object is sandwiched therebetween. Therefore, for example, when the layer B is formed above the layer A, the case where the layer B is formed in direct contact with the layer A and the case where another layer is formed in direct contact with the layer A. (For example, the layer C or the layer D) is formed, and the layer B is formed in direct contact therewith. It should be noted that the same applies to the case of below or below, and includes the case of direct contact and the case of no contact.

本発明により、入力信号を負電源側、及び正電源側に同時にレベルシフトできるレベルシフタを有する表示装置を提供することができる。また、本発明の表示装置は全て同じ導電型のトランジスタで構成することができるため、低コストな表示装置を提供することができる。 According to the present invention, it is possible to provide a display device having a level shifter capable of simultaneously shifting the level of an input signal to a negative power source side and a positive power source side. In addition, since all the display devices of the present invention can be formed using transistors having the same conductivity type, a low-cost display device can be provided.

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において同様のものに関しては共通の符号を用いて示し、同一部分又は同様な機能を有する部分の詳細な説明は省略する。 Hereinafter, embodiments of the present invention will be described with reference to the drawings. However, the present invention can be implemented in many different modes, and those skilled in the art can easily understand that the modes and details can be variously changed without departing from the spirit and scope of the present invention. Is done. Therefore, the present invention is not construed as being limited to the description of this embodiment mode. In addition, in the structure of this invention demonstrated below, regarding the same thing, it shows using a common code | symbol and detailed description of the part which has the same part or the same function is abbreviate | omitted.

(第1の実施形態)

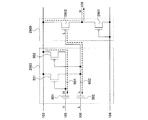

本実施形態では、本発明に係るレベルシフタの基本構成について、図1(a)を参照して説明する。

(First embodiment)

In the present embodiment, the basic configuration of the level shifter according to the present invention will be described with reference to FIG.

図1(a)に示すレベルシフタは、回路101、回路102を有している。 The level shifter illustrated in FIG. 1A includes a circuit 101 and a circuit 102.

図1(a)のレベルシフタに示すように、回路101は、配線103、配線104、配線105、配線106、配線107、配線108に接続されている。回路102は、配線103、配線104、配線107、配線108、配線109に接続されている。

As shown in the level shifter of FIG. 1A, the circuit 101 is connected to a

なお、配線103及び配線104には、正電源VDD及び負電源VSSがそれぞれ供給されている。また、電源電位VDDは、電源電位VSSよりも高い電圧である。

Note that a positive power supply VDD and a negative power supply VSS are supplied to the

また、配線105及び配線106には、信号(以下、入力信号ともいう)が供給されている。なお、回路101は、配線105及び配線106に供給される信号によって制御されている。

In addition, a signal (hereinafter also referred to as an input signal) is supplied to the

また、配線107及び配線108には、回路101からの信号(以下、オフセット信号ともいう)が供給されている。なお、回路102は、配線107及び配線108に供給される信号によって制御されている。

A signal from the circuit 101 (hereinafter also referred to as an offset signal) is supplied to the

また、配線109には、回路102からの信号(以下、出力信号ともいう)が供給されている。

Further, a signal from the circuit 102 (hereinafter also referred to as an output signal) is supplied to the

なお、配線105及び配線106に供給される信号は、2値の値を持つデジタル信号である。これらのデジタル信号の電位は、H信号(以下、Hレベルともいう)のときには電位VHであり、L信号(以下、Lレベルともいう)のときには電位VLである。なお、電位VHは、電源電位VDDよりも低く、電位VLよりも高い電圧である。なお、電位VLは、電源電位VSSよりも高く、電位VHよりも低い電位である。つまり、各電源電位と信号の電位の関係は、電源電位VDD>電位VH>電位VL>電源電位VSSとなっている。

Note that signals supplied to the

次に、図1(a)で示したレベルシフタの動作について、図2(a)のタイミングチャートを参照して説明する。なお、図2(a)のタイミングチャートは、配線105の信号、配線107の信号、及び配線108の信号を示している。なお、図示はしないが、配線106の信号は、配線105の信号に対して、Hレベル、Lレベルが反転したものと同様である。

Next, the operation of the level shifter shown in FIG. 1A will be described with reference to the timing chart of FIG. Note that the timing chart in FIG. 2A shows a signal of the

ここで、回路101は、オフセット動作をする機能を有する。具体的には、回路101は、配線105及び配線106に供給されている入力信号をオフセットして、配線107、及び配線108にオフセット信号を供給する。このオフセット信号は、配線105に供給されている信号と同じタイミング(若しくは反転)であり、おおむね等しい振幅電圧である。そして、配線107に供給するオフセット信号は、入力信号に対して電位がH側にシフトしている。また、配線108に供給するオフセット信号は、入力信号に対して電位がL側にシフトしている。なお、回路101をオフセット回路ともいう。

Here, the circuit 101 has a function of performing an offset operation. Specifically, the circuit 101 offsets an input signal supplied to the

よって、図2(a)のタイミングチャートに示すように、配線107の信号は、配線105の信号と比較して、タイミング、及び振幅電圧が配線105の信号とおおむね等しく、電位がH側にシフトしている。具体的には、配線107の信号は、L信号の電位がVDDであり、H信号の電位がVDD+(VH−VL)である。つまり、配線107の信号の振幅電圧はVH−VLであり、配線105の信号の振幅電圧とおおむね同じである。

Therefore, as shown in the timing chart of FIG. 2A, the signal of the

配線107の信号と同様に、配線108の信号は、配線105の信号と比較して、タイミング、及び振幅電圧が配線105の信号とおおむね同じであり、電位がL側にシフトしている。具体的には、配線108の信号は、L信号の電位がVSSであり、H信号の電位がVSS+(VH−VL)である。つまり、配線108の信号の振幅電圧はVH−VLであり、配線105の信号の振幅電圧とおおむね同じである。

Similar to the signal of the

なお、すでに述べたように、配線107の信号、及び配線108の信号は、配線105の信号と比較して、H信号、L信号が反転していてもよい。

Note that as described above, the signal of the

なお、図2(b)に示すように、配線107の信号は、L信号をVDD−(VH−VL)、H信号をVDDとしてもよい。また、配線108の信号は、L信号をVSS−(VH−VL)としてもよい。図2(b)に示す場合でも、配線107の信号の振幅電圧、及び配線108の信号の振幅電圧は、VH−VLであり、配線105の信号の振幅電圧とおおむね同じである。

2B, the signal of the

なお、図2(b)に示す配線107の信号、及び配線108の信号も、配線105の信号と比較して、H信号・L信号が反転していてもよい。

Note that the signal of the

ここで、回路102は、インバータ、NAND回路、NOR回路などの論理回路である。具体的には、回路102は、オフセット信号によって制御され、配線109に出力信号を供給する。また、出力信号の電位は、H信号のときには電源電位VDDと等しく、L信号のときには電源電位VSSと等しい。

Here, the circuit 102 is a logic circuit such as an inverter, a NAND circuit, or a NOR circuit. Specifically, the circuit 102 is controlled by the offset signal and supplies an output signal to the

なお、配線107の信号、及び配線108の信号は振幅電圧が小さいため、回路102は貫通電流が少なくなるため省電力化を実現できる。また、回路102は、入力される信号の振幅電圧が小さいためノイズを低減できる。

Note that since the amplitude voltage of the signal of the

以上説明したように、本発明のレベルシフタは、オフセット信号によって、論理回路を駆動することで、レベルシフタとしての機能を実現する。また、本発明のレベルシフタは、省電力であり、低ノイズである。また、本発明のレベルシフタは、1つのレベルシフタによって、入力信号のHレベル、及びLレベルを同時にレベルシフトできる。 As described above, the level shifter of the present invention realizes a function as a level shifter by driving a logic circuit with an offset signal. In addition, the level shifter of the present invention is power saving and low noise. The level shifter of the present invention can simultaneously shift the H level and the L level of the input signal with one level shifter.

なお、図1(b)に示すように、回路102は、配線105の信号、及び配線106の信号をH側にシフトした信号(配線107の信号)だけで、制御されていてもよい。また、回路102が配線107の信号だけで制御される場合、回路101には、電源電位VSSを供給しなくてもよい。

Note that as illustrated in FIG. 1B, the circuit 102 may be controlled only by a signal of the

同様に、図1(c)に示すように、回路102は、配線105の信号、及び配線106の信号をL側だけにシフトした信号(配線108の信号)だけで、制御されていてもよい。また、回路102が配線108の信号だけで制御される場合、回路101には、電源電位VDDを供給しなくてもよい。

Similarly, as illustrated in FIG. 1C, the circuit 102 may be controlled only by the signal of the

また、回路102が配線107の信号、若しくは配線108の信号だけで制御されることによって、図1(b)、及び図1(c)のレベルシフタは回路101を簡単な構成にできる。

Further, when the circuit 102 is controlled only by the signal of the

なお、本実施形態は、本明細書中の他の実施形態のいかなる記載とも自由に組み合わせて実施することができる。また、本実施形態中のいかなる記載も自由に組み合わせて実施することができる。 Note that this embodiment mode can be freely combined with any description in other embodiment modes in this specification. In addition, any description in the present embodiment can be implemented in any combination.

(第2の実施形態)

本実施形態では、第1の実施形態に示したレベルシフタが有する回路101(オフセット回路)の構成例について説明する。なお、本実施形態では、配線105、及び配線106に供給される信号を、同じタイミング(若しくは反転)、及びおおむね等しい振幅電圧のまま、電位をH側にシフトさせて、配線107に供給する場合の構成例について説明する。

(Second Embodiment)

In this embodiment, a configuration example of the circuit 101 (offset circuit) included in the level shifter shown in the first embodiment will be described. In this embodiment, the signal supplied to the

なお、実施の形態1と同様のものに関しては共通の符号を用いて示し、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

Note that components similar to those in

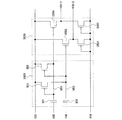

まず、オフセット回路の構成例を図3(a)を参照して説明する。 First, a configuration example of the offset circuit will be described with reference to FIG.

図3(a)に示すオフセット回路は、容量素子301、容量素子302、トランジスタ303、及びトランジスタ304を有している。

The offset circuit illustrated in FIG. 3A includes a

図3(a)のオフセット回路に示すように、容量素子301の第1電極が配線105に接続されている。容量素子302の第1電極が配線106に接続されている。トランジスタ303のゲートが容量素子301の第2電極に接続され、第1端子が配線103に接続され、第2端子が容量素子302の第2電極に接続されている。トランジスタ304のゲートが容量素子302の第2電極に接続され、第1端子が配線103に接続され、第2端子が容量素子301の第2電極に接続されている。なお、容量素子301の第2電極、トランジスタ303のゲート、及びトランジスタ304の第2端子の接続点を節点N31とする。なお、容量素子302の第2電極、トランジスタ303の第2端子、及びトランジスタ304のゲートの接続点を節点N32とする。なお、節点N31と節点N32のうちのどちらかが、図1に示す配線107(a)に接続されている。

As shown in the offset circuit in FIG. 3A, the first electrode of the

次に、図3(a)で示したオフセット回路の動作について、図3(b)、及び図3(c)を参照して説明する。 Next, the operation of the offset circuit shown in FIG. 3A will be described with reference to FIGS. 3B and 3C.

なお、図3(b)は、配線105の信号がH信号からL信号、配線106の信号がL信号からH信号に変化した場合の図3(a)のオフセット回路の動作を示している。

3B shows the operation of the offset circuit in FIG. 3A when the signal of the

また、図3(c)は、配線105の信号がL信号からH信号、配線106の信号がH信号からL信号に変化した場合の図3(a)のオフセット回路の動作を示している。つまり、図3(a)のオフセット回路は、図3(b)の動作と図3(c)の動作を任意のタイミングで繰り返している。また、図3(b)の動作を第1の動作とし、図3(c)の動作を第2の動作とする。

FIG. 3C shows the operation of the offset circuit in FIG. 3A when the signal of the

なお、VH−VLは、トランジスタ303、及びトランジスタ304のしきい値電圧以上である。

Note that VH−VL is higher than or equal to the threshold voltages of the

まず、図3(a)のオフセット回路の第1の動作について、図3(b)を参照して説明する。なお、節点N32の初期値の電位をVDDとする。 First, the first operation of the offset circuit of FIG. 3A will be described with reference to FIG. Note that the initial potential of the node N32 is VDD.

初期状態として、容量素子302には、配線106の電位VL(L信号)と、節点N32の電位VDDとの電位差VDD−VLが保持されている。そして、配線106の電位がVLからVHに変化すると、節点N32の電位は容量素子302の容量結合によってVDD+(VH−VL)となる。したがって、トランジスタ304がオンする。

As an initial state, the

また、トランジスタ304がオンすることによって、節点N31には電源電位VDDが供給され、節点N31の電位がVDDになる。したがって、容量素子301は、配線105の電位VL(L信号)と、節点N31の電位VDDとの電位差VDD−VLを保持する。また、トランジスタ303がオフする。

When the

また、トランジスタ303がオフすることで、節点N32はフローティング状態になり、節点N32は電位をVDD+(VH−VL)に維持する。

Further, when the

次に、図3(a)のオフセット回路の第2の動作について、図3(c)を参照して説明する。 Next, the second operation of the offset circuit of FIG. 3A will be described with reference to FIG.

すでに述べたように、容量素子301には、第1の動作によって、VDD−VLが保持されている。そして、配線105の電位がVLからVHに変化すると、節点N31の電位は容量素子301の容量結合によって、VDD+(VH−VL)となる。したがって、トランジスタ303がオンする。

As already described, VDD-VL is held in the

また、トランジスタ303がオンすることによって、節点N32には電源電位VDDが供給され、節点N32の電位がVDDになる。したがって、容量素子302は、配線106の電位VL(L信号)と、節点N32の電位VDDとの電位差VDD−VLを保持する。また、トランジスタ304がオフする。

When the

また、トランジスタ304がオフすることで、節点N31はフローティング状態になり、節点N31は電位をVDD+(VH−VL)に維持する。

Further, when the

ここで、容量素子301、容量素子302、トランジスタ303、及びトランジスタ304が有する機能について説明する。

Here, functions of the

まず、容量素子301は、第1の動作において、配線105の電位VLと、節点N31の電位VDDとの電位差を保持する。そして、容量素子301は、第2の動作において、容量結合によって、配線105の電位の上昇にしたがって、節点N31の電位を上昇させる機能を有する。

First, in the first operation, the

また、容量素子302は、第2の動作において、配線106の電位VLと、節点N32の電位VDDとの電位差を保持する。そして、容量素子302は、第1の動作において、容量結合によって、配線106の電位の上昇にしたがって、節点N32の電位を上昇させる機能を有する。

Further, in the second operation, the

また、トランジスタ303は、節点N31の電位によって、配線103と節点N32とを接続するかしないかを選択するスイッチとしての機能を有する。また、トランジスタ303は、第1の動作において、オフし、節点N32をフローティング状態にする。また、トランジスタ303は、第2の動作において、オンし、節点N32に電源電位VDDを供給する。

The

また、トランジスタ304は、節点N32の電位によって、配線103と節点N31とを接続するかしないかを選択するスイッチとしての機能を有する。また、トランジスタ304は、第1の動作において、オンし、節点N31に電源電位VDDを供給する。また、トランジスタ304は、第2の動作において、オフし、節点N31をフローティング状態にする。

The

以上説明した第1の動作、及び第2の動作によって、図3(a)のオフセット回路は、第1の動作において、節点N31には電源電位VDDを供給し、節点N32をフローティング状態にし、節点N32の電位をVDD+(VH−VL)に維持するように動作する。また、図3(a)のオフセット回路は、第2の動作において、節点N31をフローティング状態にし、節点N31の電位をVDD+(VH−VL)に維持し、節点N32には電源電位VDDを供給するように動作する。 By the first operation and the second operation described above, in the first operation, the offset circuit in FIG. 3A supplies the power supply potential VDD to the node N31, sets the node N32 in a floating state, and It operates so as to maintain the potential of N32 at VDD + (VH−VL). Further, in the second operation, the offset circuit of FIG. 3A places the node N31 in a floating state, maintains the potential of the node N31 at VDD + (VH−VL), and supplies the power supply potential VDD to the node N32. To work.

したがって、図3(a)のオフセット回路が生成する信号は、H信号がVDD+(VH−VL)であり、L信号がVDDである。つまり、図3(a)のオフセット回路は、電源電位VDDを基準とした信号を生成することができる。 Therefore, in the signal generated by the offset circuit of FIG. 3A, the H signal is VDD + (VH−VL) and the L signal is VDD. That is, the offset circuit in FIG. 3A can generate a signal based on the power supply potential VDD.

なお、第1の動作における節点N32の電位、及び第2の動作における節点N31の電位は、VDD+(VH−VL)を維持するとした。しかし、実際には、第1の動作における節点N32の電位、及び第2の動作における節点N31の電位は、配線容量や寄生容量の影響などによって、VDD+(VH−VL)よりも低くなる。したがって、配線容量や寄生容量の影響を少なくするために、容量素子301、及び容量素子302の容量値は、配線容量や寄生容量の容量値よりも十分大きくしておけばよい。

Note that the potential of the node N32 in the first operation and the potential of the node N31 in the second operation are maintained at VDD + (VH−VL). However, in reality, the potential of the node N32 in the first operation and the potential of the node N31 in the second operation are lower than VDD + (VH−VL) due to the influence of wiring capacitance and parasitic capacitance. Therefore, in order to reduce the influence of the wiring capacitance and the parasitic capacitance, the capacitance values of the

なお、節点N31を図1(a)に示す配線107に接続すれば、配線105に供給されている信号とHレベル、Lレベルが同じ信号を配線107に供給することができる。同様に、節点N32を図1に示す配線107に接続すれば、配線105に供給されている信号とH信号、L信号が反転した信号を配線107に供給することができる。

Note that if the node N31 is connected to the

また、節点N31を配線107に接続する場合には、容量素子302の容量値は、容量素子301の容量値よりも小さいことが好ましい。なぜなら、すでに述べたように、容量素子301の容量値は、配線容量や寄生容量の容量値よりも十分大きくしておけばよいと説明したが、節点N32の電位はトランジスタ304をオンできれば、節点N32の電位はVDD+(VH−VL)にならなくてもよいからである。したがって、容量素子302の容量値を容量素子301の容量値よりも小さくできるため、容量素子302の素子領域を小さくできる。

In the case where the node N31 is connected to the

また、節点N32を配線107に接続する場合には、節点N31を配線107に接続する場合と同様の理由で、容量素子301の容量値は容量素子302の容量値よりも小さくすることが好ましい。

In addition, when the node N32 is connected to the

なお、容量素子301、及び容量素子302は、絶縁層を2つの電極層で挟持した構成でもよい。容量素子301、及び容量素子302を絶縁層を2つの電極層で挟持した構成にすることで、容量素子301、及び容量素子302は印加される電圧に関係なく容量値を一定に保つことができるため、本発明のレベルシフタは安定して動作できる。

Note that the

また、容量素子301、及び容量素子302の絶縁層は、ゲート絶縁膜であることが好ましい。なぜなら、ゲート絶縁膜の膜厚は、一般的に他の絶縁膜(例えば、層間膜、平坦化膜など)に比べ薄いため、容量素子301、及び容量素子302は効率的に容量値を得ることができるからである。

The insulating layer of the

なお、容量素子301、及び容量素子302は、MOS構造の容量素子としてもよい。容量素子301、及び容量素子302をMOS構造の容量素子とした場合の構成を図4(a)に示す。図4(a)に示すオフセット回路は、容量素子301の代わりにNチャネル型のトランジスタ401を用い、容量素子302の代わりにNチャネル型のトランジスタ402を用いている。また、トランジスタ401は、ゲートが節点N31に接続され、第1端子、及び第2端子が配線105に接続されていることを特徴とする。なぜなら、節点N31の電位は配線105の電位よりも高いため、トランジスタ401がオンして、チャネルがトランジスタ401のチャネル領域に形成されるため、トランジスタ401は容量素子として動作できるからである。同様に、トランジスタ402は、ゲートが節点N32に接続され、第1端子、及び第2端子が配線106に接続されていることを特徴とする。なぜなら、節点N32電位は配線106の電位よりも高いため、トランジスタ402がオンして、チャネルがトランジスタ402のチャネル領域に形成されるため、トランジスタ402は容量素子として動作できるからである。

Note that the

また、図4(b)のように、容量素子として、Pチャネル型のトランジスタを容量素子として用いることもできる。図4(b)に示すオフセット回路は、容量素子301の代わりにPチャネル型のトランジスタ403を用い、容量素子302の代わりにPチャネル型のトランジスタ404を用いている。また、トランジスタ403は、ゲートが配線105に接続され、第1端子、及び第2端子が節点N31に接続されていることを特徴とする。なぜなら、節点N31の電位は、配線105の電位よりも高いため、トランジスタ403がオンして、チャネルがトランジスタ403のチャネル領域に形成されるため、トランジスタ403が容量素子として動作できるからである。同様に、トランジスタ404は、ゲートが配線106に接続され、第1端子、及び第2端子が節点N32に接続されていることを特徴とする。なぜなら、節点N32の電位は配線106の電位よりも高いため、トランジスタ404がオンして、チャネルがトランジスタ404のチャネル領域に形成されるため、トランジスタ404は容量素子として動作できるからである。

As shown in FIG. 4B, a P-channel transistor can be used as the capacitor as the capacitor. The offset circuit illustrated in FIG. 4B uses a P-

なお、すでに述べたように、図4(a)において、節点N31を配線107に接続する場合には、トランジスタ401のチャネル領域(L:チャネル長×W:チャネル幅)よりも、トランジスタ402のチャネル領域のほうが小さいことが好ましい。また、節点N32を配線107に接続する場合には、トランジスタ401のチャネル領域よりも、トランジスタ402のチャネル領域のほうが大きいほうが好ましい。

4A, when the node N31 is connected to the

また、同様に、図4(b)において、節点N31を配線107に接続する場合には、トランジスタ403のチャネル領域(L:チャネル長×W:チャネル幅)よりも、トランジスタ404のチャネル領域のほうが小さいことが好ましい。また、節点N32を配線107に接続する場合には、トランジスタ403のチャネル領域よりも、トランジスタ404のチャネル領域のほうが大きいほうが好ましい。

Similarly, in FIG. 4B, when the node N31 is connected to the

ここで、図3(a)に示したオフセット回路は、Nチャネル型のトランジスタと容量素子とで構成したが、Pチャネル型のトランジスタと容量素子とで構成されていてもよい。Pチャネル型のトランジスタと容量素子とで構成した場合のオフセット回路を図5(a)に示す。 Here, the offset circuit illustrated in FIG. 3A is configured with an N-channel transistor and a capacitor, but may be configured with a P-channel transistor and a capacitor. FIG. 5A shows an offset circuit in the case where it is configured by a P-channel transistor and a capacitor.

図5(a)に示すオフセット回路は、容量素子301、容量素子302、トランジスタ501、及びトランジスタ502を有している。

The offset circuit illustrated in FIG. 5A includes a

なお、トランジスタ501、及びトランジスタ502は、図3(a)のトランジスタ303、及びトランジスタ304に、それぞれ対応し、それぞれ同様な機能を有する。また、節点N51、及び節点N52は、図3(a)のトランジスタ節点N31、及び節点N32に、それぞれ対応している。

Note that the

図5(a)のオフセット回路に示すように、容量素子301の第1電極が配線105に接続されている。容量素子302の第1電極が配線106に接続されている。トランジスタ501のゲートが容量素子301の第2電極に接続され、第1端子が配線103に接続され、第2端子が容量素子302の第2電極に接続されている。トランジスタ502のゲートが容量素子302の第2電極に接続され、第1端子が配線103に接続され、第2端子が容量素子301の第2電極に接続されている。なお、容量素子301の第2電極、トランジスタ501のゲート、及びトランジスタ502の第2端子の接続点を節点N51とする。なお、容量素子302の第2電極、トランジスタ501の第2端子、及びトランジスタ502のゲートの接続点を節点N52とする。なお、節点N51と節点N52のうちのどちらかが、図1(a)に示す配線107に接続されている。

As shown in the offset circuit of FIG. 5A, the first electrode of the

次に、図5(a)で示したオフセット回路の動作について、図5(b)、及び図5(c)を参照して説明する。 Next, the operation of the offset circuit shown in FIG. 5A will be described with reference to FIGS. 5B and 5C.

なお、図5(b)は、配線105の信号がH信号からL信号、配線106の信号がL信号からH信号に変化した場合の図5(a)のオフセット回路の動作を示している。

FIG. 5B shows the operation of the offset circuit in FIG. 5A when the signal of the

また、図5(c)は、配線105の信号がL信号からH信号、配線106の信号がH信号からL信号に変化した場合の図5(a)のオフセット回路の動作を示している。つまり、図5(a)のオフセット回路は、図5(b)の動作と図5(c)の動作を任意のタイミングで繰り返している。また、図5(b)の動作を第1の動作とし、図5(c)の動作を第2の動作とする。

5C shows the operation of the offset circuit in FIG. 5A when the signal of the

まず、図5(a)のオフセット回路の第1の動作について、図5(b)を参照して説明する。なお、節点N51の初期値の電位をVDDとする。 First, the first operation of the offset circuit of FIG. 5A will be described with reference to FIG. Note that the initial potential of the node N51 is VDD.

初期状態として、容量素子301には、配線105の電位VH(H信号)と、節点N51の電位VDDとの電位差VDD−VHが保持されている。そして、配線105の電位がVHからVLに変化すると、節点N51の電位は容量素子301の容量結合によってVDD−(VH−VL)となる。したがって、トランジスタ501がオンする。

As an initial state, the

また、トランジスタ501がオンするとによって、節点N52には電源電位VDDが供給され、節点N52の電位がVDDになる。したがって、容量素子302は、配線106の電位VH(H信号)と、節点N52の電位VDDとの電位差VDD−VHを保持する。また、トランジスタ502がオフする。

When the

また、トランジスタ502がオフすることによって、節点N51はフローティング状態になり、節点N51は電位VDD−(VH−VL)を維持する。

Further, when the

次に、図5(a)のオフセット回路の第2の動作について、図5(c)を参照して説明する。 Next, the second operation of the offset circuit of FIG. 5A will be described with reference to FIG.

すでに述べたように、容量素子302には、第1の動作によって、VDD−VHが保持されている。そして、配線106の電位がVHからVLに変化すると、節点N52の電位は容量素子302の容量結合によって、VDD−(VH−VL)となる。したがって、トランジスタ502がオンする。

As already described, VDD-VH is held in the

また、トランジスタ502がオンすることによって、節点N51には電源電位VDDが供給され、節点N51の電位がVDDになる。したがって、容量素子301は、配線105の電位VH(H信号)と、節点N51の電位VDDとの電位差VDD−VHを保持する。また、トランジスタ501がオフする。

When the

また、トランジスタ501がオフすることで、節点N52がフローティング状態になり、節点N52は電位をVDD−(VH−VL)に維持する。

Further, when the

以上説明した第1の動作、及び第2の動作によって、図5(a)のオフセット回路は、第1の動作において、節点N51をフローティング状態にし、節点N51の電位をVDD−(VH−VL)に維持し、節点N52には電源電位VDDを供給するように動作する。また、図5(a)のオフセット回路は、第2の動作において、節点N51には電源電位VDDを供給し、節点N52をフローティング状態にし、節点N52の電位をVDD−(VH−VL)に維持するように動作する。 By the first operation and the second operation described above, the offset circuit in FIG. 5A causes the node N51 to be in a floating state and the potential of the node N51 to be VDD− (VH−VL) in the first operation. And the node N52 operates to supply the power supply potential VDD. In the second operation, the offset circuit in FIG. 5A supplies the power supply potential VDD to the node N51, sets the node N52 in a floating state, and maintains the potential of the node N52 at VDD− (VH−VL). To work.

したがって、図5(a)のオフセット回路が生成する信号は、H信号がVDDであり、L信号がVDD−(VH−VL)である。つまり、図5(a)の回路101は、電源電位VDDを基準とした信号を生成することができる。 Therefore, in the signal generated by the offset circuit of FIG. 5A, the H signal is VDD and the L signal is VDD− (VH−VL). That is, the circuit 101 in FIG. 5A can generate a signal based on the power supply potential VDD.

なお、図3(a)のオフセット回路と同様に、図5(a)のオフセット回路が生成する信号は、L信号の電位をVDD−(VH−VL)としたが、実際には、VDD−(VH−VL)よりも少し高くなっている。 As in the offset circuit of FIG. 3A, the signal generated by the offset circuit of FIG. 5A has the L signal potential VDD− (VH−VL). It is slightly higher than (VH-VL).

なお、図3(a)のオフセット回路と同様に、節点N51を図1(a)に示す配線107に接続すれば、配線105に供給されている信号とHレベルLレベルが同じ信号を配線107に供給することができる。同様に、節点N52を図1(a)に示す配線107に接続すれば、配線105に供給されている信号とH信号、L信号が反転した信号を配線107に供給することができる。

3A, if the node N51 is connected to the

また、図3(a)のオフセット回路と同様に、節点N51を配線107に接続する場合には、容量素子302の容量値は、容量素子301の容量値よりも小さいことが好ましい。

3A, in the case where the node N51 is connected to the

また、図3(a)のオフセット回路と同様に、節点N52を配線107に接続する場合には、容量素子301の容量値は容量素子302の容量値よりも小さくすることが好ましい。

3A, when the node N52 is connected to the

なお、図4のオフセット回路と同様に、容量素子301、及び容量素子302はMOS構造の容量素子としてもよい。図6(a)に示すように、容量素子301の代わりにPチャネル型のトランジスタ601を用い、容量素子302の代わりにPチャネル型のトランジスタ602を用いてもよい。また、トランジスタ601のゲートが配線105に接続され、第1端子、及び第2端子が節点N51に接続されていることを特徴とする。同様に、トランジスタ602のゲートが配線106に接続され、第1端子、及び第2端子が節点N52に接続されていることを特徴とする。

Note that as in the offset circuit in FIG. 4, the

また、図4のオフセット回路と同様に、図6(b)のように、容量素子301、及び容量素子302として、Nチャネル型のトランジスタ603、及びNチャネル型のトランジスタ604を、それぞれ用いることもできる。また、トランジスタ603のゲートが節点N51に接続され、第1端子、及び第2端子が配線105に接続されていることを特徴とする。同様に、トランジスタ604のゲートが節点N52に接続され、第1端子、及び第2端子が配線106に接続されていることを特徴とする。

Similarly to the offset circuit in FIG. 4, an N-

なお、図4と同様に、図6(a)において、節点N51を配線107に接続する場合には、トランジスタ601のチャネル領域よりも、トランジスタ602のチャネル領域のほうが小さいことが好ましい。また、節点N52を配線107に接続する場合には、トランジスタ601のチャネル領域よりも、トランジスタ602のチャンネル領域のほうが大きいことが好ましい。

4A, in the case where the node N51 is connected to the

また、同様に、図6(b)において、節点N51を配線107に接続する場合には、トランジスタ603のチャネル領域よりも、トランジスタ604のチャネル領域のほうが小さいことが好ましい。また、節点N52を配線107に接続する場合には、トランジスタ603のチャネル領域よりも、トランジスタ604のチャンネル領域のほうが大きいことが好ましい。

Similarly, in FIG. 6B, in the case where the node N51 is connected to the

なお、本実施形態は、本明細書中の他の実施形態のいかなる記載とも自由に組み合わせて実施することができる。また、本実施形態中のいかなる記載も自由に組み合わせて実施することができる。 Note that this embodiment mode can be freely combined with any description in other embodiment modes in this specification. In addition, any description in the present embodiment can be implemented in any combination.

(第3の実施形態)

本実施形態では、第1の実施形態に示したレベルシフタが有する回路101(オフセット回路)の構成例について説明する。なお、本実施形態では、配線105、及び配線106に供給される信号を、同じタイミング(若しくは反転)、及びおおむね等しい振幅電圧のまま、電位をL側にシフトさせて、配線108に供給する場合の構成例について説明する。

(Third embodiment)

In this embodiment, a configuration example of the circuit 101 (offset circuit) included in the level shifter shown in the first embodiment will be described. Note that in this embodiment, the signal supplied to the