JP4271268B2 - イメージセンサおよびイメージセンサ一体型アクティブマトリクス型表示装置 - Google Patents

イメージセンサおよびイメージセンサ一体型アクティブマトリクス型表示装置 Download PDFInfo

- Publication number

- JP4271268B2 JP4271268B2 JP27345897A JP27345897A JP4271268B2 JP 4271268 B2 JP4271268 B2 JP 4271268B2 JP 27345897 A JP27345897 A JP 27345897A JP 27345897 A JP27345897 A JP 27345897A JP 4271268 B2 JP4271268 B2 JP 4271268B2

- Authority

- JP

- Japan

- Prior art keywords

- light receiving

- image sensor

- electrically connected

- extraction

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000011159 matrix material Substances 0.000 title claims description 111

- 239000010408 film Substances 0.000 claims description 153

- 238000000605 extraction Methods 0.000 claims description 69

- 239000000758 substrate Substances 0.000 claims description 34

- 238000006243 chemical reaction Methods 0.000 claims description 22

- 239000010409 thin film Substances 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 88

- 239000004973 liquid crystal related substance Substances 0.000 description 29

- 238000000034 method Methods 0.000 description 28

- 238000004519 manufacturing process Methods 0.000 description 22

- 230000002093 peripheral effect Effects 0.000 description 21

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 20

- 229910052710 silicon Inorganic materials 0.000 description 20

- 239000010703 silicon Substances 0.000 description 20

- 229910021417 amorphous silicon Inorganic materials 0.000 description 18

- 230000008569 process Effects 0.000 description 18

- 238000000059 patterning Methods 0.000 description 17

- 239000010936 titanium Substances 0.000 description 15

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 14

- 229910052719 titanium Inorganic materials 0.000 description 14

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 12

- 230000015572 biosynthetic process Effects 0.000 description 11

- 239000011229 interlayer Substances 0.000 description 11

- 238000005530 etching Methods 0.000 description 10

- 239000012535 impurity Substances 0.000 description 9

- 239000011347 resin Substances 0.000 description 7

- 229920005989 resin Polymers 0.000 description 7

- 229920001721 polyimide Polymers 0.000 description 6

- 239000004065 semiconductor Substances 0.000 description 6

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- 239000011574 phosphorus Substances 0.000 description 5

- 229910052698 phosphorus Inorganic materials 0.000 description 5

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- 239000004642 Polyimide Substances 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 238000006073 displacement reaction Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 238000003384 imaging method Methods 0.000 description 3

- 230000010365 information processing Effects 0.000 description 3

- 230000003287 optical effect Effects 0.000 description 3

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 3

- 229920005591 polysilicon Polymers 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 239000004952 Polyamide Substances 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 150000001408 amides Chemical class 0.000 description 2

- 239000000460 chlorine Substances 0.000 description 2

- 238000002425 crystallisation Methods 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 2

- 229920002647 polyamide Polymers 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- 125000002066 L-histidyl group Chemical group [H]N1C([H])=NC(C([H])([H])[C@](C(=O)[*])([H])N([H])[H])=C1[H] 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000005224 laser annealing Methods 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- SBIBMFFZSBJNJF-UHFFFAOYSA-N selenium;zinc Chemical compound [Se]=[Zn] SBIBMFFZSBJNJF-UHFFFAOYSA-N 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14634—Assemblies, i.e. Hybrid structures

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/13306—Circuit arrangements or driving methods for the control of single liquid crystal cells

- G02F1/13312—Circuits comprising photodetectors for purposes other than feedback

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136286—Wiring, e.g. gate line, drain line

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

Description

【発明の属する技術分野】

本発明は、光を電荷に変換する受光部と、受光画素を走査して、受光部で発生した電荷を信号として読み出す走査回路を有するイメージセンサに関するものであり、特に走査回路上に受光部を積層した積層型のイメージセンサに関するものである。

【0002】

更に、他の発明は積層型のイメージセンサと表示マトリクスとを一体化したアクティブマトリクス型表示装置に関するものである。

【0003】

【従来の技術】

光センサは、光を電気信号に変換するセンサとして広く用いられている。例えば、ファクシミリ、複写機、ビデオカメラ、デジタルスチルカメラ等のイメージセンサとして広く使用されている。

【0004】

マルチメディアの要求に対応するため、イメージセンサの画素の高密度化が急激に進んでいる。例えば、デジタルスチルカメラの画素の規格はVGA(640×480=31万画素)から、SVGA、XGAへと高密度化され、更にSXGA(1280×1024=131万画素)へと高密度化が進んでいる。

【0005】

また、デジタルスチルカメラ等のマルチメディアツールの小型化、低コスト化の要求から、光学系は2/3inchから1/2inch、1/3inch、1/4inchへと年々小型化されている。

【0006】

このように、画素の高密度化、光学系の小型化を実現するうえで、小さな受光セルであって、変換効率の良いイメージセンサが要求される。この要求を満足するため、例えば開口率を向上するため、受光部で発生した電荷を信号として読み出す走査回路と、受光部(フォトダイオード部)とを積層した積層型イメージセンサが提案されている。

【0007】

近年、ポリシリコンTFTと呼ばれる多結晶シリコンを用いたTFTする技術が鋭意研究されている。その成果として、ポリシリコンTFTによって、シフトレジスタ回路等の駆動回路を作製することが可能になり、表示マトリクスと、表示マトリクスを駆動する周辺駆動回路とを同一基板上に集積したアクティブマトリクス型の液晶パネル実用化に至っている。そのため、液晶パネルが低コスト化、小型化、軽量化されたため、パーソナルコンピュータ、携帯電話、ビデオカメラやデジタルカメラ等の各種情報機器、携帯機器の表示部に用いられている。

【0008】

現在、ノート型パソコンよりも携帯性に優れ、安価なポケットサイズの小型携帯用情報処理端末装置が実用化されており、その表示部にはアクティブマトリクス型液晶パネルが用いられている。このような情報処理端末装置は表示部からタッチペン方式でデータを入力可能となっているが、紙面上の文字・図画情報や、映像情報を入力するには、スキャナーやデジタルカメラ等の周辺機器が必要である。そのため、情報処理端末装置の携帯性が損なわれてしまっている。また、使用者に周辺機器を購入するための経済的な負担をかけている。

【0009】

また、アクティブマトリクス型表示装置は、TV会議システム、TV電話、インターネット用端末等の表示部にも用いられている。これらシステムや、端末では、対話者や使用者の映像を撮影するカメラを備えているが、表示部とカメラ部は個別に製造されてモジュール化されている。

【0010】

【発明が解決しようとする課題】

本発明では、積層型のイメージセンサにおいて、さらなる開口率の向上を図ることを課題とし、特に、受光部の光入射側の上部電極を定電位に固定するための取出し端子の構造に関する。

【0011】

本発明の目的は、上述した問題点を解消し、表示マトリクス、周辺回路が形成される基板上に、イメージセンサを設けることにより、撮像機能と表示機能とを兼ね備えたインテリジェント化されたアクティブマトリクス型表示装置をすることにある。

【0012】

【課題を解決するための手段】

上述の課題を解決するために本発明は、複数の受光画素が配置された受光画素領域に、光を電荷に変換する受光部と、前記受光部で発生した電荷を信号として読み出す信号読出し部とが積層されたイメージセンサであって、

前記受光部は、前記受光画素ごとに分離された複数の下部電極と、光電変換層と、前記受光画素に共通な上部電極とを有し、

前記イメージセンサは、前記上部電極と異なる層に形成された取出し端子を有し、

前記受光画素領域外部において、前記上部電極は前記取出し端子と光入射側で接続されていることを特徴とする。

【0013】

更に、本発明は、複数の選択線と複数の信号線が格子状に配置され、複数の画素電極を有する表示マトリクスと、複数の受光画素が配置された受光画素領域に、光を電荷に変換する受光部と、前記受光部で発生した電荷を信号として読み出す信号読出し部とが積層されたイメージセンサとを同一基板上に有するアクティブマトリクス型表示装置であって、

前記受光部は、前記受光画素ごとに分離された複数の下部電極と、光電変換層と、前記受光画素に共通な上部電極とを有し、前記上部電極は、光入射側で取出し端子に接続され、前記取出し端子は前記上部電極と異なる層に形成されていることを特徴とする。

【0014】

更に、上記イメージセンサ一体型アクティブマトリクス型表示装置において、前記信号線及び前記選択線を少なくとも覆う電極層を形成し、かつ受光部の下部電極を前記電極層と同じ出発膜で形成されすることを特徴とする。

【0015】

更に、イメージセンサ一体型アクティブマトリクス型表示装置において、

前記画素マトリクスは、前記基板上に形成され、前記信号線及び前記選択線に接続された能動素子と、前記能動素子を覆う第1の絶縁膜と、前記第1の絶縁膜上に形成され、前記信号線及び前記選択線とを少なくとも覆う電極層と、前記電極層上に形成された第2の絶縁膜と、前記第2の絶縁膜上に形成され、前記能動素子に接続された画素電極とを有し、

前記イメージセンサは、前記基板上に形成された前記信号読出し部と、前記信号読出し部を覆う前記第1の絶縁膜と、前記第1の絶縁膜上に形成され前記電極層と同じ出発膜でなり、前記受光画素ごとに分離された複数の下部電極と、前記下部電極上に形成された光電変換層と、前記光電変換層上に形成され、前記受光画素に共通な上部電極と、前記上部電極を覆う前記第2の絶縁膜と、前記第2の絶縁膜上に形成され、前記上部電極に接続された取出し端子とを有し、

前記上部電極は、前記画素電極と同じ出発膜で形成されていることを特徴とする。

【0016】

【発明の実施形態】

図1を用いて、本実施形態の周辺回路一体型のアクティブマトリクス型表示装置において、素子基板にイメージセンサを一体的に設けた表示装置を説明する。

【0017】

基板500上には、受光マトリクス111と表示マトリクス121が形成されている。表示マトリクス121には、信号線307及び選択線302が格子状に配列され、この格子内に、信号線307及び選択線302接続されたTFTでなる能動素子が表示画素ごとに配置されている。

【0018】

表示マトリクス121には、TFTを覆う第2の絶縁膜540と、第2の絶縁膜540上に形成され、選択線302及び信号線307とを少なくとも覆う電極層308が配置されている。図1において、電極層308は分断されているように図示されているが、格子状に一体的に配置されている。

【0019】

電極層308上には第3の絶縁膜550が形成され、第3の絶縁膜550上には画素電極312が形成されている。画素電極312は第1、第2の絶縁膜540、550に設けられたコンタクトホールを介して表示マトリクスのTFTに接続されている。

【0020】

電極層308は、表示マトリクス121に配置されている能動素子に光が入射するのを防止すると共に、有効表示領域からの光が表示に寄与して、表示特性が劣化するのを防いでいる。また電極層308の電位を固定することにより、選択線302、信号線306の電位の変動が、画素電極312の電位にフィードバックされることが防止できる。

【0021】

他方、受光マトリクス111には、信号読取り部として、TFTをスイッチング素子として用い受光画素を走査するための走査回路が配置されている。信号読取り部は、表示部の能動素子と同様、第1の絶縁膜540に覆われている。第1の絶縁層540上には、受光部が形成されている。第2の絶縁ゲイト型半導体素子により、受光部で発生した電荷、もしくは受光部の電位の変化が信号として読み出される。

【0022】

受光部は、受光画素ごとに分離された複数の下部電極208と、下部電極208上に形成された光電変換層210と、光電変換層210上に形成され、受光画素に共通な上部電極212とで構成されている。下部電極212は電極層308と同じ出発膜で形成されている。受光部は第2の絶縁膜550によってパッシベーションされている。

【0023】

光電変換膜210は真性もしくは実質的に真性な非晶質シリコンや非晶質シリコンゲルマニューム等のシリコン系半導体を用いることができる。pin接合を有するシリコン系半導体膜を用いることもできる。また受光部をフォトコンダクタとする場合には、一般に固体撮像管に用いられてるZnSe/ZnCdTe膜や、Se/Te/As等の積層膜を用いることができる。

【0024】

なお、図1において、膜209、膜211は非晶質シリコンでなる光電変換層210を下部電極208、上部電極212にオーミック接合させるためのn型、p型非晶質シリコン膜である。なお、n型非晶質シリコン膜209の代わりに、非晶質シリコン膜210のバリア膜として機能する膜を設けても良い。この場合、リン等のn型不純物が添加された酸化珪素膜、窒化珪素膜、炭化珪素膜等を用いることができる。

【0025】

上部電極212の電位を固定するために、前記受光マトリクス111外部において、受光部の上部電極212は、第2の絶縁膜550に設けられたコンタクトホールを介して、画素電極312と同じ出発膜でなる取出し配線606に接続されている。

【0026】

更に、取出し配線606は、電極層308と同じ出発膜でなる取出し端子603に接続され、さらに取出し端子603は信号線307と同じ出発膜でなる取出し端子601に接続されている。取出し端子601は基板外部の配線との接続部となる外部端子に、直接もしくは他の配線を介して接続されている。取出し端子601を一定電位に固定することにより、上部電極212の電位が一定に固定できる。

【0027】

積層型イメージセンサにおいて、開口部が全て上部電極212に覆われ、その電位が一定に固定されるため、光入射側から侵入する雑音を上部電極212にてシールドすることができる。さらに、本実施形態では、受光部の側面は、端子601、603、606で囲まれ、これら端子の電位は一定に固定されるため、受光部側面からの雑音が侵入することも抑制できる。よって、S/N比が向上でき、高性能、高信頼性のイメージセンサを提供できる

【0028】

本実施形態では、表示マトリクス121と受光マトリクス111を同一基板上に形成するために、成膜プロセス及びパターニングプロセスを各マトリクス111、121とで共通化することを特徴とする。絶縁膜540、550を各マトリクス111、121で共有する。

【0029】

更に電極層308と下部電極208、画素電極312と取出し端子606とを同一の成膜プロセス及びパターニングプロセスで形成する。これにより、追加工程を最小限にして、イメージセンサ一体型のアクティブマトリクス型表示装置を提供することが可能であり、製造コストを安価におさえることができる。

【0030】

また本実施形態では、受光部の上部電極212の電位を固定するために、上部電極212を外部端子に接続するための取出し端子606を、上部電極212と一体的に形成せずい点に特徴を有する。この取出し端子606を上部電極212と異なる層に形成し、かつ上部電極212の光入射側で接続することにある。

【0031】

この取出し端子606を上部電極212と一体的に形成した場合には、上部電極212と光電変換層210とのパターンが異り、上部電極212のパターニング工程は光電変換層210と異なることとなる。このため、上部電極212のパターニングのマスクずれにより、開口率が低下するおそれがある。

【0032】

他方、上部電極212と取出し端子とをそれぞれ異なる層に配置された導電膜で構成することにより、1つのレジストマスクを用いて、上部電極212と光電変換層210とのパターニングを連続して行うことが可能になり、マスクずれによる開口率の低下を防止するという効果を得る。更に光電変換層210をパターニングする際に、光電変換層210上には上部電極212が存在するため、光電変換層210のパターニングプロセス時のダメージを抑制することができる。

【0033】

本実施形態では、上部電極212と取出し端子606とをそれぞれ異なる層に配置された導電膜で構成する。上部電極212と光電変換層210とを同じプロセスでパターニングするには、この導電膜は上部電極212よりも上部に形成することも重要であり、取出し端子606を上部電極212の光入射側で接続させる。またこの取出し端子606を画素電極312と同じプロセスによって形成することにより、アクティブ型表示装置の製造プロセスとの整合性をとる。

【0034】

【実施例】

図1〜図16を用いて、本発明の実施例を詳細に説明する。

【0035】

[実施例1] 本実施例は、イメージセンサと表示マトリクスとを同一基板上に備えた透過型液晶表示装置に関するものである。

【0036】

図2は、本実施例の液晶表示装置の正面図である。図2に示すように基板100上には、受光領域110と表示領域120とが共に設けられている。受光領域110には、複数の受光画素がマトリクス状に配置された受光マトリクス111と、受光マトリクス111に接続された周辺回路112と、周辺回路が接続されていない受光マトリクス111の周囲を囲むように、取出し端子が配置される端子部113とが形成されている。受光マトリクス111は、受光部(フォトダイオード)と、受光部で発生した電荷を信号として読み出すための半導体素子が積層した構造を有する。

【0037】

他方、表示領域120は、画素電極と画素電極に接続された能動素子とが配置された表示マトリクス121と、表示マトリクス121配置された能動素子を駆動するための周辺駆動回路122とが設けられている。更に、基板100上には、基板外部の電源線等の配線との接続部となる外部取出し端子部130が設けられている。

【0038】

本実施例では、受光マトリクス111の絶縁ゲイト型半導体素子、表示マトリクス121の能動素子、及び周辺駆動回路112、122に配置される半導体素子を、CMOS技術を用いてTFT(薄膜トランジスタ)にて同時に作製する。以下に本実施例の液晶パネルの作製方法を説明する。

【0039】

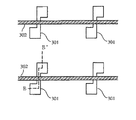

図3、図4には、受光マトリクス111、取出し端子部113及び表示マトリクス121の断面図を示す。また、図5〜図8には受光領域121の作製過程を示す正面図を示し、図9〜図12には表示マトリクス121の作製過程を示す正面図を示し、図13、図14には周辺回路112、122に配置されるCMOS−TFTの作製過程を示す正面図を示す。

【0040】

まず図3(A)に示すように、ガラス基板500全面に、基板からの不純物の拡散を防止するための下地膜510を形成する。下地膜510として、プラズマCVD法によって、酸化珪素膜を200nmの厚さに形成する。

【0041】

図3(A)の受光マトリクス111、表示マトリクス121及びCMOS−TFTの正面図が図5、図9、図13に相当する。図5、図9において線A−A’、線B−B’に沿った断面図が図3(A)に対応する。

【0042】

本実施例では透過型液晶パネルを作製するため、基板500は可視光を透過する基板であれば良く、ガラス基板500の代わりに石英基板等も用いることができる。なお、本実施例では、TFTを多結晶シリコン膜で形成するため、基板500は多結晶シリコン膜の形成プロセスに耐え得るものを選択する。多結晶シリコン膜は移動度が10〜200cm2 /Vsec程度と非常に大きく、多結晶シリコンでTFTのチャネル形成領域を構成することにより、高速応答させることができ、特に、受光マトリクス110のTFTや、周辺駆動回路112、122のCMOS−TFTに有効である。

【0043】

次に、プラズマCVD法によって非晶質シリコン膜を55nmの厚さに成膜し、エキシマレーザ光を照射して、多結晶化する。非晶質珪素膜の結晶化方法として、SPCと呼ばれる熱結晶化法、赤外線を照射するRTA法、熱結晶化とレーザアニールとを併用する方法等を用いることができる。

【0044】

次に、多結晶化されたシリコン膜を島状にパターニングして、TFTの活性層201、301、401、402を形成する。次に、これら活性層201、301、401、402を覆うゲイト絶縁膜520を形成する。ゲイト絶縁膜520はシラン(SiH4)とN2Oを原料ガスに用いて、プラズマCVD法で120nmの厚さに形成する。

【0045】

次に、Al、Cr、Mo等の金属や導電性ポリシリコン膜等の導電膜を成膜しパターニングして、選択線202、302、ゲイト電極403を形成する。これら配線・電極202、302、403をマスクにして、公知のCMOS技術を用いて活性層201、301、401、402に導電性を付与する不純物をドーピングしてソース及びドレイン領域を形成する。

【0046】

活性層201にリンをドープすることにより、 N 型のソース領域203、ドレイン領域204、チャネル形成領域205が自己整合的に形成され、活性層301にリンをドープすることにより、 N 型のソース領域303、ドレイン領域304、チャネル形成領域305が自己整合的に形成され、活性層401にリンをドープすることにより、 N 型のソース領域、ドレイン領域、チャネル形成領域が自己整合的に形成される。活性層201、301、401をレジストマスクで覆い、活性層402のみにボロンをドープして、P型のソース領域およびドレイン領域と、チャネル形成領域を自己整合的に形成する。ドーピング後、ドーピングされた不純物を活性化する。

【0047】

なお、本実施例では活性層201、301、401が多結晶シリコンであるため、配線・電極202、302、403を形成する前に、少なくともNチャネル型TFTのチャネル形成領域となる領域にボロン等のP型の不純物を添加して、しきい値を最適化するのが好ましい。

【0048】

次に、図3(B)に示すように、基板500全面を覆う第1の層間絶縁膜530を形成する。層間絶縁膜530に各TFTのソース領域およびドレイン領域に達するコンタクトホール及びCMOS−TFTのゲイト電極403に達するコンタクトホールをそれぞれ形成する。しかる後、チタン膜、アルミニウム膜、チタン膜でなる積層膜を形成し、パターニングして、受光マトリクス111の信号線206、ソース電極207と、表示マトリクス121の信号線306、ドレイン電極307がそれぞれ形成される。

【0049】

この状態の受光マトリクス111、表示マトリクス121の正面図が図6、図10に相当する。図6、図10において線A−A’、線B−B’に沿った断面図が図3(A)に対応する。

【0050】

更にCMOS−TFTには、図14に示すようにゲイト電極403に接続される入力配線411、nチャネル型TFTのソース領域に接続される配線412、pチャネル型TFTのドレイン領域に接続される配線413、nチャネル型TFTのドレイン領域406とpチャネル型TFTのソース領域408とを接続する配線414を形成する。

【0051】

図6に示すように、受光マトリクス111において、選択線202は周辺回路122Hに接続され、周辺回路122Hから、受光部で発生した信号電荷を読み取る受光画素を指定する選択信号が入力される。また信号線206は周辺回路112Vに接続され、読み出された信号電荷は、信号線206を経て周辺回路112Vに出力され、周辺回路112Vから映像信号として外部に出力される。

【0052】

さらに、取出し端子部113には、取出し端子601が形成される。図6に示すように、取出し端子601は、受光マトリクス111の周囲であって周辺駆動回路112が接続されていない周囲に沿って『L』字型に形成されている。更に取出し端子601は受光領域110外部に延在する部分を有し、この部分で外部取出し端子部130に形成された端子に接続されている。

【0053】

更に、表示領域120内において、表示マトリクス121外部に後に形成される電極層308の電位を固定するための端子602も形成される。

【0054】

以上のCMOSプロセスを経て、多結晶シリコンTFTを用いた受光マトリクス111、表示マトリクス121及び駆動回路112、122に配置されるCMOS−TFTが同時に完成する。ここでは、これらTFTをトップゲイトのプラナ型としたが、逆スタガ等のボトムゲイト型としてもよい。この場合、活性層201、301、401、402と選択線202、302、ゲイト電極403の形成順序を逆にし、選択線202、302、ゲイト電極403を形成した後、ゲイト絶縁膜520を形成すればよい。また、LDD領域やオフセット領域を設けてもよい。

【0055】

次に、図3(C)に示すように、受光部TFT200と受光部とを絶縁分離するための第2の層間絶縁膜540を基板500全面に形成する。第2の層間絶縁膜540には下層の凹凸を相殺して、平坦な表面が得られる樹脂膜が好適である。このような樹脂膜として、ポリイミド、ポリアミド、ポリイミドアミド、アクリルを用いることができる。また、第2の層間絶縁膜540の表面層は平坦な表面を得るため樹脂膜とし、下層は酸化珪素、窒化珪素、酸化窒化珪素等の無機絶縁材料の単層、多層としても良い。本実施例では、第2の層間絶縁膜540としてポリイミド膜を1.5μmの厚さに形成する。

【0056】

次に、第2の層間絶縁膜540に、ソース電極207、ドレイン電極307、端子601、602に達するコンタクトホールをそれぞれ形成した後、受光部の下部電極、及び表示マトリクスの電極層を構成するTi、Cr、Mo、Al等の導電膜11を形成する。本実施例では導電膜として厚さ200nmのチタン膜11をスッパタ法で成膜する。

【0057】

次に、受光部の光電変換層と下部電極とをオーミック接合させるためのn型の非晶質シリコン膜12を30〜50nmの厚さに、ここでは30nmの厚さに基板全面に成膜する。チタン膜11及びシリコン膜12をパターニングするためのレジストマスク13を形成する。

【0058】

レジストマスク13を用いて、図4(A)に示すようにシリコン膜12、チタン膜11を順次パターニングする。ここでは、ドライエッチング法を用いる。シリコン膜12のエッチングガスにはCF4を1〜10%混合したO2ガスを用いる。本実施例ではCF4の濃度を5%とする。またチタン膜11のエッチングガスにはCl2 /BCl3/SiCl4を混合した塩素系ガスを用いる。なお、チタン膜11は樹脂でなる絶縁膜540上に形成されるため、チタン膜11のエッチングガス、エッチャントは樹脂を変質しないものを選択する必要がある。

【0059】

チタン膜11をパターニングすることにより、図4(A)に示すように、受光マトリクス111には、受光部の下部電極208、表示マトリクス121の電極層308、画素電極との接続用電極309、および端子部113の端子603が形成される。これらチタンでなる電極208、308、309、603上には、チタン膜11と概略同一形状にパターニングされたシリコン膜11でなるn層209、310、311、604が形成される。

【0060】

受光マトリクス以外のn層310、311、604は実質的な機能を有しないため、形成しなくともよい。この場合はチタン膜11とシリコン膜12のパターニングを別々に行えばよい。しかし、チタン膜11とシリコン膜12のパターニングを同時に行うことで、工程が簡略化できる。

【0061】

なお、受光部のn層209として非晶質シリコンの代わりに微結晶シリコンを用いることもできる。また、リン等のn型不純物が添加された窒化珪素、酸化珪素、炭化珪素を用いることができる。

【0062】

この状態の受光領域110および表示マトリクス120の上面図を図7(A)、図11にそれぞれ示す。なお、図7、図11において、n層209、310、311、604は省略されている。

【0063】

図7(A)に示すように、下部電極208は選択線202、信号線206で形成された格子内に、受光画素ごとに分離されて形成されている。また端子部113には、取出し端子601と接続される端子603が形成されている。端子603は端子601と同様に、周辺駆動回路112と接続されていない受光マトリクス111の周囲に沿って、『L』字型に形成されている。図7(A)の線A−A’による断面図が図4(A)に図示されている。

【0064】

図7(B)に示すように、端子601と端子603とは絶縁膜540に形成された複数のコンタクトホールを介して上下間で接続されている。コンタクトが小さいほどアンテナ効果が緩和されるため、端子601と603は複数のコンタクトホール605により接続する。なお。図7(A)の線D−D’による断面図が図7(B)に相当する。コンタクトホール605のピッチは例えば受光画素のピッチと同程度であれば、上部電極を等電位にするのに問題がない。

【0065】

他方、表示マトリクス121には、図11に示すように電極層308が、選択線302、信号線306および、電極307とのコンタクト部を除いた活性層301を覆うように格子状に一体的に形成されている。電極層308は受光部に光が入射するのを防ぐと共に、有効表示領域以外から光が漏れることを防止している。さらに、電極層308は表示マトリクス121外部において、取出し配線602に接続されている。取出し配線602はその電位が一定電位に固定されるため、電極層308の電位も一定電位に固定される。これにより、電極層308の下層の選択線302、信号線306の電位の変動によって、電極層308の上層の画素電極の電位が変動することを抑制できる。

【0066】

次に、チタン膜11、シリコン膜のパターニング終了後、図4(A)に示すように、真性もしくは実質的に真性な非晶質シリコン膜14を1〜2μm、ここでは1.5μmの膜厚に形成し、連続してボロンを含んだp型の非晶質シリコン膜15を30〜100nmの厚さに、ここでは50nmの厚さに成膜する。さらに、受光部の上部電極を構成する透明導電膜、ここではITO膜16を120nmの厚さに成膜する。そして、これら膜14〜16をパターニングするためのレジストマスク17を形成する。

【0067】

なお、非晶質シリコン膜14が実質的に真性な状態とは、ボロン等のp型不純物を5×1016〜1×1019cm-3程度添加し、そのフェルミ準位がバンドギャプの中央に位置した状態をいう。これは非晶質シリコンは成膜時にはフェルミ準位がバンドギャプの中央に必ずしも位置している訳ではなく、若干n型になる方向にフェルミ準位がずれている。そのため、上記のようにp型不純物を添加することで、フェルミ準位をバンドギャプの中央にすることができる。この場合に不純物が添加されているが、フェルミ準位をバンドギャプの中央にある状態を実質的に真性な状態であるとしている。

【0068】

なお、真性または実質的に真正な非晶質シリコン膜14の代わりに非晶質シリコンゲルマニュームを用いることができる。また、p型非晶質シリコン膜15の代わりに微結晶シリコンを用いることもできる。

【0069】

次に、レジストマスク17を用いて、ITO膜16、シリコン膜15、14を順次パターニングして、図4(B)に示すように、上部電極212、p層211、i層210をそれぞれ形成する。ITO膜16、シリコン膜15、14をパターニングするには、CF4/SF6/O2を混合したエッチングガスを用いたR

IEエッチングを用いる。なお、ITO膜16をパターニングした後は、シリコン膜のみをエッチングするガスを用いることにより、上部電極212をマスクにしてシリコン膜15、14をエッチング可能であるため、レジストマスク17は不要になる。しかしシリコン膜15、14のエッチング時に、レジストマスク17を残存させることで、RIEエッチングによって上部電極212が変質することを防止できる。

【0070】

本実施例では、シリコン膜15、14とITO膜16とのパターニング工程を連続して行う、即ち、ITO膜成膜前にシリコン膜15、14の成膜の間にパターニング工程を行わないことで、上部電極212と光電変換層210とのパターンずれによる開口率低下を回避することができる。

【0071】

また上部電極212とp層211、i層210を、受光マトリクス111内のみでなく、端子部113側に突出させて形成する。これは、後に、開口率を低下することなく、上部電極212を電極604に接続させるためであり、製造マージンや受光部の信頼性を考慮して、端子部113側に突出させる幅は、受光画素のピッチの2〜10倍程度とすればよい。

【0072】

また、受光部の信頼性の点から、i層210において、受光マトリクス111の境界部を絶縁化して、受光マトリクス111外部のi層210で発生したフォトキャリアが受光マトリクス111内に漏れ込むことを防止すると良い。絶縁化の方法の1つとして、受光マトリクス111の境界部に沿ってi層210に溝部を形成し、この溝部に絶縁物を埋め込む方法が挙げられる。この溝部はi層210を完全に分断するように形成しても良い。なお、上記のように境界部を絶縁化する場合は、シリコン膜14、15のパターニング工程と、ITO膜16のパターニング工程を別々に行う必要がある。

【0073】

次にレジストマスク17を除去した後、図1に示すように、表示マトリクス121の画素電極312の下地となる第3の層間絶縁膜550を基板500全面に形成する。絶縁膜550受光マトリクス111のパッシベーション膜としても機能する。第3の層間絶縁膜550を構成する絶縁被膜として、ポリイミド、ポリアミド、ポリイミドアミド、アクリル等の樹脂膜を形成して、平坦な表面を得るようにする。本実施例では、ポリイミド膜を形成し、受光マトリクス111での膜厚が、0.3〜1μm、ここでは0.5μmとなる成膜にする。

【0074】

次に層間絶縁膜550に、上部電極212、電極309および端子603に達するコンタクトホールを形成する。ここでは、エッチングガスにはCF4を1〜10%混合したO2ガスを用いたRIEエッチング法を用いる。層間絶縁膜550は樹脂でなるためO2ガスのみでエッチング可能であるが、CF4混合することにより、電極309、604上のシリコン膜でなるn層310、604もエッチングされる。

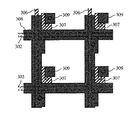

【0075】

コンタクトホールを開口後、100〜300nm厚さ、ここでは120nmのITO膜をスパッタ法にて成膜し、CF4/SF6/O2を混合したエッチングガスを用いてパターニングして、電極309に接続された画素電極312、および上部電極212を端子603に接続するための取出し端子606が形成される。この状態の受光マトリクス111、表示マトリクス121の上面図をそれぞれ、図8(A)、図12に示す。

【0076】

図8(A)に示すように、取出し端子606は端子603同様、受光マトリクス111の駆動回路121が接続されていない周囲を囲むように、『L』字型に形成されている。そして、端子606は受光マトリクス111外部において上部電極212に接続され、端子部113において端子603に接続されている。この構造により、取出し端子601を一定電位に固定することにより、上部電極212は端子606、603を介して、その電位が一定電位に固定される。例えば、端子601を一定電位に固定するには、端子601を図1に示す取出し端子部130に形成される外部取出し端子に接続する。この場合、外部取出し端子を信号線206、306と同一の導電膜で形成して、外部取出し端子と取出し端子601を一体的に形成することも可能である。

【0077】

なお、上部電極212の全体を一定電位にするためには、端子606を接続するためのコンタクトホール607は受光画素のピッチと同程度とすればよい。なお、図8(A)の線D−D’による断面図を図8(B)に示す。また図8(A)の線A−A’による断面図が図1に図示されている。

【0078】

ここで、端子601、603、606は受光マトリクス111が駆動回路121と接続されていない周囲を囲むように形成したため、図1の断面構成からも明らかなように、受光部(フォトダイオード)側面が端子601、端子603、606で囲まれている。ここでは、端子601、端子603、606は電位が一定に固定されているため、受光部に対するシールドとして機能させることができる。よって、表示マトリクス121と受光マトリクス111を同一基板に設けても、受光部の信頼性を保つことができる。

【0079】

さらに、選択線202、信号線302が周辺回路112H、112Vとの接続端の他端も端子601、603、606によって、電気的に保護できるため、受光マトリクス111に配置されるTFTの静電破壊を抑制できる。

【0080】

他方、表示マトリクス121においては、図12に示すように、画素電極312は表示画素ごとに電気的に分離され、その周縁が電極層308と重なるように形成される。この構造により、絶縁膜550を誘電体とし、電極層308、画素電極312を対向電極とする補助容量が形成できる。なお、図12において電極層308上のn層309は省略されている。

【0081】

実施例において、受光マトリクス111をTFTを作製した後、TFT上に受光部(フォトダイオード)を形成する積層型としたので、従来のように受光部を非晶質シリコン膜で形成しても、受光TFT200を多結晶シリコンで構成することができる。よって、ガラス基板等の絶縁性基板上に、変換効率が良く、高速応答可能なイメージセンサが作製できる。

【0082】

また、イメージセンサを積層構造とすることで、従来多結晶シリコンTFTで構成されている液晶パネルの作製工程と整合性が保たれる。従って、イメージセンサと液晶パネルの各特性を損なうことなく同一基板上に集積化できる。

【0083】

本実施例では、受光マトリクス111に受光画素を2次元に配列したが、受光画素を1次元に配列したラインセンサとしても良い。また、受光画素のフォーマットを表示部のフォーマットと同一にすると、受光画素と表示画素が1対1に対応するため、受光マトリクス111で検出された画像を表示マトリクス121に表示するための信号処理が簡単化、高速化できる。ラインセンサとした場合も、受光画素数は、列方向又は行方向の表示画素数と同じにすると良い。

【0084】

画素フォーマットを一致させた場合には、例えば表示マトリクス121のフォーマットを640×480(VGA規格)とし場合には、1つの受光画素ピッチを10μm程度とすると、受光マトリクス111の占有面積は6.4mm×4.8mm程度となり、液晶パネルに集積化することは可能である。

【0085】

本実施例では、受光部を抵抗型のフォトダイオードとしたため、下部電極208、上部電極とオーミック接合させるn層209、p層211を設けたが、例えばショットキー型とする場合は、n層209、p層211を省略すればよい。

【0086】

本実施例では、透過型液晶パネルとしたが、画素電極312を鏡面表面を有する反射型電極とし、直視型の液晶パネルとすることもできる。

【0087】

本実施例では、受光マトリクス111において、受光部(フォトダイオード)と接続される信号読出し回路として、スイッチング素子として機能するTFTを1つ設けたパッシブ型としたが、例えば、増幅機能を有するアクティブ型とし、複数のTFTで構成することもできる。

【0088】

[実施例2] 本実施例は、受光領域111の端子部113の変形例である。本実施例を図15を用いて説明する。

【0089】

本実施例では、信号線306と同じ出発膜でなる端子601を省略する。この場合、最下層の配線701は電極層308と同一の出発膜でなる配線となる。配線701の形状は、実施例1の端子601と同様とし、受光マトリクス111外部へ延長して、外部取出し端子部130に形成される端子と接続するようにすればよい。

[実施例3] 本実施例は、受光領域111の端子部113の変形例である。本実施例を図16を用いて説明する。

【0090】

本実施例では、端子601及び電極308を省略する。この場合、端子部113に配置される配線801は画素電極312と同一の出発膜でなる配線のみとなる。配線801の形状は、実施例1の端子601と同様とし、受光マトリクス111外部に延在して、外部取出し端子部130に形成される端子と接続するようにすればよい。

[実施例4] 本実施例は、受光領域111の端子部113の変形例である。実施例1では端子部の最下層の端子601と信号線306と同じ出発膜で形成したが、選択線302と同じ出発膜で構成することも可能である。

【0091】

[実施例5] 本実施例の受光領域111の端子部113の変形例である。実施例1において電極層308と同じ出発膜でなる端子603を省略して、端子606と端子601を直接に接続する。また、この場合、実施例4で述べたように、端子601を選択線302と同じ出発膜で構成することも可能である。

【0092】

[実施例6] 本実施例は、実施例1で説明した、イメージセンサ一体型の液晶パネルの応用製品を説明する。図17に本実施例の電子機器の模式的な外観図を示す。

【0093】

実施例1の液晶パネルは撮像機能を有する受光領域と、表示領域が一体的に設けられているため、TV会議システム、TV電話、インターネット用端末やパーソナルコンビュータ等の通信機能を備えた表示部に好適である。例えば、表示部で対話者の端末から送信された映像を見ながら、受光マトリクスで自身の姿を撮影して、対話者の端末にその映像を転送することできるので、動画像を双方向通信することが可能である。

【0094】

またこのような電子機器の1つとして、図17(A)に、液晶パネルを有するノート型パソコン2000を示す。2001が液晶パネルであり、2002がイメージセンサ部である。

【0095】

また他の電子機器として、図17(B)に、テレビ電話2010を示す。2011が液晶パネルであり、2012がイメージセンサ部である。使用者は自身の姿を姿をイメージセンサ部2012で撮影しつつ、また液晶パネルにて2011通話相手の姿を見ながら通話することができる。

【0096】

更に図17(C)にはペン入力型の携帯型情報端末機器2020を示す。2021が液晶パネルであり、2021がエリアセンサ部である。エリアセンサ2021により、名紙等の文字・図画情報を取り込んで、液晶パネル2021に表示したり、携帯型情報端末機器内にこれらの情報を保存できるようになっている。

【0097】

本発明では液晶パネルとセンサ部を同一基板に設けたため、小型、軽量でとすることができる。またセンサ部の駆動を液晶パネルと共有化することも可能であるため、省電力化が図れる。よって、図17で示したような、バッテリー駆動型の電子機器に本発明は好適である。

【0098】

【発明の効果】

本実施形態では、表示マトリクスと受光マトリクスを同一基板上に形成するために、成膜プロセス及びパターニングプロセスを各マトリクスとで共通化することで、製造コストを安価におさえることができる。

【0099】

また本実施形態では、受光部の上部電極の電位を固定するための取出し端子を上部電極と一体的に形成しないことにより、受光部の上部電極と光電変換層とのパターニングを連続して行うことが可能になり、マスクずれによる開口率の低下を防止できる。さらにこの取出し端子を表示マトリクスの画素電極と同一出発膜で形成することにより、プロセスの簡略化が図れる。

【図面の簡単な説明】

【図1】 実施例1の液晶パネルの断面図。

【図2】 実施例1の液晶パネルの正面図。

【図3】 実施例1の液晶パネルの作製工程を説明するための断面図。

【図4】 実施例1の液晶パネルの作製工程を説明するための断面図。

【図5】 実施例1の受光マトリクスの作製工程の説明するための正面図。

【図6】 実施例1の受光マトリクスの作製工程の説明するための正面図。。

【図7】 実施例1の受光マトリクスの作製工程の説明するための正面図及び断面図。

【図8】 実施例1の受光マトリクスの作製工程の説明するための正面図及び断面図。。

【図9】 実施例1の表示マトリクスの作製工程の説明するための正面図。

【図10】実施例1の表示マトリクスの作製工程の説明するための正面図。

【図11】実施例1の表示マトリクスの作製工程の説明するための正面図。

【図12】実施例1の表示マトリクスの作製工程の説明するための正面図。

【図13】実施例1の駆動回路の作製工程を説明するための正面図。

【図14】実施例1の駆動回路の作製工程を説明するための正面図

【図15】実施例2のの液晶パネルの断面図

【図16】実施例3のの液晶パネルの断面図

【図17】実施例6の液晶パネルの応用製品の模式的な外観図。

【符号の説明】

110 受光領域

111 受光マトリクス

112 周辺駆動回路

113 端子部

120 画素領域

121 表示マトリクス

122 周辺駆動回路

201 活性層

202 選択線

206 信号線

207 ソース電極

208 下部電極

209 n層

210 i層

211 p層

212 上部電極

301 活性層

302 選択線

306 信号線

307 ドレイン電極

308 電極層

309 電極

312 画素電極

601、603、606 取出し端子

Claims (22)

- 複数の受光画素が配置された矩形状の受光画素領域に、光を電荷に変換する受光部と、前記受光部に電気的に接続されたスイッチング素子とを有し、

前記受光部は、前記複数の受光画素ごとに分離された複数の下部電極と、光電変換層と、前記複数の受光画素に共通な上部電極とを有し、

前記上部電極は、前記上部電極の上層に形成された取出し配線と電気的に接続され、

前記取出し配線は、前記取出し配線の下に形成された取出し端子と電気的に接続され、

前記取出し配線は、前記受光画素領域の隣り合う2辺に沿ったL字型の領域を有し、

前記取出し端子は、前記受光画素領域の隣り合う2辺に沿ったL字型の領域を有することを特徴とするイメージセンサ。 - 複数の受光画素が配置された矩形状の受光画素領域に、光を電荷に変換する受光部と、前記受光部に電気的に接続されたスイッチング素子とを有し、

前記受光部は、前記複数の受光画素ごとに分離された複数の下部電極と、光電変換層と、前記複数の受光画素に共通な上部電極とを有し、

前記上部電極は、前記上部電極の上層に形成された取出し配線と電気的に接続され、

前記取出し配線は、前記取出し配線の下に形成された第1の取出し端子と電気的に接続され、

前記第1の取出し端子は、前記第1の取出し端子の下層に形成された第2の取出し端子と電気的に接続され、

前記取出し配線は、前記受光画素領域の隣り合う2辺に沿ったL字型の領域を有し、

前記第1の取出し端子は、前記受光画素領域の隣り合う2辺に沿ったL字型の領域を有し、

前記第2の取出し端子は、前記受光画素領域の隣り合う2辺に沿ったL字型の領域を有することを特徴とするイメージセンサ。 - 請求項1において、

前記取出し端子は前記複数の下部電極と同じ出発膜で形成されていることを特徴とするイメージセンサ。 - 請求項2において、

前記第1の取出し端子は前記複数の下部電極と同じ出発膜で形成されていることを特徴とするイメージセンサ。 - 請求項1において、

前記スイッチング素子は、信号を読み出す受光画素を選択するための信号が入力される選択線と電気的に接続され、

前記取出し端子は前記選択線と同じ出発膜で形成されていることを特徴とするイメージセンサ。 - 請求項2または請求項4において、

前記スイッチング素子は、信号を読み出す受光画素を選択するための信号が入力される選択線と電気的に接続され、

前記第2の取出し端子は前記選択線と同じ出発膜で形成されていることを特徴とするイメージセンサ。 - 請求項1において、

前記スイッチング素子は、受光画素から読み出した信号を出力するための信号線と電気的に接続され、

前記取出し端子は前記信号線と同じ出発膜で形成されていることを特徴とするイメージセンサ。 - 請求項2または請求項4において、

前記スイッチング素子は、受光画素から読み出した信号を出力するための信号線と電気的に接続され、

前記第2の取出し端子は前記信号線と同じ出発膜で形成されていることを特徴とするイメージセンサ。 - 請求項1、請求項3、請求項5、請求項7のいずれか一において、

前記取出し配線と前記取出し端子とは、複数のコンタクトホールによって電気的に接続されていることを特徴とするイメージセンサ。 - 請求項2、請求項4、請求項6、請求項8のいずれか一において、

前記取出し配線と前記第1の取出し端子とは、複数のコンタクトホールによって電気的に接続されていることを特徴とするイメージセンサ。 - 請求項2、請求項4、請求項6、請求項8、請求項10のいずれか一において、

前記第1の取出し端子と前記第2の取出し端子とは、複数のコンタクトホールによって電気的に接続されていることを特徴とするイメージセンサ。 - 請求項9乃至請求項11のいずれか一において、

前記複数のコンタクトホールの間隔は、前記複数の受光画素の画素ピッチと等しいことを特徴とするイメージセンサ。 - 請求項1乃至請求項12のいずれか一において、

前記取出し配線には一定の電位が与えられることを特徴とするイメージセンサ。 - 請求項1乃至請求項13のいずれか一において、

前記受光画素領域の隣り合う2辺とは異なる2辺において、前記スイッチング素子と電気的に接続された駆動回路を有することを特徴とするイメージセンサ。 - 請求項1乃至請求項14のいずれか一において、

前記スイッチング素子は薄膜トランジスタであることを特徴とするイメージセンサ。 - 請求項1乃至請求項15のいずれか一に記載のイメージセンサを用いることを特徴とする電子機器。

- 請求項1乃至請求項15のいずれか一に記載のイメージセンサが形成された基板と同一基板上に表示マトリクスを有し、

前記表示マトリクスは、能動素子と、前記能動素子に電気的に接続された複数の画素電極とを有することを特徴とするイメージセンサ一体型アクティブマトリクス型表示装置。 - 請求項1乃至請求項15のいずれか一に記載のイメージセンサが形成された基板と同一基板上に表示マトリクスを有し、

前記表示マトリクスは、能動素子と、前記能動素子を覆う電極層と、前記能動素子に電気的に接続された複数の画素電極とを有することを特徴とするイメージセンサ一体型アクティブマトリクス型表示装置。 - 請求項18において、

前記複数の下部電極は、前記電極層と同じ出発膜で形成されていることを特徴とするイメージセンサ一体型アクティブマトリクス型表示装置。 - 請求項18または請求項19において、

前記表示マトリクスにおいて、

前記能動素子は第1の絶縁膜に覆われ、

前記電極層は前記第1の絶縁膜上に形成され、

前記画素電極は前記電極層を覆う第2の絶縁膜上に形成され、

前記イメージセンサにおいて、

前記スイッチング素子は前記第1の絶縁膜に覆われ、

前記複数の下部電極は前記第1の絶縁膜上に形成され、

前記上部電極は前記第2の絶縁膜に覆われていることを特徴とするイメージセンサ一体型アクティブマトリクス型表示装置。 - 請求項17乃至請求項20のいずれか一において、

前記能動素子は薄膜トランジスタであることを特徴とするイメージセンサ一体型アクティブマトリクス型表示装置。 - 請求項17乃至請求項21のいずれか一に記載のイメージセンサ一体型アクティブマトリクス型表示装置を用いることを特徴とする電子機器。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP27345897A JP4271268B2 (ja) | 1997-09-20 | 1997-09-20 | イメージセンサおよびイメージセンサ一体型アクティブマトリクス型表示装置 |

| US09/156,461 US7046282B1 (en) | 1997-09-20 | 1998-09-18 | Image sensor and image sensor integrated type active matrix type display device |

| US11/418,279 US7286173B2 (en) | 1997-09-20 | 2006-05-04 | Image sensor and image sensor integrated type active matrix type display device |

| US11/838,600 US7791117B2 (en) | 1997-09-20 | 2007-08-14 | Image sensor and image sensor integrated type active matrix type display device |

| US12/875,537 US8564035B2 (en) | 1997-09-20 | 2010-09-03 | Image sensor and image sensor integrated type active matrix type display device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP27345897A JP4271268B2 (ja) | 1997-09-20 | 1997-09-20 | イメージセンサおよびイメージセンサ一体型アクティブマトリクス型表示装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008212007A Division JP5025596B2 (ja) | 2008-08-20 | 2008-08-20 | イメージセンサ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH1197690A JPH1197690A (ja) | 1999-04-09 |

| JP4271268B2 true JP4271268B2 (ja) | 2009-06-03 |

Family

ID=17528204

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP27345897A Expired - Lifetime JP4271268B2 (ja) | 1997-09-20 | 1997-09-20 | イメージセンサおよびイメージセンサ一体型アクティブマトリクス型表示装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (4) | US7046282B1 (ja) |

| JP (1) | JP4271268B2 (ja) |

Families Citing this family (92)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4044187B2 (ja) * | 1997-10-20 | 2008-02-06 | 株式会社半導体エネルギー研究所 | アクティブマトリクス型表示装置およびその作製方法 |

| US7289083B1 (en) * | 2000-11-30 | 2007-10-30 | Palm, Inc. | Multi-sided display for portable computer |

| US7348964B1 (en) * | 2001-05-22 | 2008-03-25 | Palm, Inc. | Single-piece top surface display layer and integrated front cover for an electronic device |

| US8384674B1 (en) | 2001-01-30 | 2013-02-26 | Hewlett-Packard Development Company, L.P. | Integrated enclosure/touch screen assembly |

| JP4485087B2 (ja) | 2001-03-01 | 2010-06-16 | 株式会社半導体エネルギー研究所 | 半導体装置の動作方法 |

| JP4896302B2 (ja) * | 2001-04-09 | 2012-03-14 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US6992659B2 (en) | 2001-05-22 | 2006-01-31 | Palmone, Inc. | High transparency integrated enclosure touch screen assembly for a portable hand held device |

| US7142195B2 (en) | 2001-06-04 | 2006-11-28 | Palm, Inc. | Interface for interaction with display visible from both sides |

| US7852430B1 (en) | 2001-11-29 | 2010-12-14 | Palm, Inc. | Light guide spacers for backlighting a reflective display |

| KR100869737B1 (ko) * | 2001-12-29 | 2008-11-21 | 엘지디스플레이 주식회사 | 표시소자 및 그 제조방법 |

| JP4401066B2 (ja) * | 2002-11-19 | 2010-01-20 | 三洋電機株式会社 | 半導体集積装置及びその製造方法 |

| US7253391B2 (en) * | 2003-09-19 | 2007-08-07 | Semiconductor Energy Laboratory Co., Ltd. | Optical sensor device and electronic apparatus |

| JP4827396B2 (ja) * | 2003-10-06 | 2011-11-30 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| CN100477240C (zh) * | 2003-10-06 | 2009-04-08 | 株式会社半导体能源研究所 | 半导体器件以及制造该器件的方法 |

| KR101002332B1 (ko) * | 2003-12-30 | 2010-12-17 | 엘지디스플레이 주식회사 | 액정표시소자 및 그 제조방법 |

| JP2006030889A (ja) * | 2004-07-21 | 2006-02-02 | Toshiba Matsushita Display Technology Co Ltd | 液晶表示装置 |

| JP4831456B2 (ja) * | 2004-09-16 | 2011-12-07 | カシオ計算機株式会社 | 画像読取装置 |

| JP4817636B2 (ja) | 2004-10-04 | 2011-11-16 | 株式会社半導体エネルギー研究所 | 半導体装置およびその作製方法 |

| JP4905762B2 (ja) * | 2005-08-23 | 2012-03-28 | 富士フイルム株式会社 | 光電変換素子、撮像素子、および該光電変換素子の製造方法 |

| KR100736086B1 (ko) * | 2005-09-06 | 2007-07-06 | 삼성전자주식회사 | 엔트로피 코딩의 성능 향상 방법 및 장치, 상기 방법을이용한 비디오 코딩 방법 및 장치 |

| TW200804900A (en) * | 2006-07-07 | 2008-01-16 | Innolux Display Corp | Liquid crystal display device |

| JP2008122659A (ja) * | 2006-11-13 | 2008-05-29 | Seiko Epson Corp | 液晶表示装置及び液晶表示装置の製造方法並びに電子機器 |

| US8749483B2 (en) * | 2007-02-15 | 2014-06-10 | Pixart Imaging Inc. | Control device and control method for image display |

| JP4793281B2 (ja) * | 2007-02-21 | 2011-10-12 | ソニー株式会社 | 撮像装置および表示装置 |

| EP1986238A3 (en) * | 2007-04-27 | 2010-12-29 | Semiconductor Energy Laboratory Co., Ltd. | Resin molded optical semiconductor device and corresponding fabrication method |

| US20100045642A1 (en) * | 2007-05-18 | 2010-02-25 | Masakazu Satoh | Display device |

| WO2008143211A1 (ja) * | 2007-05-18 | 2008-11-27 | Sharp Kabushiki Kaisha | 表示装置 |

| US8309901B2 (en) * | 2007-05-18 | 2012-11-13 | Sharp Kabushiki Kaisha | Display device adjusting luminance of display based at least on detections by ambient light sensors |

| JP5298461B2 (ja) * | 2007-05-29 | 2013-09-25 | セイコーエプソン株式会社 | 液晶装置及び電子機器 |

| JP2009065160A (ja) * | 2007-09-06 | 2009-03-26 | Dongbu Hitek Co Ltd | イメージセンサ及びその製造方法 |

| KR100954927B1 (ko) * | 2007-12-14 | 2010-04-27 | 주식회사 동부하이텍 | 이미지 센서 및 그 제조방법 |

| KR100856948B1 (ko) * | 2007-12-27 | 2008-09-04 | 주식회사 동부하이텍 | 이미지 센서 제조방법 |

| JP5185013B2 (ja) * | 2008-01-29 | 2013-04-17 | 富士フイルム株式会社 | 電磁波検出素子 |

| JP5461719B2 (ja) * | 2008-01-29 | 2014-04-02 | 富士フイルム株式会社 | 電磁波検出素子 |

| JP5136112B2 (ja) * | 2008-02-19 | 2013-02-06 | セイコーエプソン株式会社 | 光電変換装置及び電気光学装置 |

| US9367998B2 (en) * | 2008-02-21 | 2016-06-14 | Bally Gaming, Inc. | Gaming system having displays with integrated image capture capabilities |

| JP5185014B2 (ja) * | 2008-02-29 | 2013-04-17 | 富士フイルム株式会社 | 電磁波検出素子 |

| JP2009252835A (ja) * | 2008-04-02 | 2009-10-29 | Fujifilm Corp | 電磁波検出素子 |

| US7955890B2 (en) * | 2008-06-24 | 2011-06-07 | Applied Materials, Inc. | Methods for forming an amorphous silicon film in display devices |

| JP2010087332A (ja) * | 2008-10-01 | 2010-04-15 | Seiko Epson Corp | 光電変換素子、光電変換装置、及びイメージセンサ |

| TWI373853B (en) * | 2009-03-16 | 2012-10-01 | Au Optronics Corp | Active device array substrate and method for fabricating thereof |

| JP2010225618A (ja) * | 2009-03-19 | 2010-10-07 | Seiko Epson Corp | センシング装置および電子機器 |

| US8456586B2 (en) | 2009-06-11 | 2013-06-04 | Apple Inc. | Portable computer display structures |

| JP4811502B2 (ja) * | 2009-07-01 | 2011-11-09 | カシオ計算機株式会社 | 液晶表示パネル及びタッチパネル |

| TWI547845B (zh) * | 2009-07-02 | 2016-09-01 | 半導體能源研究所股份有限公司 | 觸控面板及其驅動方法 |

| KR101610846B1 (ko) * | 2009-09-08 | 2016-04-11 | 삼성디스플레이 주식회사 | 표시 장치 및 그 제조 방법 |

| US8408780B2 (en) * | 2009-11-03 | 2013-04-02 | Apple Inc. | Portable computer housing with integral display |

| US8743309B2 (en) | 2009-11-10 | 2014-06-03 | Apple Inc. | Methods for fabricating display structures |

| DE112011100842T5 (de) * | 2010-03-08 | 2013-01-17 | Semiconductor Energy Laboratory Co., Ltd. | Halbleiterbauelement und Verfahren zu dessen Herstellung |

| KR101048918B1 (ko) * | 2010-04-28 | 2011-07-12 | 삼성모바일디스플레이주식회사 | 터치 스크린 패널 및 이를 구비한 영상표시장치 |

| KR101343293B1 (ko) * | 2010-04-30 | 2013-12-18 | 샤프 가부시키가이샤 | 회로 기판 및 표시 장치 |

| JP5530839B2 (ja) * | 2010-07-09 | 2014-06-25 | パナソニック株式会社 | 固体撮像装置 |

| US8467177B2 (en) | 2010-10-29 | 2013-06-18 | Apple Inc. | Displays with polarizer windows and opaque masking layers for electronic devices |

| US9143668B2 (en) | 2010-10-29 | 2015-09-22 | Apple Inc. | Camera lens structures and display structures for electronic devices |

| US8753917B2 (en) * | 2010-12-14 | 2014-06-17 | International Business Machines Corporation | Method of fabricating photoconductor-on-active pixel device |

| US8446514B2 (en) * | 2011-05-09 | 2013-05-21 | Intellectual Ventures Fund 83 Llc | Capturing images using a switchable imaging apparatus |

| JP5978577B2 (ja) * | 2011-09-16 | 2016-08-24 | 株式会社リコー | 多層配線基板 |

| JP5876265B2 (ja) * | 2011-10-11 | 2016-03-02 | 富士フイルム株式会社 | 有機撮像素子 |

| US9158113B2 (en) * | 2012-03-14 | 2015-10-13 | Google Inc. | Integrated display and photosensor |

| JP5737358B2 (ja) * | 2013-10-22 | 2015-06-17 | セイコーエプソン株式会社 | 光電変換装置 |

| KR20150073539A (ko) * | 2013-12-23 | 2015-07-01 | 삼성전자주식회사 | 전자장치의 입력 감지장치 및 방법 |

| CN103941452A (zh) * | 2014-03-17 | 2014-07-23 | 京东方科技集团股份有限公司 | 阵列基板及显示装置 |

| WO2015141777A1 (ja) * | 2014-03-20 | 2015-09-24 | シャープ株式会社 | 光検出装置 |

| TWI656631B (zh) * | 2014-03-28 | 2019-04-11 | 日商半導體能源研究所股份有限公司 | 攝像裝置 |

| KR20150120730A (ko) * | 2014-04-18 | 2015-10-28 | 삼성전자주식회사 | 물리적 버튼과 이미지 센서를 내장한 디스플레이 모듈과 이의 제조 방법 |

| US9638950B2 (en) | 2014-05-15 | 2017-05-02 | Apple Inc. | Display with opaque border resistant to electrostatic discharge |

| JP6612056B2 (ja) | 2014-05-16 | 2019-11-27 | 株式会社半導体エネルギー研究所 | 撮像装置、及び監視装置 |

| KR20220100106A (ko) | 2014-06-09 | 2022-07-14 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 촬상 장치 |

| JP6545541B2 (ja) | 2014-06-25 | 2019-07-17 | 株式会社半導体エネルギー研究所 | 撮像装置、監視装置、及び電子機器 |

| TW202243228A (zh) | 2014-06-27 | 2022-11-01 | 日商半導體能源研究所股份有限公司 | 攝像裝置及電子裝置 |

| JP6389685B2 (ja) * | 2014-07-30 | 2018-09-12 | キヤノン株式会社 | 撮像装置、および、撮像システム |

| JP6555956B2 (ja) | 2014-07-31 | 2019-08-07 | 株式会社半導体エネルギー研究所 | 撮像装置、監視装置、及び電子機器 |

| KR101640192B1 (ko) | 2014-08-05 | 2016-07-18 | 삼성디스플레이 주식회사 | 디스플레이 장치 |

| KR102509203B1 (ko) | 2014-08-29 | 2023-03-14 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 촬상 장치 및 전자 기기 |

| JP6552336B2 (ja) | 2014-08-29 | 2019-07-31 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| KR102545592B1 (ko) | 2014-09-02 | 2023-06-21 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 촬상 장치 및 전자 기기 |

| WO2016046685A1 (en) * | 2014-09-26 | 2016-03-31 | Semiconductor Energy Laboratory Co., Ltd. | Imaging device |

| JP6570417B2 (ja) * | 2014-10-24 | 2019-09-04 | 株式会社半導体エネルギー研究所 | 撮像装置および電子機器 |

| WO2016170442A1 (en) * | 2015-04-22 | 2016-10-27 | Semiconductor Energy Laboratory Co., Ltd. | Imaging device, method for driving imaging device, and electronic device |

| JP6777421B2 (ja) | 2015-05-04 | 2020-10-28 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US11728356B2 (en) | 2015-05-14 | 2023-08-15 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion element and imaging device |

| US9860465B2 (en) | 2015-06-23 | 2018-01-02 | Semiconductor Energy Laboratory Co., Ltd. | Imaging device and electronic device |

| US9754980B2 (en) | 2015-06-30 | 2017-09-05 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion element and imaging device |

| CN107534553B (zh) * | 2015-09-24 | 2021-02-26 | 锡克拜控股有限公司 | 证件的重新认证 |

| JP6796461B2 (ja) | 2015-11-18 | 2020-12-09 | 株式会社半導体エネルギー研究所 | 半導体装置、コンピュータ及び電子機器 |

| JP2017152656A (ja) * | 2016-02-26 | 2017-08-31 | Tianma Japan株式会社 | イメージセンサおよびその製造方法 |

| CN110100311B (zh) * | 2016-12-27 | 2023-06-27 | 夏普株式会社 | 摄像面板及其制造方法 |

| CN106527004B (zh) * | 2016-12-29 | 2019-07-05 | 深圳市华星光电技术有限公司 | 阵列基板、液晶显示面板及阵列基板制造方法 |

| TWI622844B (zh) * | 2017-03-29 | 2018-05-01 | 友達光電股份有限公司 | 畫素單元與其製造方法 |

| US11503143B2 (en) | 2019-12-03 | 2022-11-15 | Apple Inc. | Handheld electronic device |

| US11637919B2 (en) | 2019-12-03 | 2023-04-25 | Apple Inc. | Handheld electronic device |

| CN112713161B (zh) * | 2020-12-30 | 2023-10-31 | 武汉华星光电技术有限公司 | 一种阵列基板及其制备方法 |

Family Cites Families (69)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5722251A (en) | 1980-06-02 | 1982-02-05 | Xerox Corp | Electrostatic developing method and device |

| JPS5722251U (ja) * | 1980-07-11 | 1982-02-04 | ||

| US4517733A (en) | 1981-01-06 | 1985-05-21 | Fuji Xerox Co., Ltd. | Process for fabricating thin film image pick-up element |

| US5650637A (en) | 1982-04-30 | 1997-07-22 | Seiko Epson Corporation | Active matrix assembly |

| JPS59115668A (ja) | 1982-12-22 | 1984-07-04 | Fuji Xerox Co Ltd | 読取印字複写装置 |

| JPS60213062A (ja) | 1984-04-09 | 1985-10-25 | Hosiden Electronics Co Ltd | 薄膜トランジスタの製造方法 |

| JPS6255961A (ja) | 1985-09-05 | 1987-03-11 | Mitsubishi Electric Corp | 固体撮像装置 |

| JPS6286855A (ja) * | 1985-10-14 | 1987-04-21 | Fuji Photo Film Co Ltd | 放射線用固体撮像素子 |

| JPH069242B2 (ja) * | 1985-10-14 | 1994-02-02 | 富士写真フイルム株式会社 | 固体撮像素子およびその製造方法 |

| JPS62125329A (ja) | 1985-11-27 | 1987-06-06 | Hosiden Electronics Co Ltd | 透過形表示装置 |

| JPH01220862A (ja) * | 1988-02-29 | 1989-09-04 | Seiko Epson Corp | 固体撮像素子 |

| JPH0229623A (ja) | 1988-07-19 | 1990-01-31 | Semiconductor Energy Lab Co Ltd | 液晶表示装置 |

| JPH02128468A (ja) | 1988-11-08 | 1990-05-16 | Fujitsu Ltd | 固体撮像装置及びその製造方法 |

| JPH02262369A (ja) * | 1989-03-31 | 1990-10-25 | Toshiba Corp | 固体撮像装置及びその製造方法 |

| JPH02265274A (ja) * | 1989-04-06 | 1990-10-30 | Toshiba Corp | 固体撮像装置 |

| JPH02280374A (ja) * | 1989-04-21 | 1990-11-16 | Toshiba Corp | 固体撮像装置の電極接続方法 |

| JP2617798B2 (ja) | 1989-09-22 | 1997-06-04 | 三菱電機株式会社 | 積層型半導体装置およびその製造方法 |

| JPH0734467B2 (ja) * | 1989-11-16 | 1995-04-12 | 富士ゼロックス株式会社 | イメージセンサ製造方法 |

| JP2714993B2 (ja) | 1989-12-15 | 1998-02-16 | セイコーエプソン株式会社 | 液晶表示装置 |

| JPH03187267A (ja) | 1989-12-15 | 1991-08-15 | Mitsubishi Electric Corp | 固体撮像装置 |

| JPH0423470A (ja) * | 1990-05-18 | 1992-01-27 | Fuji Xerox Co Ltd | イメージセンサ |

| US5273910A (en) * | 1990-08-08 | 1993-12-28 | Minnesota Mining And Manufacturing Company | Method of making a solid state electromagnetic radiation detector |

| US5182624A (en) * | 1990-08-08 | 1993-01-26 | Minnesota Mining And Manufacturing Company | Solid state electromagnetic radiation detector fet array |

| US5589847A (en) | 1991-09-23 | 1996-12-31 | Xerox Corporation | Switched capacitor analog circuits using polysilicon thin film technology |

| US5313055A (en) * | 1991-09-30 | 1994-05-17 | Fuji Xerox Co., Ltd. | Two-dimensional image read/display device |

| KR0125454B1 (ko) | 1992-02-03 | 1997-12-26 | 쯔지 하루오 | 광투과율 조정 장치 |

| GB9202693D0 (en) | 1992-02-08 | 1992-03-25 | Philips Electronics Uk Ltd | A method of manufacturing a large area active matrix array |

| US5424244A (en) | 1992-03-26 | 1995-06-13 | Semiconductor Energy Laboratory Co., Ltd. | Process for laser processing and apparatus for use in the same |

| TW223178B (en) | 1992-03-27 | 1994-05-01 | Semiconductor Energy Res Co Ltd | Semiconductor device and its production method |

| GB9209734D0 (en) | 1992-05-06 | 1992-06-17 | Philips Electronics Uk Ltd | An image sensor |

| JP3223383B2 (ja) | 1992-06-30 | 2001-10-29 | カシオ計算機株式会社 | 液晶表示装置およびそれを用いた機器 |

| JPH0618845A (ja) | 1992-07-03 | 1994-01-28 | Casio Comput Co Ltd | 液晶表示装置およびそれを用いた機器 |

| US5491566A (en) * | 1992-11-27 | 1996-02-13 | Goldstar Co., Ltd. | Integrated input-output device having a reading and a printing section on a single substrate |

| TW226478B (en) | 1992-12-04 | 1994-07-11 | Semiconductor Energy Res Co Ltd | Semiconductor device and method for manufacturing the same |

| JPH06342146A (ja) | 1992-12-11 | 1994-12-13 | Canon Inc | 画像表示装置、半導体装置及び光学機器 |

| JP3382300B2 (ja) | 1993-05-21 | 2003-03-04 | キヤノン株式会社 | 画像表示装置 |

| DE69330709T2 (de) | 1992-12-28 | 2002-07-11 | Canon Kk | Blickrichtungsdetektor und Kamera mit diesem Detektor |

| JP3347423B2 (ja) * | 1993-08-31 | 2002-11-20 | キヤノン株式会社 | 液晶表示装置 |

| DE69430687T2 (de) | 1993-02-10 | 2002-11-21 | Seiko Epson Corp | Aktives matrix-substrat und dünnfilmtransistor und verfahren zur herstellung |

| JPH06334920A (ja) | 1993-03-23 | 1994-12-02 | Nippon Hoso Kyokai <Nhk> | 固体撮像素子とその駆動方法 |

| JPH0762865B2 (ja) | 1993-05-13 | 1995-07-05 | 日本電気株式会社 | 指紋画像入力装置 |

| GB9311129D0 (en) | 1993-05-28 | 1993-07-14 | Philips Electronics Uk Ltd | Electronic devices with-film circuit elements forming a sampling circuit |

| KR100294026B1 (ko) | 1993-06-24 | 2001-09-17 | 야마자끼 순페이 | 전기광학장치 |

| JP3030368B2 (ja) | 1993-10-01 | 2000-04-10 | 株式会社半導体エネルギー研究所 | 半導体装置およびその作製方法 |

| JPH07302912A (ja) | 1994-04-29 | 1995-11-14 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP3715996B2 (ja) | 1994-07-29 | 2005-11-16 | 株式会社日立製作所 | 液晶表示装置 |

| JP3565453B2 (ja) * | 1994-08-23 | 2004-09-15 | キヤノン株式会社 | 画像入出力装置 |

| US5812109A (en) * | 1994-08-23 | 1998-09-22 | Canon Kabushiki Kaisha | Image input/output apparatus |

| JP2953321B2 (ja) | 1994-08-31 | 1999-09-27 | 日本電気株式会社 | 原稿読取装置における密着型イメージセンサ |

| JPH08186241A (ja) * | 1995-01-06 | 1996-07-16 | Canon Inc | 撮像素子と固体撮像装置 |

| JP3675886B2 (ja) | 1995-03-17 | 2005-07-27 | 株式会社半導体エネルギー研究所 | 薄膜半導体デバイスの作製方法 |

| US5760760A (en) | 1995-07-17 | 1998-06-02 | Dell Usa, L.P. | Intelligent LCD brightness control system |

| JP3744980B2 (ja) | 1995-07-27 | 2006-02-15 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US6091382A (en) | 1995-12-30 | 2000-07-18 | Casio Computer Co., Ltd. | Display device for performing display operation in accordance with signal light and driving method therefor |

| US5831699A (en) | 1996-04-29 | 1998-11-03 | Motorola, Inc. | Display with inactive portions and active portions, and having drivers in the inactive portions |

| US6005648A (en) | 1996-06-25 | 1999-12-21 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| JP3708637B2 (ja) | 1996-07-15 | 2005-10-19 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| JP3473658B2 (ja) | 1996-07-18 | 2003-12-08 | アルプス電気株式会社 | 指紋読取り装置 |

| US5831258A (en) | 1996-08-20 | 1998-11-03 | Xerox Corporation | Pixel circuit with integrated amplifer |

| US6233027B1 (en) | 1997-01-07 | 2001-05-15 | Canon Kabushiki Kaisha | Liquid crystal device and process for production thereof |

| JP4027465B2 (ja) | 1997-07-01 | 2007-12-26 | 株式会社半導体エネルギー研究所 | アクティブマトリクス型表示装置およびその製造方法 |

| US6388652B1 (en) | 1997-08-20 | 2002-05-14 | Semiconductor Energy Laboratory Co., Ltd. | Electrooptical device |

| JP3838393B2 (ja) | 1997-09-02 | 2006-10-25 | 株式会社半導体エネルギー研究所 | イメージセンサを内蔵した表示装置 |

| US6031655A (en) | 1997-09-12 | 2000-02-29 | Canon Kabushiki Kaisha | Spatial light modulator and picture-forming apparatus including same |

| JP4294745B2 (ja) | 1997-09-26 | 2009-07-15 | 株式会社半導体エネルギー研究所 | 光電変換装置の作製方法 |

| JP4044187B2 (ja) | 1997-10-20 | 2008-02-06 | 株式会社半導体エネルギー研究所 | アクティブマトリクス型表示装置およびその作製方法 |

| US6028581A (en) | 1997-10-21 | 2000-02-22 | Sony Corporation | Method and apparatus for a liquid crystal display (LCD) having an input function |

| JPH11326954A (ja) | 1998-05-15 | 1999-11-26 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| US6277679B1 (en) | 1998-11-25 | 2001-08-21 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing thin film transistor |

-

1997

- 1997-09-20 JP JP27345897A patent/JP4271268B2/ja not_active Expired - Lifetime

-

1998

- 1998-09-18 US US09/156,461 patent/US7046282B1/en not_active Expired - Fee Related

-

2006

- 2006-05-04 US US11/418,279 patent/US7286173B2/en not_active Expired - Fee Related

-

2007

- 2007-08-14 US US11/838,600 patent/US7791117B2/en not_active Expired - Fee Related

-

2010

- 2010-09-03 US US12/875,537 patent/US8564035B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20060227232A1 (en) | 2006-10-12 |

| US7791117B2 (en) | 2010-09-07 |

| US8564035B2 (en) | 2013-10-22 |

| US20100321357A1 (en) | 2010-12-23 |

| US7046282B1 (en) | 2006-05-16 |

| US20070290246A1 (en) | 2007-12-20 |

| JPH1197690A (ja) | 1999-04-09 |

| US7286173B2 (en) | 2007-10-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4271268B2 (ja) | イメージセンサおよびイメージセンサ一体型アクティブマトリクス型表示装置 | |

| JP4044187B2 (ja) | アクティブマトリクス型表示装置およびその作製方法 | |

| JP4027465B2 (ja) | アクティブマトリクス型表示装置およびその製造方法 | |

| JP4255527B2 (ja) | 半導体装置 | |

| JPH1197664A (ja) | 電子機器およびその作製方法 | |

| JP4183784B2 (ja) | 液晶パネルの作製方法 | |

| JP5025596B2 (ja) | イメージセンサ | |

| JP4700659B2 (ja) | 液晶表示装置 | |

| JP5138107B2 (ja) | イメージセンサ、電子機器 | |

| JP4986923B2 (ja) | イメージセンサの作製方法 | |

| JP5312442B2 (ja) | 半導体装置、イメージセンサ及び撮影機器 | |

| JP4163156B2 (ja) | 表示装置 | |

| JP5100799B2 (ja) | 液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040806 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040806 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070831 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080513 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080620 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20080620 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080722 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080908 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20081111 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081225 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090224 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090225 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120306 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120306 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120306 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120306 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130306 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130306 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140306 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |