JP2010153501A - Method of manufacturing semiconductor device - Google Patents

Method of manufacturing semiconductor device Download PDFInfo

- Publication number

- JP2010153501A JP2010153501A JP2008328419A JP2008328419A JP2010153501A JP 2010153501 A JP2010153501 A JP 2010153501A JP 2008328419 A JP2008328419 A JP 2008328419A JP 2008328419 A JP2008328419 A JP 2008328419A JP 2010153501 A JP2010153501 A JP 2010153501A

- Authority

- JP

- Japan

- Prior art keywords

- region

- misfet

- semiconductor

- ion implantation

- channel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Abstract

Description

本発明は、半導体装置の製造方法に関し、特に、MISFETを有する半導体装置の製造に適用して有効な技術に関する。 The present invention relates to a method for manufacturing a semiconductor device, and more particularly to a technique effective when applied to the manufacture of a semiconductor device having a MISFET.

MISFETなどの半導体素子を半導体基板に形成し、更に半導体基板上に多層配線構造を形成して半導体素子間を結線することで、半導体装置が製造される。 A semiconductor device is manufactured by forming a semiconductor element such as a MISFET on a semiconductor substrate, forming a multilayer wiring structure on the semiconductor substrate, and connecting the semiconductor elements.

特開2008−42059号公報(特許文献1)には、少なくともレトログレードチャネル構造を有するMISトランジスタを備えた半導体装置において、ランダム成分によるトランジスタ特性のばらつきを抑制した、信頼性の高い半導体装置及びその製造方法を提供する技術が記載されている。 Japanese Patent Laying-Open No. 2008-42059 (Patent Document 1) discloses a highly reliable semiconductor device in which variation in transistor characteristics due to random components is suppressed in a semiconductor device including at least a MIS transistor having a retrograde channel structure and its Techniques providing manufacturing methods are described.

特開2008−47698号公報(特許文献2)には、微細化に伴いトランジスタの特性ばらつきが増加するのを抑制することが可能な半導体記憶装置に関する技術が記載されている。 Japanese Patent Laying-Open No. 2008-47698 (Patent Document 2) describes a technology related to a semiconductor memory device capable of suppressing an increase in variation in transistor characteristics due to miniaturization.

国際公開第2004/077673号パンフレット(特許文献3)には、MOSトランジスタの基板電位を制御することによって、動作速度のばらつきを小さく抑制する技術が記載されている。 International Publication No. 2004/076673 pamphlet (Patent Document 3) describes a technique for suppressing variations in operating speed by controlling the substrate potential of a MOS transistor.

非特許文献1には、MOSFETのしきい値のばらつきに関する技術が記載されている。

本発明者の検討によれば、次のことが分かった。 According to the study of the present inventor, the following has been found.

MISFETを有する半導体装置は、次のようにして製造することができる。すなわち、半導体基板に素子分離領域を形成し、素子分離領域で規定された活性領域に、MISFETのしきい値を調整するためのチャネルドープイオン注入を行なってから、ゲート絶縁膜およびゲート電極を形成する。それから、ゲート電極をマスクにしてイオン注入によりLDD用のエクステンション領域と、ハロー領域を形成してから、ゲート電極の側壁上に側壁絶縁膜を形成し、ゲート電極および側壁絶縁膜をマスクにしてイオン注入により、エクステンション領域よりも高不純物濃度のソース・ドレイン領域を形成する。その後、ソース・ドレイン領域の上部にサリサイドプロセスにより金属シリサイド層を形成する。 A semiconductor device having a MISFET can be manufactured as follows. That is, an element isolation region is formed in a semiconductor substrate, and channel doping ion implantation for adjusting the threshold value of the MISFET is performed in an active region defined by the element isolation region, and then a gate insulating film and a gate electrode are formed. To do. Then, an extension region for LDD and a halo region are formed by ion implantation using the gate electrode as a mask, and then a sidewall insulating film is formed on the sidewall of the gate electrode, and the gate electrode and the sidewall insulating film are used as a mask. By implantation, source / drain regions having a higher impurity concentration than the extension region are formed. Thereafter, a metal silicide layer is formed on the source / drain regions by a salicide process.

一般に、n型不純物が添加された多結晶シリコンからなるゲート電極を用いたnチャネル型のMISFETでは、チャネルドープイオン注入にはホウ素(B)を用いる。しかしながら、ホウ素(B)をチャネルドープイオン注入に用いた場合、実際に形成したMISFETのしきい値のばらつきは、チャネルドープ不純物の分布の離散性で計算されるしきい値のばらつきよりも大きな値を示すことが、上記非特許文献1により分かっている。

In general, in an n-channel MISFET using a gate electrode made of polycrystalline silicon to which an n-type impurity is added, boron (B) is used for channel doping ion implantation. However, when boron (B) is used for channel-doped ion implantation, the threshold variation of the actually formed MISFET is larger than the threshold variation calculated by the discreteness of the channel-doped impurity distribution. It is known from Non-Patent

本発明者は、一般的な手法で形成したMISFETのしきい値のばらつきが、チャネルドープ不純物の分布の離散性で計算されるしきい値のばらつきよりも大きな値を示す理由について検討したところ、次のことが分かった。すなわち、半導体基板にチャネルドープイオン注入した場合、注入直後の段階では、注入された不純物はランダムに配置されているが、その後の種々の加熱工程で不純物が拡散(移動)すると、不純物のランダム配置が崩れ、注入直後に比べて不純物の分布に偏りが生じてしまう。換言すれば、チャネルドープイオン注入した直後の段階では、注入した不純物の配置のランダム性が高いが、その後の種々の加熱工程で不純物が拡散(移動)すると、不純物の配置のランダム性が低下してしまうのである。 The inventor examined the reason why the threshold variation of the MISFET formed by a general technique shows a larger value than the threshold variation calculated by the discreteness of the distribution of the channel-doped impurities. I found the following. That is, when channel-doped ions are implanted into a semiconductor substrate, the implanted impurities are randomly arranged at the stage immediately after the implantation. However, when impurities are diffused (moved) in various subsequent heating processes, the impurities are randomly arranged. Collapses, and the impurity distribution is biased compared to immediately after the implantation. In other words, in the stage immediately after the channel dope ion implantation, the randomness of the implanted impurity is high, but if the impurity diffuses (moves) in the subsequent various heating processes, the randomness of the impurity is reduced. It will end up.

なお、不純物の配置のランダム性が高い状態では、微視的(原子配列のレベル)には、不純物は均一(規則的)に配置されているのではなく、ばらばら(ランダム)に存在しているが、微視的にランダムであるが故に、巨視的(チャネル領域のレベル)には、不純物は偏りなく同じように分布している。このため、不純物の配置のランダム性が高い状態では、チャネル領域同士を比べたときの不純物分布の違い(あるMISFETのチャネル領域の不純物分布と他のMISFETのチャネル領域の不純物分布との差)が小さく、MISFETのしきい値のばらつきが小さい。しかしながら、不純物配置のランダム性が低下すると、この状態が崩れ、巨視的な不純物の分布(チャネル領域のレベルでの不純物分布)に偏りが生じてしまう。このため、注入後に熱拡散によって不純物の配置のランダム性が低くなった状態では、チャネル領域同士を比べたときの不純物分布の違い(あるMISFETのチャネル領域の不純物分布と他のMISFETのチャネル領域の不純物分布との差)が大きく、MISFETのしきい値のばらつきが大きくなってしまう。 In addition, in a state where the randomness of the arrangement of impurities is high, the impurities are not arranged uniformly (regularly) microscopically (at the level of atomic arrangement) but are present in a random (random) manner. However, since they are microscopically random, the impurities are distributed equally in a macroscopic manner (channel region level). For this reason, in a state where the randomness of the impurity arrangement is high, the difference in impurity distribution (difference between the impurity distribution in the channel region of one MISFET and the impurity distribution in the channel region of another MISFET) when the channel regions are compared with each other. Small, variation in threshold of MISFET is small. However, if the randomness of the impurity arrangement decreases, this state collapses, and the macroscopic impurity distribution (impurity distribution at the channel region level) is biased. Therefore, in the state where the randomness of the impurity arrangement is lowered by thermal diffusion after the implantation, the difference in impurity distribution when comparing the channel regions (impurity distribution in the channel region of one MISFET and the channel region of another MISFET) The difference between the impurity distribution and the MISFET becomes large.

このように、一般的な手法で形成したMISFETでは、チャネルドープイオン注入した不純物の配置が、注入後の熱拡散によってランダム性を低下させることにより、MISFETのしきい値のばらつきが大きくなってしまう。MISFETのしきい値のばらつきが大きいと、半導体装置の性能が低下してしまうため、MISFETのしきい値のばらつきを抑制して半導体装置の性能を向上させることが望まれる。 As described above, in the MISFET formed by a general technique, the dispersion of the threshold value of the MISFET becomes large because the arrangement of the impurity implanted with the channel dope ion reduces the randomness by the thermal diffusion after the implantation. . If the variation in the threshold value of the MISFET is large, the performance of the semiconductor device is degraded. Therefore, it is desired to improve the performance of the semiconductor device by suppressing the variation in the threshold value of the MISFET.

上記特許文献1では、MISFETの特性のばらつきを低減するために、チャネルドープイオン注入する不純物のプロファイルに変調を加えることで対策を行っている。半導体基板の表面近傍のチャネル不純物の分布が、MISFETの特性のばらつきに最も影響するため、この手法は一部有効である。しかしながら、チャネル不純物の配置(分布)のランダム性を高める工夫をしないと、離散不純物分布で説明される特性(しきい値)のばらつきのレベルまで、実際のMISFETの特性のばらつきを低減させることは困難である。

In the above-mentioned

上記特許文献2では、デバイスの特性のばらつきが問題となるメモリセルの最小トランジスタのゲート長やゲート幅を大きくすることで、トランジスタの特性のばらつきによる影響を回避している。しかしながら、この手法は、トランジスタの特性(しきい値)のばらつきを改善する根本的解決手段ではなく、トランジスタの微細化(半導体装置の小型化)を困難にする。

In

上記特許文献3では、しきい値の変動に対して、基板電位を制御することで対応している。しかしながら、離散不純物による特性のばらつきが問題になる場合、隣接するトランジスタ間での特性の差が大きく、多数のトランジスタが形成された半導体装置においては、基板電位を制御することによる個々のトランジスタの特性(しきい値)のばらつきを制御することは困難である。

In the above-mentioned

本発明の目的は、MISFETのしきい値のばらつきを抑制して半導体装置の性能を向上させることができる技術を提供することにある。 An object of the present invention is to provide a technique capable of improving the performance of a semiconductor device by suppressing variations in threshold values of MISFETs.

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。 The above and other objects and novel features of the present invention will be apparent from the description of this specification and the accompanying drawings.

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。 Of the inventions disclosed in the present application, the outline of typical ones will be briefly described as follows.

代表的な実施の形態による半導体装置の製造方法は、(a)半導体基板を準備する工程、(b)前記半導体基板に、前記第1MISFETのしきい値調整用のイオン注入を行なう工程、(c)前記半導体基板の主面に前記第1MISFETのゲート絶縁膜用の第1絶縁膜を形成する工程、(d)前記第1絶縁膜上に前記第1MISFETの第1ゲート電極を形成する工程、(e)前記(d)工程後、前記第1ゲート電極をマスクとして前記半導体基板にイオン注入を行ない、前記半導体基板に第1導電型の第1半導体領域を形成する工程、(f)前記(d)工程後、前記半導体基板に第1元素のイオン注入を行なう工程、(g)前記(e)工程および前記(f)工程後に、前記第1ゲート電極の側壁上に側壁絶縁膜を形成する工程、(h)前記第1ゲート電極および前記側壁絶縁膜をマスクとして前記半導体基板にイオン注入を行ない、前記半導体基板に前記第1半導体領域よりも不純物濃度が高い第1導電型の第2半導体領域を形成する工程、を有している。そして、前記第1および第2半導体領域は、前記第1MISFETのソースまたはドレイン用の半導体領域として機能し、前記(f)工程でイオン注入する前記第1元素は、炭素、窒素またはフッ素のうちの1種以上からなり、前記(f)工程で前記第1元素が導入された領域の少なくとも一部は、前記第1MISFETのチャネル領域と前記第1半導体領域との間に位置する。 A method of manufacturing a semiconductor device according to a representative embodiment includes (a) a step of preparing a semiconductor substrate, (b) a step of ion implantation for adjusting the threshold value of the first MISFET into the semiconductor substrate, (c) ) Forming a first insulating film for the gate insulating film of the first MISFET on the main surface of the semiconductor substrate; (d) forming a first gate electrode of the first MISFET on the first insulating film; e) After the step (d), ion implantation is performed on the semiconductor substrate using the first gate electrode as a mask to form a first semiconductor region of a first conductivity type in the semiconductor substrate, (f) the step (d) ) After the step, the step of ion-implanting the first element into the semiconductor substrate, (g) After the step (e) and the step (f), a step of forming a sidewall insulating film on the sidewall of the first gate electrode , (H) ago Performing ion implantation on the semiconductor substrate using the first gate electrode and the sidewall insulating film as a mask to form a second semiconductor region of a first conductivity type having an impurity concentration higher than that of the first semiconductor region in the semiconductor substrate; have. The first and second semiconductor regions function as a semiconductor region for the source or drain of the first MISFET, and the first element ion-implanted in the step (f) is carbon, nitrogen, or fluorine. At least a part of the region where the first element is introduced in the step (f) is located between the channel region of the first MISFET and the first semiconductor region.

また、他の代表的な実施の形態による半導体装置の製造方法は、炭素、窒素またはフッ素のうちの1種以上が導入された半導体層を上部に有する半導体基板を準備し、前記半導体層にMISFETを形成するものである。 According to another exemplary embodiment of the present invention, a method of manufacturing a semiconductor device includes preparing a semiconductor substrate having a semiconductor layer into which one or more of carbon, nitrogen, and fluorine are introduced at the top, and MISFET in the semiconductor layer Is formed.

また、他の代表的な実施の形態による半導体装置の製造方法は、(a)半導体基板を準備する工程、(b)前記(a)工程後に前記半導体基板の主面に第1MISFETのゲート絶縁膜用の第1絶縁膜を形成する工程、(c)前記(b)工程後に前記第1絶縁膜上に第1導電体層を形成する工程、(d)前記(c)工程後に前記半導体基板に前記第1MISFETのしきい値調整用のイオン注入を行なう工程、(e)前記(d)工程後に前記第1導電体層上に第2導電体層を形成する工程、(f)前記第2導電体層および前記第1導電体層をパターニングして前記第1MISFETの第1ゲート電極を形成する工程、(g)前記(f)工程後に前記半導体基板に前記第1MISFETのソースまたはドレイン用の半導体領域を形成する工程を有するものである。 Further, the semiconductor device manufacturing method according to another representative embodiment includes (a) a step of preparing a semiconductor substrate, (b) a gate insulating film of a first MISFET on the main surface of the semiconductor substrate after the step (a). Forming a first insulating film for the semiconductor substrate, (c) forming a first conductor layer on the first insulating film after the step (b), (d) forming the semiconductor substrate on the semiconductor substrate after the step (c) Performing ion implantation for adjusting the threshold value of the first MISFET, (e) forming a second conductor layer on the first conductor layer after the step (d), and (f) the second conductivity. Forming a first gate electrode of the first MISFET by patterning a body layer and the first conductor layer; (g) a semiconductor region for the source or drain of the first MISFET on the semiconductor substrate after the step (f); The process of forming It is intended to.

また、他の代表的な実施の形態による半導体装置の製造方法は、(a)半導体基板を準備する工程、(b)前記半導体基板にMISFETのしきい値調整用のイオン注入を行なう工程、(c)前記半導体基板の主面にゲート絶縁膜用の第1絶縁膜を形成する工程、(d)前記第1絶縁膜上にゲート電極を形成する工程、(e)前記半導体基板にソースまたはドレイン用の半導体領域を形成する工程を有する。そして、前記(b)工程でイオン注入する元素として、インジウムまたはガリウムの一方または両方か、あるいはそれにホウ素を加えたものを用いる。 Further, a method of manufacturing a semiconductor device according to another representative embodiment includes (a) a step of preparing a semiconductor substrate, (b) a step of performing ion implantation for adjusting a threshold value of a MISFET in the semiconductor substrate, c) forming a first insulating film for a gate insulating film on the main surface of the semiconductor substrate; (d) forming a gate electrode on the first insulating film; and (e) a source or drain on the semiconductor substrate. Forming a semiconductor region. In addition, as the element to be ion-implanted in the step (b), one or both of indium and gallium, or an element in which boron is added thereto is used.

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。 Among the inventions disclosed in the present application, effects obtained by typical ones will be briefly described as follows.

代表的な実施の形態によれば、MISFETのしきい値のばらつきを抑制して半導体装置の性能を向上させることができる。 According to the typical embodiment, it is possible to improve the performance of the semiconductor device by suppressing the variation in the threshold value of the MISFET.

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。 In the following embodiments, when it is necessary for the sake of convenience, the description will be divided into a plurality of sections or embodiments. However, unless otherwise specified, they are not irrelevant to each other. There are some or all of the modifications, details, supplementary explanations, and the like. Further, in the following embodiments, when referring to the number of elements (including the number, numerical value, quantity, range, etc.), especially when clearly indicated and when clearly limited to a specific number in principle, etc. Except, it is not limited to the specific number, and may be more or less than the specific number. Further, in the following embodiments, the constituent elements (including element steps and the like) are not necessarily indispensable unless otherwise specified and apparently essential in principle. Needless to say. Similarly, in the following embodiments, when referring to the shapes, positional relationships, etc. of the components, etc., the shapes are substantially the same unless otherwise specified, or otherwise apparent in principle. And the like are included. The same applies to the above numerical values and ranges.

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。 Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings. Note that components having the same function are denoted by the same reference symbols throughout the drawings for describing the embodiments, and the repetitive description thereof will be omitted. In the following embodiments, the description of the same or similar parts will not be repeated in principle unless particularly necessary.

また、実施の形態で用いる図面においては、断面図であっても図面を見易くするためにハッチングを省略する場合もある。また、平面図であっても図面を見易くするためにハッチングを付す場合もある。 In the drawings used in the embodiments, hatching may be omitted even in a cross-sectional view so as to make the drawings easy to see. Further, even a plan view may be hatched to make the drawing easy to see.

(実施の形態1)

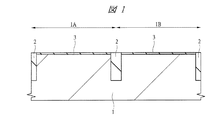

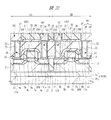

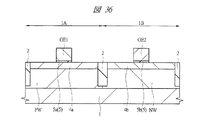

本実施の形態の半導体装置の製造工程を図面を参照して説明する。図1〜図15は、本発明の一実施の形態である半導体装置、ここではCMISFET(Complementary Metal Insulator Semiconductor Field Effect Transistor)を有する半導体装置の製造工程中の要部断面図である。

(Embodiment 1)

A manufacturing process of the semiconductor device of the present embodiment will be described with reference to the drawings. FIG. 1 to FIG. 15 are cross-sectional views of a principal part during a manufacturing process of a semiconductor device according to an embodiment of the present invention, here, a semiconductor device having a CMISFET (Complementary Metal Insulator Semiconductor Field Effect Transistor).

まず、図1に示されるように、例えば1〜10Ωcm程度の比抵抗を有するp型の単結晶シリコンなどからなる半導体基板(半導体ウエハ)1を準備する。それから、半導体基板1の主面に素子分離領域2を形成する。素子分離領域2は酸化シリコンなどの絶縁体からなり、例えばSTI(Shallow Trench Isolation)法またはLOCOS(Local Oxidization of Silicon)法などにより形成される。例えば、半導体基板1に形成された溝(素子分離溝)に埋め込まれた絶縁膜により、素子分離領域2を形成することができる。素子分離領域2によって、nチャネル型MISFET(Metal Insulator Semiconductor Field Effect Transistor:MIS型電界効果トランジスタ)Qnが形成される領域(活性領域)であるnMIS形成領域1Aと、pチャネル型MISFETQpが形成される領域(活性領域)であるpMIS形成領域1Bとが規定される。

First, as shown in FIG. 1, a semiconductor substrate (semiconductor wafer) 1 made of, for example, p-type single crystal silicon having a specific resistance of about 1 to 10 Ωcm is prepared. Then, the

次に、表面の汚染防止のための薄い絶縁膜(スルー膜)3を半導体基板1の表面(主面)に形成してから、図2に示されるように、pMIS形成領域1Bを覆うフォトレジスト膜(フォトレジストパターン)RP1aを、フォトリソグラフィ技術を用いて形成する。nMIS形成領域1Aは、このフォトレジスト膜RP1aでは覆われずに露出される。このフォトレジスト膜RP1aは、pMIS形成領域1Bへのイオン注入阻止マスクとして機能することができる。

Next, after forming a thin insulating film (through film) 3 for preventing surface contamination on the surface (main surface) of the

次に、nMIS形成領域1Aにおいて、半導体基板1の上層部分に、後で形成されるnチャネル型MISFETQnのしきい値調整用のイオン注入(すなわちチャネルドープイオン注入)IM1aを行なう。なお、図2では、チャネルドープイオン注入IM1aを矢印で模式的に示してある。

Next, in the

MIFETのしきい値調整用のイオン注入は、チャネルドープイオン注入と呼ぶこともでき、このチャネルドープイオン注入(しきい値調整用のイオン注入)によって、MISFETのチャネル領域に不純物が導入(ドープ)される。すなわち、チャネルドープイオン注入では、MISFETのチャネル領域を含む領域に、不純物(不純物イオン)が導入(ドープ)される。なお、ここでいう「MISFETのチャネル領域」とは、チャネルドープイオン注入の段階ではMISFETは形成されていなくとも、その後MISFETが形成されると、MISFETのチャネル領域となる領域に対応する。このことは、本実施の形態1および以下の実施の形態2〜6で述べるチャネルドープイオン注入(しきい値調整用のイオン注入)に共通である。 The ion implantation for adjusting the threshold value of the MISFET can also be referred to as channel doping ion implantation. By this channel doping ion implantation (ion implantation for adjusting the threshold value), impurities are introduced (doped) into the channel region of the MISFET. Is done. That is, in channel dope ion implantation, impurities (impurity ions) are introduced (doped) into a region including the channel region of the MISFET. The “channel region of the MISFET” here corresponds to a region that becomes a channel region of the MISFET when the MISFET is formed afterwards even though the MISFET is not formed at the channel doping ion implantation stage. This is common to channel dope ion implantation (threshold adjustment ion implantation) described in the first embodiment and the following second to sixth embodiments.

しきい値調整用のイオン注入IM1a、すなわちチャネルドープイオン注入IM1aでは、nチャネル型MISFETQnのチャネル領域を含む領域に、不純物(不純物イオン)が導入(イオン注入)されて、チャネルドープ層4aが形成される。このチャネルドープ層4aは、後でnチャネル型MISFETQnのチャネル領域となる領域を含んでいる。チャネルドープイオン注入IM1aによってチャネルドープ層4aに導入される不純物は、例えばホウ素(B)などのp型の不純物を用いることができる。このチャネルドープイオン注入IM1aでは、pMIS形成領域1Bを覆うフォトレジスト膜RP1aは、イオン注入阻止マスクとして機能するので、pMIS形成領域1Bの半導体基板1には、イオン注入されない。

In the ion implantation IM1a for adjusting the threshold, that is, the channel dope ion implantation IM1a, impurities (impurity ions) are introduced (ion implantation) into a region including the channel region of the n-channel MISFET Qn to form the

次に、nMIS形成領域1Aにおいて、半導体基板1の主面から所定の深さに渡ってp型ウエル(p型半導体領域)PWを形成する。p型ウエルPWは、pMIS形成領域1Bを覆うフォトレジスト膜RP1aをイオン注入阻止マスクとして、nMIS形成領域1Aの半導体基板1に例えばホウ素(B)などのp型の不純物をイオン注入することなどによって形成することができる。なお、チャネルドープ層4aは、半導体基板1の上層部分に浅く形成され、p型ウエルPWは、半導体基板1において、チャネルドープ層4aよりも深くまで形成されている。また、他の形態として、先にp型ウエルPWをイオン注入で形成してから、チャネルドープイオン注入IM1aによってチャネルドープ層4aを形成することもでき、これは以下の実施の形態2〜4でも同様である。

Next, in the

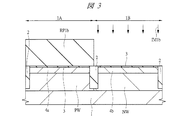

次に、図3に示されるように、アッシングなどによりフォトレジスト膜RP1aを除去してから、nMIS形成領域1Aを覆うフォトレジスト膜(フォトレジストパターン)RP1bを、フォトリソグラフィ技術を用いて形成する。pMIS形成領域1Bは、このフォトレジスト膜RP1bでは覆われずに露出される。このフォトレジスト膜RP1bは、nMIS形成領域1Aへのイオン注入阻止マスクとして機能することができる。

Next, as shown in FIG. 3, after removing the photoresist film RP1a by ashing or the like, a photoresist film (photoresist pattern) RP1b covering the

次に、pMIS形成領域1Bにおいて、半導体基板1の上層部分に、後で形成されるpチャネル型MISFETQpのしきい値調整用のイオン注入(すなわちチャネルドープイオン注入)IM1bを行なう。なお、図3では、チャネルドープイオン注入IM1bを矢印で模式的に示してある。

Next, in the

しきい値調整用のイオン注入IM1b、すなわちチャネルドープイオン注入IM1bでは、pチャネル型MISFETQpのチャネル領域を含む領域に、不純物(不純物イオン)が導入(イオン注入)されて、チャネルドープ層4bが形成される。このチャネルドープ層4bは、後でpチャネル型MISFETQpのチャネル領域となる領域を含んでいる。チャネルドープイオン注入によってチャネルドープ層4bに導入される不純物は、例えばリン(P)などのn型の不純物を用いることができる。このチャネルドープイオン注入IM1bでは、nMIS形成領域1Aを覆うフォトレジスト膜RP1bは、イオン注入阻止マスクとして機能するので、nMIS形成領域1Aの半導体基板1には、イオン注入されない。

In the ion implantation IM1b for adjusting the threshold, that is, the channel dope ion implantation IM1b, impurities (impurity ions) are introduced (ion implantation) into a region including the channel region of the p-channel MISFET Qp to form the

次に、pMIS形成領域1Bにおいて、半導体基板1の主面から所定の深さに渡ってn型ウエル(n型半導体領域)NWを形成する。n型ウエルNWは、nMIS形成領域1Aを覆うフォトレジスト膜RP1bをイオン注入阻止マスクとして、pMIS形成領域1Bの半導体基板1に例えばリン(P)などのn型の不純物をイオン注入することなどによって形成することができる。なお、チャネルドープ層4bは、半導体基板1の上層部分に浅く形成され、n型ウエルNWは、半導体基板1において、チャネルドープ層4bよりも深くまで形成されている。また、他の形態として、先にn型ウエルNWをイオン注入で形成してから、チャネルドープイオン注入IM1bによってチャネルドープ層4bを形成することもでき、これは以下の実施の形態2〜4でも同様である。更に他の形態として、先にpMIS形成領域1Bにチャネルドープ層4bおよびn型ウエルNWを形成した後で、nMIS形成領域1Aにチャネルドープ層4aおよびp型ウエルPWを形成することもでき、これは以下の実施の形態2〜4でも同様である。

Next, in the

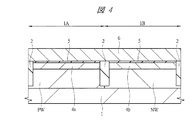

次に、図4に示されるように、アッシングなどによりフォトレジスト膜RP1bを除去してから、例えばフッ酸(HF)水溶液を用いたウェットエッチングなどにより上記絶縁膜3を除去して半導体基板1の表面を清浄化(洗浄)した後、nMIS形成領域1AおよびpMIS形成領域1Bの半導体基板1の表面(主面、ここではp型ウエルPWおよびn型ウエルNWの表面)上にゲート絶縁膜用の絶縁膜(第1絶縁膜)5を形成する。この絶縁膜5は、後でnチャネル型MISFETQnおよびpチャネル型MISFETQpのゲート絶縁膜となる。絶縁膜5は、例えば薄い酸化シリコン膜などからなり、例えば熱酸化法などによって形成することができる。

Next, as shown in FIG. 4, after removing the photoresist film RP <b> 1 b by ashing or the like, the insulating

次に、半導体基板1の主面全面上(すなわちnMIS形成領域1AおよびpMIS形成領域1Bの絶縁膜5上を含む)に、ゲート電極形成用の導電体膜として、多結晶シリコン膜のようなシリコン膜6を形成する。シリコン膜6のうちのnMIS形成領域1A(後述するゲート電極GE1となる領域)は、フォトレジスト膜(図示せず)をマスクとして用いてリン(P)またはヒ素(As)などのn型の不純物をイオン注入することなどにより、低抵抗のn型半導体膜(ドープトポリシリコン膜)とされている。また、シリコン膜6のうちのpMIS形成領域1B(後述するゲート電極GE2となる領域)は、他のフォトレジスト膜(図示せず)をマスクとして用いてホウ素(B)などのp型の不純物をイオン注入することなどにより、低抵抗のp型半導体膜(ドープトポリシリコン膜)とされている。また、シリコン膜6は、成膜時にはアモルファスシリコン膜であったものを、成膜後(イオン注入後)の熱処理により多結晶シリコン膜に変えることもできる。

Next, on the entire main surface of the semiconductor substrate 1 (that is, on the insulating

次に、図5に示されるように、シリコン膜6をフォトリソグラフィ法およびドライエッチング法を用いてパターニングすることにより、ゲート電極GE1,GE2を形成する。

Next, as shown in FIG. 5, the

nチャネル型MISFETQnのゲート電極となるゲート電極GE1は、n型の不純物を導入した多結晶シリコン(n型半導体膜、ドープトポリシリコン膜)からなり、nMIS形成領域1Aのp型ウエルPW(の上部のチャネルドープ層4a)上に絶縁膜5を介して形成される。ゲート電極GE1の下に残存する絶縁膜5が、nチャネル型MISFETQnのゲート絶縁膜5aとなる。すなわち、ゲート電極GE1は、nMIS形成領域1Aの絶縁膜5(すなわちゲート絶縁膜5a)上に形成される。また、pチャネル型MISFETQpのゲート電極となるゲート電極GE2は、p型の不純物を導入した多結晶シリコン(p型半導体膜、ドープトポリシリコン膜)からなり、pMIS形成領域1Bのn型ウエルNW(の上部のチャネルドープ層4b)上に絶縁膜5を介して形成される。ゲート電極GE2の下に残存する絶縁膜5が、pチャネル型MISFETQpのゲート絶縁膜5bとなる。すなわち、ゲート電極GE2は、pMIS形成領域1Bの絶縁膜5(すなわちゲート絶縁膜5b)上に形成される。

The gate electrode GE1 serving as the gate electrode of the n-channel type MISFET Qn is made of polycrystalline silicon (n-type semiconductor film, doped polysilicon film) into which an n-type impurity is introduced, and the p-type well PW (of the

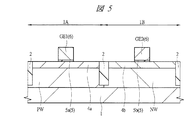

次に、図6に示されるように、pMIS形成領域1Bを覆うフォトレジスト膜(フォトレジストパターン)RP2aを、フォトリソグラフィ技術を用いて形成する。nMIS形成領域1Aは、このフォトレジスト膜RP2aでは覆われずに露出される。このフォトレジスト膜RP2aは、pMIS形成領域1Bへのイオン注入阻止マスクとして機能することができる。このため、後述するイオン注入IM2a,IM3a,IM4aでは、フォトレジスト膜RP2aがイオン注入阻止マスクとして機能し、pMIS形成領域1Bの半導体基板1にはイオン注入されない。

Next, as shown in FIG. 6, a photoresist film (photoresist pattern) RP2a covering the

次に、nMIS形成領域1Aの半導体基板1(p型ウエルPW)のゲート電極GE1の両側の領域に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、(一対の)エクステンション領域(第1半導体領域、ソース・ドレインエクステンション領域、n−型半導体領域)7aを形成する。エクステンション領域7aはn型の半導体領域であり、後で形成するn+型半導体領域11aよりも不純物濃度が低い。なお、図6では、エクステンション領域7aを形成するためのイオン注入IM2aを矢印で模式的に示してある。このイオン注入IM2aの際、ゲート電極GE1もマスク(イオン注入阻止マスク)として機能することができるので、エクステンション領域7aは、ゲート電極GE1(の側壁)に整合して形成され、ゲート電極GE1の直下には、不純物は導入(イオン注入)されない。エクステンション領域7aの深さ(接合深さ)は、後で形成されるn+型半導体領域11aの深さ(接合深さ)よりも浅い。また、エクステンション領域7a形成のためのイオン注入IM2aは、斜めイオン注入ではなく、半導体基板1の主面に対して垂直な方向にイオン注入することが好ましい。

Next, n-type impurities such as phosphorus (P) or arsenic (As) are ion-implanted into regions on both sides of the gate electrode GE1 of the semiconductor substrate 1 (p-type well PW) in the

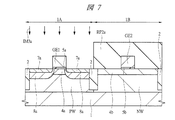

次に、図7に示されるように、nMIS形成領域1Aの半導体基板1(p型ウエルPW)にp型不純物のイオン注入(ハローイオン注入)IM3aを行ってハロー領域(p型半導体領域)8aを形成する。なお、図7では、ハロー領域8aを形成するためのイオン注入(ハローイオン注入)IM3aを矢印で模式的に示してある。ハロー領域8aは、エクステンション領域7aとは逆の導電型で、かつp型ウエルPWとは同じ導電型であり、ここではp型(p型の半導体領域)である。ハロー領域8aは、短チャネル特性抑制のために形成される。ハロー領域8aを形成するためのイオン注入IM3aの際、ゲート電極GE1もマスク(イオン注入阻止マスク)として機能することができる。ハロー領域8aは、エクステンション領域7aを包み込む(覆う)ように形成され、p型ウエルPWよりも不純物濃度(p型不純物濃度)が高い。ハロー領域8aを形成するためのイオン注入IM3aは、斜めイオン注入(傾斜イオン注入)とすることがより好ましく、これにより、エクステンション領域7aを包み込む(覆う)ようにハロー領域8aを的確に形成することができる。なお、一般のイオン注入では、半導体基板1の主面に対して垂直な方向に不純物イオンを加速して打ち込むが、斜めイオン注入では、半導体基板1の主面に対して垂直な方向から所定の角度(傾斜角)傾斜した方向に不純物イオンを加速して打ち込む。

Next, as shown in FIG. 7, p-type impurity ion implantation (halo ion implantation) IM3a is performed on the semiconductor substrate 1 (p-type well PW) in the

次に、図8に示されるように、nMIS形成領域1Aの半導体基板1(p型ウエルPW)に第1元素のイオン注入IM4aを行って拡散防止領域10aを形成する。なお、図8では、拡散防止領域10aを形成するためのイオン注入IM4aを矢印で模式的に示してある。このイオン注入IM4aの際、ゲート電極GE1もマスク(イオン注入阻止マスク)として機能することができる。拡散防止領域10aは、第1元素が導入(ドープ)された領域である。拡散防止領域10aを形成するためのイオン注入IM4aで半導体基板1に注入される第1元素は、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上からなる。拡散防止領域10aにおける第1元素の濃度は、イオン注入IM4aの注入量(ドーズ量)で例えば5×1014〜5×1015/cm2程度、体積濃度で例えば1×1018〜1×1020/cm3程度とすることができる。

Next, as shown in FIG. 8, the

拡散防止領域10aは、エクステンション領域7a、ハロー領域8a、および後述のn+型半導体領域11aを形成する際のイオン注入で生成された点欠陥が、nチャネル型MISFETQnのチャネル領域に拡散するのを防止する機能を有している。このため、拡散防止領域10aは、その少なくとも一部が、エクステンション領域7a、ハロー領域8a、および後述のn+型半導体領域11aと、nチャネル型MISFETQnのチャネル領域との間に位置する必要がある。従って、ハロー領域8aを包み込む(覆う)ように拡散防止領域10aを形成することが好ましい。

The

このため、拡散防止領域10a形成のためのイオン注入IM4aでは、ハロー領域8aよりも深い位置に上記第1元素をイオン注入することが好ましい。また、拡散防止領域10a形成のためのイオン注入IM4aは、斜めイオン注入(傾斜イオン注入)とすることが好ましい。これにより、ハロー領域8aとnチャネル型MISFETQnのチャネル領域との間に拡散防止領域10aを的確に位置させることができるようになる。

For this reason, in the ion implantation IM4a for forming the

また、拡散防止領域10aを形成するためのイオン注入IM4aの傾斜角を、ハロー領域8aを形成するためのイオン注入IM3aの傾斜角よりも大きくすれば、更に好ましい。これにより、ハロー領域8aとnチャネル型MISFETQnのチャネル領域との間に拡散防止領域10aを更に的確に位置させることができるようになる。ここで、イオン注入の傾斜角とは、イオン注入方向の半導体基板1の主面に垂直な方向からの傾斜角に対応し、半導体基板1の主面に垂直な方向に不純物イオンを打ち込む場合は、傾斜角は0°である。

Further, it is more preferable that the inclination angle of the ion implantation IM4a for forming the

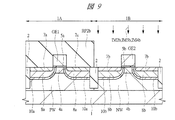

次に、図9に示されるように、アッシングなどによりフォトレジスト膜RP2aを除去してから、nMIS形成領域1Aを覆うフォトレジスト膜(フォトレジストパターン)RP2bを、フォトリソグラフィ技術を用いて形成する。pMIS形成領域1Bは、このフォトレジスト膜RP2bでは覆われずに露出される。このフォトレジスト膜RP2bは、nMIS形成領域1Aへのイオン注入阻止マスクとして機能することができる。このため、後述するイオン注入IM2b,IM3b,IM4bでは、フォトレジスト膜RP2bがイオン注入阻止マスクとして機能し、nMIS形成領域1Aの半導体基板1にはイオン注入されない。

Next, as shown in FIG. 9, after removing the photoresist film RP2a by ashing or the like, a photoresist film (photoresist pattern) RP2b covering the

次に、pMIS形成領域1Bの半導体基板1(n型ウエルNW)のゲート電極GE2の両側の領域に、ホウ素(B)などのp型の不純物をイオン注入することにより、(一対の)エクステンション領域(第1半導体領域、ソース・ドレインエクステンション領域、p−型半導体領域)7bを形成する。エクステンション領域7bはp型の半導体領域であり、後で形成するp+型半導体領域11bよりも不純物濃度が低い。なお、エクステンション領域7bを形成するためのイオン注入IM2bと、後述するハロー領域8bを形成するためのイオン注入IM3bと、後述する拡散防止領域10bを形成するためのイオン注入IM4bとは、それぞれ別々のイオン注入工程として行なわれるが、図9では、まとめて矢印で模式的に示してある。

Next, a p-type impurity such as boron (B) is ion-implanted into regions on both sides of the gate electrode GE2 of the semiconductor substrate 1 (n-type well NW) in the

エクステンション領域7bを形成するためのイオン注入IM2bでは、ゲート電極GE2もマスク(イオン注入阻止マスク)として機能することができるので、エクステンション領域7bは、ゲート電極GE2(の側壁)に整合して形成され、ゲート電極GE2の直下には、不純物は導入(イオン注入)されない。エクステンション領域7bの深さ(接合深さ)は、後で形成されるp+型半導体領域11bの深さ(接合深さ)よりも浅い。また、エクステンション領域7b形成のためのイオン注入IM2bは、斜めイオン注入ではなく、半導体基板1の主面に対して垂直な方向にイオン注入することが好ましい。

In the ion implantation IM2b for forming the

次に、pMIS形成領域1Bの半導体基板1(n型ウエルNW)にn型不純物のイオン注入(ハローイオン注入)IM3bを行ってハロー領域(n型半導体領域)8bを形成する。ハロー領域8bは、エクステンション領域7bとは逆の導電型で、かつn型ウエルNWとは同じ導電型であり、ここではn型(n型の半導体領域)である。ハロー領域8bは、短チャネル特性抑制のために形成される。ハロー領域8bを形成するためのイオン注入IM3bの際、ゲート電極GE2もマスク(イオン注入阻止マスク)として機能することができる。ハロー領域8bは、エクステンション領域7bを包み込む(覆う)ように形成され、n型ウエルNWよりも不純物濃度(n型不純物濃度)が高い。ハロー領域8bを形成するためのイオン注入IM3bは、斜めイオン注入(傾斜イオン注入)とすることがより好ましく、これにより、エクステンション領域7bを包み込む(覆う)ようにハロー領域8bを的確に形成することができる。

Next, n-type impurity ion implantation (halo ion implantation) IM3b is performed on the semiconductor substrate 1 (n-type well NW) in the

次に、pMIS形成領域1Bの半導体基板1(n型ウエルNW)に第1元素のイオン注入IM4bを行って拡散防止領域10bを形成する。拡散防止領域10bは、第1元素が導入(ドープ)された領域である。このイオン注入IM4bの際、ゲート電極GE2もマスク(イオン注入阻止マスク)として機能することができる。拡散防止領域10bを形成するためのイオン注入IM4bで注入される第1元素は、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上からなる。拡散防止領域10bにおける第1元素の濃度は、イオン注入IM4bの注入量(ドーズ量)で例えば5×1014〜5×1015/cm2程度、体積濃度で例えば1×1018〜1×1020/cm3程度とすることができる。

Next, a first element ion implantation IM4b is performed on the semiconductor substrate 1 (n-type well NW) in the

拡散防止領域10bは、エクステンション領域7b、ハロー領域8b、および後述のp+型半導体領域11bを形成する際のイオン注入で生成された点欠陥が、pチャネル型MISFETQpのチャネル領域に拡散するのを防止する機能を有している。このため、拡散防止領域10bは、その少なくとも一部が、エクステンション領域7b、ハロー領域8b、および後述のp+型半導体領域11bと、pチャネル型MISFETQpのチャネル領域との間に位置する必要がある。従って、ハロー領域8bを包み込む(覆う)ように拡散防止領域10bを形成することが好ましい。

The

このため、拡散防止領域10b形成のためのイオン注入IM4bでは、ハロー領域8bよりも深い位置に上記第1元素をイオン注入することが好ましい。また、拡散防止領域10b形成のためのイオン注入IM4bは、斜めイオン注入(傾斜イオン注入)とすることが好ましい。これにより、ハロー領域8bとnチャネル型MISFETQpのチャネル領域との間に拡散防止領域10bを的確に位置させることができるようになる。

For this reason, in the ion implantation IM4b for forming the

また、拡散防止領域10bを形成するためのイオン注入IM4bの傾斜角を、ハロー領域8bを形成するためのイオン注入の傾斜角よりも大きくすれば、更に好ましい。これにより、ハロー領域8bとpチャネル型MISFETQpのチャネル領域との間に拡散防止領域10bを更に的確に位置させることができるようになる。

It is further preferable that the inclination angle of the ion implantation IM4b for forming the

また、他の形態として、先にpMIS形成領域1Bにエクステンション領域7b、ハロー領域8bおよび拡散防止領域10bを形成してから、nMIS形成領域1Aにエクステンション領域7a、ハロー領域8aおよび拡散防止領域10aを形成することもでき、これは以下の実施の形態2〜4でも同様である。

As another form, after the

また、ハロー領域8a,8bは、短チャネル特性抑制のために形成することが好ましいが、不要であればその形成を省略することもでき、これは以下の実施の形態2〜4でも同様である。

The

また、エクステンション領域7a、ハロー領域8aおよび拡散防止領域10aは、必ずしもこの順序で形成しなくともよいが、エクステンション領域7a、ハロー領域8aおよび拡散防止領域10aを形成する各イオン注入IM2a,IM3a,IM4aは、少なくとも、ゲート電極GE1形成後で、かつ、ゲート電極GE1の側壁上に後述のサイドウォールSWを形成する前に行う必要がある。同様に、エクステンション領域7b、ハロー領域8bおよび拡散防止領域10bは、必ずしもこの順序で形成しなくともよいが、エクステンション領域7b、ハロー領域8bおよび拡散防止領域10bを形成する各イオン注入IM2b,IM3b,IM4bは、少なくとも、ゲート電極GE2形成後で、かつ、ゲート電極GE2の側壁上に後述のサイドウォールSWを形成する前に行う必要がある。

Further, the

次に、図10に示されるように、アッシングなどによりフォトレジスト膜RP2bを除去してから、ゲート電極GE1,GE2の側壁上に、絶縁膜(側壁絶縁膜)として、例えば酸化シリコンまたは窒化シリコンあるいはそれら絶縁膜の積層膜などからなる側壁スペーサまたはサイドウォール(側壁絶縁膜、サイドウォールスペーサ)SWを形成する。サイドウォールSWは、例えば、半導体基板1(の主面全面)上に酸化シリコン膜または窒化シリコン膜あるいはそれらの積層膜を堆積し、この酸化シリコン膜または窒化シリコン膜あるいはそれらの積層膜をRIE(Reactive Ion Etching:反応性イオンエッチング)法などにより異方性エッチングすることによって形成することができる。 Next, as shown in FIG. 10, after removing the photoresist film RP2b by ashing or the like, as an insulating film (sidewall insulating film) on the side walls of the gate electrodes GE1 and GE2, for example, silicon oxide or silicon nitride or Sidewall spacers or sidewalls (sidewall insulating films, sidewall spacers) SW made of a laminated film of these insulating films are formed. For example, the sidewall SW is formed by depositing a silicon oxide film, a silicon nitride film, or a laminated film thereof on the semiconductor substrate 1 (entire main surface thereof), and depositing the silicon oxide film, the silicon nitride film, or the laminated film thereof by RIE ( Reactive Ion Etching (reactive ion etching) can be formed by anisotropic etching.

次に、図11に示されるように、pMIS形成領域1Bを覆うフォトレジスト膜(フォトレジストパターン)RP3aを、フォトリソグラフィ技術を用いて形成する。nMIS形成領域1Aは、このフォトレジスト膜RP3aでは覆われずに露出される。このフォトレジスト膜RP3aは、pMIS形成領域1Bへのイオン注入阻止マスクとして機能することができる。このため、後述するイオン注入IM5aでは、フォトレジスト膜RP3aがイオン注入阻止マスクとして機能し、pMIS形成領域1Bの半導体基板1にはイオン注入されない。

Next, as shown in FIG. 11, a photoresist film (photoresist pattern) RP3a covering the

次に、nMIS形成領域1Aの半導体基板1(p型ウエルPW)のゲート電極GE1およびサイドウォールSWの両側の領域に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、(一対の)n+型半導体領域11a(ソース、ドレイン)を形成する。なお、図11では、n+型半導体領域11aを形成するためのイオン注入IM5aを矢印で模式的に示してある。このイオン注入IM5aの際、ゲート電極GE1およびその側壁上のサイドウォールSWもマスク(イオン注入阻止マスク)として機能することができるので、n+型半導体領域11aは、ゲート電極GE1の側壁上のサイドウォールSW(の側壁)に整合して形成され、ゲート電極GE1およびサイドウォールSWの直下には、不純物は導入(イオン注入)されない。n+型半導体領域11aの深さ(接合深さ)は、エクステンション領域7aの深さ(接合深さ)よりも深い。

Next, an n-type impurity such as phosphorus (P) or arsenic (As) is ion-implanted into regions on both sides of the gate electrode GE1 and the sidewall SW of the semiconductor substrate 1 (p-type well PW) in the

n+型半導体領域(第2半導体領域)11aとエクステンション領域(第1半導体領域)7aとは同じ導電型であるが、n+型半導体領域11aは、エクステンション領域7aよりも、不純物濃度(n型不純物濃度)が高い。これにより、nチャネル型MISFETQnのソースまたはドレインとして機能するn型の半導体領域(不純物拡散層)が、n+型半導体領域(不純物拡散層)11aおよびエクステンション領域(n−型半導体領域)7aにより形成される。換言すれば、エクステンション領域7aと、それよりも高不純物濃度のn+型半導体領域11aとは、nチャネル型MISFETQnのソースまたはドレイン用の半導体領域として機能する。従って、nチャネル型MISFETQnのソース・ドレイン領域は、LDD(Lightly doped Drain)構造を有している。上述のように、エクステンション領域7aは、ゲート電極GE1に対して自己整合的に形成され、n+型半導体領域11aは、ゲート電極GE1の側壁上に形成されたサイドウォールSWに対して自己整合的に形成される。

The n + type semiconductor region (second semiconductor region) 11a and the extension region (first semiconductor region) 7a have the same conductivity type, but the n +

また、サイドウォールSWの形成後、n+型半導体領域11a形成用のイオン注入の前または後に、半導体基板1に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上からなる第1元素をイオン注入することもできる。この場合、このイオン注入で第1元素が注入された領域が、n+型半導体領域11aを包み込む(覆う)ようにすることが好ましい。これにより、n+型半導体領域11aに生成された点欠陥が、nチャネル型MISFETQnのチャネル領域に拡散するのを、更に的確に防止することができる。

In addition, after forming the sidewall SW, before or after ion implantation for forming the n + -

次に、図12に示されるように、アッシングなどによりフォトレジスト膜RP3aを除去してから、nMIS形成領域1Aを覆うフォトレジスト膜(フォトレジストパターン)RP3bを、フォトリソグラフィ技術を用いて形成する。pMIS形成領域1Bは、このフォトレジスト膜RP3bでは覆われずに露出される。このフォトレジスト膜RP3bは、nMIS形成領域1Aへのイオン注入阻止マスクとして機能することができる。このため、後述するイオン注入IM5bでは、フォトレジスト膜RP3bがイオン注入阻止マスクとして機能し、nMIS形成領域1Aの半導体基板1にはイオン注入されない。

Next, as shown in FIG. 12, after removing the photoresist film RP3a by ashing or the like, a photoresist film (photoresist pattern) RP3b covering the

次に、pMIS形成領域1Bの半導体基板1(n型ウエルNW)のゲート電極GE2およびサイドウォールSWの両側の領域に、ホウ素(B)などのp型の不純物をイオン注入することにより、(一対の)p+型半導体領域11b(ソース、ドレイン)を形成する。なお、図12では、p+型半導体領域11bを形成するためのイオン注入IM5bを矢印で模式的に示してある。このイオン注入IM5bの際、ゲート電極GE2およびその側壁上のサイドウォールSWもマスク(イオン注入阻止マスク)として機能することができるので、p+型半導体領域11bは、ゲート電極GE2の側壁上のサイドウォールSW(の側壁)に整合して形成され、ゲート電極GE2およびサイドウォールSWの直下には、不純物は導入(イオン注入)されない。p+型半導体領域11bの深さ(接合深さ)は、エクステンション領域7bの深さ(接合深さ)よりも深い。

Next, a p-type impurity such as boron (B) is ion-implanted into regions on both sides of the gate electrode GE2 and the side wall SW of the semiconductor substrate 1 (n-type well NW) in the

p+型半導体領域(第2半導体領域)11bとエクステンション領域(第1半導体領域)7bとは同じ導電型であるが、p+型半導体領域11bは、エクステンション領域7bよりも、不純物濃度(p型不純物濃度)が高い。これにより、pチャネル型MISFETQpのソースまたはドレインとして機能するp型の半導体領域(不純物拡散層)が、p+型半導体領域(不純物拡散層)11bおよびエクステンション領域(p−型半導体領域)7bにより形成される。換言すれば、エクステンション領域7bと、それよりも高不純物濃度のp+型半導体領域11bとは、pチャネル型MISFETQpのソースまたはドレイン用の半導体領域として機能する。従って、pチャネル型MISFETQpのソース・ドレイン領域は、LDD構造を有している。上述のように、エクステンション領域7bは、ゲート電極GE2に対して自己整合的に形成され、p+型半導体領域11bは、ゲート電極GE2の側壁上に形成されたサイドウォールSWに対して自己整合的に形成される。

The p + type semiconductor region (second semiconductor region) 11b and the extension region (first semiconductor region) 7b have the same conductivity type, but the impurity concentration (p type) of the p +

また、サイドウォールSWの形成後、p+型半導体領域11b形成用のイオン注入の前または後に、半導体基板1に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上からなる第1元素をイオン注入することもできる。この場合、このイオン注入で第1元素が注入された領域が、p+型半導体領域11bを包み込む(覆う)ようにすることが好ましい。これにより、p+型半導体領域11bに生成された点欠陥が、pチャネル型MISFETQpのチャネル領域に拡散するのを、更に的確に防止することができる。

In addition, after forming the sidewall SW, before or after ion implantation for forming the p + -

また、他の形態として、先にpMIS形成領域1Bにp+型半導体領域11bを形成してから、nMIS形成領域1Aにn+型半導体領域11aを形成することもでき、これは以下の実施の形態2〜4でも同様である。

As another form, after forming the p +

次に、アッシングなどによりフォトレジスト膜RP3bを除去する。それから、これまでのイオン注入で導入した不純物の活性化のためのアニール処理(熱処理)を行う。このアニール処理は、例えば1050℃程度のスパイクアニール処理にて行うことができる。 Next, the photoresist film RP3b is removed by ashing or the like. Then, annealing treatment (heat treatment) for activating the impurities introduced by the conventional ion implantation is performed. This annealing process can be performed, for example, by a spike annealing process at about 1050 ° C.

このようにして、nMIS形成領域1A(のp型ウエルPW)に、電界効果トランジスタとしてnチャネル型MISFET(Metal Insulator Semiconductor Field Effect Transistor)Qnが形成される。また、pMIS形成領域1B(のn型ウエルNW)に、電界効果トランジスタとしてpチャネル型MISFET(Metal Insulator Semiconductor Field Effect Transistor)Qpが形成される。これにより、図13の構造が得られる。nチャネル型MISFETQnは、nチャネル型の電界効果トランジスタとみなすことができ、pチャネル型MISFETQpは、pチャネル型の電界効果トランジスタとみなすことができる。

In this manner, an n-channel MISFET (Metal Insulator Semiconductor Field Effect Transistor) Qn is formed as a field effect transistor in the

次に、ゲート電極GE1,GE2、n+型半導体領域11aおよびp+型半導体領域11bの表面を露出させ、例えばコバルト(Co)膜またはニッケル(Ni)のような金属膜を堆積して熱処理することによって、図14に示されるように、ゲート電極GE1,GE2、n+型半導体領域11aおよびp+型半導体領域11bの表面に、それぞれ金属シリサイド層12を形成する。これにより、n+型半導体領域11aおよびp+型半導体領域11bの拡散抵抗やコンタクト抵抗などを低抵抗化することができる。その後、未反応の金属膜は除去する。

Next, the surfaces of the gate electrodes GE1, GE2, the n +

次に、半導体基板1の主面上に絶縁膜21を形成する。すなわち、ゲート電極GE1,GE2を覆うように、金属シリサイド層12上を含む半導体基板1上に絶縁膜21を形成する。絶縁膜21は例えば窒化シリコン膜からなり、プラズマCVD法などを用いて形成することができる。それから、絶縁膜21上に絶縁膜21よりも厚い絶縁膜22を形成する。絶縁膜22は例えば酸化シリコン膜などからなり、TEOS(Tetraethoxysilane:テトラエトキシシラン、またはTetra Ethyl Ortho Silicateとも言う)を用いてプラズマCVD法などにより形成することができる。これにより、絶縁膜21,22からなる層間絶縁膜が形成される。その後、絶縁膜22の表面をCMP法により研磨するなどして、絶縁膜22の上面を平坦化する。下地段差に起因して絶縁膜21の表面に凹凸形状が形成されていても、絶縁膜22の表面をCMP法により研磨することにより、その表面が平坦化された層間絶縁膜を得ることができる。

Next, an insulating

次に、絶縁膜22上に形成したフォトレジストパターン(図示せず)をエッチングマスクとして用いて、絶縁膜22,21をドライエッチングすることにより、絶縁膜22,21にコンタクトホール(貫通孔、孔)23を形成する。この際、まず絶縁膜21に比較して絶縁膜22がエッチングされやすい条件で絶縁膜22のドライエッチングを行い、絶縁膜21をエッチングストッパ膜として機能させることで、絶縁膜22にコンタクトホール23を形成してから、絶縁膜22に比較して絶縁膜21がエッチングされやすい条件でコンタクトホール23の底部の絶縁膜21をドライエッチングして除去する。コンタクトホール23の底部では、半導体基板1の主面の一部、例えばn+型半導体領域11aおよびp+型半導体領域11bの表面上の金属シリサイド層12の一部や、ゲート電極GE1,GE2の表面上の金属シリサイド層12の一部などが露出される。

Next, by using the photoresist pattern (not shown) formed on the insulating

次に、コンタクトホール23内に、タングステン(W)などからなるプラグ(接続用導体部)24を形成する。プラグ24を形成するには、例えば、コンタクトホール23の内部(底部および側壁上)を含む絶縁膜22上に、プラズマCVD法によりバリア導体膜24a(例えばチタン膜、窒化チタン膜、あるいはそれらの積層膜)を形成する。それから、タングステン膜などからなる主導体膜24bをCVD法などによってバリア導体膜24a上にコンタクトホール23を埋めるように形成し、絶縁膜22上の不要な主導体膜24bおよびバリア導体膜24aをCMP法またはエッチバック法などによって除去することにより、プラグ24を形成することができる。ゲート電極GE1,GE2、n+型半導体領域11aまたはp+型半導体領域11b上に形成されたプラグ24は、その底部でゲート電極GE1,GE2、n+型半導体領域11aまたはp+型半導体領域11bの表面上の金属シリサイド層12と接して、電気的に接続される。

Next, a plug (connecting conductor portion) 24 made of tungsten (W) or the like is formed in the

次に、図15に示されるように、プラグ24が埋め込まれた絶縁膜22上に、ストッパ絶縁膜25および配線形成用の絶縁膜26を順次形成する。ストッパ絶縁膜25は絶縁膜26への溝加工の際にエッチングストッパとなる膜であり、絶縁膜26に対してエッチング選択比を有する材料を用いる。ストッパ絶縁膜25は、例えばプラズマCVD法により形成される窒化シリコン膜とし、絶縁膜26は、例えばプラズマCVD法により形成される酸化シリコン膜とすることができる。なお、ストッパ絶縁膜25と絶縁膜26には、次に説明する第1層目の配線が形成される。

Next, as shown in FIG. 15, a

次に、シングルダマシン法により第1層目の配線を形成する。まず、フォトレジストパターン(図示せず)をマスクとしたドライエッチングによって絶縁膜26およびストッパ絶縁膜25の所定の領域に配線溝27を形成した後、半導体基板1の主面上(すなわち配線溝27の底部および側壁上を含む絶縁膜26上)にバリア導体膜(バリアメタル膜)28を形成する。バリア導体膜28は、例えば窒化チタン膜、タンタル膜または窒化タンタル膜などを用いることができる。続いて、CVD法またはスパッタリング法などによりバリア導体膜28上に銅のシード層を形成し、さらに電解めっき法などを用いてシード層上に銅めっき膜を形成して、銅めっき膜により配線溝27の内部を埋め込む。図15では、シード膜および銅めっき膜を合わせたものを銅の主導体膜29として図示している。それから、配線溝27以外の領域の主導体膜29(銅めっき膜およびシード層)とバリアメタル膜28をCMP法により除去して、配線溝27に埋め込まれ銅を主導電材料とする第1層目の配線M1を形成する。配線M1は、プラグ24を介してnチャネル型MISFETQnおよびpチャネル型MISFETQpのソースまたはドレイン用のn+型半導体領域11aおよびp+型半導体領域11bやゲート電極GE1,GE2などと電気的に接続されている。その後、デュアルダマシン法により2層目の配線を形成するが、ここでは図示およびその説明は省略する。

Next, a first layer wiring is formed by a single damascene method. First, after forming a

次に、本実施の形態の効果について、より詳細に説明する。 Next, the effect of this embodiment will be described in more detail.

半導体基板に不純物をイオン注入した場合、注入直後の段階では、注入された不純物はランダムに配置されているが、その後の種々の加熱工程で不純物が拡散(移動)すると、不純物のランダム配置が崩れ、注入直後に比べて不純物の分布に偏りが生じてしまう。すなわち、イオン注入した直後の段階では、注入した不純物の配置のランダム性が高いが、その後の種々の加熱工程で不純物が拡散(移動)すると、不純物の配置のランダム性が低下してしまう。このことは、イオン注入が、MISFETのしきい値調整用のチャネルドープイオン注入である場合でも同様である。従って、チャネルドープイオン注入した直後の段階では、チャネル領域にドープされた不純物の配置のランダム性が高いが、その後の種々の加熱工程で不純物が拡散(移動)すると、チャネル領域にドープされた不純物の配置のランダム性が低下してしまう。 When an impurity is ion-implanted into a semiconductor substrate, the implanted impurity is randomly arranged at the stage immediately after the implantation. However, when the impurity diffuses (moves) in various subsequent heating processes, the random arrangement of the impurity is destroyed. As a result, the distribution of impurities is biased compared to immediately after the implantation. That is, in the stage immediately after ion implantation, the randomness of the arrangement of implanted impurities is high, but if the impurities diffuse (move) in various subsequent heating steps, the randomness of the arrangement of impurities deteriorates. This is the same even when the ion implantation is channel doping ion implantation for adjusting the threshold value of the MISFET. Accordingly, in the stage immediately after channel doping ion implantation, the arrangement of impurities doped in the channel region is highly random, but when the impurities diffuse (move) in various subsequent heating processes, the impurities doped in the channel region The randomness of the arrangement of will be reduced.

なお、不純物の配置のランダム性が高い状態では、微視的(原子配列のレベル)には、不純物は均一(規則的)に配置されているのではなく、ばらばら(ランダム)に存在しているが、微視的にランダムであるが故に、巨視的(チャネル領域のレベル)には、不純物は偏りなく同じように分布している。このため、不純物の配置のランダム性が高い状態では、チャネル領域同士を比べたときの不純物分布の違い(あるMISFETのチャネル領域の不純物分布と他のMISFETのチャネル領域の不純物分布との差)が小さく、MISFETのしきい値のばらつきが小さい。 In addition, in a state where the randomness of the arrangement of impurities is high, the impurities are not arranged uniformly (regularly) microscopically (at the level of atomic arrangement) but are present in a random (random) manner. However, since they are microscopically random, the impurities are distributed equally in a macroscopic manner (channel region level). For this reason, in a state where the randomness of the impurity arrangement is high, the difference in impurity distribution (difference between the impurity distribution in the channel region of one MISFET and the impurity distribution in the channel region of another MISFET) when the channel regions are compared with each other. Small, variation in threshold of MISFET is small.

しかしながら、不純物配置のランダム性が低下すると、この状態が崩れ、巨視的な不純物の分布(チャネル領域のレベルでの不純物分布)に偏りが生じてしまう。このため、チャネルドープイオン注入後に、熱拡散によってチャネルドープ不純物の配置のランダム性が低くなった状態では、チャネル領域同士を比べたときの不純物分布の違い(あるMISFETのチャネル領域の不純物分布と他のMISFETのチャネル領域の不純物分布との差)が大きくなり、MISFETのしきい値のばらつきが大きくなってしまう。すなわち、MISFET毎にチャネル領域の状態(チャネル領域における不純物の配置状態)が変動してしまい、MISFET毎にしきい値電圧が変動してしまうのである。半導体装置の性能を向上させるためには、MISFET毎のしきい値電圧のばらつきを抑制することが望まれる。 However, if the randomness of the impurity arrangement decreases, this state collapses, and the macroscopic impurity distribution (impurity distribution at the channel region level) is biased. For this reason, after the channel doping ion implantation, in the state where the randomness of the channel doping impurities is reduced by thermal diffusion, the difference in the impurity distribution when comparing the channel regions (impurity distribution in the channel region of a certain MISFET and others) (Difference from the impurity distribution in the channel region of the MISFET) increases, and the variation in threshold value of the MISFET increases. That is, the state of the channel region (arrangement state of impurities in the channel region) varies for each MISFET, and the threshold voltage varies for each MISFET. In order to improve the performance of the semiconductor device, it is desired to suppress variations in threshold voltage for each MISFET.

このため、チャネルドープイオン注入で導入された不純物が、その後の加熱工程の際に再配置(拡散)されるのをできるだけ抑制して、注入直後のチャネルドープ不純物の配置(ランダム性が高い配置)を注入後もできるだけ維持することが、MISFET毎のしきい値電圧のばらつきを抑制するために重要である。 For this reason, it is possible to suppress as much as possible the impurities introduced in the channel doping ion implantation from being rearranged (diffused) during the subsequent heating process, and to arrange the channel doped impurities immediately after the implantation (arrangement with high randomness). It is important to maintain as much as possible after the implantation in order to suppress variation in threshold voltage for each MISFET.

また、半導体基板1にイオン注入を行なうと、半導体基板1の不純物イオンがドープされた領域に点欠陥も生成されてしまうが、点欠陥は拡散しやすい。このため、エクステンション領域7a,7b、ハロー領域8a,8b、n+型半導体領域11aおよびp+型半導体領域11bを形成する際の各イオン注入で生成された点欠陥が、その後の種々の加熱工程でMISFETのチャネル領域(ゲート電極GE1,GE2の直下の領域)にまで拡散してしまう可能性がある。特に、エクステンション領域7a,7bおよびハロー領域8a,8bは、チャネル領域(ゲート電極GE1,GE2の直下の領域)に近いため、イオン注入でエクステンション領域7a,7bおよびハロー領域8a,8bに生成された点欠陥が、チャネル領域にまで拡散しやすい。点欠陥がチャネル領域に拡散すると、チャネル領域における点欠陥の密度が大きくなるが、点欠陥の密度が大きいほど、チャネルドープイオン注入でチャネル領域に導入された不純物が移動(拡散)しやすくなる。これは、点欠陥が多いと、点欠陥を介して不純物が移動(拡散)しやすくなるためである。

Further, when ion implantation is performed on the

このため、チャネルドープイオン注入で導入した不純物が、その後の種々の加熱工程の際に再配置(拡散)されるのをできるだけ抑制するためには、エクステンション領域7a,7b、ハロー領域8a,8b、n+型半導体領域11aおよびp+型半導体領域11bを形成する際の各イオン注入で生成された点欠陥がチャネル領域にまで拡散してしまうのをできるだけ防止し、チャネル領域における点欠陥の密度を抑制することが有効である。

For this reason, in order to suppress as much as possible the impurities introduced by channel dope ion implantation from being rearranged (diffused) during various subsequent heating steps, the

本発明者の検討によれば、単結晶シリコンからなる基板領域(半導体基板1)に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上が導入された領域(本実施の形態の拡散防止領域10a,10bに対応)は、点欠陥が拡散(移動)しにくく、点欠陥の拡散(移動)を防止する機能を有していることが分かった。

According to the study of the present inventor, a region in which at least one of carbon (C), nitrogen (N), and fluorine (F) is introduced into a substrate region (semiconductor substrate 1) made of single crystal silicon (this embodiment) It was found that the

そこで、本実施の形態では、上述のように、nMIS形成領域1Aの半導体基板1(p型ウエルPW)に、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上(すなわち第1元素)をイオン注入して、拡散防止領域10aを形成している。また、上述のように、pMIS形成領域1Bの半導体基板1(n型ウエルNW)に、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上(すなわち第1元素)をイオン注入して、拡散防止領域10bを形成している。

Therefore, in the present embodiment, as described above, one or more of carbon (C), nitrogen (N), and fluorine (F) is applied to the semiconductor substrate 1 (p-type well PW) in the

炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上が導入された領域である拡散防止領域10aは、エクステンション領域7a、ハロー領域8a、およびn+型半導体領域11aを形成する際の各イオン注入で生成された点欠陥が、nチャネル型MISFETQnのチャネル領域(ゲート電極GE1の直下の領域)にまで拡散するのを防止する機能を有している。また、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上が導入された領域である拡散防止領域10bは、エクステンション領域7b、ハロー領域8b、およびp+型半導体領域11bを形成する際の各イオン注入で生成された点欠陥が、pチャネル型MISFETQpのチャネル領域(ゲート電極GE2の直下の領域)にまでに拡散するのを防止する機能を有している。

The

上述の機能を拡散防止領域10aが有するためには、拡散防止領域10aの少なくとも一部が、エクステンション領域7a、ハロー領域8aおよびn+型半導体領域11aと、nチャネル型MISFETQnのチャネル領域(ゲート電極GE1の直下の領域)との間に位置する必要がある。エクステンション領域7a、ハロー領域8aおよびn+型半導体領域11aのうち、ハロー領域8aが最もnチャネル型MISFETQnのチャネル領域に近いため、ハロー領域8aを形成した場合は、拡散防止領域10aの少なくとも一部が、ハロー領域8aとnチャネル型MISFETQnのチャネル領域との間に位置すればよい。このようにするためには、ハロー領域8aを包み込む(覆う)ように拡散防止領域10aを形成することが好ましい。ハロー領域8aの形成を省略した場合は、エクステンション領域7aがチャネル領域に近いので、拡散防止領域10aの少なくとも一部が、エクステンション領域7aとnチャネル型MISFETQnのチャネル領域との間に位置すればよく、このようにするためには、エクステンション領域7aを包み込む(覆う)ように拡散防止領域10aを形成することが好ましい。

In order for the

なお、拡散防止領域10aの少なくとも一部が、ハロー領域8aとnチャネル型MISFETQnのチャネル領域との間に位置する場合には、必然的に、エクステンション領域7aとnチャネル型MISFETQnのチャネル領域との間に拡散防止領域10aの少なくとも一部が位置することになる。このため、ハロー領域8aを形成するか否かにかかわらず、エクステンション領域7aとnチャネル型MISFETQnのチャネル領域との間に拡散防止領域10aの少なくとも一部を位置させ、ハロー領域8aを形成した場合には、ハロー領域8aとnチャネル型MISFETQnのチャネル領域との間に拡散防止領域10aの少なくとも一部が位置するようにすればよい。

When at least a part of the

また、上述の機能を拡散防止領域10bが有するためには、拡散防止領域10bの少なくとも一部が、エクステンション領域7b、ハロー領域8bおよびp+型半導体領域11bと、pチャネル型MISFETQpのチャネル領域(ゲート電極GE2の直下の領域)との間に位置する必要がある。エクステンション領域7b、ハロー領域8bおよびp+型半導体領域11bのうち、ハロー領域8bが最もpチャネル型MISFETQpのチャネル領域に近いため、ハロー領域8bを形成した場合は、拡散防止領域10bの少なくとも一部が、ハロー領域8bとpチャネル型MISFETQpのチャネル領域との間に位置すればよい。このようにするためには、ハロー領域8bを包み込む(覆う)ように拡散防止領域10bを形成することが好ましい。ハロー領域8bの形成を省略した場合は、エクステンション領域7bがチャネル領域に近いので、拡散防止領域10bの少なくとも一部が、エクステンション領域7bとpチャネル型MISFETQpのチャネル領域との間に位置すればよく、このようにするためには、エクステンション領域7bを包み込む(覆う)ように拡散防止領域10bを形成することが好ましい。

Further, in order for the

なお、拡散防止領域10bの少なくとも一部が、ハロー領域8bとpチャネル型MISFETQpのチャネル領域との間に位置する場合には、必然的に、エクステンション領域7bとpチャネル型MISFETQpのチャネル領域との間に拡散防止領域10bの少なくとも一部が位置することになる。このため、ハロー領域8bを形成するか否かにかかわらず、エクステンション領域7bとpチャネル型MISFETQpのチャネル領域との間に拡散防止領域10bの少なくとも一部を位置させ、ハロー領域8bを形成した場合には、ハロー領域8bとpチャネル型MISFETQpのチャネル領域との間に拡散防止領域10bの少なくとも一部が位置するようにすればよい。

When at least a part of the

本実施の形態では、拡散防止領域10a,10bを形成したことで、エクステンション領域7a,7b、ハロー領域8a,8b、n+型半導体領域11aおよびp+型半導体領域11bを形成する際の各イオン注入で生成された点欠陥が、nチャネル型MISFETQnおよびpチャネル型MISFETQpのチャネル領域に拡散するのを防止でき、チャネル領域における点欠陥の密度を抑制することできる。これにより、チャネルドープイオン注入でチャネル領域に導入された不純物が、その後の加熱工程の際に再配置(拡散)されるのを抑制または防止することができるので、注入直後のチャネルドープ不純物の配置(ランダム性が高い配置)を維持することができる。従って、MISFET毎のチャネル領域の状態(不純物分布)のばらつきを抑制して、MISFET毎のしきい値電圧のばらつきを抑制することができ、半導体装置の性能を向上させることができる。

In the present embodiment, since the

また、拡散防止領域10a,10bには、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上が導入されているが、炭素(C)、窒素(N)およびフッ素(F)のうち、点欠陥の拡散防止に最も有効なのは炭素(C)である。このため、拡散防止領域10a,10bには、炭素(C)、窒素(N)またはフッ素(F)のうち少なくとも炭素(C)を導入していればより好ましい。これにより、拡散防止領域10a,10bを設けたことによる上述の効果を、より的確に得ることができる。

In addition, one or more of carbon (C), nitrogen (N), and fluorine (F) are introduced into the

また、本実施の形態では、半導体基板において、必要な領域のみに炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上をイオン注入して拡散防止領域10a,10bを形成することができる。このため、不要な領域に炭素(C)、窒素(N)またはフッ素(F)が導入されることを防止でき、不要な領域に炭素(C)、窒素(N)またはフッ素(F)が導入されることによる悪影響を排除できる。

In this embodiment,

また、チャネルドープイオン注入で導入した不純物の再配置(拡散)に起因したMISFET毎のしきい値電圧のばらつきは、pチャネル型MISFETに比べて、nチャネル型MISFETの方が大きい。これは、一般に、nチャネル型MISFETには、チャネルドープイオン注入でp型不純物を注入し、pチャネル型MISFETには、チャネルドープイオン注入でn型不純物を注入するが、リン(P)などのn型不純物に比べて、ホウ素(B)などのp型不純物の方が、熱拡散しやすいためである。このため、本実施の形態(拡散防止領域10a,10bに相当するものを形成すること)は、CMISFETを有する半導体装置だけでなく、pチャネル型MISFETまたはnチャネル型MISFETの一方だけを有する半導体装置に対しても適用できるが、少なくともnチャネル型MISFETを有する半導体装置に適用すれば、効果が大きい。このこと、以下の実施の形態2〜6においても同様である。

In addition, the variation in threshold voltage for each MISFET due to the rearrangement (diffusion) of impurities introduced by channel doping ion implantation is larger in the n-channel MISFET than in the p-channel MISFET. In general, n-channel MISFETs are implanted with p-type impurities by channel dope ion implantation, and p-channel MISFETs are implanted with n-type impurities by channel dope ion implantation. This is because a p-type impurity such as boron (B) is more easily thermally diffused than an n-type impurity. For this reason, the present embodiment (forming those corresponding to the

(実施の形態2)

本実施の形態2の半導体装置の製造工程を図面を参照して説明する。図16〜図22は、本実施の形態の半導体装置の製造工程中の要部断面図である。

(Embodiment 2)

A manufacturing process of the semiconductor device according to the second embodiment will be described with reference to the drawings. 16 to 22 are main-portion cross-sectional views during the manufacturing process of the semiconductor device of the present embodiment.

本実施の形態では、まず、図16に示されるように、例えば1〜10Ωcm程度の比抵抗を有するp型の単結晶シリコンなどからなる半導体基板(半導体ウエハ)1aを準備し、半導体基板1a(の主面全面)上に半導体層(半導体領域)1bを形成する。 In the present embodiment, first, as shown in FIG. 16, a semiconductor substrate (semiconductor wafer) 1a made of p-type single crystal silicon having a specific resistance of about 1 to 10 Ωcm, for example, is prepared, and the semiconductor substrate 1a ( A semiconductor layer (semiconductor region) 1b is formed on the entire main surface of the substrate.

半導体層1bは、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上(すなわち第1元素)が導入された半導体層(単結晶シリコン層)であり、具体的には、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上(すなわち第1元素)が導入(ドープ)された単結晶シリコン(Si)で構成されている。

The

半導体層1bは、好ましくは、半導体基板1a上に半導体層1bをエピタキシャル成長させることで形成されている。半導体基板1aとその上の半導体層1bとを合わせたものを、半導体基板SUB1と称することとし、この半導体基板SUB1は、いわゆるエピタキシャルウエハとみなすこともできる。半導体基板SUB1の主面(表面)は、半導体層1bの主面(表面)に対応する。半導体層1bにおける第1元素の濃度は、例えば1×1018〜1×1020/cm3程度とすることができる。半導体層1bの厚さは、後で形成されるp型ウエルPWおよびn型ウエルNWが半導体層1b内に含まれ得るような厚さで形成され、例えば1〜10μm程度の厚さを有している。

The

他の形態として、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上が導入された半導体層(半導体領域)1bを、半導体基板1aの上層部分に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上をイオン注入することによって形成することもできる。 As another form, a semiconductor layer (semiconductor region) 1b into which one or more of carbon (C), nitrogen (N), or fluorine (F) are introduced is formed on the upper layer portion of the semiconductor substrate 1a with carbon (C), It can also be formed by ion implantation of one or more of nitrogen (N) or fluorine (F).

次に、図17に示されるように、半導体基板SUB1の主面に素子分離領域2を形成する。素子分離領域2の形成法などは、上記実施の形態1と同様であるので、ここではその説明は省略する。素子分離領域2によって、nMIS形成領域1AとpMIS形成領域1Bとが規定される。

Next, as shown in FIG. 17, the

次に、上記実施の形態1と同様の絶縁膜3を半導体基板SUB1の表面(すなわち半導体層1bの表面)に形成する。

Next, an insulating

次に、図18に示されるように、nMIS形成領域1Aにおいて、上記実施の形態1のチャネルドープイオン注入IM1aと同様のチャネルドープイオン注入(後で形成されるnチャネル型MISFETQnのしきい値調整用のイオン注入)IM1aを行なって、半導体層1bの上層部分にチャネルドープ層4aを形成する。それから、nMIS形成領域1Aにおいて、半導体層1bにp型ウエルPWをイオン注入によって形成する。また、pMIS形成領域1Bにおいて、上記実施の形態1のチャネルドープイオン注入IM1bと同様のチャネルドープイオン注入(後で形成されるpチャネル型MISFETQpのしきい値調整用のイオン注入)IM1bを行なって、半導体層1bの上層部分にチャネルドープ層4bを形成する。それから、pMIS形成領域1Bにおいて、半導体層1bにn型ウエルNWをイオン注入によって形成する。

Next, as shown in FIG. 18, in the

なお、図18では、チャネルドープイオン注入IM1a,IM1bを矢印で模式的に示してあるが、チャネルドープイオン注入IM1aとチャネルドープイオン注入IM1bとは、それぞれ別工程で行なう。すなわち、上記実施の形態1と同様に本実施の形態においても、チャネルドープ層4aを形成するためのチャネルドープイオン注入IM1aと、p型ウエルPWを形成するためのイオン注入とは、上記フォトレジスト膜RP1aと同様のフォトレジスト膜(図示せず)でpMIS形成領域1Bを覆った状態で行ない、pMIS形成領域1Bの半導体層1bにイオン注入されないようにする。一方、チャネルドープ層4bを形成するためのチャネルドープイオン注入IM1bと、n型ウエルNWを形成するためのイオン注入とは、上記フォトレジスト膜RP1bと同様のフォトレジスト膜(図示せず)でnMIS形成領域1Aを覆った状態で行ない、nMIS形成領域1Aの半導体層1bにイオン注入されないようにする。

In FIG. 18, channel dope ion implantation IM1a and IM1b are schematically indicated by arrows, but channel dope ion implantation IM1a and channel dope ion implantation IM1b are performed in separate steps. That is, in the present embodiment as in the first embodiment, the channel dope ion implantation IM1a for forming the

上記実施の形態1では、半導体基板1にチャネルドープイオン注入IM1a,IM1bを行なってチャネルドープ層4a,4bを形成していた。それに対して、本実施の形態では、半導体層1bにチャネルドープイオン注入IM1a,IM1bを行なってチャネルドープ層4a,4bを形成しているが、それ以外は、本実施の形態でのチャネルドープイオン注入IM1a,IM1bおよびチャネルドープ層4a,4bの構成については、上記実施の形態1と同様である。また、上記実施の形態1では、半導体基板1にp型ウエルPWおよびn型ウエルNWを形成していたのに対して、本実施の形態では、半導体層1bにp型ウエルPWおよびn型ウエルNWを形成しているが、それ以外は、本実施の形態でのp型ウエルPWおよびn型ウエルNWの形成法と構成については、上記実施の形態1と同様である。

In the first embodiment, channel dope ion implantation IM1a and IM1b are performed on the

次に、上記絶縁膜3を除去して半導体層1bの表面を清浄化した後、nMIS形成領域1AおよびpMIS形成領域1Bの半導体層1bの表面(p型ウエルPWおよびn型ウエルNWの表面)上にゲート絶縁膜用の絶縁膜5を形成する。上記実施の形態1では、半導体基板1に絶縁膜の表面に絶縁膜5を形成していたのに対して、本実施の形態では、半導体層1bに絶縁膜5を形成しているが、それ以外は、本実施の形態での絶縁膜5の形成法と構成については、上記実施の形態1と同様である。

Next, after removing the insulating

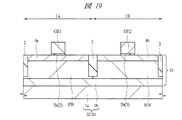

次に、ゲート電極GE1,GE2を形成する。上記実施の形態1では、半導体基板1上に絶縁膜5(ゲート絶縁膜5a,5b)を介してゲート電極GE1,GE2を形成していたのに対して、本実施の形態では、半導体層1b上に絶縁膜5(ゲート絶縁膜5a,5b)を介してゲート電極GE1,GE2を形成している。それ以外は、本実施の形態でのゲート電極GE1,GE2の形成法と構成については、上記実施の形態1と同様である。これにより、図19の構造が得られる。

Next, gate electrodes GE1 and GE2 are formed. In the first embodiment, the gate electrodes GE1 and GE2 are formed on the

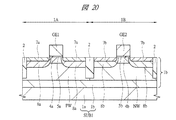

次に、図20に示されるように、nMIS形成領域1Aの半導体層1b(p型ウエルPW)のゲート電極GE1の両側の領域に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、エクステンション領域7aを形成する。それから、nMIS形成領域1Aの半導体層1b(p型ウエルPW)に、イオン注入(ハローイオン注入)を行ってハロー領域8aを形成する。また、pMIS形成領域1Bの半導体層1b(n型ウエルNW)のゲート電極GE2の両側の領域に、上記実施の形態1と同様に、ホウ素(B)などのp型の不純物をイオン注入することにより、エクステンション領域7bを形成する。それから、pMIS形成領域1Bの半導体層1b(n型ウエルNW)に、イオン注入(ハローイオン注入)を行ってハロー領域8bを形成する。

Next, as shown in FIG. 20, n-type impurities such as phosphorus (P) or arsenic (As) are formed in the regions on both sides of the gate electrode GE1 of the

なお、上記実施の形態1と同様に本実施の形態2および以下の実施の形態3,4においても、エクステンション領域7aを形成するためのイオン注入と、ハロー領域8aを形成するためのイオン注入とは、上記フォトレジスト膜RP2aと同様のフォトレジスト膜(図示せず)でpMIS形成領域1Bを覆った状態で行ない、pMIS形成領域1Bの半導体層1bにイオン注入されないようにする。一方、上記実施の形態1と同様に本実施の形態2および以下の実施の形態3,4においても、エクステンション領域7bを形成するためのイオン注入と、ハロー領域8bを形成するためのイオン注入とは、上記フォトレジスト膜RP2bと同様のフォトレジスト膜(図示せず)でnMIS形成領域1Aを覆った状態で行ない、nMIS形成領域1Aの半導体層1bにイオン注入されないようにする。

As in the first embodiment, also in the second embodiment and the following third and fourth embodiments, ion implantation for forming the

上記実施の形態1では、半導体基板1にエクステンション領域7a,7bおよびハロー領域8a,8bを形成していたのに対して、本実施の形態では、半導体層1bにエクステンション領域7a,7bおよびハロー領域8a,8bを形成しているが、それ以外は、本実施の形態でのエクステンション領域7a,7bおよびハロー領域8a,8bの形成法と構成については、上記実施の形態1と同様である。

In the first embodiment, the

次に、図21に示されるように、上記実施の形態1と同様に、ゲート電極GE1,GE2の側壁上にサイドウォール(側壁絶縁膜)SWを形成する。 Next, as shown in FIG. 21, as in the first embodiment, sidewalls (sidewall insulating films) SW are formed on the sidewalls of the gate electrodes GE1 and GE2.

次に、nMIS形成領域1Aの半導体層1b(p型ウエルPW)のゲート電極GE1およびサイドウォールSWの両側の領域に、リン(P)またはヒ素(As)などのn型の不純物をイオン注入することにより、n+型半導体領域11a(ソース、ドレイン)を形成する。また、pMIS形成領域1Bの半導体層1b(n型ウエルNW)のゲート電極GE2およびサイドウォールSWの両側の領域に、ホウ素(B)などのp型の不純物をイオン注入することにより、p+型半導体領域11b(ソース、ドレイン)を形成する。

Next, n-type impurities such as phosphorus (P) or arsenic (As) are ion-implanted into the regions on both sides of the gate electrode GE1 and the sidewall SW of the

なお、上記実施の形態1と同様に本実施の形態2および以下の実施の形態3,4においても、n+型半導体領域11aを形成するためのイオン注入は、上記フォトレジスト膜RP3aと同様のフォトレジスト膜(図示せず)でpMIS形成領域1Bを覆った状態で行ない、pMIS形成領域1Bの半導体層1bにイオン注入されないようにする。一方、上記実施の形態1と同様に本実施の形態2および以下の実施の形態3,4においても、p+型半導体領域11bを形成するためのイオン注入は、上記フォトレジスト膜RP3bと同様のフォトレジスト膜(図示せず)でnMIS形成領域1Aを覆った状態で行ない、nMIS形成領域1Aの半導体層1bにイオン注入されないようにする。

As in the first embodiment, also in the second embodiment and the following third and fourth embodiments, the ion implantation for forming the n +

上記実施の形態1では、半導体基板1にn+型半導体領域11aおよびp+型半導体領域11bを形成していたのに対して、本実施の形態では、半導体層1bにn+型半導体領域11aおよびp+型半導体領域11bを形成しているが、それ以外は、本実施の形態でのn+型半導体領域11aおよびp+型半導体領域11bの形成法と構成については、上記実施の形態1と同様である。

In the first embodiment, the n +

次に、上記実施の形態1と同様に、これまでのイオン注入で導入した不純物の活性化のためのアニール処理(熱処理)を行う。 Next, similarly to the first embodiment, annealing treatment (heat treatment) for activating the impurities introduced by the conventional ion implantation is performed.

以降の工程は、上記実施の形態1と同様である。すなわち、図22に示されるように、ゲート電極GE1,GE2、n+型半導体領域11aおよびp+型半導体領域11bの表面にそれぞれ金属シリサイド層12を形成し、半導体基板SUB1の主面(すなわち半導体層1bの主面)上にゲート電極GE1,GE2を覆うように絶縁膜21を形成し、絶縁膜21上に絶縁膜22を形成する。それから、絶縁膜22,21にコンタクトホール23を形成し、コンタクトホール23内にプラグ24を形成する。その後、プラグ24が埋め込まれた絶縁膜22上に、ストッパ絶縁膜25および絶縁膜26を順に形成し、絶縁膜26およびストッパ絶縁膜25に配線溝27を形成し、配線溝27の底部および側壁上を含む絶縁膜26上にバリア導体膜28を形成し、配線溝27を銅の主導体膜29で埋め込んで配線M1を形成する。

The subsequent steps are the same as those in the first embodiment. That is, as shown in FIG. 22, the metal silicide layers 12 are formed on the surfaces of the gate electrodes GE1, GE2, the n +

次に、本実施の形態の効果について、より詳細に説明する。 Next, the effect of this embodiment will be described in more detail.

上記実施の形態1では、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上が導入された拡散防止領域10a,10bを形成することで、チャネル領域への点欠陥の拡散を防止し、それによって、チャネル領域における点欠陥の密度を抑制して、チャネルドープイオン注入でチャネル領域に導入された不純物の再配置(拡散)を抑制していた。

In the first embodiment, by forming the

それに対して、本実施の形態では、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上が導入された半導体層1bを上部に有する半導体基板SUB1を準備し、この半導体層1bにnチャネル型MISFETQnおよびpチャネル型MISFETQpを形成している。すなわち、本実施の形態では、nチャネル型MISFETQnおよびpチャネル型MISFETQpのチャネル領域、エクステンション領域7a,7b、ハロー領域8a,8b、n+型半導体領域11aおよびp+型半導体領域11bは、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上が導入された半導体層1bに形成されている。

On the other hand, in the present embodiment, a semiconductor substrate SUB1 having a

上述のように、単結晶シリコンに炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上が導入された領域(本実施の形態の半導体層1bに対応)は、点欠陥が拡散(移動)しにくく、点欠陥の拡散(移動)を防止する機能を有している。このため、本実施の形態では、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上が導入された半導体層1b全体に渡って、点欠陥が拡散(移動)しにくい。このため、エクステンション領域7a,7b、ハロー領域8a,8b、n+型半導体領域11aおよびp+型半導体領域11bを形成する際の各イオン注入で生成された点欠陥が、nチャネル型MISFETQnおよびpチャネル型MISFETQpのチャネル領域(ゲート電極GE1,GE2の直下の領域)にまで拡散するのを防止でき、チャネル領域における点欠陥の密度を抑制することできる。これにより、チャネルドープイオン注入でチャネル領域に導入された不純物が、その後の加熱工程の際に再配置(拡散)されるのを抑制または防止することができるので、注入直後のチャネルドープ不純物の配置(ランダム性が高い配置)を維持することができる。従って、MISFET毎のチャネル領域の状態(不純物分布)のばらつきを抑制して、MISFET毎のしきい値電圧のばらつきを抑制することができ、半導体装置の性能を向上させることができる。

As described above, a region where one or more of carbon (C), nitrogen (N), and fluorine (F) is introduced into single crystal silicon (corresponding to the

また、半導体層1bには、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上が導入されているが、炭素(C)、窒素(N)およびフッ素(F)のうち、点欠陥の拡散防止に最も有効なのは炭素(C)である。このため、半導体層1bには、炭素(C)、窒素(N)またはフッ素(F)のうち少なくとも炭素(C)を導入していればより好ましい。

In addition, one or more of carbon (C), nitrogen (N), and fluorine (F) are introduced into the

また、本実施の形態では、半導体基板1aの主面上に半導体層1bをエピタキシャル成長などで形成したが、他の形態として、半導体基板1の上層部分に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上をイオン注入することで、半導体基板1の上層部分に半導体層1bに相当する領域を形成することもできる。この場合、上記半導体基板SUB1全体が上記半導体基板1に相当し、上記半導体基板SUB1のうちの上記半導体層1bが、半導体基板1のうち、イオン注入で炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上を導入した半導体領域(半導体層)に相当する。すなわち、半導体基板1の上層部分に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上をイオン注入することで、半導体層1bに相当する半導体領域(半導体層)を形成し、この半導体領域(半導体層)内に、p型ウエルPW、n型ウエルNW、エクステンション領域7a,7b、ハロー領域8a,8b、n+型半導体領域11aおよびp+型半導体領域11bを形成するのである。この場合も、エクステンション領域7a,7b、ハロー領域8a,8b、n+型半導体領域11aおよびp+型半導体領域11bを形成する際のイオン注入で生成された点欠陥が、nチャネル型MISFETQnおよびpチャネル型MISFETQpのチャネル領域に拡散するのを防止でき、チャネル領域における点欠陥の密度を抑制することができる。従って、チャネルドープイオン注入でチャネル領域に導入された不純物が、その後の加熱工程の際に再配置(拡散)されるのを抑制または防止することができ、MISFET毎のチャネル領域の状態(不純物分布)のばらつきを抑制して、MISFET毎のしきい値電圧のばらつきを抑制することができる。

In the present embodiment, the

また、本実施の形態では、半導体層1b全体に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上を導入して、そこにp型ウエルPW、n型ウエルNW、エクステンション領域7a,7b、ハロー領域8a,8b、n+型半導体領域11aおよびp+型半導体領域11bを形成している。このため、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上を導入したことによる、イオン注入時に生成された点欠陥の拡散を抑制する効果は、極めて大きい。

In the present embodiment, at least one of carbon (C), nitrogen (N), and fluorine (F) is introduced into the

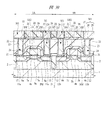

(実施の形態3)

本実施の形態3の半導体装置の製造工程を図面を参照して説明する。図23〜図32は、本実施の形態の半導体装置の製造工程中の要部断面図である。

(Embodiment 3)

A manufacturing process of the semiconductor device according to the third embodiment will be described with reference to the drawings. 23 to 32 are main-portion cross-sectional views during the manufacturing process of the semiconductor device of the present embodiment.

本実施の形態では、上記実施の形態1と同様に、図23に示されるように、まず、半導体基板(半導体ウエハ)1を準備し、半導体基板1の主面に素子分離領域2を形成する。

In the present embodiment, as in the first embodiment, as shown in FIG. 23, first, a semiconductor substrate (semiconductor wafer) 1 is prepared, and an

次に、上記実施の形態1と同様の絶縁膜3を半導体基板1の表面に形成する。

Next, an insulating

次に、nMIS形成領域1Aにおいて、上記実施の形態1と同様にして、半導体基板1の主面から所定の深さに渡ってp型ウエルPWを形成し、また、pMIS形成領域1Bにおいて、上記実施の形態1と同様にして、半導体基板1の主面から所定の深さに渡ってn型ウエルNWを形成する。本実施の形態でのp型ウエルPWおよびn型ウエルNWの形成法と構成については、上記実施の形態1と同様である。

Next, in the

なお、本実施の形態では、後述するゲート絶縁膜用の絶縁膜5を形成する前には、nチャネル型MISFETQnのしきい値調整用のチャネルドープイオン注入IM1aおよびpチャネル型MISFETQpのしきい値調整用のチャネルドープイオン注入IM1bは行なわないため、この段階では、チャネルドープ層4a,4bは形成されていない。

In this embodiment, before forming an insulating

次に、図24に示されるように、上記実施の形態1と同様、上記絶縁膜3を除去して半導体基板1の表面を清浄化した後、nMIS形成領域1AおよびpMIS形成領域1Bの半導体基板1の表面(p型ウエルPWおよびn型ウエルNWの表面)上にゲート絶縁膜用の絶縁膜5を形成する。本実施の形態での絶縁膜5の形成法と構成については、上記実施の形態1と同様である。

Next, as shown in FIG. 24, after removing the insulating

次に、図25に示されるように、半導体基板1の主面全面上(すなわちnMIS形成領域1AおよびpMIS形成領域1Bの絶縁膜5上を含む)に、導電体膜(導電体層)として、多結晶シリコン膜のようなシリコン膜(第1導電体層)6aを形成する。また、シリコン膜6aは、成膜時にはアモルファスシリコン膜であったものを、成膜後の熱処理により多結晶シリコン膜に変えることもできる。シリコン膜6aの厚み(堆積膜厚)t1は、例えば20〜100nm程度とすることができる。

Next, as shown in FIG. 25, as a conductor film (conductor layer) on the entire main surface of the semiconductor substrate 1 (that is, on the insulating

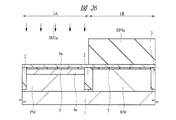

次に、図26に示されるように、pMIS形成領域1Bを覆うフォトレジスト膜(フォトレジストパターン)RP4aを、フォトリソグラフィ技術を用いて形成する。nMIS形成領域1Aは、このフォトレジスト膜RP4aでは覆われずに露出される。このフォトレジスト膜RP4aは、pMIS形成領域1Bへのイオン注入阻止マスクとして機能することができる。

Next, as shown in FIG. 26, a photoresist film (photoresist pattern) RP4a covering the

次に、nMIS形成領域1Aにおいて、上記実施の形態1と同様のチャネルドープイオン注入(後で形成されるnチャネル型MISFETQnのしきい値調整用のイオン注入)IM1aを行なって、半導体基板1(p型ウエルPW)の上層部分にチャネルドープ層4aを形成する。なお、図26では、チャネルドープイオン注入IM1aを矢印で模式的に示してある。

Next, in the

上記実施の形態1では、ゲート絶縁膜用の絶縁膜5の形成前に半導体基板1にチャネルドープイオン注入IM1aを行なってチャネルドープ層4aを形成していた。これに対して、本実施の形態では、ゲート絶縁膜用の絶縁膜5とシリコン膜6aの形成後にチャネルドープイオン注入IM1aを行なってチャネルドープ層4aを形成しているが、それ以外は、本実施の形態でのチャネルドープイオン注入IM1aおよびチャネルドープ層4aの構成については、上記実施の形態1と同様である。

In the first embodiment, the channel dope ion implantation IM1a is performed on the

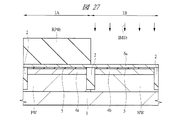

次に、図27に示されるように、フォトレジスト膜RP4aを除去してから、nMIS形成領域1Aを覆うフォトレジスト膜(フォトレジストパターン)RP4bを、フォトリソグラフィ技術を用いて形成する。pMIS形成領域1Bは、このフォトレジスト膜RP4bでは覆われずに露出される。このフォトレジスト膜RP4bは、nMIS形成領域1Aへのイオン注入阻止マスクとして機能することができる。

Next, as shown in FIG. 27, after the photoresist film RP4a is removed, a photoresist film (photoresist pattern) RP4b covering the

次に、pMIS形成領域1Bにおいて、上記実施の形態1と同様のチャネルドープイオン注入(後で形成されるpチャネル型MISFETQpのしきい値調整用のイオン注入)IM1bを行なって、半導体基板1(n型ウエルNW)の上層部分にチャネルドープ層4bを形成する。なお、図27では、チャネルドープイオン注入IM1bを矢印で模式的に示してある。

Next, in the

上記実施の形態1では、ゲート絶縁膜用の絶縁膜5の形成前に半導体基板1にチャネルドープイオン注入IM1bを行なってチャネルドープ層4bを形成していた。これに対して、本実施の形態では、ゲート絶縁膜用の絶縁膜5とシリコン膜6aの形成後にチャネルドープイオン注入IM1bを行なってチャネルドープ層4bを形成しているが、それ以外は、本実施の形態でのチャネルドープイオン注入IM1bおよびチャネルドープ層4bの構成については、上記実施の形態1と同様である。他の形態として、pMIS形成領域1Bにチャネルドープイオン注入IM1bによってチャネルドープ層4bを形成した後で、nMIS形成領域1Aにチャネルドープイオン注入IM1aによってチャネルドープ層4aを形成することもできる。

In the first embodiment, the channel dope ion implantation IM1b is performed on the

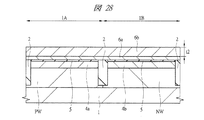

次に、図28に示されるように、フォトレジスト膜RP4aを除去してから、シリコン膜6a上に、導電体膜(導電体層)として、多結晶シリコン膜のようなシリコン膜(第2導電体層)6bを形成する。シリコン膜6bの厚み(堆積膜厚)t2は、シリコン膜6aの厚みt1よりも厚い(すなわちt2>t1)ことが好ましく、例えば80〜150nm程度とすることができる。シリコン膜6aとシリコン膜6bとの積層膜が、上記シリコン膜6に相当するものとなる。

Next, as shown in FIG. 28, after removing the photoresist film RP4a, a silicon film (second conductive film) such as a polycrystalline silicon film is formed on the

次に、図29に示されるように、シリコン膜6aとシリコン膜6bとの積層膜をフォトリソグラフィ法およびドライエッチング法を用いてパターニングすることにより、ゲート電極GE1,GE2を形成する。すなわち、nMIS形成領域1Aの絶縁膜5(すなわちゲート絶縁膜5a)上にゲート電極GE1を、pMIS形成領域1Bの絶縁膜5(すなわちゲート絶縁膜5b)上にゲート電極GE2を形成する。

Next, as shown in FIG. 29, gate electrodes GE1 and GE2 are formed by patterning the laminated film of the

このため、本実施の形態では、ゲート電極GE1,GE2は、シリコン膜6aとシリコン膜6a上のシリコン膜6bとの積層膜からなる。ゲート電極GE1の下に残存する絶縁膜5が、nチャネル型MISFETQnのゲート絶縁膜5aとなり、ゲート電極GE2の下に残存する絶縁膜5が、pチャネル型MISFETQpのゲート絶縁膜5bとなる。

For this reason, in the present embodiment, the gate electrodes GE1 and GE2 are formed of a laminated film of the

以降の工程は、拡散防止領域10a,10b形成工程(イオン注入IM5a,IM5b)を省略すること以外は、上記実施の形態1と同様である。

Subsequent steps are the same as those in the first embodiment except that the step of forming

すなわち、図30に示されるように、nMIS形成領域1Aの半導体基板1(p型ウエルPW)に、エクステンション領域7aおよびハロー領域8aを形成し、また、pMIS形成領域1Bの半導体基板1(n型ウエルNW)に、エクステンション領域7bおよびハロー領域8bを形成する。本実施の形態でのエクステンション領域7a,7bおよびハロー領域8a,8bの形成法と構成については、上記実施の形態1と同様である。

That is, as shown in FIG. 30, the

次に、図31に示されるように、ゲート電極GE1,GE2の側壁上にサイドウォール(側壁絶縁膜)SWを形成してから、nMIS形成領域1Aの半導体基板1(p型ウエルPW)にn+型半導体領域11a(ソース、ドレイン)を形成し、また、pMIS形成領域1Bの半導体基板1(n型ウエルNW)にp+型半導体領域11b(ソース、ドレイン)を形成する。本実施の形態でのサイドウォールSW、n+型半導体領域11aおよびp+型半導体領域11bの形成法と構成については、上記実施の形態1と同様である。

Next, as shown in FIG. 31, after sidewalls (sidewall insulating films) SW are formed on the sidewalls of the gate electrodes GE1 and GE2, n are formed on the semiconductor substrate 1 (p-type well PW) in the

次に、上記実施の形態1と同様に、これまでのイオン注入で導入した不純物の活性化のためのアニール処理(熱処理)を行う。 Next, similarly to the first embodiment, annealing treatment (heat treatment) for activating the impurities introduced by the conventional ion implantation is performed.

その後、図32に示されるように、上記実施の形態1と同様に、ゲート電極GE1,GE2、n+型半導体領域11aおよびp+型半導体領域11bの表面にそれぞれ金属シリサイド層12を形成し、半導体基板1の主面上にゲート電極GE1,GE2を覆うように絶縁膜21を形成し、絶縁膜21上に絶縁膜22を形成し、絶縁膜22,21にコンタクトホール23を形成し、コンタクトホール23内にプラグ24を形成する。それから、上記実施の形態1と同様に、プラグ24が埋め込まれた絶縁膜22上に、ストッパ絶縁膜25および絶縁膜26を順に形成し、絶縁膜26およびストッパ絶縁膜25に配線溝27を形成し、配線溝27の底部および側壁上を含む絶縁膜26上にバリア導体膜28を形成し、配線溝27を銅の主導体膜29で埋め込んで配線M1を形成する。

Thereafter, as shown in FIG. 32, similarly to the first embodiment, metal silicide layers 12 are formed on the surfaces of the gate electrodes GE1, GE2, the n +

次に、本実施の形態の効果について、より詳細に説明する。 Next, the effect of this embodiment will be described in more detail.

上記実施の形態1,2では、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上が導入された拡散防止領域10a,10bまたは半導体層1bを形成することで、チャネル領域への点欠陥の拡散を防止し、それによって、チャネル領域における点欠陥の密度を抑制して、チャネルドープイオン注入でチャネル領域に導入された不純物の再配置(拡散)を抑制していた。

In the first and second embodiments, the channel is formed by forming the

それに対して、本実施の形態では、チャネルドープイオン注入の工程順を工夫することで、チャネルドープイオン注入でチャネル領域に導入された不純物の再配置(拡散)を抑制している。 On the other hand, in the present embodiment, the rearrangement (diffusion) of impurities introduced into the channel region by channel doping ion implantation is suppressed by devising the process order of channel doping ion implantation.

ゲート絶縁膜用の絶縁膜5を熱酸化で形成すると、熱酸化時の加熱温度が例えば700〜900℃程度と高いため、本実施の形態とは異なり、ゲート絶縁膜用の絶縁膜5形成前にチャネルドープイオン注入を行なった場合には、チャネルドープイオン注入でチャネル領域に導入された不純物が、ゲート絶縁膜用の絶縁膜5形成時の加熱(ゲート酸化時の加熱)により再配置(拡散)しやすい。

When the insulating

そこで、本実施の形態では、ゲート絶縁膜用の絶縁膜5を形成した後で、nMIS形成領域1Aへのチャネルドープイオン注入IM1aおよびpMIS形成領域1Bへのチャネルドープイオン注入IM1bを行なってチャネルドープ層4a,4bを形成している。ゲート絶縁膜用の絶縁膜5を形成した後にチャネルドープイオン注入IM1a,IM1bを行なうことで、チャネルドープイオン注入IM1a,IM1bでチャネル領域に導入された不純物が、ゲート絶縁膜用の絶縁膜5形成時の加熱(ゲート酸化時の加熱)により再配置(拡散)することがない。すなわち、たとえゲート絶縁膜用の絶縁膜5を熱酸化で形成することで半導体基板1が高温に加熱されても、その段階ではチャネルドープイオン注入IM1a,IM1bが行なわれていないため、その後のチャネルドープイオン注入IM1a,IM1bでチャネル領域に導入された不純物が、熱酸化(ゲート酸化)時の加熱で再配置(拡散)することはない。これにより、チャネルドープイオン注入でチャネル領域に導入された不純物が、その後の加熱工程の際に再配置(拡散)されるのを抑制することができるので、MISFET毎のチャネル領域の状態(不純物分布)のばらつきを抑制して、MISFET毎のしきい値電圧のばらつきを抑制することができる。従って、半導体装置の性能を向上させることができる。

Therefore, in this embodiment, after forming the insulating

また、本実施の形態では、ゲート絶縁膜用の絶縁膜5形成後、更にシリコン膜6aを形成した後に、nMIS形成領域1Aへのチャネルドープイオン注入IM1aおよびpMIS形成領域1Bへのチャネルドープイオン注入IM1bを行なってチャネルドープ層4a,4bを形成している。ゲート絶縁膜用の絶縁膜5がシリコン膜6aで覆われた状態(すなわち絶縁膜5が露出していない状態)でチャネルドープイオン注入IM1a,IM1bを行なうため、チャネルドープイオン注入によってゲート絶縁膜用の絶縁膜5がダメージを受けるのを防止することができる。これにより、ゲート絶縁膜5a,5bの信頼性を向上することができ、半導体装置の信頼性を向上させることができる。

In the present embodiment, after forming the insulating

また、ゲート電極の高さに相当する厚い導体膜(ゲート電極用の導体膜)を半導体基板の全面に形成した状態でチャネルドープイオン注入を行なった場合、ゲート電極用の導体膜が厚いことにより、半導体基板へのチャネルドープが的確に行えない虞がある。それに対して、本実施の形態では、シリコン膜6aが形成された状態でチャネルドープイオン注入IM1a,IM1bを行ない、その後シリコン膜6a上にシリコン膜6bを形成して、この積層膜をパターニングすることで、ゲート電極GE1,GE2を形成している。このため、ゲート電極GE1,GE2の高さよりも、シリコン膜6aの厚みt1を薄くすることができる。従って、チャネルドープイオン注入IM1a,IM1bを行なう際の、シリコン膜6aの厚みt1を薄くすることができ、半導体基板へのチャネルドープを的確に行うことができる。

In addition, when channel doping ion implantation is performed in a state where a thick conductor film (gate electrode conductor film) corresponding to the height of the gate electrode is formed on the entire surface of the semiconductor substrate, the gate electrode conductor film is thick. There is a possibility that channel doping to the semiconductor substrate cannot be performed accurately. On the other hand, in this embodiment, channel dope ion implantation IM1a and IM1b is performed in a state where the

また、シリコン膜6aの厚み(堆積膜厚)t1が、シリコン膜6bの厚み(堆積膜厚)t2よりも薄いことが好ましい(すなわちt1<t2)。すなわち、ゲート電極GE1,GE2の高さは、シリコン膜6aの厚みt1とシリコン膜6bの厚みt2とを足したもの(すなわちt1+t2)に相当するが、シリコン膜6aの厚み(堆積膜厚)t1を、ゲート電極GE1,GE2の高さの半分以下にすることが好ましい。これにより、チャネルドープイオン注入IM1a,IM1bを行なう際のシリコン膜6aの厚みt1を薄くすることができるため、チャネルドープイオン注入IM1a,IM1bをより的確に行うことができる。

The thickness (deposited film thickness) t1 of the

また、本実施の形態は、ゲート絶縁膜用の絶縁膜5の形成後にチャネルドープイオン注入を行なうことで、チャネル領域の不純物に対する絶縁膜5形成時の加熱の影響を防止しているため、ゲート絶縁膜用の絶縁膜5形成時の温度が高い場合に適用すれば、効果が大きい。このため、本実施の形態は、ゲート絶縁膜用の絶縁膜5を熱酸化法で形成する場合に適用すれば、効果が極めて大きい。

Further, in the present embodiment, channel doping ion implantation is performed after the formation of the insulating

また、本実施の形態3は、上記実施の形態1,2と組み合わせることもできる。すなわち、本実施の形態3において、上記実施の形態1と同様に拡散防止領域10a,10bを形成することもでき、この場合も、拡散防止領域10a,10bの構成と形成法については、上記実施の形態1と同様である。また、本実施の形態3において、上記実施の形態2と同様の半導体基板SUB1(すなわち半導体基板1a上に半導体層1bを形成したもの)を用いることもできる。この場合、本実施の形態において、nチャネル型MISFETQnおよびpチャネル型MISFETQpのチャネル領域、p型ウエルPW、n型ウエルNW、エクステンション領域7a,7b、ハロー領域8a,8b、n+型半導体領域11aおよびp+型半導体領域11bは、炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上が導入された半導体層1bに形成されることになる。これにより、ゲート絶縁膜用の絶縁膜5形成後にチャネルドープイオン注入を行なうことによる、チャネルドープ不純物の再配置(拡散)抑制効果と、拡散防止領域10a,10bまたは半導体層1bを設けたことでチャネル領域への点欠陥の拡散を防止したことによる、チャネルドープ不純物の再配置(拡散)抑制効果との両方を得ることができる。従って、MISFET毎のチャネル領域の状態(不純物分布)のばらつきをより的確に抑制して、MISFET毎のしきい値電圧のばらつきをより的確に抑制することができ、半導体装置の性能を更に向上させることができる。

Further, the third embodiment can be combined with the first and second embodiments. That is, in the third embodiment, the

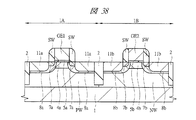

(実施の形態4)

本実施の形態4の半導体装置の製造工程を図面を参照して説明する。図33〜図39は、本実施の形態の半導体装置の製造工程中の要部断面図である。

(Embodiment 4)

A manufacturing process of the semiconductor device according to the fourth embodiment will be described with reference to the drawings. 33 to 39 are main-portion cross-sectional views during the manufacturing process of the semiconductor device of the present embodiment.

本実施の形態では、図33に示されるように、上記実施の形態1と同様に、まず、半導体基板(半導体ウエハ)1を準備し、半導体基板1の主面に素子分離領域2を形成する。

In the present embodiment, as shown in FIG. 33, as in the first embodiment, first, a semiconductor substrate (semiconductor wafer) 1 is prepared, and an

次に、上記実施の形態1と同様に、絶縁膜3を半導体基板1の表面に形成してから、pMIS形成領域1Bを覆うフォトレジスト膜RP1aを形成する。

Next, as in the first embodiment, after the insulating

次に、nMIS形成領域1Aにおいて、半導体基板1の上層部分に、後で形成されるnチャネル型MISFETQnのしきい値調整用のイオン注入(すなわちチャネルドープイオン注入)IM1aを行なう。なお、図34では、このチャネルドープイオン注入IM1aを矢印で模式的に示してある。しきい値調整用のイオン注入IM1a、すなわちチャネルドープイオン注入IM1aでは、nチャネル型MISFETQnのチャネル領域を含む領域に、不純物(不純物イオン)が導入(イオン注入)されて、チャネルドープ層4aが形成されるため、このチャネルドープ層4aは、後でnチャネル型MISFETQnのチャネル領域となる領域を含んでいる。

Next, in the

本実施の形態において、このnMIS形成領域1Aへのチャネルドープイオン注入IM1aによってチャネルドープ層4aに導入される元素(不純物)は、インジウム(In)とガリウム(Ga)の一方または両方を用い、これに更にホウ素(B)を組み合わせることもできる。すなわち、本実施の形態でnMIS形成領域1Aへのチャネルドープイオン注入工程でイオン注入する元素(不純物)は、インジウム(In)か、ガリウム(Ga)か、インジウム(In)とガリウム(Ga)か、ホウ素(B)とインジウム(In)か、ホウ素(B)とガリウム(Ga)か、あるいはホウ素(B)とインジウム(In)とガリウム(Ga)である。なお、nMIS形成領域1Aへのチャネルドープイオン注入IM1aでは、pMIS形成領域1Bを覆うフォトレジスト膜RP1aは、イオン注入阻止マスクとして機能するので、pMIS形成領域1Bの半導体基板1には、イオン注入されない。

In the present embodiment, one or both of indium (In) and gallium (Ga) is used as an element (impurity) introduced into the

次に、nMIS形成領域1Aにおいて、上記実施の形態1と同様にして、半導体基板1の主面から所定の深さに渡ってp型ウエルPWを形成する。本実施の形態でのp型ウエルPWの形成法と構成については、上記実施の形態1と同様である。

Next, in the

次に、図35に示されるように、アッシングなどによりフォトレジスト膜RP1aを除去してから、上記実施の形態1と同様に、nMIS形成領域1Aを覆うフォトレジスト膜RP1bを形成する。

Next, as shown in FIG. 35, after the photoresist film RP1a is removed by ashing or the like, a photoresist film RP1b covering the

次に、pMIS形成領域1Bにおいて、半導体基板1の上層部分に、後で形成されるpチャネル型MISFETQpのしきい値調整用のイオン注入(すなわちチャネルドープイオン注入)IM1bを行なう。なお、図35では、このチャネルドープイオン注入IM1bを矢印で模式的に示してある。このしきい値調整用のイオン注入IM1b、すなわちチャネルドープイオン注入IM1bでは、pチャネル型MISFETQpのチャネル領域を含む領域に、不純物(不純物イオン)が導入(イオン注入)されて、チャネルドープ層4bが形成されるため、このチャネルドープ層4bは、後でpチャネル型MISFETQpのチャネル領域となる領域を含んでいる。

Next, in the

本実施の形態において、このpMIS形成領域1Bへのチャネルドープイオン注入IM1bによってチャネルドープ層4bに導入される元素(不純物)は、ヒ素(As)とアンチモン(Sb)の一方または両方を用い、これに更にリン(P)を組み合わせることもできる。すなわち、本実施の形態でpMIS形成領域1Bへのチャネルドープイオン注入工程でイオン注入する元素(不純物)は、ヒ素(As)か、アンチモン(Sb)か、ヒ素(As)とアンチモン(Sb)か、リン(P)とヒ素(As)か、リン(P)とアンチモン(Sb)か、あるいはリン(P)とヒ素(As)とアンチモン(Sb)かである。なお、pMIS形成領域1Bへのチャネルドープイオン注入IM1bでは、nMIS形成領域1Aを覆うフォトレジスト膜RP1aは、イオン注入阻止マスクとして機能するので、nMIS形成領域1Aの半導体基板1には、イオン注入されない。

In the present embodiment, the element (impurity) introduced into the

次に、pMIS形成領域1Bにおいて、上記実施の形態1と同様にして、半導体基板1の主面から所定の深さに渡ってn型ウエルNWを形成する。本実施の形態でのn型ウエルNWの形成法と構成については、上記実施の形態1と同様である。

Next, in the

以降の工程は、拡散防止領域10a,10b形成工程(イオン注入IM5a,IM5b)を省略すること以外は、上記実施の形態1と同様である。

Subsequent steps are the same as those in the first embodiment except that the step of forming

すなわち、図36に示されるように、フォトレジスト膜RP1bを除去してから、上記絶縁膜3を除去して半導体基板1の表面を清浄化した後、nMIS形成領域1AおよびpMIS形成領域1Bの半導体基板1の表面(p型ウエルPWおよびn型ウエルNWの表面)上にゲート絶縁膜用の絶縁膜5を形成し、絶縁膜5上にゲート電極GE1,GE2を形成する。それから、図37に示されるように、nMIS形成領域1Aの半導体基板1(p型ウエルPW)に、エクステンション領域7aおよびハロー領域8aを形成し、また、pMIS形成領域1Bの半導体基板1(n型ウエルNW)に、エクステンション領域7bおよびハロー領域8bを形成する。本実施の形態での絶縁膜5、ゲート電極GE1,GE2、エクステンション領域7a,7bおよびハロー領域8a,8bの形成法と構成については、上記実施の形態1と同様である。

That is, as shown in FIG. 36, after removing the photoresist film RP1b, the insulating

次に、図38に示されるように、ゲート電極GE1,GE2の側壁上にサイドウォール(側壁絶縁膜)SWを形成してから、nMIS形成領域1Aの半導体基板1(p型ウエルPW)にn+型半導体領域11a(ソース、ドレイン)を形成し、また、pMIS形成領域1Bの半導体基板1(n型ウエルNW)にp+型半導体領域11b(ソース、ドレイン)を形成する。本実施の形態でのサイドウォールSW、n+型半導体領域11aおよびp+型半導体領域11bの形成法と構成については、上記実施の形態1と同様である。

Next, as shown in FIG. 38, sidewalls (sidewall insulating films) SW are formed on the sidewalls of the gate electrodes GE1 and GE2, and then n is formed on the semiconductor substrate 1 (p-type well PW) in the

次に、上記実施の形態1と同様に、これまでのイオン注入で導入した不純物の活性化のためのアニール処理(熱処理)を行う。 Next, similarly to the first embodiment, annealing treatment (heat treatment) for activating the impurities introduced by the conventional ion implantation is performed.

その後、図39に示されるように、上記実施の形態1と同様に、ゲート電極GE1,GE2、n+型半導体領域11aおよびp+型半導体領域11bの表面にそれぞれ金属シリサイド層12を形成し、半導体基板1の主面上にゲート電極GE1,GE2を覆うように絶縁膜21を形成し、絶縁膜21上に絶縁膜22を形成し、絶縁膜22,21にコンタクトホール23を形成し、コンタクトホール23内にプラグ24を形成する。それから、上記実施の形態1と同様に、プラグ24が埋め込まれた絶縁膜22上に、ストッパ絶縁膜25および絶縁膜26を順に形成し、絶縁膜26およびストッパ絶縁膜25に配線溝27を形成し、配線溝27の底部および側壁上を含む絶縁膜26上にバリア導体膜28を形成し、配線溝27を銅の主導体膜29で埋め込んで配線M1を形成する。

Thereafter, as shown in FIG. 39, similarly to the first embodiment, metal silicide layers 12 are formed on the surfaces of the gate electrodes GE1, GE2, the n +

次に、本実施の形態の効果について、より詳細に説明する。 Next, the effect of this embodiment will be described in more detail.

上記実施の形態1〜3では、チャネルドープイオン注入IM1a,IM1bで導入された不純物が、イオン注入後に拡散されにくいように工夫していた。それに対して、本実施の形態では、チャネルドープイオン注入後に拡散されにくいような元素(不純物)を、チャネルドープイオン注入IM1a,IM1bで注入している。 In the first to third embodiments, the impurities introduced by the channel dope ion implantation IM1a and IM1b are devised so that they are not easily diffused after the ion implantation. In contrast, in the present embodiment, elements (impurities) that are difficult to diffuse after channel doping ion implantation are implanted by channel doping ion implantation IM1a and IM1b.

すなわち、イオン注入された元素(不純物)は、原子番号が大きい元素ほど(すなわち重い元素ほど)、イオン注入後の加熱によって移動(拡散)しにくく、イオン打ち込みで配置された位置に留まりやすい。このため、原子番号が小さな軽い不純物元素をイオン注入した場合、注入直後の段階では、注入された不純物元素はランダムに配置されていても、その後の種々の加熱工程で不純物元素が拡散(移動)して、不純物元素の配置のランダム性が低下しやすいのに比べて、原子番号が大きな重い不純物元素をイオン注入した場合、注入直後の不純物元素のランダムな配置は、その後の種々の加熱工程を経ても維持されやすい。 That is, an ion-implanted element (impurity) is more difficult to move (diffusion) by heating after ion implantation as the element with a larger atomic number (that is, heavier element) and stays at the position where ion implantation is performed. For this reason, when a light impurity element having a small atomic number is ion-implanted, the impurity element diffuses (moves) in various subsequent heating steps even if the implanted impurity element is randomly arranged in the stage immediately after the implantation. When the impurity element having a large atomic number is ion-implanted compared to the random arrangement of the impurity element, the random arrangement of the impurity element immediately after the implantation is performed in various subsequent heating steps. It is easy to maintain even after passing.

そこで、本実施の形態では、チャネルドープイオン注入IM1a,IM1bに、原子番号が大きい元素(すなわち重い元素)を用いる。 Therefore, in this embodiment, an element having a large atomic number (that is, a heavy element) is used for channel dope ion implantation IM1a and IM1b.

nMIS形成領域1A(nチャネル型MISFETQn)について具体的に説明すると、nMIS形成領域1Aへのチャネルドープイオン注入IM1aに用いる元素(すなわちチャネルドープイオン注入IM1aでチャネルドープ層4aに導入される不純物元素)として、インジウム(In)とガリウム(Ga)の一方または両方を用いる。インジウム(In)およびガリウム(Ga)は、ホウ素(B)と同様にp型の不純物として機能できるが、ホウ素(B)よりも原子番号が大きく重いため、ホウ素(B)に比べて、注入後の加熱によって移動(拡散)されにくい。このため、チャネルドープイオン注入IM1aでチャネルドープ層4aに導入された不純物(ここではインジウム(In)とガリウム(Ga)の一方または両方)は、注入直後の不純物元素のランダムな配置が、その後の種々の加熱工程を経ても維持されやすい。これにより、チャネルドープイオン注入IM1aでnチャネル型MISFETQnのチャネル領域(チャネルドープ層4a)に導入された不純物(ここではインジウム(In)とガリウム(Ga)の一方または両方)が、その後の加熱工程の際に再配置(拡散)されるのを抑制または防止することができるので、nチャネル型MISFET毎のチャネル領域の状態(不純物分布)のばらつきを抑制することができる。従って、nチャネル型MISFET毎のしきい値電圧のばらつきを抑制することができ、半導体装置の性能を向上させることができる。

The